功能仿真不是一個孤立的過程,其和綜合、時序分析等形成一個反饋工作過程,只有這個過程收斂,各個環節才有意義。而孤立的功能仿真通過是沒有意義的,如果在時序分析過程中發現時序不滿足需要更改代碼,則功能仿真必須從新進行。

2011-03-03 10:18:03 7765

7765

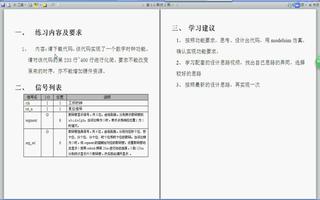

對于FPGA開發而言,仿真是開發流程中必不可少的一步,也是非常重要的一步,仿真是將RTL代碼模擬運行,得到module中信號波形,再進行功能分析的過程。強大的功能與速度兼具的modelsim仿真就是

2020-09-30 13:52:33 8686

8686

Vivado Simulator基本操作 Vivado Simulator是一款硬件描述語言事件驅動的仿真器,支持功能仿真和時序仿真,支持VHDL、Verilog、SystemVerilog和混合

2020-12-31 10:02:10 7123

7123 直接在modelsim軟件內執行.do文件進行仿真,不通過vivado調用modelsim,vivado僅用于生成IP核。

2023-12-04 18:26:34 477

477

大家好!我在使用Modelsim進行仿真時,從 ISE 啟動 Modelsim 仿真是完全正常的,但從 Modelsim 直接建立工程,進行仿真,總是提示“Module 'IBUFG

2015-01-26 23:17:51

為什么這樣做就不是很了解了。經過昨天一天的努力,現在基本上明白了整個過程。對這篇文章進行整體的完善和補充(本人水平有限,如有錯誤請留言指正)。 用Modelsim對Quartus II工程進行時序仿真

2012-02-01 11:37:40

` Modelsim 與Matalb模擬視頻流仿真 本章節主要搭建一個視頻流Modelsim仿真,在基于FPGA視頻圖像算法開發過程中,最終目的是為了把攝像頭實時視頻數據經過一系列的圖像算法,通過

2019-03-03 18:11:22

各位,小弟最近遇到一個很奇怪的問題。我在使用modelsim進行仿真時,無論是通過quartus調用還是直接運行modelsim,都會遇到提示:“error loading design“,從而仿真

2015-08-30 22:14:39

modelsim 仿真

2013-09-09 19:27:29

各位大神,求教如何用modelsim-ase 進行時序仿真,小弟最近被這整得焦頭爛額{:4:}{:4:}。希望大家不吝賜教,最好附上詳細教程。不過注意,不是modelsim SE哦。小弟萬分感激!

2014-01-22 15:18:52

請問一下在ISE14.6中編譯完modelsim10.0a,在用modelsim進行仿真時會閃退是怎么回事,有什么解決辦法?期待熱心的你給以指教!

2016-05-19 21:10:18

如題,最近看很多modelsim的資料,很多時候仿真要添加仿真原型文件,比較困擾的是怎么選擇仿真原型文件,不同功能怎么對應相應的仿真原型文件呢,我發現很多資料都沒講清楚。

2014-03-09 22:31:36

用modelsim仿真時出來Modelsim is exiting with code 7然后就關閉了是怎么回事

2020-04-13 04:23:07

為什么簡單的分頻器程序調用modelsim仿真不了,同樣的方法仿真與門程序就沒有問題啊?下面是自己寫的源程序和測試程序。module ff (clk,q);input clk;output q

2013-10-08 20:28:56

在使用quartusii modelsim仿真時。。功能仿真可以好用,。但是時序仿真就出錯。。無論是手動打開modelsim,還是直接調用。。時序仿真就是出錯。。沒有輸出。。但是用quartus自帶的vwf那個仿真時。。功能和時序仿真就都好用。。到底什么原因呢。。{:4:}。。誰能給指點一下

2013-11-26 21:06:56

功能仿真:可以驗證代碼的邏輯性,不加任何的時延信息。仿真工具為modelsim(組合邏輯和時序邏輯都可以功能仿真),modelsim不能綜合。在modelsim中添加相應的激勵信號,調用

2016-08-23 16:57:06

ATK-DAP仿真器 BURNER 5V

2023-03-28 13:05:53

ATK-HSDAP仿真器 BURNER

2023-03-28 13:05:52

ATK-USB Blaster仿真器 BURNER 5V

2023-03-28 13:05:53

Altera和Xilinx Modelsim仿真庫Altera和Xilinx Modelsim仿真庫 我們通常使用modelsim軟件作為仿真工具,不同階段的仿真使用不同的庫文件,在開始仿真前將庫

2012-08-10 18:31:02

DAP仿真器 BURNER

2023-03-28 13:06:20

quartus和modelsim聯合仿真容易出現問題,所以一般單獨用modelsim仿真,附件是modelsim仿真的步驟

2017-02-17 20:21:18

ISE聯合Modelsim進行仿真,里面介紹得非常詳細

2018-01-12 15:01:09

本文主要描述了如何在QUARTUS II中輸入程序文件,生成網表及標準延時文件,然后通過 MODELSIM進行功能仿真與后仿真的過程,主要為圖解,含全部代碼及仿真波形。 工具: 源程序

2012-08-12 16:12:54

ST-LINK仿真器 BURNER 5V

2023-03-28 13:06:38

USB Blaster仿真器 BURNER 5V

2023-03-28 13:06:20

搗鼓了半天沒有弄明白怎么用配合modelsim進行仿真

2013-07-31 20:42:05

本人小白,最近自學FPGA,用的quartus和modelsim軟件,主要功能同時產生兩個一樣的波形,想用原理圖描述方式實現,但是在配置完原理圖和tb文件后,時序仿真波形正確,功能仿真確實高阻態,求大神幫忙解釋下!!原理圖:時序仿真:功能仿真

2016-11-16 15:30:32

。用modelsim做功能仿真FPGA的IP核ROM的時候,ROM里面需要存.hex格式文件;而用門級或者時序仿真的時候,則不需要,只需要直接給.mif文件就行。我們應該都清楚,功能仿真是只仿的.v

2014-03-06 16:22:21

vivado中如何對edif封裝后的文件進行modelsim下的時序仿真,求教

2017-09-03 14:52:44

內容了。3.總結這次的ModelSim仿真功能講的比較簡單,后續如果有再接觸到ModelSim仿真,給大家做一個詳細的講解和使用。`

2020-11-04 22:03:09

第一步:我實在quartusii上進行仿真產生.vo文件和.sdo文件第二步:用modelsim仿真,進行了一些設置但是最后時序仿真結果和功能仿真的一樣,沒有延遲,不知道怎么回事??求大神解決

2015-01-16 16:40:08

FPGA設計流程包括設計輸入,仿真,綜合,生成,板級驗證等很多階段。在整個設計流程中,完成設計輸入并成功進行編譯僅能說明設計符合一定的語法規范,并不能說明設計功能的正確性,這時就需要通過仿真對設計進行驗證。在FPGA 設計中,仿真一般分為功能仿真(前仿真)和時序仿真(后仿真)。

2019-09-20 06:36:23

我現在將vivado和modelsim做了聯合仿真,用來仿真蜂鳥e203協處理器擴展實現的功能。現在的問題是:使用vivado的仿真器仿真時vivado的TCL console可以打印輸出C程序中

2023-08-11 06:44:51

想要仿真quartus下工程中的一個IP核,但是不知道怎么樣才能把這個IP核弄到modelsim下進行仿真,求指教!!!!!

2014-04-04 00:36:25

的Keep Hierarchy選擇YES的功能是一樣的。利用ModelSim SE6.0C實現時序仿真[hide][/hide]

2012-03-01 11:46:29

的結構及意義Modelsim與c語言協同仿真,一是用于產生測試向量,避免手工編寫測試向量的繁瑣;二是可以根據程序計算結果自動檢查仿真結果正確與否;三是模擬其它模塊(如RAM)的功能,在系統級對設計文件

2019-06-06 05:00:38

如何使用modelsim仿真?是不是一定要有testbench .v 文件?

2014-03-29 09:56:53

Tutorial里面.它從簡單到復雜、從低級到高級詳細地講述了modelsim的各項功能的使用,簡單易懂。但是它也有缺點,就是它里面所有事例的初期準備工作都已經放在example文件夾里,直接將它們添加到

2015-11-29 21:35:23

本文在開環時序仿真的基礎上提出一種基于QuartusII、DSP Builder和Modelsim的閉環時序仿真測試方法,并借助于某一特定智能控制器的設計對該閉環測試方法進行了較為深入的研究。

2021-05-06 09:36:44

Quartusii 13.1版本,執行全編譯后,在simulation-modelsim文件夾下可以找到后仿真所需.vo文件,Modelsim后仿真過程正確,但是,在chip planner下移

2018-01-22 21:51:35

三篇給大家講解使用腳本命令來加速FPGA的仿真過程。FPGA的仿真又分為前仿真和后仿真,前仿真即功能仿真,是在不考慮器件的布局布線和延時的理想情況下對源代碼進行的仿真;后仿真即時序仿真,時序仿真

2020-04-25 08:00:00

高速DAP仿真器 BURNER

2023-03-28 13:06:20

總線監控分析、仿真、測試工具。具備對總線數據的監控與分析、節點仿真、報文發送、負載統計、離線回放、故障診斷、腳本編程、Panel面板搭建等功能。當前支持CAN、CA

2021-03-05 10:42:54

在Modelsim SE中如何指定altera仿真庫

2008-09-09 17:50:04 44

44 SPEOS是ANSYS公司功能強大的光學仿真軟件,用于光學設計、環境與視覺模擬、成像仿真等,強大的解決方案提供了可視化光學系統和直觀的人機交互平臺,其仿真技術已廣泛用于汽車、電子電器、精密儀器

2022-04-19 10:37:53

用ModelSimSE進行功能仿真和時序仿真的方法(ALTERA篇)(ALTERA 篇)軟件準備(1) QuartusII,本文截圖是QuartusII 6.1 界面的。我個人認為,如果是開發StratixII 或CycloneII 或MAXII

2009-06-19 00:26:41 70

70 本文主要描述了如何在 QUARTUS II 中輸入程序文件,生成網表及標準延時文件,然后通過MODELSIM 進行功能仿真與后仿真的過程,主要為圖解,含全部代碼及仿真波形。

2009-07-22 15:44:53 0

0 我把我用到的軟件說明一下。如果你發現根據我的操作,你還是解決不了ModelSim后仿真的問題,那就可能是軟件版本的問題。

2009-07-22 15:46:27 0

0 我想很多人跟我一樣,被ModelSim的后仿真搞的頭暈腦脹。為了這個問題,我在網上找了很多的資料,但發現這些資料往往說的不明白。一些步驟被作者有意無意地省略掉,這常常給讀

2010-03-31 09:46:36 112

112 當我們使用QuartusII,但是大多數朋友都習慣用Modelsim SE來做仿真,由于Quaruts有很多本身器件的特色,所以造成了在仿真上的麻煩,當然網路上也有一些講解,但是都是不太系統,特

2010-06-24 17:57:18 216

216 SMT焊接溫度曲線智能仿真系統是一個全流程模擬PCB SMT焊接受熱過程的智能化仿真系統。系統通過虛擬化構建數字化PCBA模型、回流爐模型,關聯錫膏、器件、產品的工藝要求,通過熱仿真軟件來實現焊點

2024-03-18 17:00:11

1 前言 協同仿真就是利用仿真工具提供的外部接口,用其它程序設計語言(非HDL語言,如c語言等)編程,用輔助仿真工具進行仿真。Modelsim提供了與c語言的協同

2010-06-07 08:33:59 1124

1124

ModelSim為HDL仿真工具,我們可以利用該軟件來實現對所設計的VHDL或Verilog程序進行仿真,支持IEEE常見的各種硬件描述語言標準。可以進行兩種語言的混合仿真,但推薦大家只對一種語言

2011-04-19 20:52:46 151

151 ModelSim為HDL仿真工具,我們可以利用該軟件來實現對所設計的VHDL或Verilog程序進行仿真,支持IEEE常見的各種硬件描述語言標準。可以進行兩種語言的混合仿真,但推薦大家只對一種語言

2011-05-27 16:41:59 132

132 根據源同步的一些基本問題,在Cadence仿真環境下,對源同步時序進行仿真,仿真結果表明,設計能滿足噪聲容限和過沖,仿真后的可知數據線和時間的延時約為0.3ns,滿足源同步系統設

2012-05-29 15:26:26 0

0 Altera ModelSim 6.5仿真入門教程,需要的可自行下載。 平臺 軟件:ModelSim-Altera 6.5e (Quartus II 10.0) Starter Edition 內容 1 設計流程 使用ModelSim仿真的基本流程為: 圖1.1 使用 ModelSim仿真的基本

2012-08-15 15:40:24 255

255 ALTERA公司:用ModelSimSE進行功能仿真和時序仿真的方法(ALTERA篇)之學習筆記

2012-08-15 16:00:59 68

68 用ModelSim 進行功能仿真,進行功能仿真首先要檢查設計的語法是否正確;其次檢查代碼是否達到設計的功能要求。下文主要介紹仿真步驟和測試激勵的加載。

2012-11-13 15:35:59 8536

8536 基于Xilinx ISE的modelsim仿真教程

2015-11-30 15:52:56 8

8 仿真教程,在仿真過程中更好的參考,解決一些問題

2015-12-07 10:36:55 0

0 本章為ModelSim的初級教程,讀者讀完本章可以較為熟練的使用ModelSim進行設計仿真,本章沒有也不可能涉及ModelSim的各個方面,要想全面的掌握ModelSim可以參閱軟件文檔。

2015-12-24 18:29:37 0

0 在我們用ModelSim仿真的時候經常是修改一點一點修改代碼,這樣會造成一個無奈的操作循環:修改代碼--->編譯代碼--->仿真設置--->進入仿真頁面--->添加需要觀察的波形--->運行仿真

2017-02-11 15:25:07 10139

10139

Modelsim是Mentor公司開發的專業仿真軟件,支持VHDL、VerilogHDL和混合仿真的全系列流程。作為目前最流行的仿真工具之一,Modelsim提供了圖形界面和命令行兩種工作模式

2017-11-24 11:54:06 24959

24959

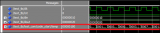

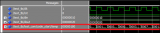

ModelSim不僅可以用于數字電路系統設計的功能仿真,還可以應用于數字電路系統設計的時序仿真。 ModelSim的使用中,最基本的步驟包括創建工程、編寫源代碼、編譯、啟動仿真器和運行仿真五個步驟,仿真流程如圖1所示:

2018-12-29 11:35:14 9227

9227 本文檔的主要內容詳細介紹的是modelsim仿真使用教程資料免費下載。

2019-04-02 08:00:00 6

6 筆者一直以來都在糾結,自己是否要為仿真編輯相關的教程呢?一般而言,Modelsim等價仿真已經成為大眾的常識,但是學習仿真是否學習Modelsim,筆者則是一直保持保留的態度。筆者認為,仿真

2019-04-30 18:24:00 23

23 本文檔的主要內容詳細介紹的是HDL仿真軟件Modelsim的安裝教程資料免費下載。安裝教程很詳細,大家一步步來安裝基本都能安裝好。

2019-05-28 08:00:00 7

7 ModelSim是業界最優秀的HDL語言仿真軟件,它能提供友好的仿真環境,是業界唯一的單內核支持VHDL和Verilog混合仿真的仿真器。它采用直接優化的編譯技術、Tcl/Tk技術、和單一內核

2019-12-02 07:01:00 4710

4710

本文檔的主要內容詳細介紹的是三態門原理HDL語言DSP和ARM總線的仿真及Modelsim使用教程資料主要內容包括了:1 ModelSimSE的使用流程,2 一個Verilog計數器仿真詳細

2019-07-09 16:49:27 10

10 之前玩過Altera的板子,不不, 現在應該叫intel PSG。在QuartusII13.0上老喜歡用modelsim_ae做仿真,小工程用起來也方便,但是我做IIC配置攝像頭的時序仿真時,就顯得有些吃力,所以還是用modelsim_se才是正點。

2020-04-10 08:00:00 1

1 仿真( Simulation)即利用軟件方法,對所設計的系統進行功能及時序驗證的過程。它是設計項目成功與否的關鍵,設計的大部分時間均被用于仿真。通常,硬件系統的仿真分為兩種,即功能仿真和時序仿真

2021-01-20 16:27:59 8

8 Modelsim加速仿真技巧 《前言》 最近在Modelsim仿真過程中,遇到一個大問題,對于分辨率2048*500的圖像數據,在進行時序約束中,發現算法模塊最高只能跑到60Mhz多,而要求必須跑到

2021-04-02 13:58:05 4720

4720 總體思想是現在 MATLAB 中產生仿真所需要的輸入信號,以十六進制形式存放在數據文件中,在modelsim 中用 vhdl 語言編寫測試文件,做時序仿真,最后將結果存入另外一個數據文件,最后在 matlab中將 modelsim 的仿真輸出文件讀入一個數組中,以便可以作圖分心,進一步做誤差分析。

2021-06-01 10:31:20 33

33 3 ModelSim工程實戰之自動仿真說完了 ModelSim 的使用流程,接下來我們將會對每個流程進行詳細的操作演示,一步步、手把手帶領大家學習使用 ModelSim 軟件。首先我們講解

2021-07-23 10:51:17 1710

1710

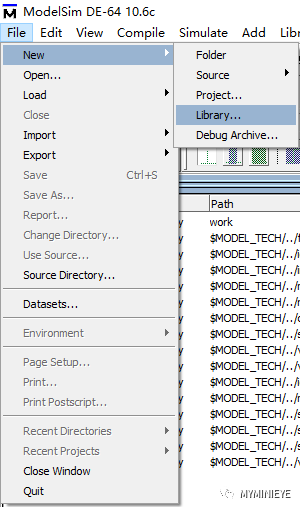

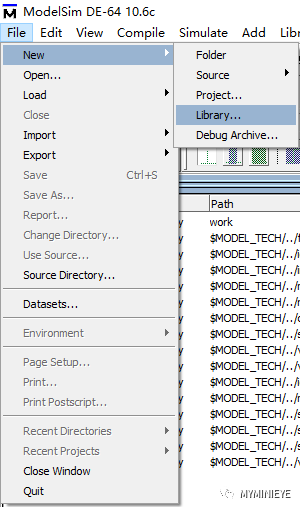

4.1 新建仿真工程 在開始動手仿真之前,首先,我們需要創建一個文件夾用來放置我們的 ModelSim 仿真工程文件,這里我們就在之前創建的 Quartus 工程目錄下的 simulation

2021-07-23 11:10:48 3514

3514 時序仿真與功能仿真的步驟大體相同,只不過中間需要添加仿真庫、網表(.vo)文件和延時(.sdo)文件。到了這里,問題來了,仿真庫、網表(.vo)文件和延時(.sdo)文件怎么獲得呢?網表(.vo

2021-07-23 11:55:41 1915

1915 Modelsim使用技巧—波形白底黑線設置 在發表期刊或者論文時,我們需要夾帶modelsim的仿真波形在我們的論文里,在modelsim默認模式下的波形一般是黑底綠線白字,如圖1所示。打印出來幾乎

2021-08-26 11:23:12 3451

3451 調用第三方仿真軟件查看波形的過程中存在的一些問題。 1、添加新的觀測信號需要重新仿真 Vivado直接調用Modelsim/QuestaSim進行仿真時,波形文件里默認只會出現仿真最頂層中包含

2021-09-02 10:12:06 7274

7274

Vivado自帶的仿真,個人覺得跑一些小模塊的仿真還是可以的,不過跑大的仿真系統,容易無體驗感,建議用第三方工具,這邊就直接對ModelSim下手了,接下來介紹下這兩者聯合仿真的操作。

2022-03-11 11:32:11 6154

6154 在開始動手仿真之前,首先,我們需要創建一個文件夾用來放置我們的 ModelSim 仿真工程文件,這里我們就在之前創建的 Quartus 工程目錄下的 simulation 文件夾中創建

2022-07-11 10:58:09 4458

4458 4.1 新建仿真工程在開始動手仿真之前,首先,我們需要創建一個文件夾用來放置我們的 ModelSim 仿真工程文件,這里我們就在之前創建的 Quartus 工程目錄下的 simulation 文件夾中創建一個manual_modelsim 文件夾。

2022-07-11 11:05:21 1152

1152 通過該圖,我們可以看出,這個工程是我們之前做功能仿真的工程,當我們關閉 ModelSim之后,我們再次打開 ModelSim 這個軟件,它會自動記錄上一個我們使用的工程并打開。我們就直接在這個工程

2022-07-18 14:17:25 894

894 最近在Modelsim仿真過程中,遇到一個大問題,對于分辨率2048*500的圖像數據,在進行時序約束中,發現算法模塊最高只能跑到60Mhz多,而要求必須跑到100Mhz,因而時序不滿足要求;通過

2022-08-08 14:15:18 12055

12055 Modelsim仿真將設計以樹狀表示,設計中的每一個實體,每一個module、每一個進程(always塊、initial塊等)在Modelsim仿真中以對象的形式展現。

2022-08-12 15:04:36 2136

2136 大家好!今天給大家帶來的是modelsim自動化仿真程序。我們在代碼編寫完成時,通常都需要先進行仿真,然后上板實驗。但是如果我們每次仿真都要去新建一個工程,添加.v文件以及testbench文件

2023-07-19 10:10:56 941

941

Modelsim是十分常用的外部仿真工具,在Vivado中也可以調用Modelsim進行仿真,下面將介紹如何對vivado進行配置并調用Modelsim進行仿真,在進行仿真之前需要提前安裝Modelsim軟件。

2023-07-24 09:04:43 1817

1817

時序仿真與功能仿真的區別在于 時序仿真與功能仿真是電子設計自動化(EDA)中最常見的兩種仿真方式。雖然二者都是仿真技術,但根據仿真模型和目的的不同,它們之間還是存在一些根本差異。 1.定位 時序仿真

2023-09-08 10:39:40 2654

2654 時序仿真與功能仿真的區別有哪些? 時序仿真和功能仿真都是電子設計自動化(EDA)過程中的常見任務,它們都是為了驗證或驗證電路設計的正確性。然而,它們之間也有明顯的區別。 時序仿真 時序仿真是一種

2023-09-17 14:15:02 2254

2254 是指在芯片設計過程中,對電路的功能和性能進行仿真驗證的環節。它主要關注電路的功能性、時序和功耗等方面,以確保設計的正確性和可行性。前仿真通常在物理布局之前進行,因此也稱為靜態時序分析或網表級仿真。 后仿真:后仿

2023-12-13 15:06:55 1484

1484 ModelSim為HDL仿真工具,我們可以利用該軟件來實現對所設計的VHDL或Verilog程 序進行仿真,支持IEEE常見的各種硬件描述語言標準。可以進行兩種語言的混合仿真,但 推薦大家只對一種語言仿真。

2024-01-14 09:47:47 0

0 后仿真也稱為時序仿真或者布局布線后仿真,是指電路已經映射到特定的工藝環境以后,綜合考慮電路的路徑延遲與門延遲的影響,驗證電路能否在一定時序條件下滿足設計構想的過程,是否存在時序違規。

2024-03-06 09:58:21 238

238

FPGA時序仿真和功能仿真在芯片設計和驗證過程中各自扮演著不可或缺的角色,它們之間存在明顯的區別。

2024-03-15 15:28:40 132

132

電子發燒友App

電子發燒友App

評論