很多應用 (包括精密儀器、工業自動化、醫療設備和自動測試設備) 都需要高準確度數模轉換。在 16 位分辨率時要求準確度好于約 ±15ppm 或 ±1LSB 的電路中,設計師傳統上一直被迫使用大量校準,以在所有情況下保持準確度。新型高精度 DAC 使得能夠采用一個單片式 DAC 來實現 ±4ppm 準確度或 ±1LSB (在 18 位分辨率條件下),而無需校準。在本文中我們將對高精度數模轉換器的選擇和使用過程中所涉及的問題進行研究。

DAC 的架構對于 DAC 的技術規格及其對電路板設計師的要求均有影響。為了實現最佳性能,需要謹慎地考慮 DAC 上的電源、基準和輸出放大器所產生的影響。

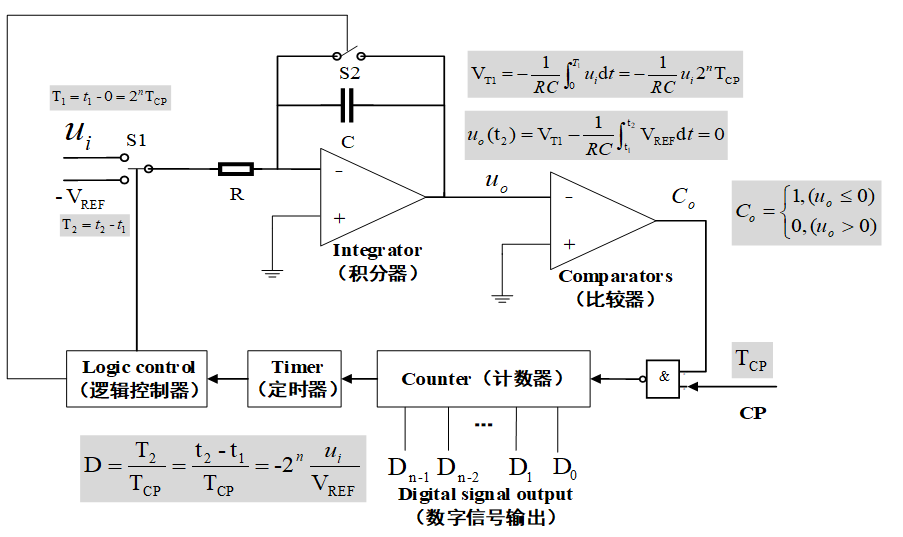

過采樣或增量累加 DAC

過采樣或 ΔΣ ADC 采用一個低分辨率 DAC (通常僅 1 位),在其前后分別布設一個噪聲整形數字調制器和一個模擬低通濾波器。最準確的商用增量累加 DAC 實現 ±15ppm 的準確度,但是需要 15ms 才能穩定,并要承受相對較高的 1μV/√Hz 噪聲密度。其它可購得的過采樣 DAC 在 80us 內穩定,但是 INL 較差,大約為 240 ppm。

合成 DAC

通過結合兩個較低分辨率的單片 DAC,有可能構成一個高分辨率的合成 DAC。請注意,粗略 DAC 的分辨率和精細 DAC 的范圍需要重疊,以確保所有想要的輸出電壓都可實現。粗略 DAC 的準確度和漂移一般將限制合成 DAC 的最終準確度,因此要提高準確度,就需要對合成 DAC 轉移函數的特性和軟件進行校正。也可能需要頻率校準,以校正隨溫度、時間、濕度和機械壓力產生的變化導致的漂移。

電阻串 DAC

電阻串 DAC 采用具有 2N 個分接點的一系列電阻分壓器,以實現 N 位分辨率。采用電阻串架構的單片 16 位 DAC 一般含有一個較低分辨率的電阻串 DAC 和一個范圍較小的 DAC,范圍較小的 DAC 用于插入串器件之間,以實現 16 位分辨率。這種串+內插器方法的一個優點是,DAC 輸出具有固有的單調性,無需微調或校準。

這類 DAC 的基準輸入阻抗一般很高 (50KΩ~ 300kΩ),而且不受輸入代碼的影響,從而有可能使用一個非緩沖型基準。因為電阻串的輸出阻抗隨輸入代碼變化,所以大多數電阻串 DAC 含有集成的輸出緩沖器放大器,以驅動電阻性負載。

盡管電阻串 DAC 的 DNL 本身非常好,但是 INL 由串聯電阻器件的匹配決定,而且可能由于含有大量的獨立器件而難以控制。直到最近,這類 DAC 的準確度一直限制在約 ±180ppm。最近的進步已經使得準確度提高到了 ±60ppm。例如,LTC2656 在 4mm x 5mm 封裝中集成了 8 個 DAC 通道,在 16 位分辨率時具有 ±4LSB 的最大 INL。

阻性梯形或 R-2R 型 DAC

阻性梯形或 R-2R DAC 采用一種類似于圖 2 所示的三端子結構,電阻器在 A 端和 B 端之間切換。請注意,A 端和 B 端上的阻抗與代碼的相關性很高,而 C 端則具有一個固定阻抗。電阻器與開關的匹配情況將會影響這種結構的單調性和準確度。此類 DAC 一般經過修整或在出廠時經過校準,而且,具 ±1LSB INL 和 DNL 的單調 16 位阻性梯形電路 DAC 上市已有很長時間了。

電壓輸出 R-2R DAC

一種常見類型的 R-2R DAC 將C 端用作 DAC 輸出電壓,而 A 端連接到基準,B 端連接到地。輸出阻抗相對于輸入代碼是恒定的,從而有可能以非緩沖方式驅動電阻負載。例如,LTC2641 16 位 DAC 能以非緩沖方式驅動 60kΩ 負載,同時保持 ±1LSB 的 INL 和 DNL,并消耗不到 200μA 的電源電流。

這種方法的一個缺點是,基準阻抗隨著輸入代碼大幅變化。由于 R-2R 梯形電路的本質,甚至 DAC 輸出電壓中很小的變化也可能在基準電流中引起 1mA 或更大的階躍變化。為此,必須由一個高性能放大器來對基準進行緩沖,并采用一種非常精細和針對性的檢測電路布局,以限制穩定、干擾脈沖和線性度性能的最終劣化。

當一個輸出緩沖器放大器和一個電壓輸出 R-2R DAC 一起使用時,該放大器的開環增益和大信號共模抑制必須足夠高,以保持輸出的線性度 (在 18 位時 >110dB)。輸出緩沖器的失調和輸入偏置電流將主要以 DAC 輸出偏移的形式出現,但是這些參數在輸入共模范圍內的任何變化都將以附加的 INL 誤差形式出現。

請注意,在正和負基準開關之間有必要保持匹配的阻抗,以保持 DAC 線性度。因為 CMOS 開關阻抗是電壓和溫度的函數,因此這給 DAC 的準確度帶來了挑戰,尤其是在低電源電壓時。可采用這種架構的 18 位 DAC 的 PSRR 被限制在約 64dB。結果,隨著時間、溫度、電壓和負載狀況的變化,電源必須在約 0.5% 的范圍內保持恒定,以保持 18 位性能。在工作溫度范圍內,這類 DAC 的 INL 可以預期以 ±0.5LSB 或更大的幅度漂移。

迄今為止,當采用一個5V電源時,運用該架構和一個集成輸出放大器的18位DAC的性能一直被限制為±2LSB INL(在18位)。采用3V電源時,其性能將進一步限制為±3LSB INL(在18位),且單調性下降至 17位。

電流輸出 R-2R DAC

對于高準確度應用來說,這種架構具有很多優點。基準阻抗是恒定的,可以用非緩沖型基準或一個慢速低精確度運算放大器驅動。因為 A 端和 B 端處于相同的地電位,所以保持匹配的開關阻抗相對容易,甚至在出現電源電壓和溫度變化時也一樣。結果,精確的電流輸出 R-2R DAC 具有卓越的 PSRR 和溫度漂移性能。

與電流輸出 R-2R DAC 一起使用的輸出放大器需要高開環增益 (在 18 位時 >110 dB) 和低失調電壓。A 端和 B 端之間的任何偏移都將產生一種取決于代碼的誤差電流,該誤差電流將以 INL 誤差的形式出現。輸出緩沖器的輸入偏置電流不那么重要,主要以 DAC 輸出偏移的形式出現。因為兩個輸入都始終處于地電位,所以放大器的共模抑制不重要。

在 16 位時實現 ±1LSB INL 的電流輸出 R-2R DAC 長久以來一直可以普遍購得,凌力爾特公司提供一種新的 18 位 DAC 系列,在 18 位分辨率時實現 ±4ppm 的準確度或 ±1LSB 的最大 INL,在整個溫度范圍內有保證 。LTC2757 提供并聯接口,可立即購得。LTC2756/8 單和雙通道 SPI DAC 計劃在未來數月內推出。在 18 位時,LTC2757 從 -40℃~+85℃的典型 INL 漂移不到 ±0.2LSB,高達 96dB 的 PSRR 使輸出對電源變化不敏感。

緩沖型與非緩沖型 DAC 輸出

有些高度準確的 DAC 在 DAC 內部集成了輸出放大器,而其它一些這類放大器則需要一個外部運算放大器。在這兩種情況下,大多數 DAC 都提供集成的電平移動和反饋電阻器,以不再需要精確的外部器件。集成輸出放大器的主要優點是占板面積小和使用方便。成本通常不是首要因素,因為外部放大器器件通常比 DAC 本身便宜得多。

設計師應該意識到,一個集成的輸出放大器也許會損害設計靈活性。內部放大器提供的輸出擺幅、速度、噪聲和功率合起來,不可能對于多種應用來說都是最佳的。例如,一個集成的單電源輸出放大器在靠近電源軌時將遭遇準確度下降問題,因此設計師必須提供電平移動差分基準,以利用全部的 DAC 代碼范圍。如果內部放大器的負反饋輸出不可使用,則有可能無法針對大容性負載來補償輸出環路,或增設一個外部緩沖器而不引入第二個反饋環路,對于那些需要一個較寬輸出擺幅或較高負載電流的用戶來說,他們將會由于增設一個具有與內部放大器環路相串聯的獨立反饋環路的外部放大級,而導致準確度、噪聲和功耗等性能的損失。

具有一個外部放大器的非緩沖型 DAC 一般實現最佳性能。多種可購得的器件給設計師提供了自由,可對給定的應用選擇一個具有最佳準確度、速度、噪聲和功率的解決方案。

選擇輸出放大器

當選擇與 LTC2757 等準確的電流輸出 DAC 一起使用的放大器電路時,失調電壓是一個重要的考慮因素。DAC 線性度對放大器失調的敏感性取決于 DAC 的實現方式,制造商應該在數據表中描述清楚。就 LTC2757 而言,±80μV 的失調電壓將在 DAC 輸出引起約 ±1LSB 的 INL 誤差。

要實現最佳的 DC 準確度,最簡單的解決方案是采用低失調 (<10μV) 自動調零放大器 (如 LTC1150 或 LTC2054)。對于較寬的輸出擺幅來說,可以在環路中納入諸如 LT1010 等第二個緩沖器放大器。LT1012 是一個良好的中間輸出放大器,以低功率 (11.4mW) 實現中等速度 (120μs 穩定時間) 和良好的準確度 (±25μV 失調)。

對于高速應用來說,一個良好的選擇是 LTC1468-2,該器件在 18 位時以 2μs 時間將 10V 階躍穩定在 ±1LSB 之內。請注意,±75μV 的最大失調將在 DAC 輸出端使 INL 劣化高達 ±0.9LSB。對于需要較高準確度的高速應用來說,放大器失調可以用數字電位器來消除。

要在高速且未采用消除失調的措施時實現最佳準確度,合成的放大器電路是一個良好的選擇。例如,LTC2054 用作積分器來消除放大器失調。在輸出轉換時,LTC6240 最大限度地降低積分器輸入的干擾,以避免擾亂低頻通路。請注意,跨 1kΩ 電阻器的任何 DC 電流都以失調電壓的形式出現,會引起 INL 誤差,因此 LTC6240 具有低輸入偏置電流很重要。LTC1360 提供寬的輸出擺幅。這樣產生的合成放大器以 16μV/√Hz 的噪聲密度在 8us 的時間實現穩定。

結論

盡管很多 DAC 架構都允許用戶實現 18 位分辨率和單調性,但是對于在 16 位時需要好于 ±15ppm 的準確度或 ±1LSB INL 的用戶來說,阻性梯形或 R-2R DAC 是最佳選擇。在電壓和電流輸出 R-2R DAC 之間進行選擇時,設計師應該意識到,每一種架構對電源、基準和輸出放大器都施加了不同的要求。選擇一個非緩沖型 DAC 并將該 DAC 與一個仔細選擇的放大器結合,可以最大限度地提高設計靈活性,并為給定應用提供最佳解決方案。

電子發燒友App

電子發燒友App

評論