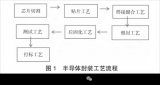

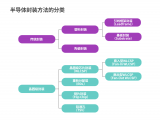

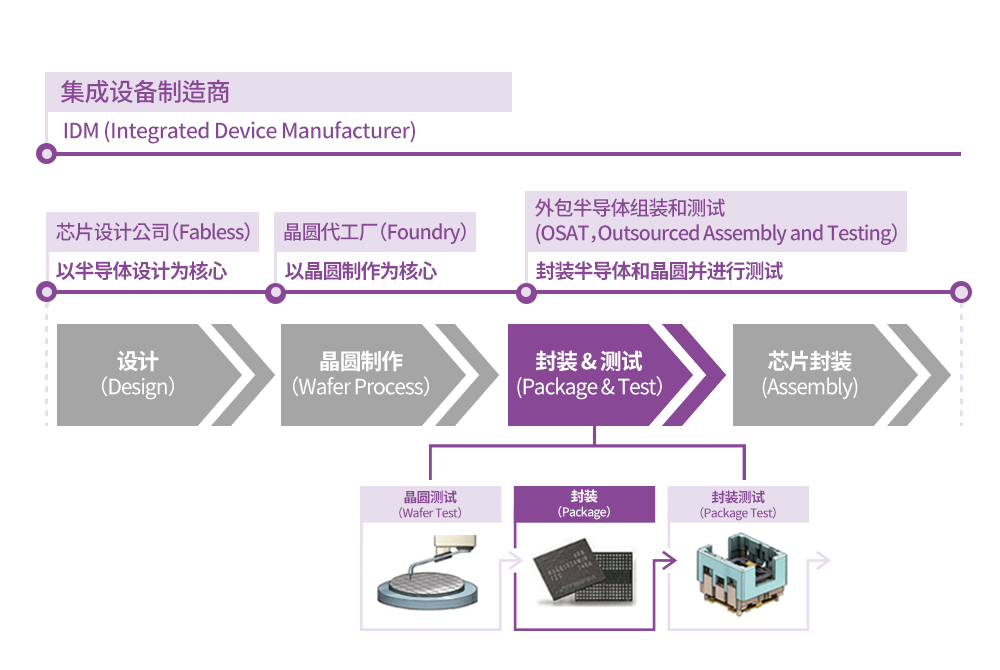

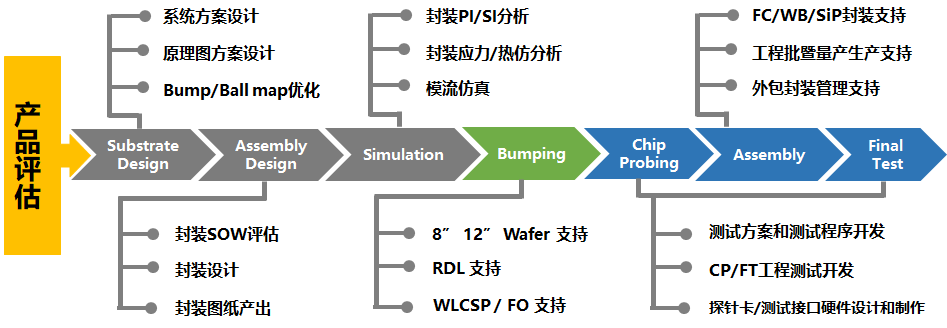

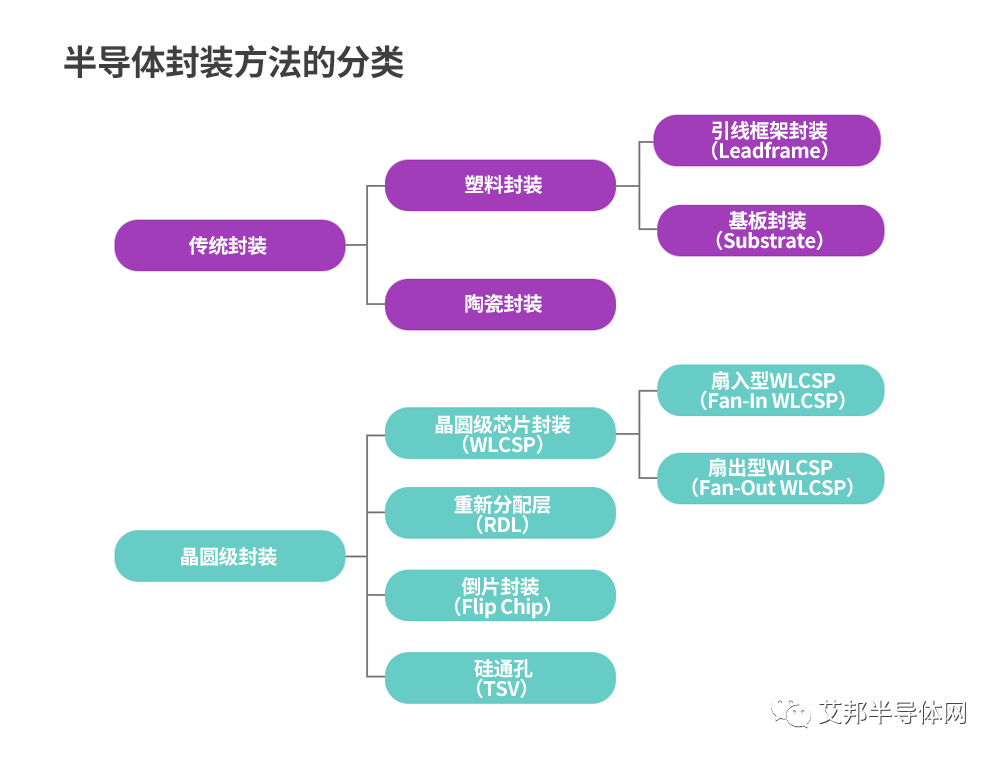

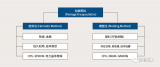

第一部分:半導體封裝概念

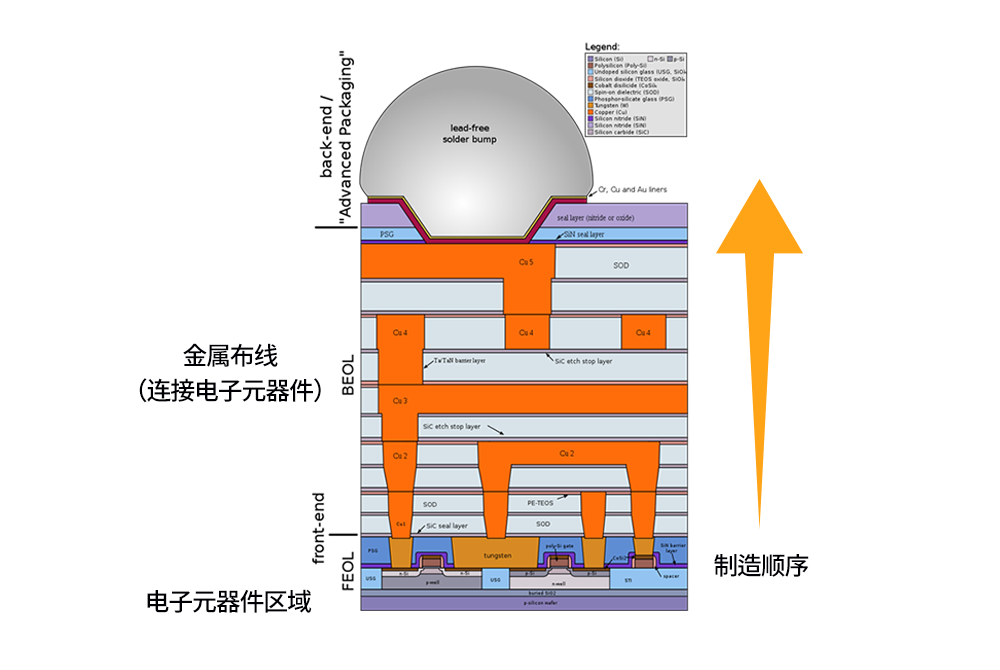

半導體芯片封裝是利用膜技術及細微加工技術,將芯片及其他元件在基板上布局、粘貼固定及連接,引出接線端子裝配成完整的集成電路系統,并確保整個系統綜合性能的工程。

第二部分:環境條件要求

雜質會對半導體的特性有著改變或破壞其性能的作用,所以在半導體器件生產過程中對一切雜質與生產環境都有著極其嚴格的控制要求,對雜質的控制涉及到多種類,如金屬離子會破壞半導體器件的導電性能、塵埃粒子破壞半導體器件的表面結構等等。因此半導體封裝工藝,必須要求在防靜電條件良好的無塵車間內進行。其廠房潔凈度要求根據不同的工藝環節從千級至十萬級不等。

第三部分:封裝工藝

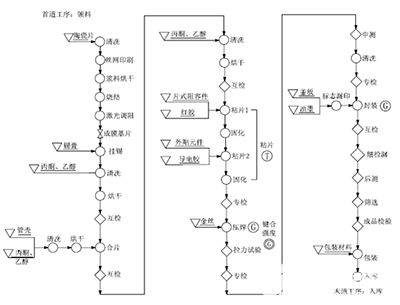

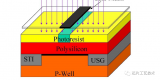

3.1成膜基片制備

陶瓷基片是電子封裝中絕緣特性、可靠性、機械強度、熱膨脹系數、熱導率、化學性能等關鍵參數中性能最為優異的基片形式。因而適用于航空航天、軍事工程、通信設備、汽車電子、石油電子等對電子元器件質量性能要求較高的領域。

智騰混合集成電路的基片陶瓷,選用日本京瓷公司的陶瓷原料作為供應商的基體材料,選用美國杜邦公司的導體漿料(金漿料)和電阻漿料作為印料。通過高精度的全自動化絲網漏印工藝,利用美國BTU的溫控燒結爐對成膜基片進行燒制。從而形成穩定可靠的以陶瓷為基材的無源網絡,完成成膜基片的制備。

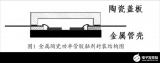

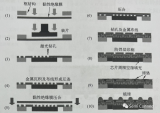

3.2成膜基片合片

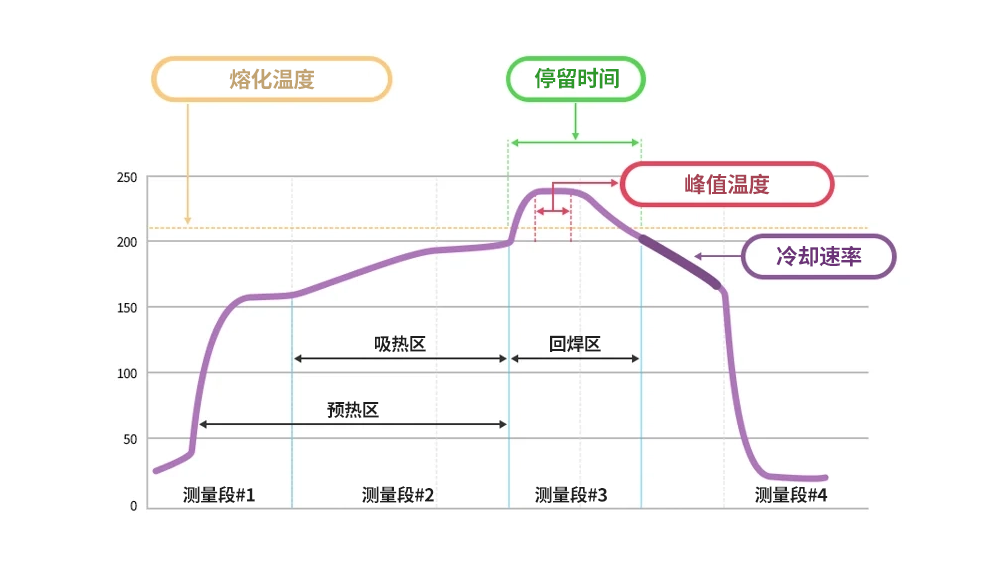

成膜基片同電路外管殼的合片工藝,是決定載體電路同芯片外管殼機械連接強度的關鍵工藝環節。將焊料錫膏通過高精度全自動化絲網漏印工藝將錫膏均勻的印刷在成膜基片的底面,清洗烘干后,經過共晶焊爐,利用金錫共晶焊將成膜基片同電路外觀可焊接成為一體。金錫合金的屈服強度很高,即使在250~260℃的溫度下,它的強度也能夠勝任氣密性的要求,保障電路后續在復雜工況下的長期穩定工作。

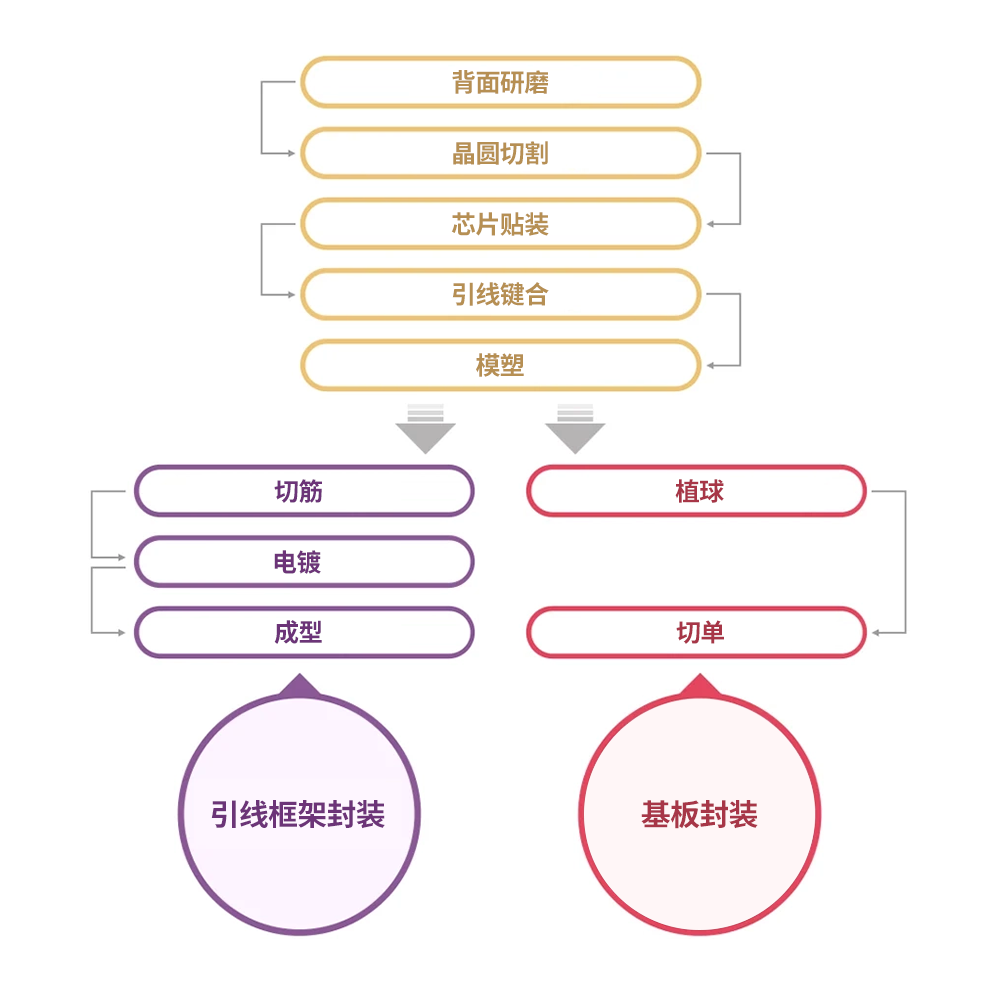

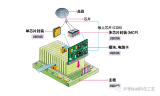

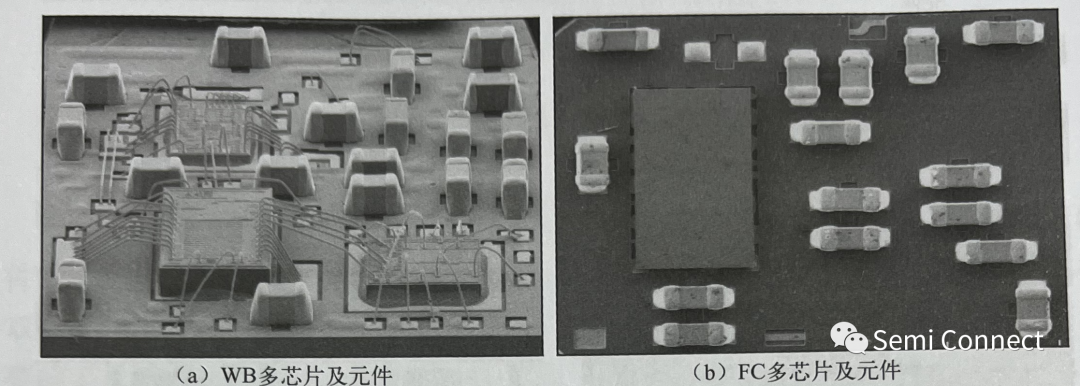

3.3全自動裸片貼裝

裸片(DIE)的貼裝過程被成為DIE BOND貼片技術,利用全自動DIE BOND設備,將裸片(DIE)和貼片阻容器件按照設計好的貼裝圖紙貼裝在合片后的無源網絡中。根據工況環境對集成電路內部貼裝溫度、應力大小、貼裝強度等技術條件的不同要求,通常智騰會主要采用共晶焊接法、樹脂粘合法和焊錫結合法三種工藝方式來實現。

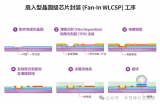

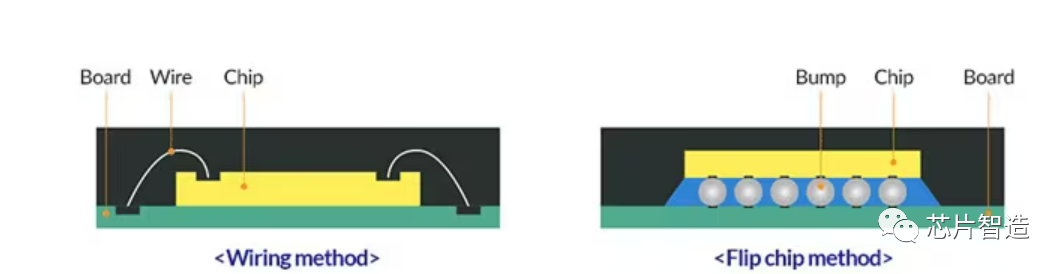

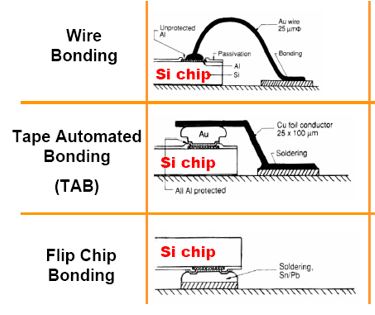

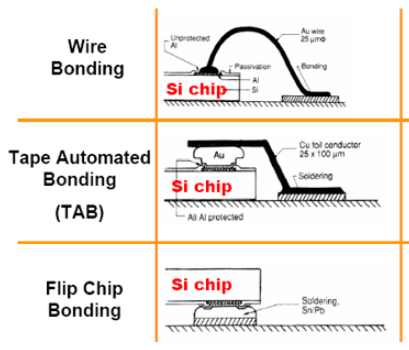

3.4邦定鍵合

Wire Bonding (壓焊,也稱為綁定,鍵合,絲焊)工藝,智騰是通過美國KNS的全自動鍵合設備,實現最小35um線間距,±2.5um@Sigma焊點精度的精度水平,完成單條導線的焊線時間小于23毫秒。使用金屬絲(金線、鋁線等),利用熱超聲能源,完成集成電路內部微電子器件及外管殼間互連接線的連接,即芯片與電路或引線框架之間的連接。

3.5氮氣封裝

封裝(Package)對于集成電路而言是至關重要的一個公益環節。它不只起著維護內部芯片和加強導熱性能等的作用,還是溝通集成電路內部世界與外部電路系統的橋梁。智騰的高等級集成電路,通常采用平行縫焊和激光焊的工藝,在99.99%\99.999%的高純氮氣環境下對集成電路進行氣密性封裝。在封裝后,利用真空檢漏儀、瑞士英福康的氦質譜檢漏儀、PIND顆粒碰撞噪聲檢測儀等設備對密封效果及密封潔凈度進行檢測。金屬或陶瓷氣密性封裝的可靠性遠高于普通的塑封封裝,因此非常適用于于航空航天、國防科技、通信工程、汽車電子、石油電子等領域。

3.6成品檢驗

封裝完畢的集成電路會根據使用環境的要求,借鑒GJB2438B-2017的國軍標標準,經過電氣功能測試、高溫老化測試、高低溫循環測試、耐鹽霧測試、濕熱測試、高溫振動測試、沖擊測試等相關試驗內容完成成品檢測,而后入庫,提供給用戶。

電子發燒友App

電子發燒友App

評論