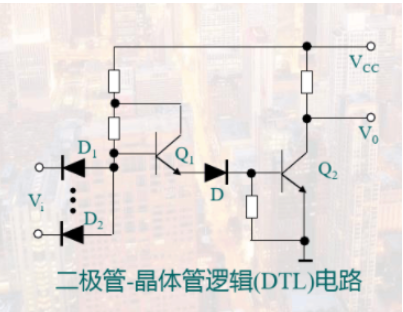

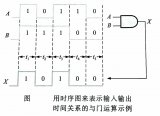

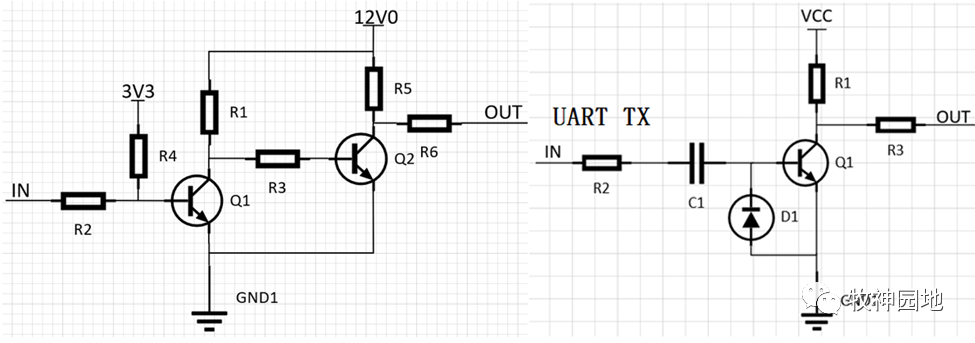

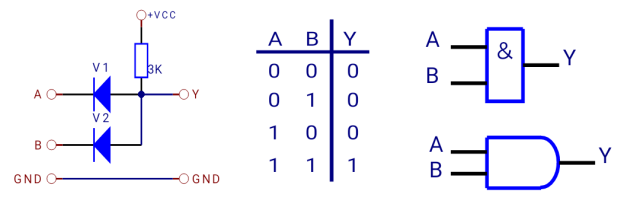

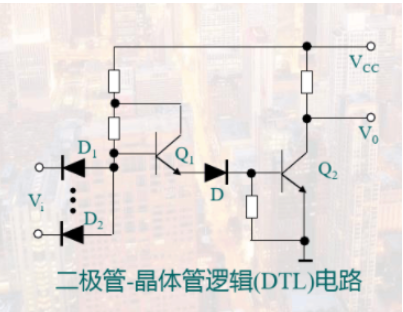

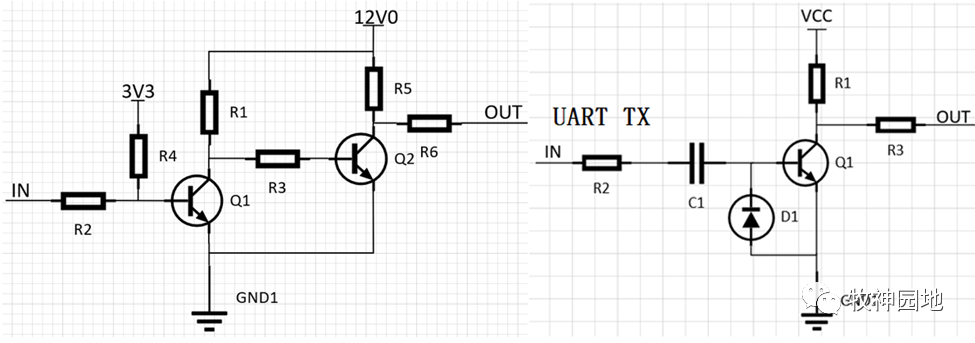

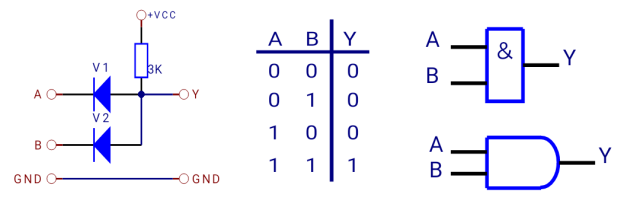

二極管-晶體管耦合邏輯電路(DTL),它是一種與非門電路。只要輸入信號為低電平,則輸出為高電平。

2024-03-15 17:39:02 158

158

大佬們,在通用定時器PWM輸出實現(xiàn)呼吸燈的實驗中,我在這個通道輸出極性選擇中選擇高電平有效,LED0為啥會一直亮?按理說應該是輸出低電平才會亮啊。

2024-03-07 06:47:45

CYT4B pwm 怎么反轉(zhuǎn)輸出信號極性,比如原先低于比較值為低電平,怎么改成高電平

2024-03-04 07:34:31

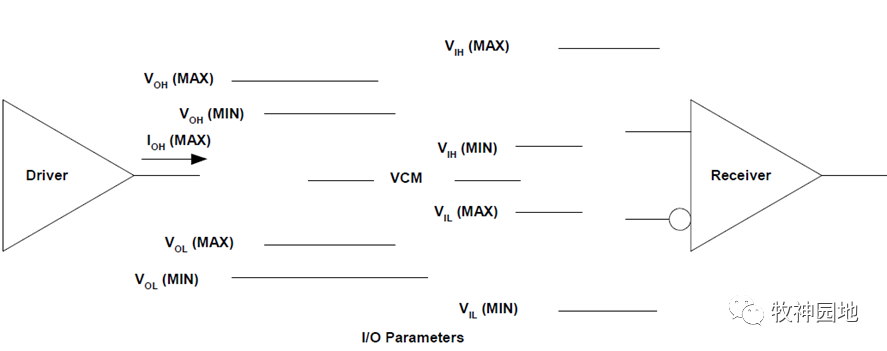

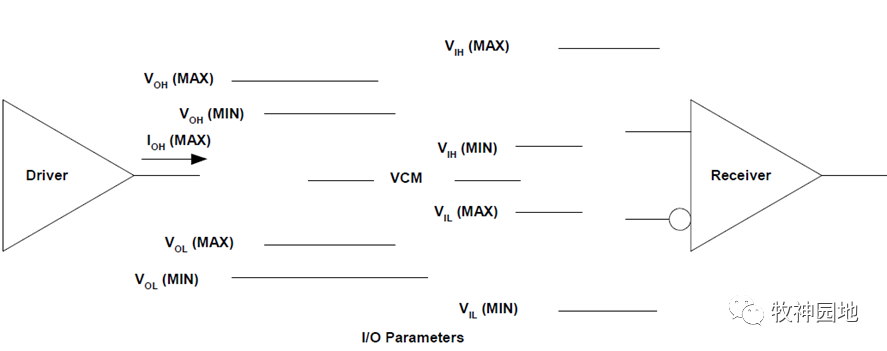

: 邏輯電平參數(shù)是描述輸入或輸出信號在邏輯門內(nèi)部的電壓范圍的指標。 VIL:輸入的低電平(Logic Low)電壓。TTL邏輯門規(guī)定,輸入低電平范圍為0V到0.8V。 VIH:輸入的高電平(Logic High)電壓。TTL邏輯門規(guī)定,輸入高電平范圍為2V到5V。 VOL:輸出的低電平電壓。TTL邏輯門

2024-02-22 11:25:25 238

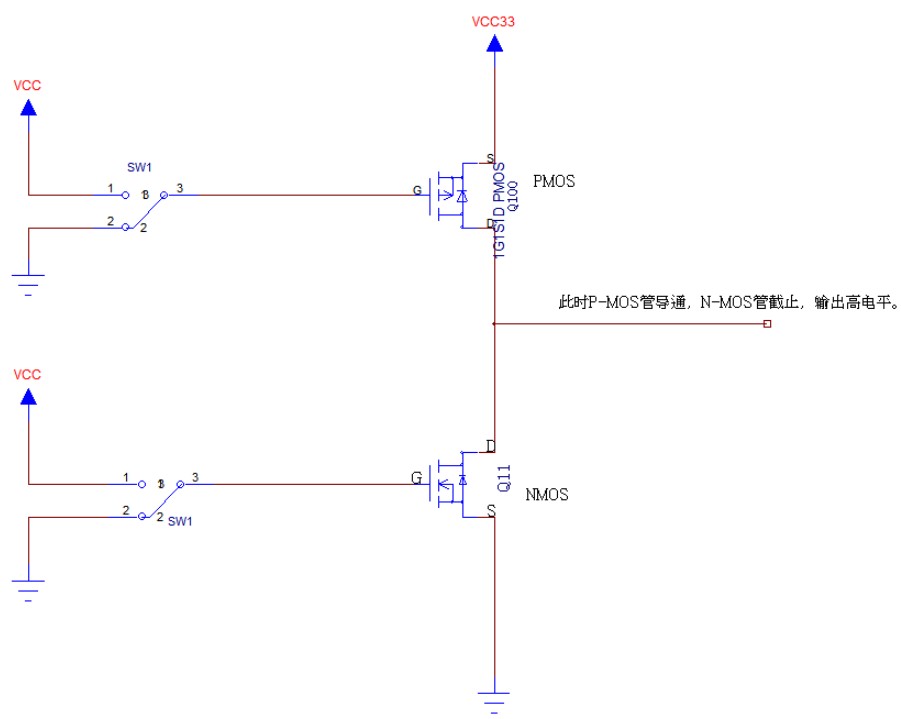

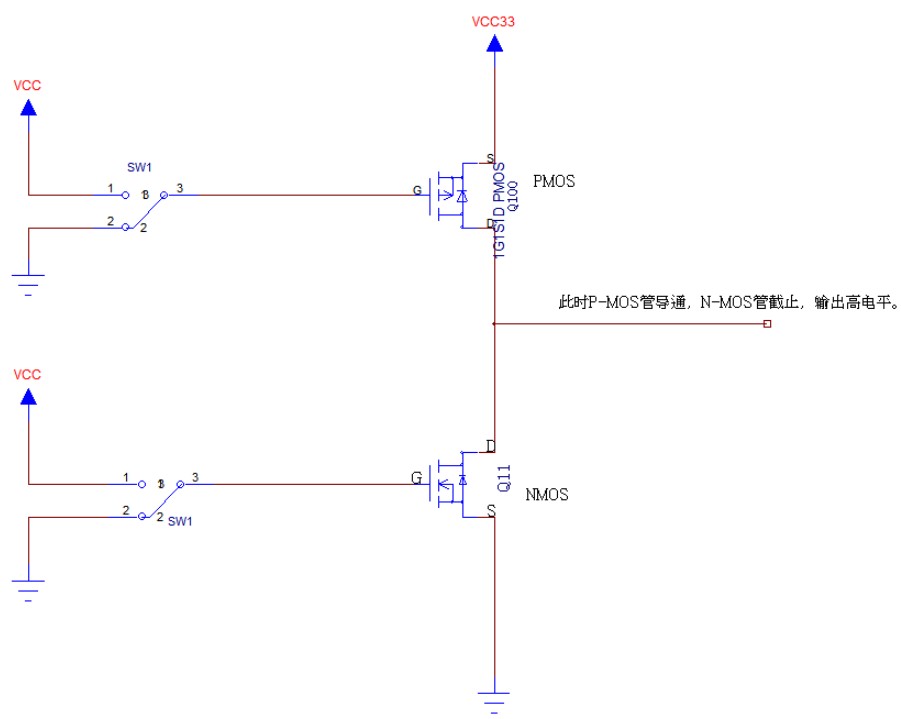

238 半導體)管道組成。在CMOS電路中,輸入信號的高和低電平取決于輸入信號的電壓和電路中的配置。 對于CMOS門電路來說,判斷輸出電平的關鍵是輸入電壓。在理想的情況下,當輸入電壓為高電平時,輸出為低電平;當輸入電壓為低電平時,輸出電平為高電平。這是因為CMOS電路的輸入管道是一個開關,當輸入電壓為高

2024-02-22 11:12:34 509

509 的CMOS電平一般分為邏輯高電平(High Level)和邏輯低電平(Low Level)。CMOS電平的取值一般在0V到Vcc之間,Vcc是CMOS電路供電電壓。邏輯高電平一般為Vcc,邏輯

2024-02-22 11:10:52 332

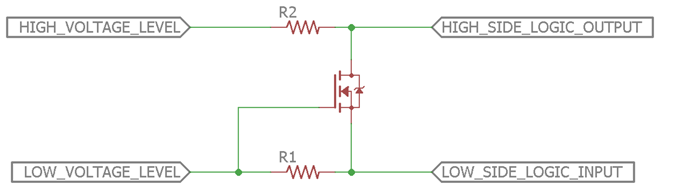

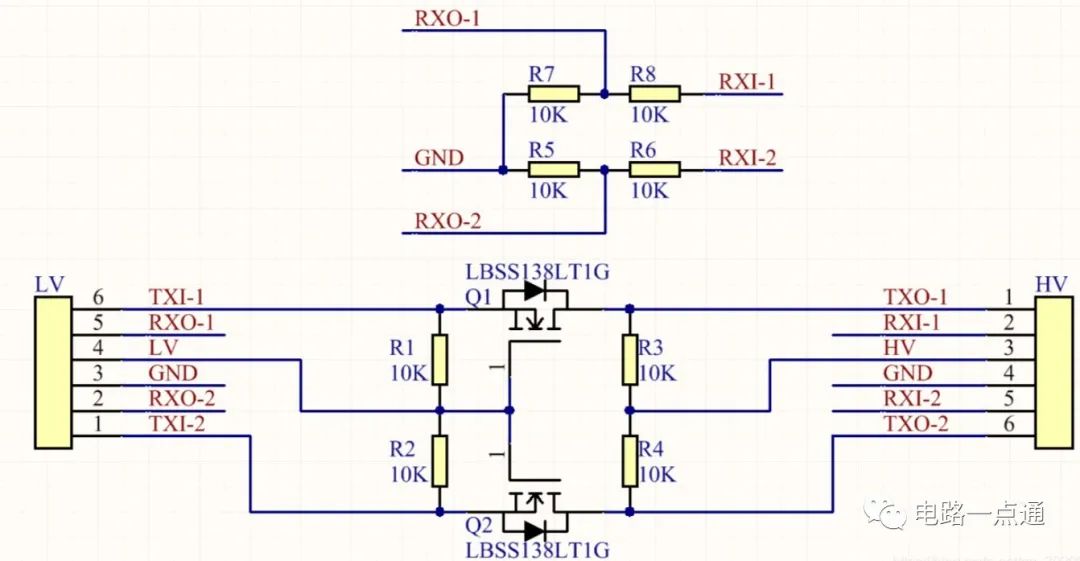

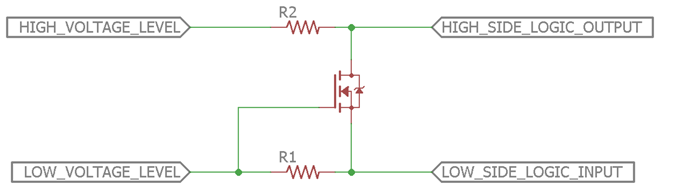

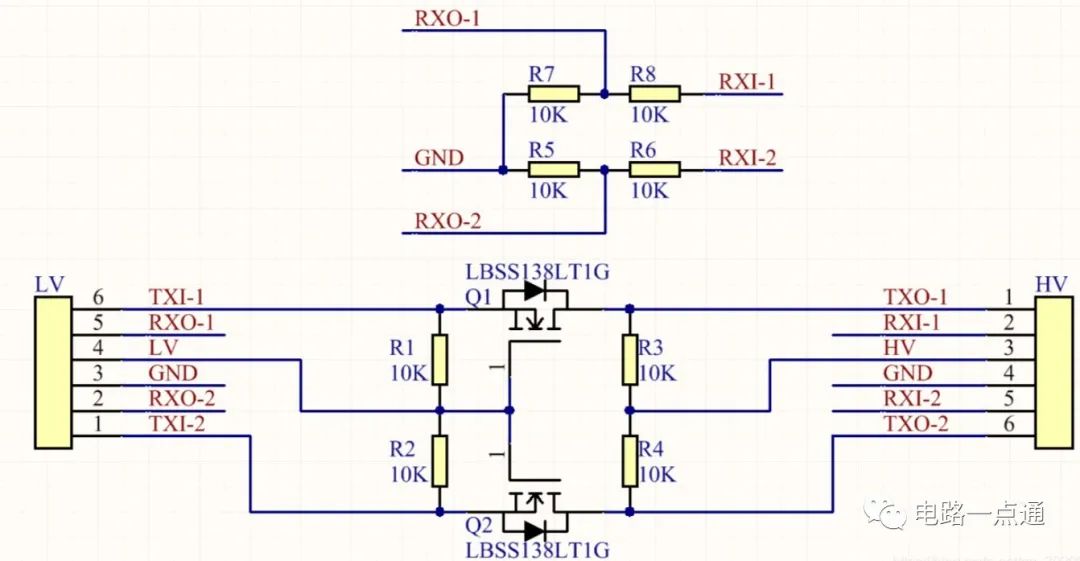

332 雙向邏輯電平轉(zhuǎn)換器是一種電子器件,用于在不同電壓邏輯電平之間進行轉(zhuǎn)換。它可以將一個邏輯電平轉(zhuǎn)換為另一個邏輯電平,從而確保在不同電壓環(huán)境下的設備之間能夠正常通信和協(xié)作。

2024-02-19 16:54:00 465

465

在推挽輸出模式下,一個晶體管用于提供高電平輸出,而另一個晶體管則用于提供低電平輸出。當內(nèi)部輸出為1電平時,上邊的晶體管(如MOS管)導通,同時下邊的晶體管截止,這時輸出高電平。

2024-02-06 09:27:10 637

637

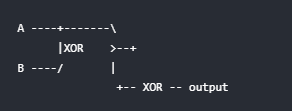

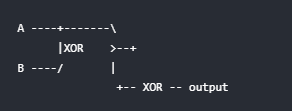

在這種實現(xiàn)中,當控制信號 B 為高電平時,異或門的輸出將反轉(zhuǎn)輸入信號 A 的邏輯電平。如果 A 是高電平,則輸出是低電平;如果 A 是低電平,則輸出是高電平。而當控制信號 B 為低電平時,異或門的輸出與輸入信號 A 保持一致。

2024-02-04 17:40:01 990

990

當控制信號處于高電平狀態(tài)時,輸入信號的邏輯電平將被反轉(zhuǎn)。例如,若輸入信號為高電平,則輸出信號為低電平;若輸入信號為低電平,則輸出信號為高電平。

2024-02-04 17:35:00 451

451 二進制中的兩個數(shù)字0和1稱為位(bit, 是二進制數(shù)字binary digit的縮寫)。在數(shù)字電路中,使用兩個不同的電平表示這兩個位。一般情況下,1 用高電平表示,0用低電平表示,這種邏輯體制稱為正邏輯。

2024-02-04 16:54:09 462

462

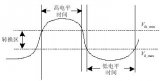

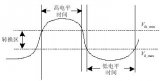

在大多數(shù)應用中,輸入波形往往不是固定的電平,而是在邏輯高電平和低電平之間頻繁變化的電壓波形。

2024-02-04 15:42:33 348

348

對于二輸入與非門運算執(zhí)行負或運算,只有當輸入A與B中有一個是低電平或者兩個都是低電平時,輸出就為高電平。

2024-02-04 14:44:08 522

522 觸發(fā)和下降沿觸發(fā)。 首先,我們需要了解一下什么是低電平觸發(fā)和下降沿觸發(fā)。低電平觸發(fā)是指當外部信號的電平低于某個特定閾值時,觸發(fā)中斷。而下降沿觸發(fā)是指當外部信號從高電平變?yōu)?b class="flag-6" style="color: red">低電平時,觸發(fā)中斷。這兩種觸發(fā)方式在實

2024-01-31 10:32:49 488

488 我使用 xmc7200 開發(fā) COOLDIM_PRG_BOARD。 我用PWM輸出正弦波,我用邏輯分析儀捕捉輸出的最后一位異常,最后一位應該是高電平,但長時間低電平,為什么?

2024-01-18 09:37:08

觸發(fā)器會觸發(fā)并改變輸出狀態(tài),這取決于JK觸發(fā)器的觸發(fā)方式。 在真實的電路中,JK觸發(fā)器的觸發(fā)方式是由實際的電壓電平決定的,通常有兩種模式,分別是懸空狀態(tài)為低電平和懸空狀態(tài)為高電平。在本文中,將詳細介紹這兩種觸發(fā)方式,并探討它

2024-01-15 13:35:53 446

446 AD7985芯片已設置為/CS模式(三線式且有繁忙指示)。

設置方法:TURBO管腳下拉,SDI上拉,SDO接10K的上拉。輸出給CNV時鐘(1.953Mhz);

問題現(xiàn)象:CNV時鐘保持高電平

2024-01-12 06:46:44

NE555電路中,觸摸2腳低電平有效有動作,觸摸6腳高電平有效有動作,觸摸電路中人體雜波信號是高電平還是低電平?

2024-01-10 13:03:22

電平轉(zhuǎn)換芯片可以在數(shù)字電路和模擬電路中使用。在數(shù)字電路中,它可以將不同的邏輯電平(例如TTL、CMOS、LVCMOS等)轉(zhuǎn)換為其他邏輯電平,以便實現(xiàn)電路之間的兼容性。在模擬電路中,它可以將不同的電壓范圍(例如±5V、0-10V等)轉(zhuǎn)換為其他電壓范圍,以便滿足不同電路的需求。

2024-01-09 13:08:56 567

567 CMOS是一種常見的邏輯門電路,它使用CMOS技術來實現(xiàn)數(shù)字邏輯功能。在CMOS電路中,輸入端接電阻后接地的情況下,一般情況下是低電平。 首先,讓我們先了解一下CMOS電路的基本原理。CMOS(互補

2024-01-09 11:25:51 653

653 我的目的是使得ADP2164的PGOOD管腳輸出高電平。

EN管腳使用示波器測得其為斜坡信號(上下峰均為4.1646V和4.076V)

VIN/TRK/SYNC/PVIN是4.9mV,RT

2024-01-08 08:16:25

正常使用情況下,LTC3331的ship引腳接高電平還是低電平?

2024-01-05 11:07:17

LTC6813-1,pin 49 DRIVE 引腳是一直輸出高電平?還是周期性的高/低電平?

我司在測試的過程中發(fā)現(xiàn),如果不與主MCU通信,DRIVE 輸出的 是1.88s的高電平后,隨即變成低電平

2024-01-03 07:26:44

無論怎么設置ADXL345_DATA_FORMAT 0x31寄存器的INT_INVERT中斷有效位,2個中斷腳都一直是低電平。

按datasheet上

INT_INVERT位值為0,設置中斷至高電平

2024-01-01 06:06:35

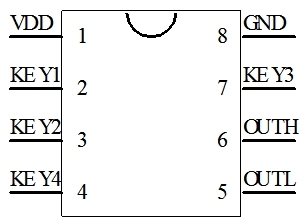

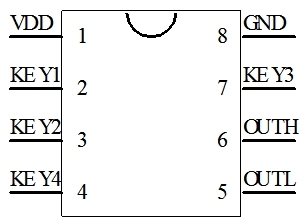

EH2730-A948長按開關機芯片 一.功能說明 四路按鍵(KEY1、KEY2、KEY3、KEY4)輸入控制,兩路信號同步輸出(可二選一)。上電狀態(tài)OUTL為高電平、OUTH為低電平。 KEY1

2023-12-23 09:15:22 158

158

數(shù)字隔離器芯片是一種將輸入信號隔離處理的器件。它的主要功能是在輸入和輸出之間提供電氣隔離,以防止傳遞噪聲、干擾和高電壓等問題。在數(shù)字隔離器芯片中,默認輸出低電平意味著在沒有輸入信號時,輸出信號

2023-12-22 13:47:36 373

373 本人初次使用AD7656。引腳接高電平是指接 VDD(12V)、AVCC(5V)、DVCC(5V)還是Vdrive(3.3V)?還是對于不同的引腳不一樣?我看到的各種文獻中接法不同。

另外硬件模式

2023-12-21 07:46:08

1AD9220在時鐘高電平下是不是一直采樣但不轉(zhuǎn)換,到低電平的時候才進行轉(zhuǎn)換并輸出?

2AD9220是不是在上升沿啟動采樣保持,到下一個上升沿開始輸出(我注意到手冊標注的輸出延遲是從上升沿開始

2023-12-21 06:39:57

你好,我用并口16,讀轉(zhuǎn)換數(shù)據(jù),負電源VSS直接接到AGND上。rest 低電平后,給CONVST ABC 高電平開始轉(zhuǎn)換,但是BUSY一直無高電平信號。

2023-12-18 06:36:21

您好,

當沒有數(shù)據(jù)輸入的時候,AD9780的 DCI數(shù)據(jù)時鐘輸入 管腳是否可以一直保持在高電平或者低電平?

謝謝!

2023-12-15 06:41:13

當DRVDD使用5V時,手冊上寫了,AD芯片的數(shù)字輸入輸出是5V的邏輯電平。當DRVDD使用3.3V時,AD芯片的數(shù)字輸入輸出是3.3V的邏輯電平。但是當DRVDD = 3.3 V時,不知道數(shù)字輸入

2023-12-14 07:09:38

有誰知道為什么AD7712的DRDY引腳一直是高電平嗎?它不是一上電就一直工作即使沒有輸入,它的DRDY引腳應該會周期性的變?yōu)?b class="flag-6" style="color: red">低電平啊?一直是高電平也就沒有數(shù)據(jù)輸出了。

2023-12-13 07:41:21

在調(diào)試AD7173-8的時候,首先發(fā)送了讀IP寄存器的命令,收到的回復是30D5,也即SPI通信無誤。然后將CS拉低,DIN保持高電平,但是一直等不到DOUT為低電平的狀態(tài)。看datasheet上說

2023-12-11 06:53:37

。請給位專家?guī)兔Ψ治鱿聠栴}所在。謝謝!上電后復位ADC電平 2us高電平,啟動轉(zhuǎn)換信號周期10us,convest低電平1us

2023-12-04 06:37:59

邏輯電平是數(shù)字電子系統(tǒng)中的關鍵概念之一。它決定了信號被認定為高電平還是低電平,并進一步影響著數(shù)字電路的正確操作。邏輯電平是用來表示數(shù)字信號狀態(tài)的電壓水平。在數(shù)字電子系統(tǒng)中,常用的邏輯電平有高電平

2023-11-24 08:20:20 1672

1672

請問ADA4930 PD管腳信號是高電平使芯片工作還是低電平使芯片工作

2023-11-20 08:21:38

Metal-Oxide-Semiconductor)。 TTL是一種基于晶體管的數(shù)字邏輯電平標準,使用5V電源供電,邏輯高電平(1)通常在2.4V以上,邏輯低電平(0)在0.4V以下。TTL邏輯電平的優(yōu)點是速度快、噪聲容忍度高,常見于早期的數(shù)字電路。然而,由于功耗較大,現(xiàn)在更常用的是

2023-11-17 14:16:06 648

648 什么是線與邏輯,要實現(xiàn)它,在硬件特性上有什么具體要求? 線與邏輯是一種基本的數(shù)字邏輯電路,用于實現(xiàn)布爾代數(shù)中的邏輯運算。在線與邏輯中,當所有輸入信號都是高電平時,輸出信號才為高電平;否則,輸出信號

2023-11-17 14:11:38 1389

1389 AD8468兩個輸入端都接地,輸出是高電平還是低電平

2023-11-15 06:11:57

讀取某一個上拉電平信號,它可能輸出是低電平,可能是高電平,可能是方波,并且這個方波不知道頻率何占空比,那么如何來通過程序來判斷呢?高電平和低電平都好說,利用HAL庫讀取即可,如下

2023-11-07 08:00:52 995

995

是基于信號保持在特定電平的條件觸發(fā)操作。通常,高電平觸發(fā)(信號為高電平時觸發(fā))和低電平觸發(fā)(信號為低電平時觸發(fā))是兩種常見的電平觸發(fā)方式。-操作持續(xù)時間:操作會持續(xù)進行,

2023-10-31 08:00:52 3407

3407

單片機IO默認低電平,怎么上電后測量是高電平

2023-10-20 07:32:25

本人是個新手剛剛接觸51單片機,怎么編程去計算51單片機某個io口的輸入高低電平時間,比如我從P1.0口輸入了一個方波信號,那么怎么通過單片機編程去檢測我這個方波高電平的時間(或者說長度),還有低電平的時間(或者說長度),這個檢測時間要精確到ms。

2023-10-20 07:11:25

在設置了PWM輸出端口,還能手動設置高電平或者低電平嗎

2023-10-15 12:25:46

信號為高電平,否則為低電平,邏輯符號為"|" 3、非門 (NOT) 有一路輸入信號一路輸出信號,當輸入為高電平時輸出為低電平,輸入為低電平時輸出為高電平,邏輯符號為“~” 4、與非門 (NAND) 有兩路輸入信號一路輸出信號,當且僅當兩路輸入信號

2023-10-12 14:35:03 4294

4294 RS觸發(fā)器是一種基本的數(shù)字邏輯電路,它由兩個輸入(R和S)和兩個輸出(Q和Q‘)組成。R和S分別代表復位(Reset)和置位(Set)信號。當R和S都是邏輯低電平時,RS觸發(fā)器會保持上一個狀態(tài)不變

2023-09-21 15:44:05 1873

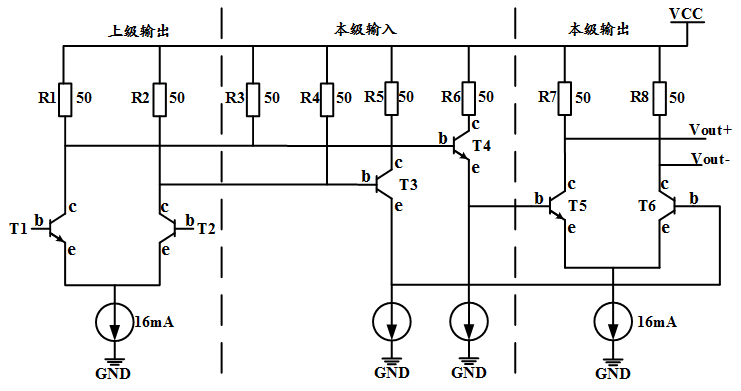

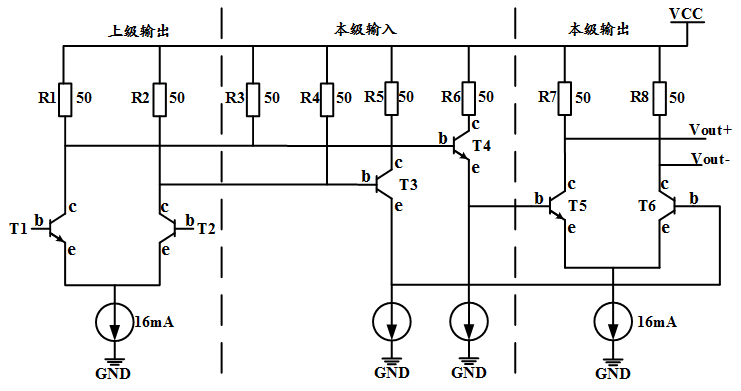

1873 CML電路如圖1 所示,輸入部分為一射隨器,假設T3管為N端,T4管為P端,當P大于N時即輸入為高電平,反之為低電平。由于輸入部分為射隨器,輸出端接收到高低電平的相位與輸入端一致,當接收為高電平

2023-09-20 15:32:41 510

510

進行邏輯計算或判斷,從而實現(xiàn)數(shù)字電路的功能。 在現(xiàn)代電子設備中,信號的邏輯狀態(tài)往往通過邏輯電平來表示。邏輯電平分為高電平和低電平兩種,通常高電平表示“1”,低電平表示“0”。“1”和“0”是數(shù)字電路中最基本的邏輯符號,

2023-09-19 17:16:11 692

692 端電平都為低電平時,輸出端就給出高電平;在其它情況下,輸出端均為低電平。TTL 與非門的功能可以表示為:Y = ? (A ∧ B)。其中,A 和 B 分別是兩個輸入電平,Y 是輸出電平,? 是取反符號,表示將輸入電平取反。 TTL NAND 門通常用于數(shù)字電路中,作為邏輯電路的基礎元件

2023-09-17 15:42:18 2006

2006 推挽輸出是低電平還是高電平? 推挽輸出器是一種常見的輸出方式。它由負和正三項組成,其中,負電平被連接到PNP晶體管,而正電平被連接到NPN晶體管。當給定輸入信號時,晶體管被開啟或關閉,電流流過負極

2023-08-31 10:26:31 1540

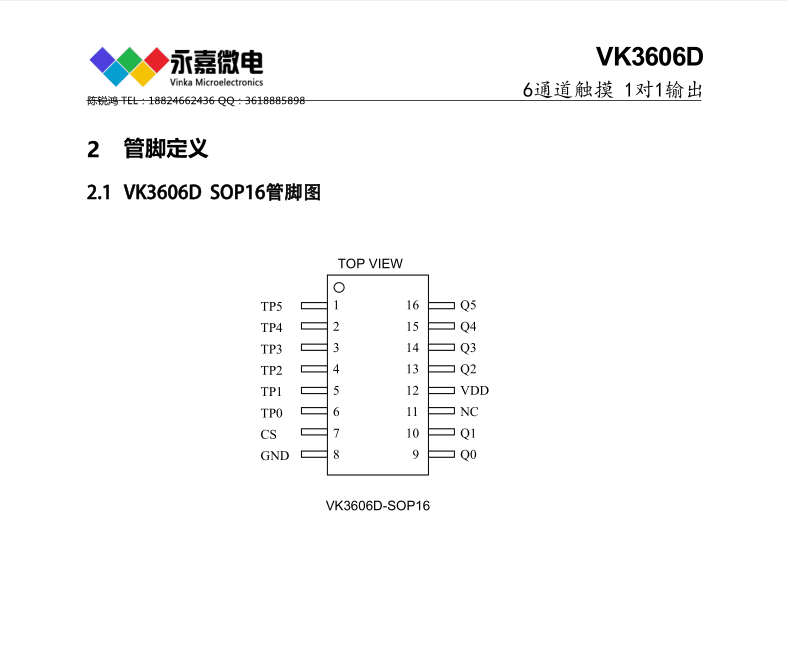

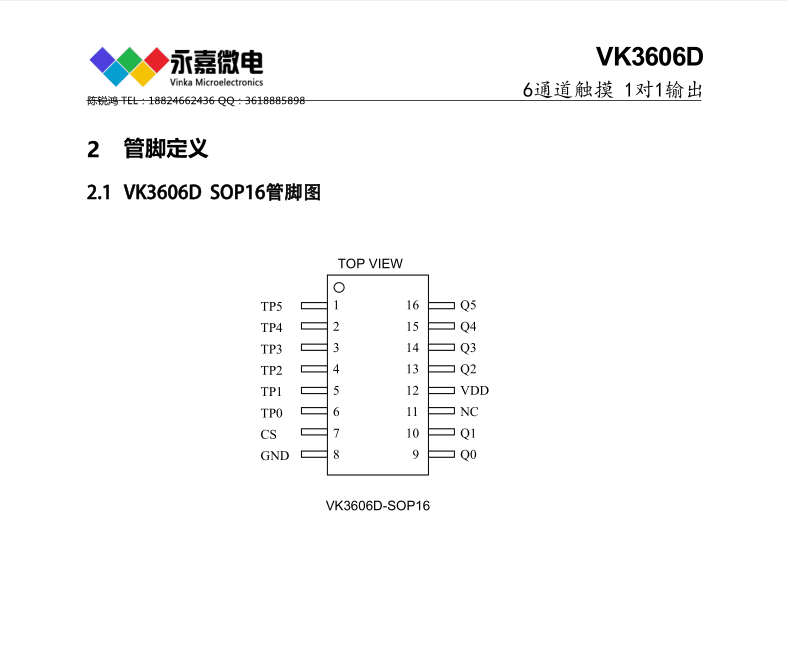

1540 ,僅需極少的外部組件便可實現(xiàn)觸摸按鍵的檢測。 提供了6路1對1直接輸出低電平有效。最長輸出時間10S。芯片內(nèi)部采用特殊的集成電路, 具有高電源電壓抑制比,可減少按鍵檢測錯誤的發(fā)生,此特性保證在不利環(huán)境條件的應用中芯 片仍具有很高的可靠性。 此觸摸芯片具有自動校準功能,

2023-08-29 10:21:28 256

256

FH154C6電子開關芯片手冊

功能說明:CMOS制造工藝,低工耗。驅(qū)動能力大,適用于各種電子開關。一路按鍵輸入控制,一路OUT低電平輸出。上電輸出低電平,短按開關后輸出高電平,再短按按鍵,0UT輸出低電平。再短按輸出高電平,如此循環(huán)。(注:輸出為延時0.5S緩慢開啟)

2023-07-03 15:30:43 2

2 差分邏輯電平之間的匹配,主要應用于時鐘和高速信號。

2023-06-25 14:56:13 1499

1499

單端邏輯電平的匹配是我們平時在硬件設計中最經(jīng)常碰到的,我們在《TTL&CMOS電平》章節(jié)中已經(jīng)對TTL和COMS電平的匹配設計做了一些分析,一般3.3V LVTTL和LVCMOS是可以直接相互驅(qū)動的。但是其它不同邏輯電平之間呢?舉個栗子,3.3V邏輯電平和1.8V邏輯電平之間呢?

2023-06-25 14:52:24 1380

1380

當LV連接器的TXI-1為3V3高電平信號(LV排針接3V3,HV排針接5V)時,Q1 mos管的柵極和源極之間的壓降為0V(TXI-1與LV排針之間的電壓),此時Q1 mos管不導通,TXO-1被R3電阻拉高,輸出5V高電平。

2023-06-25 09:10:43 569

569

芯片的電壓輸入引腳,建議放置一個100nf陶瓷電容濾波。 PIN.2: 芯片輸出使能引腳,高電平打開輸出,低電平關閉輸出。

2023-06-14 09:16:07 784

784

我在使用K312芯片測試Wakeup功能時,發(fā)現(xiàn)OutPut輸出的GPIO在進入待機后可以保持高電平輸出,但喚醒后會變?yōu)?b class="flag-6" style="color: red">低電平。

下面是我的設置:

1. 使用DS工具在Power組件中

2023-06-09 06:59:11

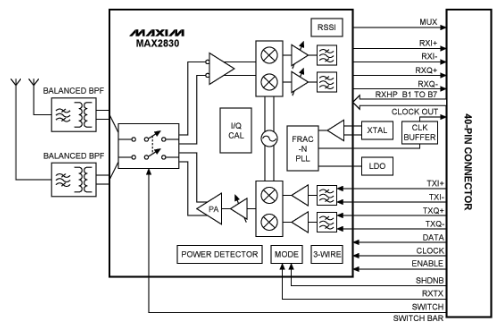

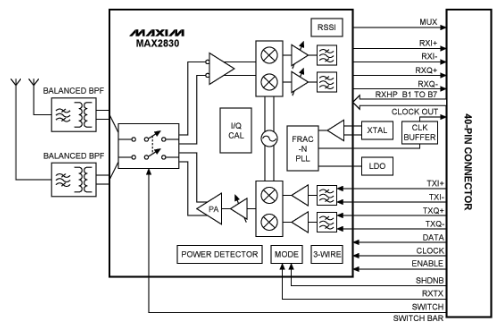

工作條件為:Vcc= 2.85V;V。.BAT = 3.3V; fRF = 2.437GHz; 根據(jù)工作模式設置RXTX和低電平有效SHDN; 低電平有效CS = 高電平; SCLK

2023-06-08 15:12:26 249

249

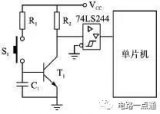

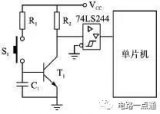

一般輸入信號最終會以開關形式輸入到單片機中,以工程經(jīng)驗來看,開關輸入的控制指令有效狀態(tài)采用低電平比采用高電平效果要好得多,如圖1如示。當按下開關S1時,發(fā)出的指令信號為低電平,而平時不按下開關S1時,輸出到單片機上的電平則為高電平。該方式具有較強的耐噪聲能力。

2023-05-30 09:06:44 1775

1775

高電平和低電平是數(shù)字電路中經(jīng)常會出現(xiàn)的專業(yè)名詞,它們所表面的意思就是電路上有和無,兩者之間沒有中間值,在不同的電路上,電壓的具體值也是各不相同的。如果用簡單的語言表達它們的意思就是開和關,平時

2023-05-26 10:17:30 24015

24015

在RT1011芯片上,我想復用配置GPIO_AD0作為普通的GPIO口輸出高電平或低電平。你能給我一個例子或一些參考文件嗎?

2023-05-05 06:56:06

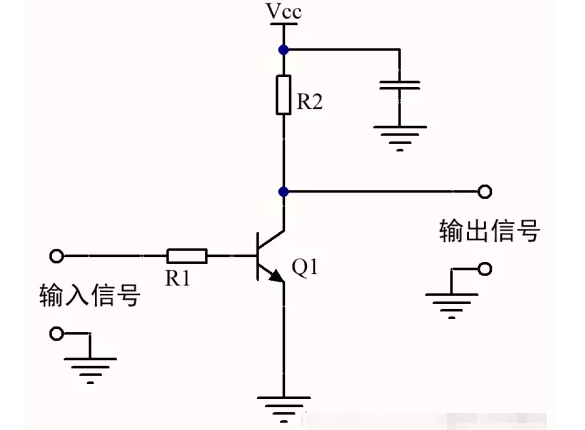

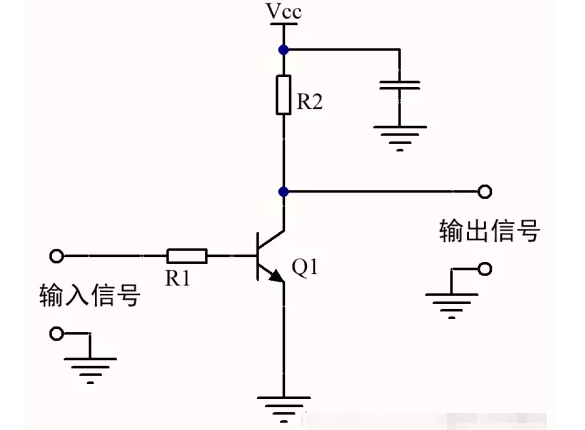

邏輯門可以用電阻、電容、二極管、三極管等分立原件構(gòu)成,成為分立元件門。也可以將門電路的所有器件及連接導線制作在同一塊半導體基片上,構(gòu)成集成邏輯門電路。簡單的邏輯門可由晶體管組成。這些晶體管的組合可以使代表兩種信號的高低電平在通過它們之后產(chǎn)生高電平或者低電平的信號。

2023-04-30 17:49:00 4912

4912 關于邏輯電路的幾個規(guī)定

①有關高電平,低電平的規(guī)定;

在邏輯電路中,電位的高低常用高電平,低電平來描述,單位也用“V”表示。實際的高電平和低電平都不是一個固定的數(shù)值,因此通常規(guī)定一個電平

2023-04-30 16:41:00 3484

3484

請問如下圖的74LS系列門電路如何判斷輸出端是高電平還是低電平?

2023-04-28 14:40:55

我想用LM324做比較器,在反向輸入端加一個4V的參考電壓,正向輸入端隨電平的變化而輸出高低電平,圖中A點是用來取樣電壓,由于是PNP三極管,當LM324輸出一個低電平時,由于低電平會使PNP導

2023-04-25 16:22:23

CMOS和TTL通過電阻接電源,要如何判斷接入高電平還是低電平?

2023-04-25 09:27:35

在數(shù)字電路的領域,常常把電壓簡化為電平,來描述邏輯狀態(tài)。比如TTL電平信號規(guī)定,+5V等價于邏輯“1”,也稱為高電平,0V等價于邏輯“0”,也就是低電平。數(shù)字電路里,只有0和1兩個狀態(tài)。其實從0V

2023-04-20 14:35:09 1739

1739

我需要將 LS1046A 的 RCW 配置為高電平有效 IRQ1 和 IRQ2 中斷。有人可以告訴我如何設置它們嗎?我對 LS1046A 還是很陌生。

2023-04-17 07:21:47

比較器的原理挺簡單,目的是比較兩個輸入端的電壓大小,若正輸入端的電壓為a,負輸入端的電壓為b,則當a>b時,輸出為高電平(邏輯1);當a<b時,輸出為低電平(邏輯0)。

2023-04-12 16:09:55 3372

3372 SPI的CPOL,表示當SCLK空閑idle的時候,其電平的值是低電平0還是高電平1:CPOL=0,時鐘空閑idle時候的電平是低電平,所以當SCLK有效的時候,就是高電平,就是所謂的active-high。

2023-04-10 16:21:34 4807

4807 具有看門狗和手動復位功能的高電平有效、低電平有效、汽車電壓監(jiān)控器(復位 IC)

2023-04-06 10:39:19

我可能遇到了 spi 驅(qū)動程序的問題。我正在嘗試讀取和寫入 eeprom,但是當讀取過程開始時,芯片選擇不會保持低電平,而是返回高電平并在每個傳輸字節(jié)后取消選擇芯片。結(jié)果,eeprom 停止讀取

2023-04-06 06:50:40

單片機的輸出信號電平可以是高電平(通常為Vcc電壓,即正電源電壓)或低電平(通常為GND電壓,即接地電壓),具體取決于單片機的設計以及輸出端口的連接方式。

2023-04-01 15:55:36 2379

2379 如何使用emios的GPIO模式輸出S32K312芯片PTA24引腳的高電平或低電平

2023-03-31 06:40:06

請教一下大神在單片機中直通方式下為啥csda接低電平有效呢?

2023-03-28 11:25:32

復位有效電平:低電平有效 3.0V 低功耗的電壓檢測器

2023-03-27 11:54:40

我想將一個 GPIO 引腳(即 A17)設置為高電平和低電平。如果一個條件為真,我將 A17 設置為高,否則 A17 為低。我為 A17 配置了輸出方向的時鐘。我嘗試

2023-03-27 07:05:14

十六進制非反相高電平到低電平移位器

2023-03-24 14:58:43

復位有效電平:低電平有效 1.5V 低功耗的電壓檢測器

2023-03-24 13:43:20

ARM 手冊中找不到關于支持類型限制的任何限制。它專門討論了可能是高電平有效或低電平有效的電平敏感中斷。所以我不知道這個限制是從哪里來的。誰能給我指出一份解釋其起源的文件?繼續(xù),我注意到在

2023-03-24 06:45:09

電子發(fā)燒友App

電子發(fā)燒友App

評論