STM8S003F3能否輸出2路可調(diào)的相位相差180度的獨(dú)立PWM波形?

兩路pwm波形有死區(qū)時(shí)間可控制

2024-03-22 06:34:43

,現(xiàn)貨庫存CYV15G0203TB-BGXCCYV15G0101DXB-BBXCCYV15G0204TRB-BGXCCYV15G0401DXB-BGXCCYV15G0104TRB-BGXC如需其他型號(hào),歡迎點(diǎn)擊右側(cè)客服咨詢!!!

2024-02-26 10:08:43

(如i2c1)。因?yàn)槔讨械?b class="flag-6" style="color: red">時(shí)鐘初始化,只有機(jī)器定時(shí)器1是分到group1和core1的,所以不太確定。

3-只有共享內(nèi)存(linker文件中已配好16k)是雙核都能訪問的,且該ram區(qū)只能

2024-02-06 21:14:30

我有[i] KIT _A2G_[i] TC377 _[i] 5V _TRB,如何使用 HighTec IDE 和板載 DAS 來 下載和調(diào)試?

2024-01-26 07:47:50

使用兩片LTM4630可以實(shí)現(xiàn)三路并聯(lián)(電壓為1.0),另一路獨(dú)立輸出嗎(電壓為1.2V).

2024-01-04 07:00:37

FIFO方案,則無法正常工作。

該問題的一種解決方案是讓雙通道轉(zhuǎn)換器使用多點(diǎn)鏈路JESD204B接口,其中每個(gè)轉(zhuǎn)換器都使用各自獨(dú)立的串行鏈路輸出。然后便可針對(duì)每個(gè)ADC使用非相干時(shí)鐘,且每個(gè)串行鏈路

2024-01-03 06:35:04

電子發(fā)燒友網(wǎng)站提供《具有串行I2C接口的實(shí)時(shí)時(shí)鐘1339 數(shù)據(jù)表.pdf》資料免費(fèi)下載

2023-12-21 10:45:31 0

0 請(qǐng)問,AD9788芯片,能否兩路DA輸出完全獨(dú)立的兩路信號(hào)分別去混頻,而不是分IQ輸出進(jìn)解調(diào)器?謝謝

2023-12-18 06:49:29

您好:

使用AD9690時(shí),想知道數(shù)據(jù)具體是怎樣映射到串行鏈路上的。

我打算不使用AD9690內(nèi)置的DDC,直接將采樣后的一路數(shù)據(jù)通過串行鏈路傳遞到FPGA;在手冊(cè)中看到一幅圖描述著,一個(gè)采樣點(diǎn)的高

2023-12-12 08:22:45

請(qǐng)問,要搭一個(gè)傳輸鏈路,鏈路中的ADC和DAC的參數(shù),比如:采樣率和分辨率一定要一樣嗎?

中頻模擬信號(hào),先模數(shù)轉(zhuǎn)換數(shù)字化進(jìn)行傳輸,之后需要數(shù)模轉(zhuǎn)換,前后的ADC和DAC采樣率和位數(shù)是否要完全相等?完全符合指標(biāo)的器件不太好找。

2023-12-12 06:21:04

稱48位或48bit LVDS接口。

單路和雙路:?jiǎn)?b class="flag-6" style="color: red">路就是只有一路 R、G、B 三色和HS、VS、DE控制信號(hào); 雙路就是有兩路 R、G、B 三色和HS、VS、DE控制信號(hào)。

經(jīng)常碰到什么單6,雙6

2023-12-11 13:21:58

假設(shè)我有4個(gè)AD5422采用菊花鏈方式連接,當(dāng)前狀態(tài)輸出電流都為10mA,現(xiàn)在想改變第3個(gè)的電流輸出為5mA,不改變其他路的輸出電流值。

問題1:那前24個(gè)時(shí)鐘(即操作第4個(gè)AD5422的時(shí)鐘

2023-12-11 07:56:50

描述 MAX9275/MAX9279是3.12Gbps千兆位多媒體串行鏈路(GMSL)串行器,具有并行LVCMOS輸入和CML串行輸出,可編程用于50ω同軸電纜或100ω屏蔽雙絞線(STP

2023-12-07 10:30:47

使用內(nèi)部PLL,輸入?yún)⒖碱l率為100MHz。在采樣率時(shí)鐘設(shè)置為1GHz時(shí),DAC的JESD204B鏈路能建立,但是當(dāng)頻率改為1.5GHz時(shí),SYNC一直為低。其他相關(guān)寄存器都已經(jīng)修改,serdes

2023-12-05 08:17:30

我理解這個(gè)D觸發(fā)正常運(yùn)轉(zhuǎn)要滿足四個(gè)約束,第一個(gè)是建立時(shí)間,第二個(gè)是保持時(shí)間,第三個(gè)是對(duì)于最后一個(gè)傳輸門的關(guān)斷時(shí)間的控制,第四個(gè)是[時(shí)鐘周期]() 約束。

2023-12-04 15:44:02 352

352

各音頻的時(shí)鐘不相同,因此用4個(gè)ASRC去進(jìn)行同步,而SPDIF、ADC與I2S0共用一路ASRC。用PCG產(chǎn)生輸出給,AD/DA的主時(shí)鐘,SPORT 0-1,6-7的FS,CLK。基本上設(shè)計(jì)是這樣

2023-11-30 06:09:13

關(guān)于AD8221

1)熱偶方式為何要用單端偏置?可否也用雙端平衡偏置電阻

2)8221的差分輸入信號(hào)是否必須與8221共地?還是共不共都行?

歡迎討論

2023-11-27 07:45:59

的答案:

(1)總的建立時(shí)間就等于兩級(jí)運(yùn)放的建立時(shí)間之和,即90 ns + 90 ns =180 ns

(2)總的建立時(shí)間還是90 ns

(3)認(rèn)為兩級(jí)運(yùn)放相互獨(dú)立,總的建立時(shí)間等于兩級(jí)運(yùn)放建立時(shí)

2023-11-27 06:54:56

華創(chuàng)翼聯(lián)HC-G30是一款使用 Wi-Fi 6 協(xié)議的便攜式路由器。采用 MT7981B 主頻1.3GHz 雙核處理器,支持160MHz, 無線速率和信號(hào)強(qiáng)度都有卓越的提升。它可以滿足家庭多設(shè)備連接

2023-11-23 15:38:45

。

時(shí)鐘輸出蜂鳴器輸出控制電路的框圖如圖13-1所示。

最大輸出頻率

功能引腳

可以輸出兩路方波CLKBUZ0與CLKBUZ1

CLKBUZ0可選為P31、 P140。

CLKBUZ1可選為P15

2023-10-25 11:20:01

C語言或Matlab如何實(shí)現(xiàn)FF鏈路調(diào)度器仿真

2023-10-18 06:12:23

僅當(dāng)存在待發(fā)送數(shù)據(jù)時(shí)串行時(shí)鐘波特發(fā)生器才產(chǎn)生對(duì)應(yīng)數(shù)據(jù)位模式的時(shí)鐘脈沖嗎?如果緩沖區(qū)沒數(shù)據(jù),串行時(shí)鐘就一直空閑嗎?

2023-10-17 08:20:06

C語言或matlab如何實(shí)現(xiàn)ff鏈路調(diào)速器仿真

2023-10-17 07:34:56

STM32的獨(dú)立看門狗用的時(shí)鐘是內(nèi)部時(shí)鐘還是外部時(shí)鐘呢

2023-10-15 11:58:05

1. 產(chǎn)品簡(jiǎn)介

USR-G808 是一款雙 4G 無線工業(yè)路由器,提供了一種用戶通過 WIFI 或是網(wǎng)口接入4G 網(wǎng)絡(luò)的解決方案。產(chǎn)品采用商業(yè)級(jí)高性能嵌入式 CPU,工作頻率高達(dá) 580MHz

2023-09-25 07:18:54

很多應(yīng)用場(chǎng)合需要檢測(cè)系統(tǒng)時(shí)鐘是否在正常范圍內(nèi),以保證MCU能正常工作,CLASS B功能安全實(shí)現(xiàn)系統(tǒng)時(shí)鐘自檢的方法是采用兩個(gè)獨(dú)立時(shí)鐘源交叉檢查來進(jìn)行測(cè)量

2023-09-14 17:30:49 945

945

耗電與頻率成正比最低為1.5μA。如果有32.768kHz的振蕩器連接到LSE精度可達(dá)0.5% 復(fù)位和從停止/待機(jī)模式退出后MSI將作為默認(rèn)的系統(tǒng)時(shí)鐘其建立時(shí)間的最大值為2us。 低速內(nèi)部振蕩器

2023-09-12 08:25:02

功能

?60 GHz V波段收發(fā)器,可實(shí)現(xiàn)高達(dá)

480 Mbit/s

?集成全射頻收發(fā)器和天線的緊湊型解決方案,在半雙工模式下運(yùn)行

?44 dB典型的總鏈路預(yù)算,高達(dá)6 cm的自由空間傳播損耗

2023-09-07 06:49:02

信號(hào)經(jīng)過傳輸線到達(dá)接收端之后,就牽涉到建立時(shí)間和保持時(shí)間這兩個(gè)時(shí)序參數(shù),它們表征了時(shí)鐘邊沿觸發(fā)前后數(shù)據(jù)需要在鎖存器的輸入持續(xù)時(shí)間,是接收器本身的特性。簡(jiǎn)而言之,時(shí)鐘邊沿觸發(fā)前,要求數(shù)據(jù)必須存在一段時(shí)間,這就是器件需要的建立時(shí)間;

2023-09-04 15:16:19 391

391

應(yīng)用:此示例代碼使用 M030G I2C 讀取 NCT7712Y 熱感應(yīng)器。

BSP 版本: M030G_Series_BSP_CMSIS_V3.02.000

硬件:NuMaker-M030GTD

2023-08-29 08:05:00

產(chǎn)品介紹PXIe7301雙路萬兆網(wǎng)卡具有局域網(wǎng)性能加速、網(wǎng)絡(luò)安全、網(wǎng)絡(luò)融合、網(wǎng)絡(luò)虛擬化、數(shù)據(jù)中心橋接等多項(xiàng)功能,通訊帶寬為雙口10Gbps,芯片的邏輯門數(shù)量達(dá)到一千八百萬,片上SRAM容量達(dá)到

2023-08-22 11:53:18

TTM Technologies 的 XMC0204P2-30G 是一款定向耦合器,頻率為 2.3 至 4 GHz,耦合 30 dB,耦合變化 ±1.5 dB,頻率靈敏度 ±0.25 dB,方向性

2023-08-16 09:49:04

安路CPLD可否提供內(nèi)部時(shí)鐘

2023-08-11 09:14:56

使用,可通過經(jīng)濟(jì)高效的 50Ω 單端同軸電纜或 100Ω 差分屏蔽雙絞線 (STP) 電纜提供單通道或雙通道高速串行流。它對(duì) OpenLDI 輸入進(jìn)行串行化處理,支持

2023-08-08 14:22:50

74HCT165是符合JEDEC標(biāo)準(zhǔn)7A的高速Si柵極CMOS器件。它們與低功率肖特基TTL(LSTL)引腳兼容。

74HCT165是8位并行加載或串行移位寄存器,具有可從最后一級(jí)獲得的互補(bǔ)串行輸出

2023-08-04 17:39:53

RJK0204DPA 數(shù)據(jù)表

2023-07-14 10:20:37 0

0 HITK0204MP 數(shù)據(jù)表

2023-07-14 09:46:50 0

0 HITJ0204MP 數(shù)據(jù)表

2023-07-14 09:45:24 0

0 RQK0204TGDQA 數(shù)據(jù)表

2023-07-13 19:10:10 0

0 RQJ0204XGDQA 數(shù)據(jù)表

2023-07-13 19:07:18 0

0 MAX9209/MAX9213將21位的LVTTL/LVCMOS并行輸入數(shù)據(jù)串行化為三路LVDS輸出。第四路LVDS輸出為并行速率時(shí)鐘,為解串器提供時(shí)鐘。MAX9209/MAX9213具有可編程直流

2023-07-11 10:25:35

。MAX9217與MAX9218解串器組成一個(gè)完整的數(shù)字視頻串行鏈路。可通過阻抗受控的PCB走線或雙絞線實(shí)現(xiàn)互連。專用數(shù)據(jù)編碼降低EMI并提供DC平衡。DC平衡允許使用

2023-07-11 10:14:49

。MAX9247與MAX9248/MAX9250解串器配合使用,組成一個(gè)完整的數(shù)字視頻串行鏈路。可通過阻抗受控的PCB走線或雙絞線實(shí)現(xiàn)互連。專用數(shù)據(jù)編碼降低EMI并提供

2023-07-11 10:08:09

MAX9257A串行器與MAX9258A解串器配對(duì)形成完整的數(shù)字視頻串行鏈路。MAX9257A/MAX9258A具有可編程并行數(shù)據(jù)寬度、并行時(shí)鐘頻率范圍、擴(kuò)頻和預(yù)加重功能。在上電時(shí),集成控制通道會(huì)在

2023-07-11 09:24:33

MAX9257A串行器與MAX9258A解串器配對(duì)形成完整的數(shù)字視頻串行鏈路。MAX9257A/MAX9258A具有可編程并行數(shù)據(jù)寬度、并行時(shí)鐘頻率范圍、擴(kuò)頻和預(yù)加重功能。在上電時(shí),集成

2023-07-11 09:22:05

??本文主要介紹了建立時(shí)間和保持時(shí)間。

2023-06-21 14:38:26 1079

1079

建立時(shí)間(setup time)和保持時(shí)間(hold time)是時(shí)序分析中最重要的概念之一,深入理解建立時(shí)間和保持時(shí)間是進(jìn)行時(shí)序分析的基礎(chǔ)。

2023-06-21 10:44:01 881

881

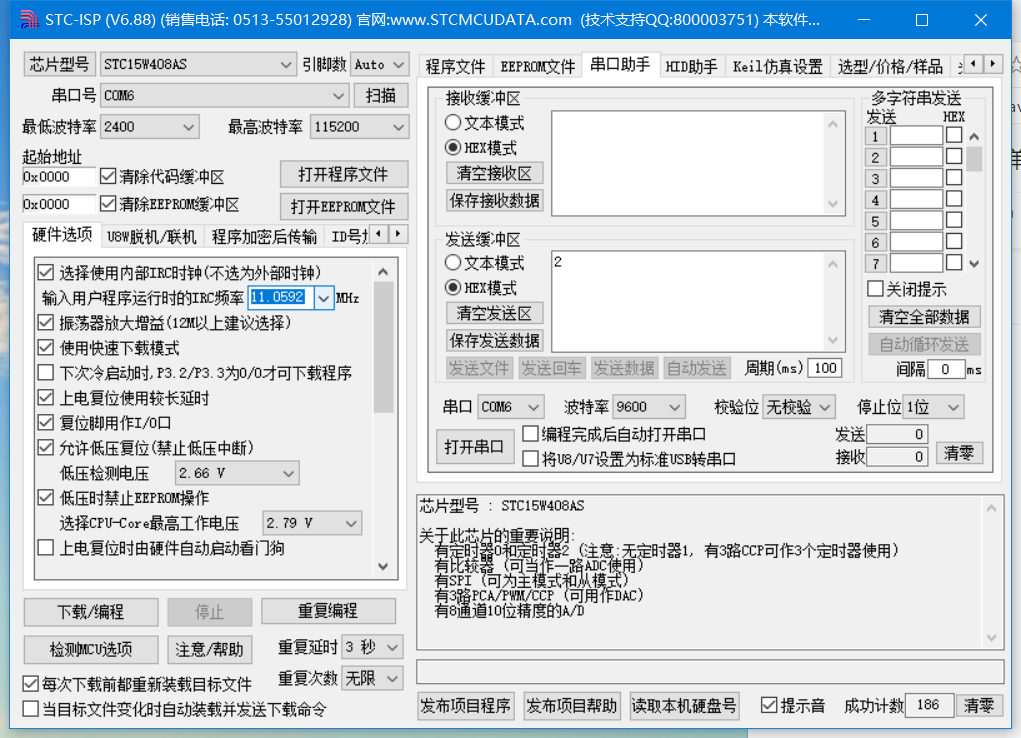

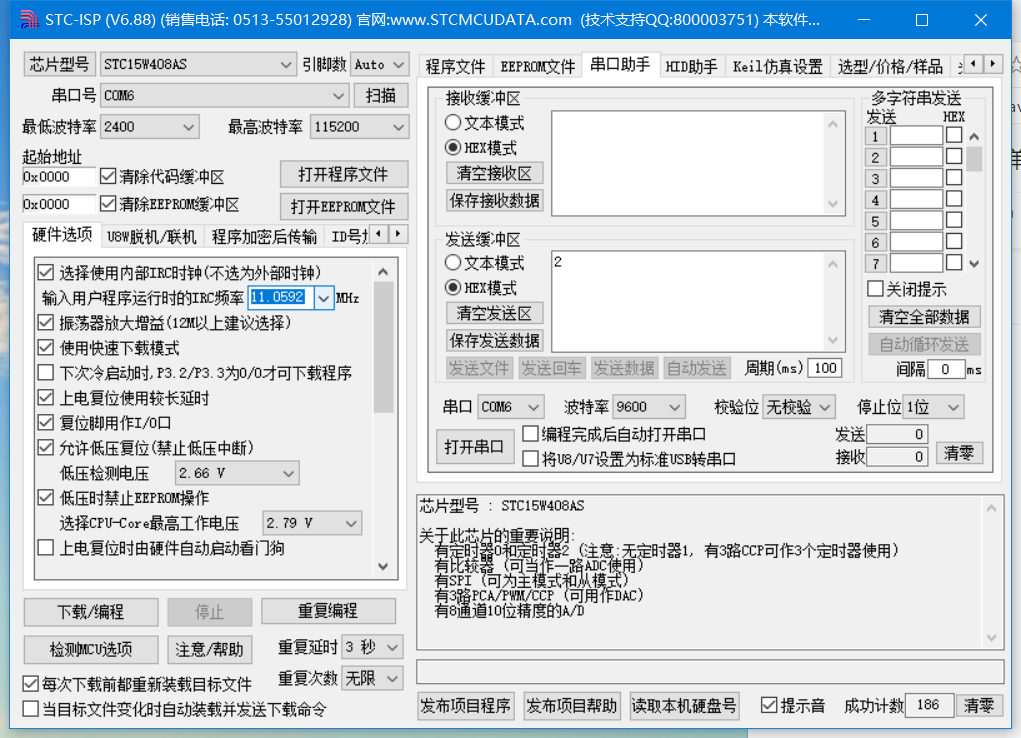

STC15W408AS單片機(jī)有兩個(gè)時(shí)鐘源:內(nèi)部高精度R/C時(shí)鐘和外部時(shí)鐘(外部輸入時(shí)鐘或外部晶體振蕩器產(chǎn)生的時(shí)鐘)。內(nèi)部高精度R/C時(shí)鐘(±0.3%),±1%溫漂,常溫下溫漂±0.6%(-20℃~+65℃)。

2023-06-15 14:45:08 1211

1211

振蕩器

--時(shí)鐘監(jiān)測(cè)系統(tǒng)

--允許獨(dú)立關(guān)斷各外設(shè)時(shí)鐘

?支持最多 39 路 I/O 接口

--所有 I/O 口支持中斷功能

--所有 I/O 支持中斷輸入濾波功能

?五通道 DMA 控制器

2023-06-07 11:04:28

flexcan在QSPI啟動(dòng)模式下無法初始化OK ,但在串行啟動(dòng)模式下可以初始化OK;

在qspi啟動(dòng)模式和串行啟動(dòng)模式下比較flexcan init之后的所有flexcan寄存器,只有兩個(gè)寄存器的位不同。

2023-06-06 07:18:53

首先,我們需要理解什么是時(shí)鐘抖動(dòng)。簡(jiǎn)而言之,時(shí)鐘抖動(dòng)(Jitter)反映的是時(shí)鐘源在時(shí)鐘邊沿的不確定性(Clock Uncertainty)。

2023-06-02 09:09:06 1024

1024

。

我們希望所有這些實(shí)例都可以獨(dú)立運(yùn)行,因此它們都配置了時(shí)鐘模塊。而且它們獨(dú)立運(yùn)行時(shí)沒有問題。但是當(dāng)我們使用Bootloader來加載和運(yùn)行所有這些實(shí)例時(shí),有些功能就無法工作,甚至?xí)霈F(xiàn)系統(tǒng)復(fù)位的情況。

以上案例如何配置時(shí)鐘模塊,所有實(shí)例一起工作時(shí)都需要配置時(shí)鐘且不沖突。

2023-05-30 08:12:04

大家好,

請(qǐng)幫助我了解 S32G2 是否支持雙內(nèi)存進(jìn)行 OTA 更新。基本上在這里我們期待雙分區(qū)。

2023-05-29 08:51:39

,中頻頻率為 DC 至 2 GHz,轉(zhuǎn)換損耗為 5 dB,LO/RF 隔離度為 38 dB。標(biāo)簽:表面貼裝,雙平衡混頻器。M1-0204的更多細(xì)節(jié)可以在下面看到。產(chǎn)品

2023-05-24 17:08:00

基站的內(nèi)部,都有自己獨(dú)立的時(shí)鐘模塊:晶振(晶體振蕩器),在沒有外部時(shí)鐘源時(shí),就處于自由震蕩狀態(tài)。

可想而知,在自由震蕩狀態(tài)的各個(gè)基站間的時(shí)鐘沒有同步,每個(gè)基站都只是一個(gè)孤島,只能獨(dú)立運(yùn)行無法協(xié)同

2023-05-10 17:09:50

和8K@30fps H265/H264視頻編碼。

核心板

核心板+底板結(jié)構(gòu),拆卸方便,核心板引腳320PIN全部引出滿足擴(kuò)展需求助力產(chǎn)品開發(fā)。

接口豐富

雙路千兆以太網(wǎng)、5G/4G模塊、HDMI輸入、HDMI輸出

2023-05-09 10:31:24

采用modbus的串口鏈路,這3個(gè)設(shè)備公用一條鏈路,該如何設(shè)設(shè)置?有一個(gè)主控屏,一臺(tái)pc上位機(jī),和一個(gè)受控設(shè)備.PC遠(yuǎn)控端,屏近地控制

2023-05-05 16:17:00

200017f NbrPorts 2

啟動(dòng)控制器

USB XHCI 1.00

掃描總線 usb3@2f00000 設(shè)備...警告已停止端點(diǎn),無論如何都在排隊(duì) URB。

意外的 XHCI 事件 TRB

2023-05-05 06:26:11

備件轉(zhuǎn)生產(chǎn)的物資信息轉(zhuǎn)換、工程文檔整理等文檔類工作耗時(shí)耗力,工程余料盤點(diǎn)難。

數(shù)字化助力工程物資供應(yīng)鏈管理價(jià)值提升為了最大限度發(fā)揮物資供應(yīng)鏈管理的實(shí)效,釋放供應(yīng)鏈管理價(jià)值,可借力數(shù)字化技術(shù),強(qiáng)化

2023-04-25 11:28:10

IC SERDES HOTLINK 256LBGA

2023-04-06 11:31:43

IC SERDES HOTLINK 256LBGA

2023-04-06 11:31:07

KL05,30 個(gè) K10。我們檢查了 K10 和 K20 uc 它不起作用。我通過 SWD 連接器 J6 對(duì) FRDM-KL46Z 板進(jìn)行編程來檢查 PE 多鏈路,它對(duì)板進(jìn)行編程沒有任何問題。我

2023-04-04 06:52:58

RJK0204DPA 數(shù)據(jù)表

2023-04-03 19:21:25 0

0 HITK0204MP 數(shù)據(jù)表

2023-04-03 18:46:08 0

0 HITJ0204MP 數(shù)據(jù)表

2023-04-03 18:44:32 0

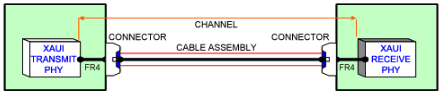

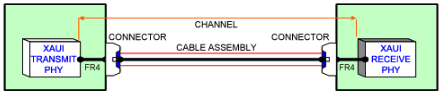

0 高速串行鏈路的表征取決于SI工程師發(fā)現(xiàn)、理解和解決嚴(yán)重抖動(dòng)問題的能力。在本討論中,我們假設(shè) PHY(物理層)或 SerDes(串行器-解串器)設(shè)備的時(shí)鐘和數(shù)據(jù)恢復(fù) (CDR) 模塊符合適用于該設(shè)備

2023-04-03 11:27:21 995

995

[0x0000004EB: cpsid i]。請(qǐng)告訴我是否需要在啟動(dòng)時(shí)初始化 PC、MSP 和更多寄存器,以及如果需要該怎么做。此外,為什么當(dāng)我使用 PE 多鏈路通用探針進(jìn)行調(diào)試時(shí),它沒有初始化就可以工作?

2023-03-31 06:17:11

RQK0204TGDQA 數(shù)據(jù)表

2023-03-30 19:39:38 0

0 RQJ0204XGDQA 數(shù)據(jù)表

2023-03-30 19:36:47 0

0 BL-2020RGB-TRB

2023-03-29 21:50:26

BB-2020BGR-TRB

2023-03-29 21:50:25

BL-HJC35B-TRB

2023-03-29 21:43:02

RP114K331D-TRB

2023-03-29 21:38:32

DA-15S-II

2023-03-29 17:52:56

BL-HB335B-TRB-6

2023-03-29 17:42:20

BL-HZ337A-L6-TRB

2023-03-29 17:41:56

BL-HKC36P-TRB

2023-03-29 17:35:50

幾乎稍微復(fù)雜的數(shù)字設(shè)計(jì)都離不開時(shí)鐘。時(shí)鐘也是所有時(shí)序邏輯建立的基礎(chǔ)。前面介紹建立時(shí)間和保持時(shí)間時(shí)也涉及過時(shí)鐘偏移的概念。下面將總結(jié)下時(shí)鐘的相關(guān)知識(shí),以便更好的進(jìn)行數(shù)字設(shè)計(jì)。

2023-03-28 13:56:41 978

978

和2024年,隨著AI大數(shù)據(jù)領(lǐng)域、以及超級(jí)計(jì)算機(jī)或者超級(jí)計(jì)算單元等應(yīng)用的迅猛發(fā)展,大電流和高功率密度模塊、以及高能量密度的Power Block模塊也將會(huì)迎來爆發(fā)式的需求增長(zhǎng)。MPS最新推出的雙路輸出系列

2023-03-24 15:42:26

64 x 8,串行,I2C實(shí)時(shí)時(shí)鐘

2023-03-24 14:48:57

64 x 8,串行,I2C實(shí)時(shí)時(shí)鐘

2023-03-24 14:01:39

根據(jù)參考手冊(cè),NXP S32K144HAMLL 具有 3 個(gè)低功耗串行外設(shè)接口,使用 SIRC 時(shí)鐘源運(yùn)行。 我想知道 3 LPSPI 是否與時(shí)鐘源一起獨(dú)立運(yùn)行。我找不到顯示時(shí)鐘源如何連接到所有三個(gè) SPI 的完整總線圖。如果有人能澄清這一點(diǎn),那將非常有幫助。

2023-03-24 06:27:34

I2C 串行實(shí)時(shí)時(shí)鐘

2023-03-23 05:01:01

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論