摘要

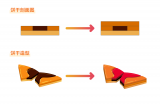

新的全濕剝離工藝在去除高度注入的光刻膠時不需要干等離子體灰化工藝,同時保持低缺陷水平和至少相當于記錄工藝的高產量性能。灰化步驟的消除減少了不希望的基板損壞和材料損失,改善了周期時間,釋放了晶圓廠占地面積,并降低了資本投資和運營成本。

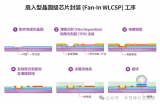

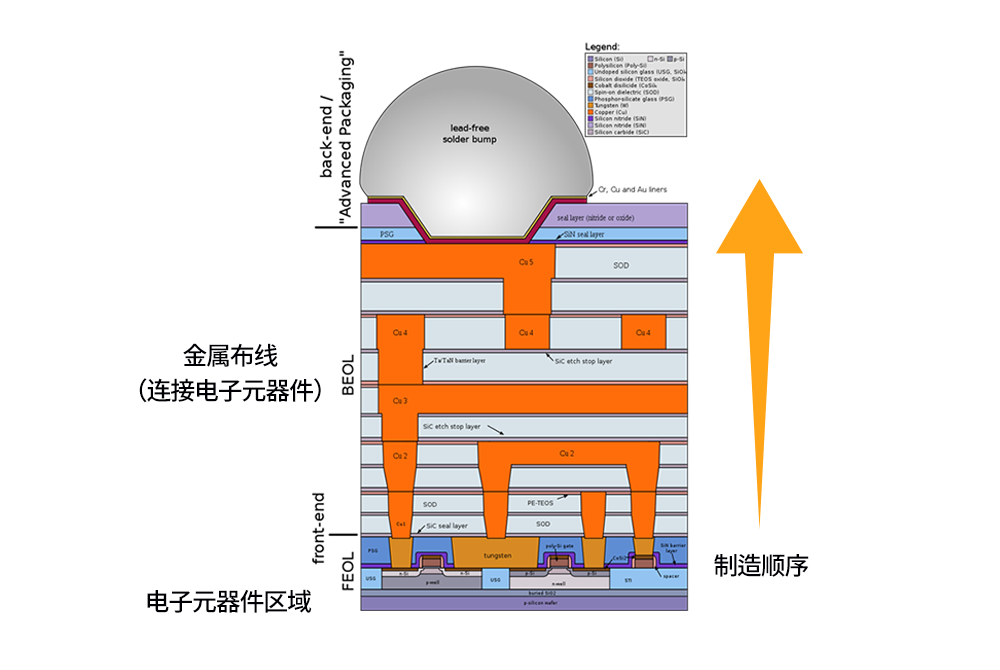

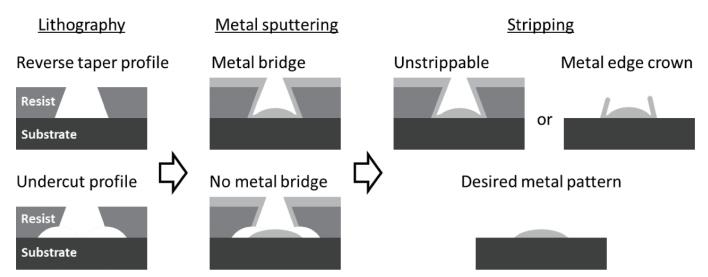

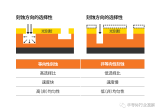

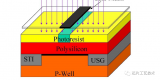

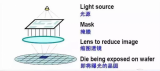

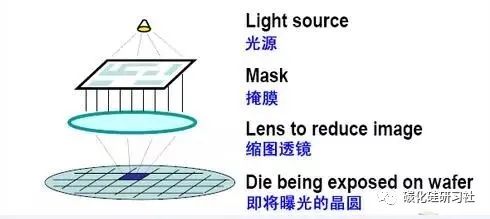

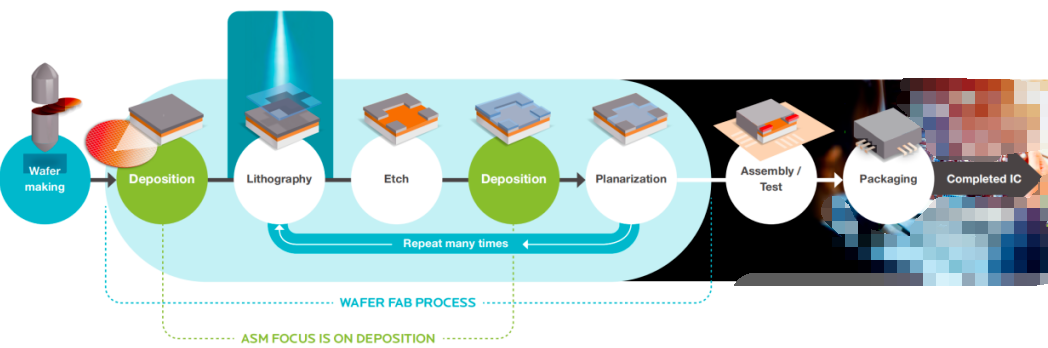

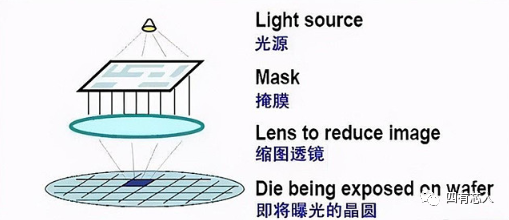

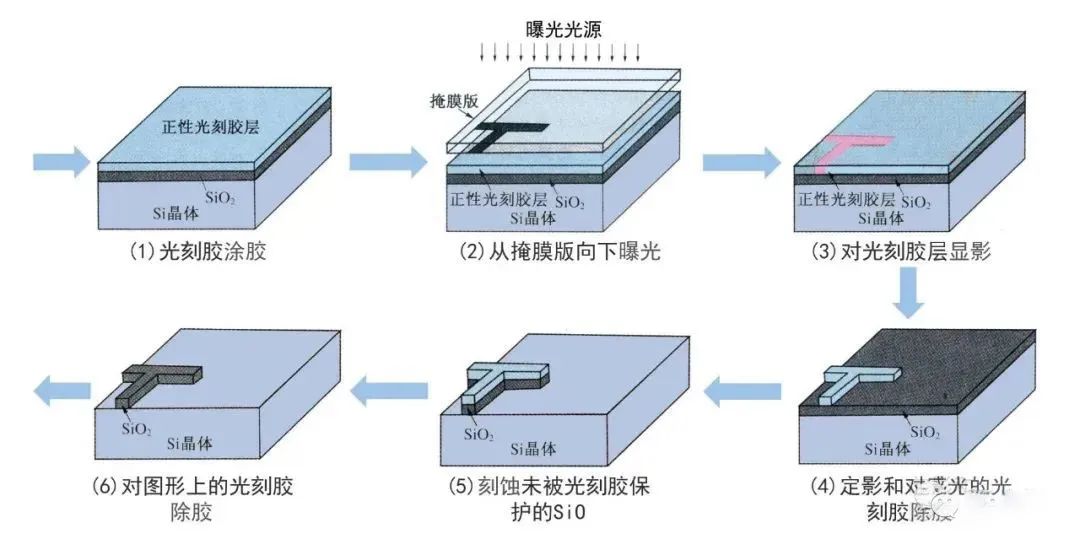

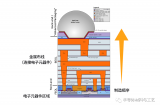

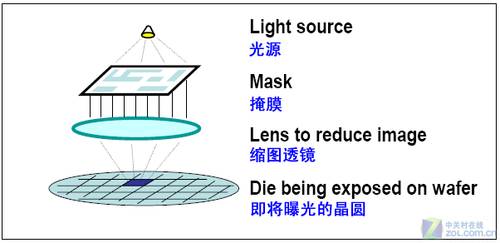

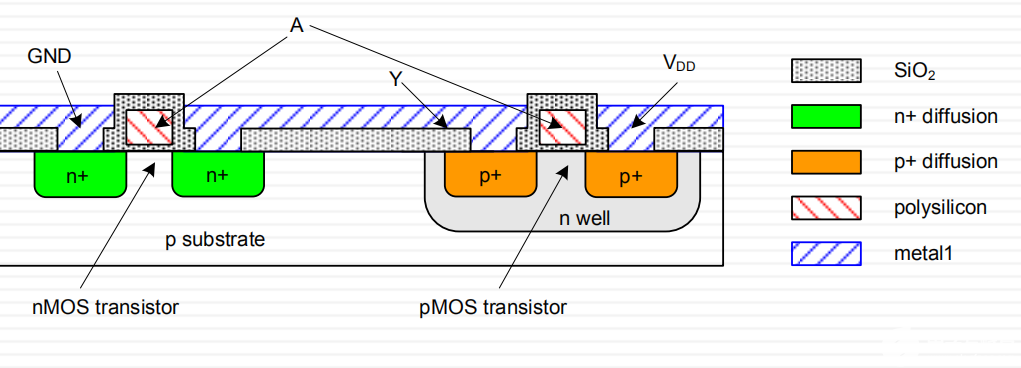

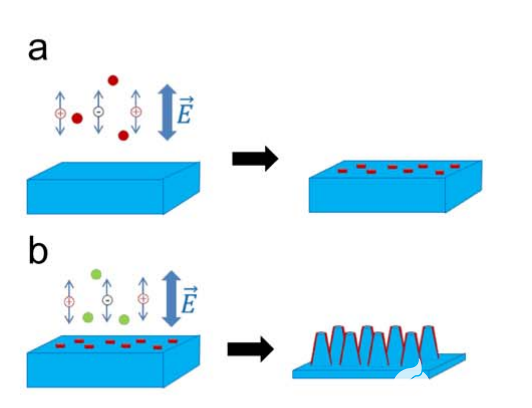

在 CMOS 制造中,離子注入用于修改硅襯底以滿足各種帶隙工程需求。通常,圖案化光刻膠 (PR) 用于定義離子注入位置。離子注入后,圖案化的光刻膠必須完全去除,表面必須為下一輪的圖案化和離子注入做好準備。離子注入在光刻膠表面形成一層堅韌的層,使其難以去除。

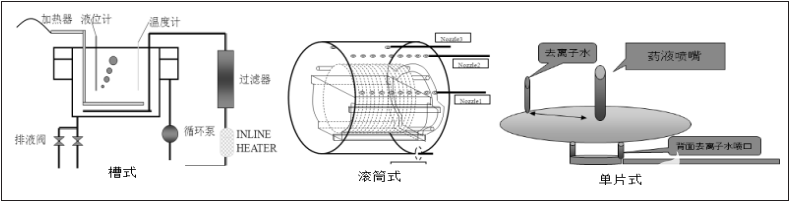

常使用干式等離子體灰化去除注入的光刻膠,然后進行濕式化學清洗。離子注入工藝的三個回路——隔離(阱)回路、晶體管通道回路和晶體管結構回路——用于構建CMOS器件。僅阱環路就占總工藝層的近三分之一,在 90nm 邏輯 CMOS 制造的情況下,可能涉及超過 21 個步驟的離子注入和光刻膠剝離。因此,循環時間的任何減少都會迅速成倍增加,從而顯著縮短總處理時間。

全濕光刻膠優勢

已經提出了一種全濕光刻膠去除工藝,以消除等離子體引起的基板損壞的可能性并減少基板材料損失 [1, 2]。此外,消除等離子體灰化步驟顯著減少了離子注入圖案化周期時間,這對于代工 CMOS 制造尤其重要。

在大批量生產環境中,只有在與現有記錄工藝 (POR) 的最終良率性能相匹配的情況下,采用這種全濕式光刻膠剝離工藝才是合理的。

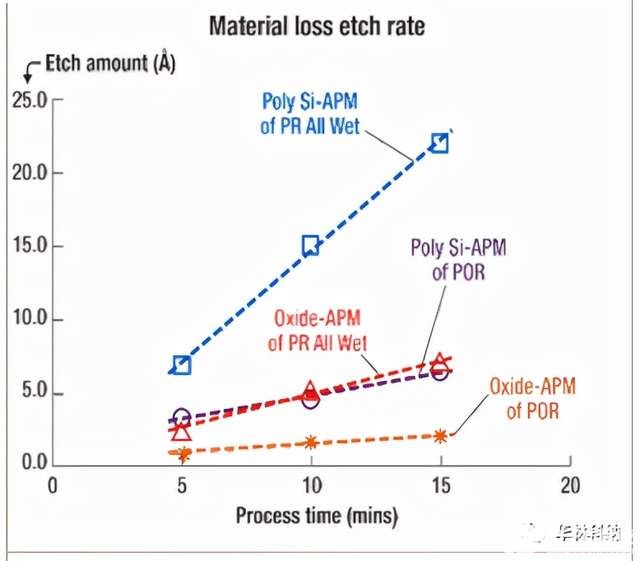

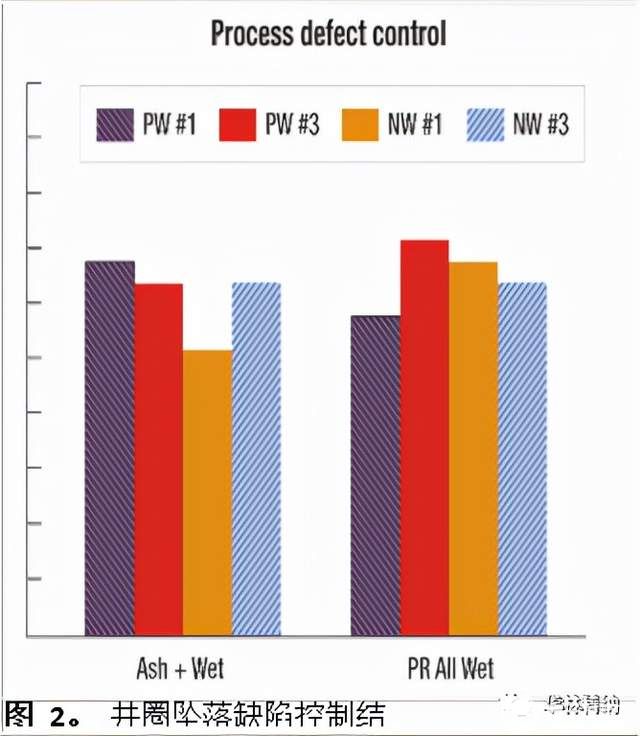

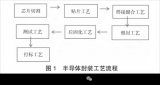

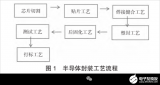

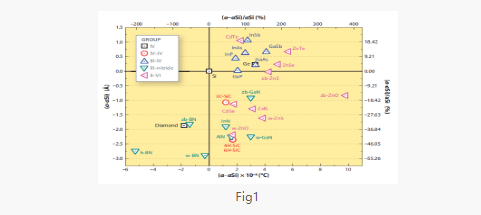

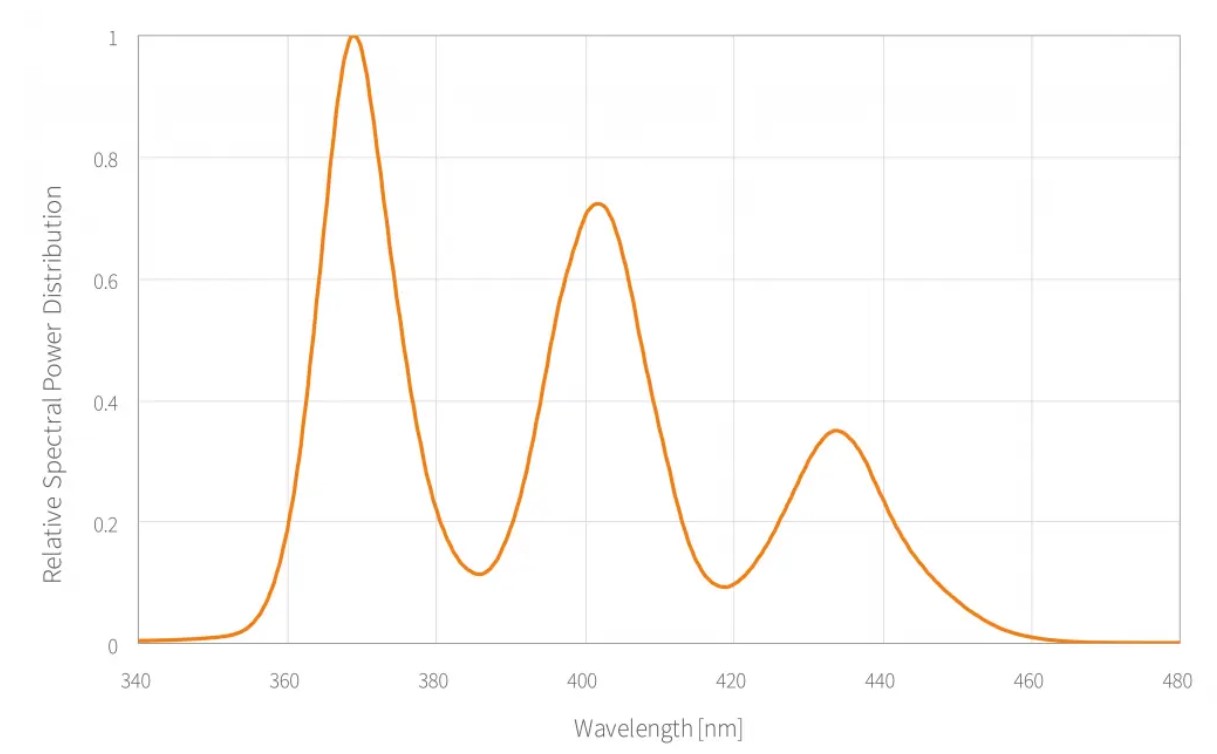

制造基線(灰化后清潔)工藝和全濕剝離工藝的蝕刻速率行為如圖 1 所示。蝕刻速率數據用于設置全濕剝離工藝參數,以最大限度地減少下降缺陷控制性能,并將工藝引起的材料損失與當前器件幾何形狀的制造基線相匹配。在這項工作中,所有四個井回路都使用了一個使用五分鐘的 SPM 暴露,然后是兩分鐘的 APM 暴露的過程。

處理周期時間

與 POR(灰+濕)相比,這種全濕工藝可以將每個掩模的光刻膠剝離周期時間從 70 分鐘減少到大約 25 分鐘——大約是 POR 基線周期時間的三分之一。考慮到井回路的七個掩模層,通過全濕光刻膠剝離的總循環時間從八小時減少到大約五小時,這使循環時間減少了 60% 以上。

產量表現基準

為了實現離子注入后光刻膠全濕剝離工藝與當前基線(灰化 + 灰化后清潔)工藝之間的批量生產比較,使用稱為協調置信度的專有統計控制技術對晶圓最終良率表現。該技術在制造過程中使用逐步相同的表征,并通過各種晶圓驗收測試 (WAT) 進行最終良率性能分析。

結論

已開發出一種全濕式光刻膠去除工藝,該工藝減少了工藝步驟的數量并消除了等離子體引起的基板損壞的可能性,同時還最大限度地減少了基板材料損失。正如本文詳述的工藝驗證實驗所證明的那樣,與當前的制造基線工藝(等離子灰化后濕法清洗)相比,這種剝離方法可提供等效的缺陷控制和可比的良率控制 (>99.9%)。此外,全濕法工藝證明能夠將離子注入周期時間減少 60% 以上,同時將潔凈室空間利用率提高 300% 以上。

審核編輯:符乾江

電子發燒友App

電子發燒友App

評論