。

**·**接地和電源分布:確保晶振附近的接地和電源分布合理,沒有電源或地線過孔導(dǎo)致的信號干擾。

4. 軟件程序配置檢查

**·**時鐘系統(tǒng)配置:查看軟件程序中關(guān)于時鐘系統(tǒng)的配置,確保晶振引腳被正確配置為

2024-03-06 17:22:17

如果晶振的外接電容值選擇不當(dāng),可能會對電路產(chǎn)生以下影響 :

1.頻率穩(wěn)定性: 電容值過小可能導(dǎo)致頻率穩(wěn)定性下降,容易受到外界因素的干擾。電容值過大可能會使頻率偏離標(biāo)稱值。

2.起振問題: 電容值

2024-03-04 11:33:16

上電USB接口識別不出,排查發(fā)現(xiàn)19.2M晶振未起振,請問這是啥原因,匹配電容更換了也不行。

2024-02-27 06:18:43

在使用PSOC 4000S系列 CY8C4025LQS-S411做汽車上的觸控應(yīng)用時,我需要使用外部晶振,外部有源晶振有兩種類型的波形輸出,正弦波和方波,我想請教一下應(yīng)該選用什么樣輸出波形的晶振呢?我的系統(tǒng)是5V供電的,是否有推薦的外接有源晶振型號?

2024-02-21 07:36:07

的微波信號皆能傳致載點的目的,不會有信號反射回來源點,從而提升能源效益。阻抗匹配關(guān)系著系統(tǒng)的整體性能,實現(xiàn)匹配可使系統(tǒng)性能達(dá)到最優(yōu)。而阻抗匹配是針對射頻等而言的,對于功率電路則不適用的,否則會燒掉東西。 為什么要測試阻抗?元件的阻抗受很

2024-01-24 10:23:30 148

148

我的應(yīng)用場景是這樣的,M487JIDAE有114個IO口,其中有兩個需要外接晶振,這樣只剩下112個IO口;正好項目需要用到114個IO,所以希望不外接晶振,然后使用內(nèi)置晶振也能夠跑USB例程。目前M487JIDAE的開發(fā)包里面也沒有找到使用內(nèi)置晶振跑USB例程的寫法,小白剛?cè)腴T,請教一下大家怎么處理,謝謝!

2024-01-16 06:15:15

無源探頭的阻抗匹配 示波器的無源高阻探頭具有非常廣泛的使用度,工程師們經(jīng)常會把探頭接在不同的示波器上,或者給示波器接入不同的探頭。而發(fā)生更換后的新系統(tǒng)中,示波器通道的輸入阻抗與探頭的阻抗往往不匹配

2024-01-12 11:11:35 136

136

最近在用這個芯片,注意到例程中使用的都是內(nèi)部16Mhz的 HFOSC,那么如果我不想接外部晶振的話可以嗎?外接的兩個引腳應(yīng)該如何處理呢?

2024-01-12 07:54:54

1、我在使用ADuC7020時,在外部晶振上是按照中文說明書上P88頁 ,沒有在晶振兩頭放匹配電容,現(xiàn)在使用時發(fā)現(xiàn)晶振有時候不能起振

想問下放不放匹配電容對起振是否有影響?

2、關(guān)于

2024-01-12 07:35:22

MCU的晶振下到底該不該鋪銅,有些資料說最好鋪銅,有些說最好不要鋪銅??求各位高手解答!!!!

2024-01-12 06:56:40

對于電子工程師而言,晶體和晶振是電路中不可或缺的關(guān)鍵元件,尤其在涉及到時鐘信號和同步操作時。雖然兩者在功能上有著相似之處,但在實際應(yīng)用、電路設(shè)計以及布局布線等方面卻存在著顯著的區(qū)別。本文將詳細(xì)對比

2024-01-04 11:54:47

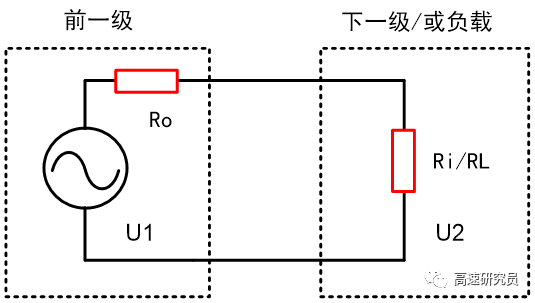

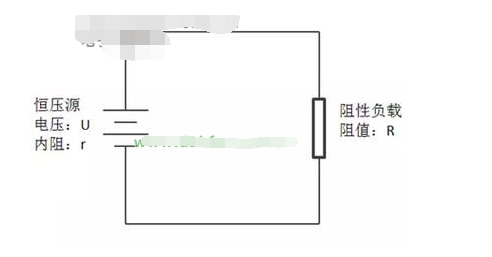

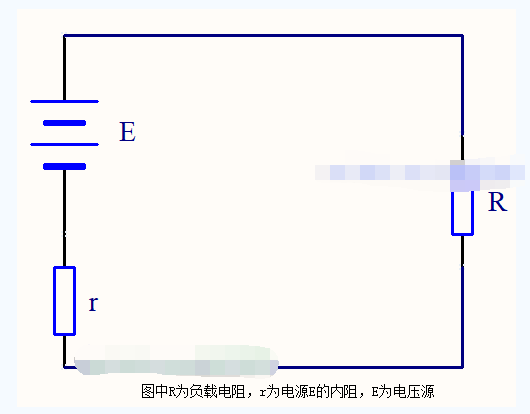

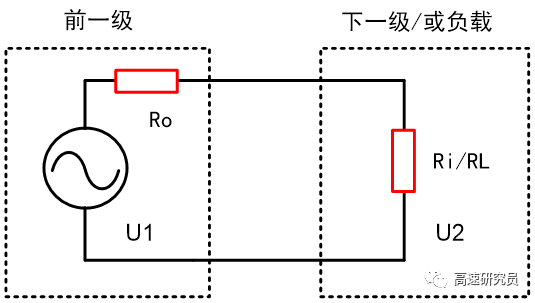

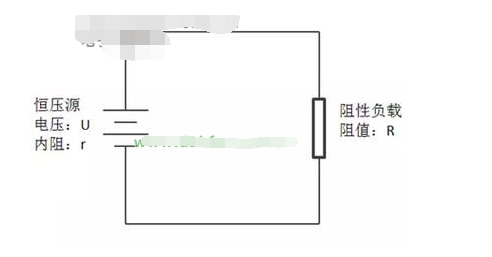

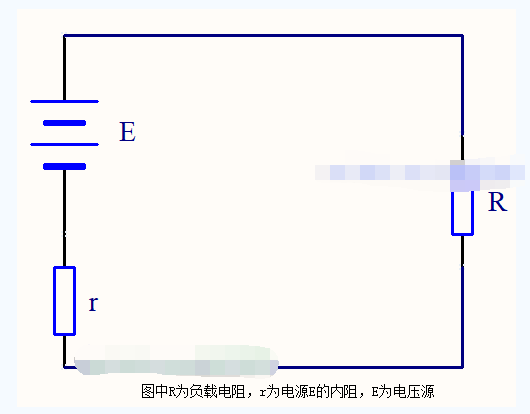

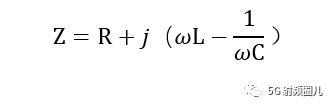

(虛部)。 其中電抗又包括容抗和感抗,由電容引起的電流阻礙稱為容抗,由電感引起的電流阻礙稱為感抗。 阻抗匹配的理想模型 射頻工程師大都遇到過匹配阻抗的問題,通俗的講,阻抗匹配的目的是確保能實現(xiàn)信號或能量從“信號源”到“負(fù)載”的有效傳送 其最最理想模

2024-01-02 16:59:13 395

395

ADE7880最小系統(tǒng):AVDD,DVDD,REF都正常,使用16.384MHZ晶振不起振,為什么換用5.9MHZ晶振起振,晶振電容都是20PF。另外換用其它頻率晶振,ADE7880可以正常工作嗎?

2023-12-26 07:53:01

AD2S1210需采用同一個晶振,有源晶振與無源晶振會有影響嗎?

2、兩片ad2s1210(粗機與精機)數(shù)據(jù)讀取是先后對于數(shù)值的正確有影響嗎?

3、就是下面這個電路(附件中)通過SPI總線讀取數(shù)據(jù)的接法正確嗎?

謝謝!

2023-12-22 06:23:59

什么是阻抗匹配?影響阻抗的因素?? 阻抗匹配是在電子電路中為了提高功率傳輸效率而進(jìn)行的一種電性特性調(diào)整方法。當(dāng)能量從一個電路傳輸?shù)搅硪粋€電路時,如果兩個電路之間的阻抗不匹配,就會發(fā)生功率反射,這導(dǎo)致

2023-12-21 11:31:33 394

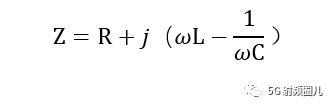

394 和輸出端口的阻抗相匹配,從而最大程度地傳輸信號,并最小化信號的反射和損耗。 在了解阻抗匹配的概念和原理之前,我們首先需要了解一些基本的電路理論。阻抗(Impedance)是指電路中的電阻、電感和電容的整體特性,它包含了電路元件對電流和電壓的阻

2023-12-18 13:39:56 479

479 晶振電路的并聯(lián)電阻有什么用?

在晶振電路中,并聯(lián)電阻是一個重要的元件,它與石英晶體諧振器并聯(lián)連接。并聯(lián)電阻的作用主要有以下幾點:1.頻率調(diào)節(jié)

并聯(lián)電阻可以調(diào)節(jié)晶振電路的頻率。當(dāng)并聯(lián)電阻的值發(fā)生變化

2023-12-13 09:38:27

請問AD9956如果選擇直接用外部晶振時鐘,對晶振的頻率有要求嗎?一定要400M,還是只要不超過400M就可以,比如20M。謝謝!

2023-12-13 08:55:39

我在使用AD7768的過程中,clk_sel拉高,使用外部晶振或者LVDS,使用LVDS的時候采樣正常,但是用無源晶振的時候晶振無法起振,是不是除了clk_sel拉高之外還需要什么設(shè)置才會使用外部晶振

2023-12-11 08:22:54

RF射頻電路為什么選取50歐姆作為阻抗匹配的數(shù)值呢?這個數(shù)值是怎么確定下來的,背后有什么意義? 阻抗匹配是RF射頻電路設(shè)計中非常重要的一個概念,它涉及到信號的傳輸效率和功率的最大化。通常情況下,RF

2023-12-07 13:37:52 1172

1172 設(shè)計時,AD2S1210的時鐘輸入采用8.192MHZ的有源晶振,選擇晶振時對有源晶振的功率有什么要求???一個有源晶振能不能給兩個AD2S1210芯片提供時鐘輸入???感謝!

2023-12-07 07:07:43

AD9249-65怎么外接晶振?有一個65M的晶振,如何接?問題二是差分信號線是否可以在VIVADO上面采集?問題三采集的時候是否需要input clk+和clk-?接多大的時鐘信號?以及多大的電壓?

2023-11-15 06:20:09

自制arduino最小系統(tǒng),晶振必要加10k電阻來起振?

2023-11-07 07:34:03

我想問一下altera系列CPLD芯片支持的外接的晶振的最大時鐘頻率從手冊的什么地方能查到,有那個高手能跟我講一下的?

2023-11-06 07:49:34

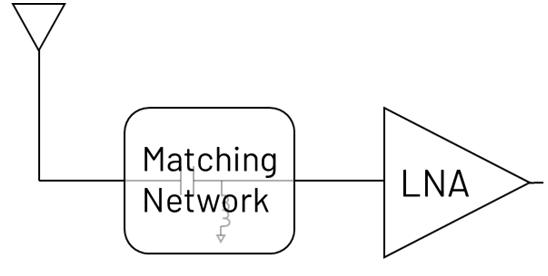

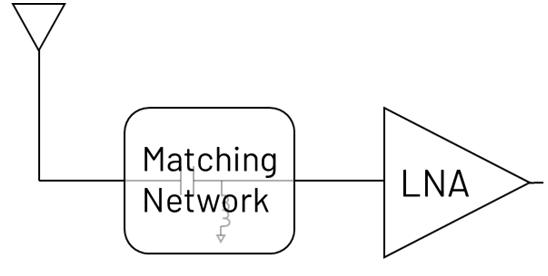

阻抗匹配是一個較大的話題,根據(jù)具體的頻率和使用場景,大概可以分為4個模塊討論。分別是:電路匹配、傳輸線匹配、天線匹配、噪聲匹配。

2023-11-03 11:50:07 696

696

外部晶振斷電內(nèi)部晶振是不是迅速起電

2023-11-03 08:02:15

非常重要,因為在高速數(shù)字和模擬電路中,信號頻率通常在數(shù)兆赫或甚至更高的范圍內(nèi)運行。如果信號阻抗不匹配,就會導(dǎo)致信號反射、串?dāng)_、噪聲等問題,從而影響信號穩(wěn)定性和可靠性。 阻抗匹配的定義是在不同電路元件之間實現(xiàn)阻抗的匹配,

2023-10-30 10:03:25 919

919

晶振的作用是啥?只是為了提供時鐘周期嗎?

2023-10-25 07:19:37

AT32MCU時鐘配置錯誤或晶振大小選擇錯誤導(dǎo)致異常在時鐘配置錯誤或晶振大小選擇錯誤的情況下,下載代碼到開發(fā)板導(dǎo)致無法繼續(xù)進(jìn)行debug或再次下載的一系列異常情況

2023-10-23 07:12:15

阻抗匹配網(wǎng)絡(luò)有L型、派型、T型,各有什么優(yōu)缺點? 阻抗匹配網(wǎng)絡(luò)有L型、派型、T型,這些網(wǎng)絡(luò)用于匹配源和負(fù)載之間的阻抗,以確保信號傳輸?shù)淖畲蠊β省T?b class="flag-6" style="color: red">阻抗匹配網(wǎng)絡(luò)之前,如果源和負(fù)載之間的阻抗不匹配,則會

2023-10-22 14:25:30 3196

3196 低噪聲放大器輸入端和輸出端匹配原則是什么?阻抗匹配的目的是什么? 低噪聲放大器輸入端和輸出端匹配原則是什么? 低噪聲放大器是電路系統(tǒng)中的一個非常重要的部分,利用它可以增強信號的弱度并減少噪聲的干擾

2023-10-20 14:55:47 870

870 為什么高頻小信號諧振放大器中要考慮阻抗匹配?如何實現(xiàn)阻抗匹配?常用有哪些連接方式? 一、高頻小信號諧振放大器的介紹 高頻小信號諧振放大器,是一種廣泛應(yīng)用于無線通信、雷達(dá)、衛(wèi)星通信、微波通信等領(lǐng)域

2023-10-20 14:55:44 679

679 采用容感元件進(jìn)行阻抗匹配,實測結(jié)果與理論仿真完全相反,可能是什么原因? 采用容感元件進(jìn)行阻抗匹配時,理論仿真與實測結(jié)果完全相反,可能有以下幾個原因: 1.元件本身參數(shù)誤差 在使用容感元件進(jìn)行阻抗匹配

2023-10-20 14:37:44 272

272 的可靠性也很高。

四、廣泛應(yīng)用

可編程晶振被廣泛應(yīng)用于各種通訊設(shè)備、網(wǎng)絡(luò)設(shè)備、GPS接收器、頻譜分析儀器等需要頻率控制的設(shè)備中。它可以滿足不同的頻率需求,從而為這些設(shè)備的穩(wěn)定運行提供了重要保障。

五、優(yōu)點

2023-10-14 17:38:14

stm32有內(nèi)部晶振,為什么還要用外部晶振?

2023-10-13 06:19:46

為什么高頻小信號諧振放大器中要考慮阻抗匹配?如何實現(xiàn)阻抗匹配?常用有哪些連接方式?? 高頻小信號諧振放大器中要考慮阻抗匹配的主要原因是為了提高其性能和效率。阻抗不匹配會導(dǎo)致信號反射和損耗,影響諧振

2023-10-11 17:43:07 869

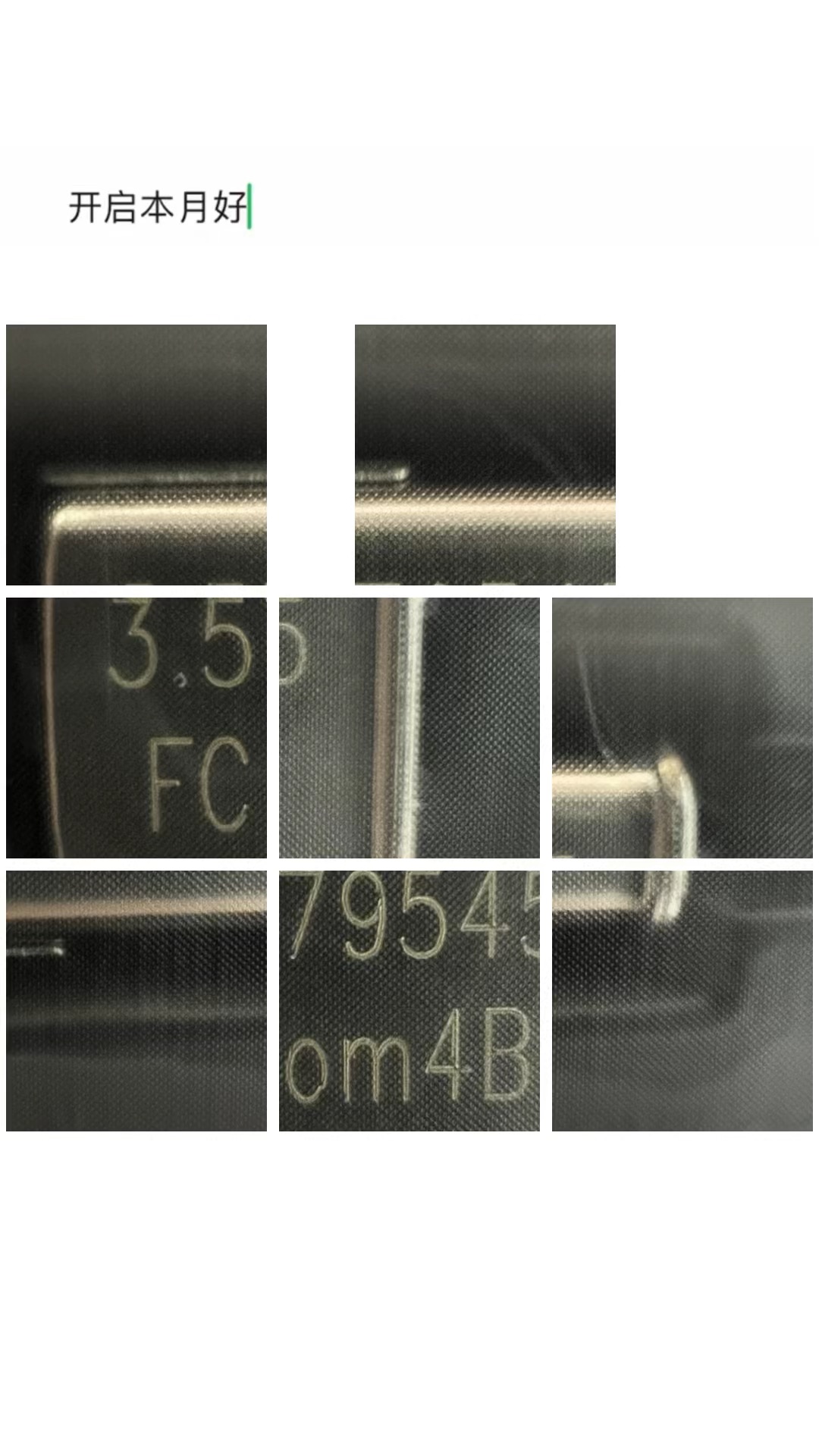

869 GD32的晶振和STM32的晶振連接有什么不同的地方

2023-10-11 07:58:05

u3000阻抗匹配問題是電子技術(shù)中的一項基本概念,通過匹配可以實現(xiàn)能量的最優(yōu)傳送,信號的 最佳處理。總之,匹配關(guān)乎著系統(tǒng)的性能,使匹配則是使系統(tǒng)的性能達(dá)到約定準(zhǔn)則下的最優(yōu)。其實,阻抗匹配的概念還可

2023-09-25 06:12:00

阻抗與頻率成反比的元件有哪些? 阻抗與頻率成反比的元件是指在電路中隨著頻率變化而阻抗發(fā)生變化,且變化的趨勢是與頻率成反比的元件。這些元件在電路中起著非常重要的作用,因為它們可以在電路中隔離高頻噪聲

2023-09-19 16:39:14 665

665 藍(lán)牙天線阻抗匹配

阻抗匹配中,阻抗的測試是在板子供電的情況下測試還是在沒有供電的情況下測試?比如藍(lán)牙天線。是測試在板子工作的時候天線的阻抗,還是怎么測試?

2023-09-18 10:20:52

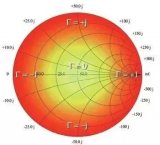

阻抗匹配(Impedance matching)是微波電子學(xué)里的一部分,主要用于傳輸線上,來達(dá)至所有高頻的微波信號皆能傳至負(fù)載點的目的,不會有信號反射回來源點,從而提升能源效益。

2023-09-03 11:06:09 1765

1765

阻抗匹配是指信號源或者傳輸線跟負(fù)載之間的一種合適的搭配方式。根據(jù)接入方式阻抗匹配有串行和并行兩種方式;根據(jù)信號源頻率阻抗匹配可分為低頻和高頻兩種。

2023-08-30 09:47:00 480

480 一顆晶振和2個負(fù)載電容,但這些料件在PCBA加工過程中,常常造成良率下降,如在電容上件過程中產(chǎn)生冷焊的現(xiàn)象,容易造成起振失敗;外掛晶振也必須增加電路板面積,增加終端產(chǎn)品的設(shè)計困難度。

新唐為解決外掛晶

2023-08-28 06:56:34

我的應(yīng)用場景是這樣的,M487JIDAE有114個IO口,其中有兩個需要外接晶振,這樣只剩下112個IO口;正好項目需要用到114個IO,所以希望不外接晶振,然后使用內(nèi)置晶振也能夠跑USB例程。目前M487JIDAE的開發(fā)包里面也沒有找到使用內(nèi)置晶振跑USB例程的寫法,小白剛?cè)腴T,請教一下大家怎么處理,謝謝!

2023-08-25 08:34:36

有時阻抗不匹配還有另外一層意思,例如一些儀器輸出端是在特定的負(fù)載條件下設(shè)計的,如果負(fù)載條件改變了,則可能達(dá)不到原來的性能,這時我們也會叫做阻抗失配。

2023-08-05 12:05:58 2795

2795

阻抗匹配是指負(fù)載阻抗與激勵源內(nèi)部阻抗互相適配,得到最大功率輸出的一種工作狀態(tài)。對于不同特性的電路,匹配條件是不一樣的。

2023-07-04 14:44:02 521

521

阻抗匹配主要用于傳輸線上,以此來達(dá)到所有高頻的微波信號均能傳遞至負(fù)載點的目的,而且?guī)缀醪粫行盘柗瓷浠貋碓袋c,從而提升能源效益。信號源內(nèi)阻與所接傳輸線的特性阻抗大小相等且相位相同,或傳輸線的特性阻抗與所接負(fù)載阻抗的大小相等且相位相同,分別稱為傳輸線的輸入端或輸出端處于阻抗匹配狀態(tài),簡稱為阻抗匹配。

2023-07-04 14:38:36 4494

4494

在RF電路中,阻抗可以在很寬的頻率范圍內(nèi)變化。RF匹配網(wǎng)絡(luò)的主要目標(biāo)是匹配源和負(fù)載的阻抗,以最大限度地提高功率傳輸,并在所需的工作頻率范圍內(nèi)最小化反射。這需要了解源和負(fù)載的阻抗,并選擇在該頻率下產(chǎn)生匹配的組件。

2023-06-27 11:38:16 1000

1000

希望本文揭開了RF阻抗匹配的神秘面紗,并使RF功率放大器電路更易于理解。使用網(wǎng)絡(luò)的負(fù)載Q值,我們可以在串聯(lián)和并聯(lián)網(wǎng)絡(luò)之間切換,并將低值電阻轉(zhuǎn)換為高值電阻。然而,與任何工程任務(wù)一樣,對計算進(jìn)行交叉檢查總是好的,LTspice在繪制電路的輸入阻抗和功率輸出方面證明是無價的。

2023-06-15 16:36:54 1097

1097

在處理RF系統(tǒng)的實際應(yīng)用問題時,總會遇到一些非常困難的工作,對各部分級聯(lián)電路的不同阻抗進(jìn)行匹配就是其中之一。一般情況下,需要進(jìn)行匹配的電路包括天線與低噪聲放大器(LNA)之間的匹配、功率放大器輸出

2023-06-08 16:59:49 620

620

我有一塊STM32U575的板子,沒焊外部高速晶振,本來上面標(biāo)著16兆晶振,四個腳的,我在淘寶上買了一些32M的晶振。

淘寶上寫著匹配晶振8pF,我忘買了,搞了兩個4.7pF的晶振,用STM32CubeMX生成代碼,就是讓一個燈閃。

可是燈一直不閃。我想會不會是匹配晶振的原因。請高手指教,謝謝!

2023-06-02 16:42:20

挑戰(zhàn)。

在高速PCB設(shè)計中,阻抗匹配顯得尤為重要,為減少在高速信號傳輸過程中的反射現(xiàn)象,必須在信號源、接收端以及傳輸線上保持阻抗的匹配。

一般而言,單端信號線的阻抗取決于它的線寬以及與參考平面之間

2023-05-26 11:30:36

我這邊的應(yīng)用對MCU的時鐘有要求,無法使用24M的晶振,只能提供一個10M的有源時鐘。芯片手冊中沒有規(guī)定外部時鐘的最大值和最小值,只是寫了一個典型值24M。用戶手冊中提到了有幾個模塊是直接使用的外部時鐘,像vad、ptmr、usb等。請問能否用10M有源時鐘替換24M晶振?

2023-05-26 06:26:07

具有電阻、電感和電容的電路里,對交流電所起的阻礙作用叫做阻抗。阻抗常用Z表示。阻抗由電阻、感抗和容抗三者組成,但不是三者簡單相加。 阻抗的單位是歐。

2023-05-18 11:15:41 4843

4843

窄帶阻抗匹配電路設(shè)計

2023-05-15 16:48:46 592

592

阻抗匹配,作為射頻設(shè)計中最為重要的一個環(huán)節(jié),每一個射頻工程師都無法繞過去的。 今天我們再加以總結(jié),把整個阻抗匹配,展現(xiàn)給大家。

2023-04-27 09:36:34 4477

4477

我正在使用帶有 ESP32 WROOM 32 的 Arduino V1.0.6 SDK。當(dāng)使用外部晶振時,我目前面臨 IO25 深度睡眠中的錯誤中斷問題。IO25是用來外接晶振,還是頻率輸出?如何禁用此功能,并使用 IO25 作為中斷以從 ESP32 的深度睡眠中喚醒。

2023-04-11 09:07:05

FPGA外接50MHZ的晶振,里面的組合邏輯電路運行時刷新頻率是多少呢?

2023-04-10 11:46:50

負(fù)載阻抗等于信源內(nèi)阻抗的共軛值,即它們的模相等而輻角之和為零。這時在負(fù)載阻抗上可以得到最大功率。這種匹配條件稱為共軛匹配。如果信源內(nèi)阻抗和負(fù)載阻抗均為純阻性,則兩種匹配條件是等同的。

2023-04-08 10:30:14 2802

2802 除了使用阻抗匹配變壓器外,設(shè)計人員還可以在 RF 放大器的輸出端使用阻抗濾波器電路,它可以兼作濾波電路和阻抗匹配電路。有多種類型的濾波器電路可用于阻抗匹配,本文討論了最常見的那些。

2023-04-06 09:03:38 2481

2481 負(fù)載阻抗匹配就是在傳輸線和負(fù)載之間加入一個阻抗匹配網(wǎng)絡(luò),阻抗匹配網(wǎng)絡(luò)應(yīng)該全部由無耗元件組成,其匹配原理就是通過阻抗匹配網(wǎng)絡(luò)引入一個新的反射波,這個反射波與負(fù)載因其的反射波等輻反相,相互抵消,使傳輸線上沒有反射波

2023-03-25 10:13:42 1250

1250 不用外接電容復(fù)位和外接晶振的單片機和外接復(fù)位和晶振的單片機使用的編程語言一樣嗎?單片機可以直接驅(qū)動場效應(yīng)管控制電磁閥每秒動作1-200次嗎

2023-03-24 11:13:46

電子發(fā)燒友App

電子發(fā)燒友App

評論