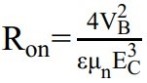

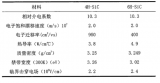

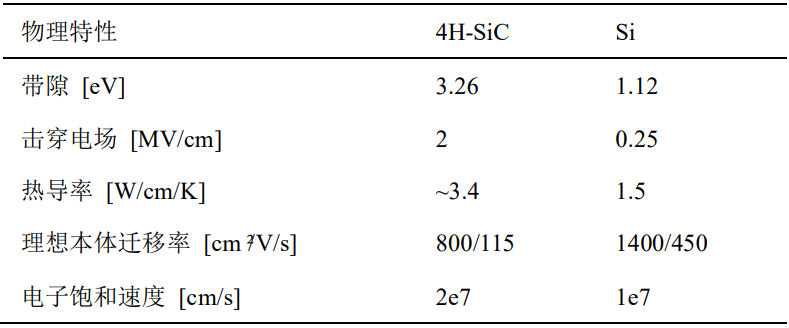

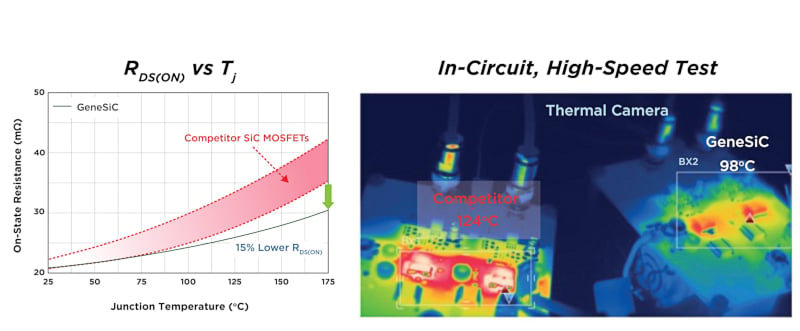

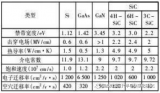

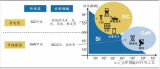

傳統(tǒng)的硅功率晶體管在理論上已經(jīng)被推到了極限。寬帶隙功率器件的緊湊模型對于分析和評估它們對電路和系統(tǒng)性能的影響是必要的。帶隙比硅的 1.1 eV 更寬的半導(dǎo)體已經(jīng)超越了效率、密度和工作溫度方面的限制。阻斷電壓和 R DS(on)之間的關(guān)系?取決于電壓擊穿值(SiC MOSFET 的帶隙值為 3.26 eV)。對于硅,導(dǎo)通電阻有一個下限,如圖 1 所示的等式所示。

該方程根據(jù)給定擊穿電壓的臨界電場表達(dá)了“硅極限”。

由于帶隙較大(2 MV/cm 對 0.5 MV/cm),SiC 中通過碰撞電離產(chǎn)生帶間電子空穴所需的能量比 Si 高得多。

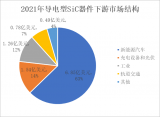

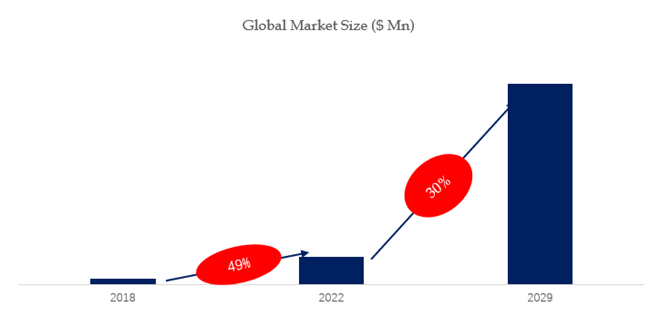

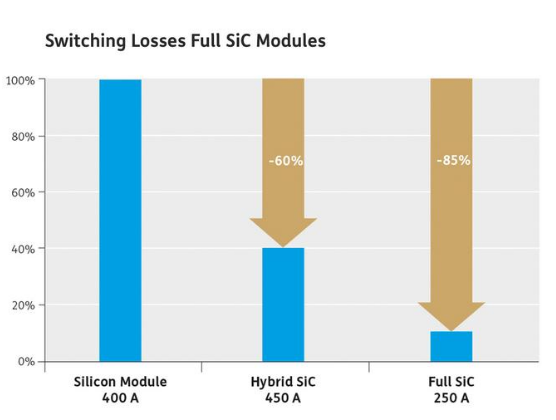

這就是為什么基于 SiC 的轉(zhuǎn)換器比基于硅的轉(zhuǎn)換器更有效地用于更高電壓級別的原因。歷史上,硅 IGBT 器件在細(xì)分市場中一直占據(jù)主導(dǎo)地位,而 SiC MOSFET 是為具有中壓水平(即 2 至 10 kV)的應(yīng)用而完美設(shè)計的。

此外,據(jù)觀察,與以效率和高功率密度著稱的 Si IGBT 相比,SiC MOSFET 能夠以更快的速度執(zhí)行開關(guān)操作。這些設(shè)備因用于海軍艦艇、儲能系統(tǒng)和高速鐵路運輸而聞名。

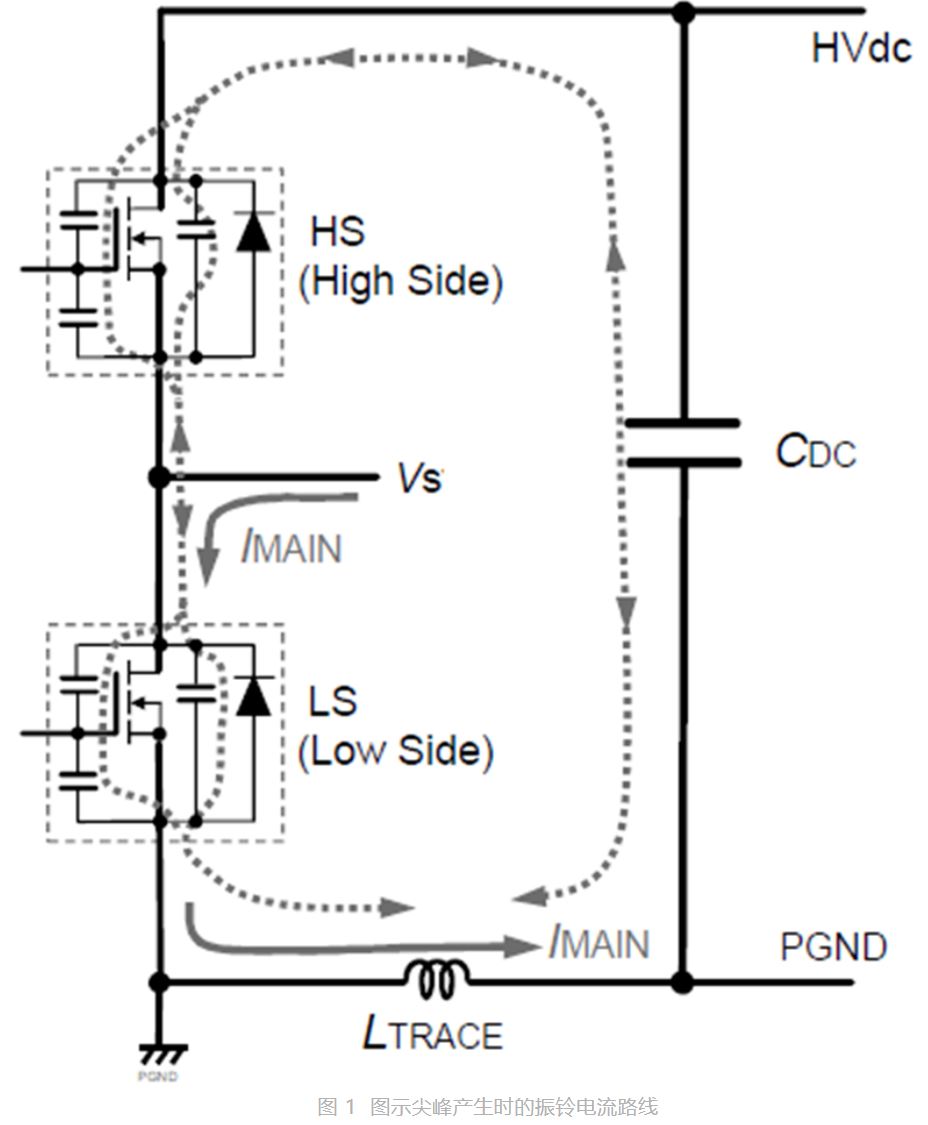

盡管如此,寬帶隙器件的極快開關(guān)和其他優(yōu)越特性也對其應(yīng)用提出了嚴(yán)峻挑戰(zhàn)。挑戰(zhàn)包括大于 100 V/ns 的 dV/dt 壓擺率和在整個轉(zhuǎn)換器中普遍存在的極高相應(yīng) di/dt 壓擺率、增強(qiáng)的電磁干擾發(fā)射、具有相應(yīng)絕緣要求的高達(dá)數(shù)十千伏的單設(shè)備阻斷電壓、開關(guān)頻率在數(shù)百千赫到兆赫范圍內(nèi),結(jié)溫超過 200°C。

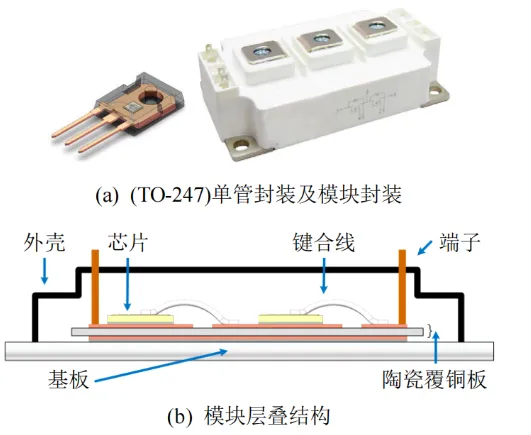

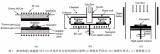

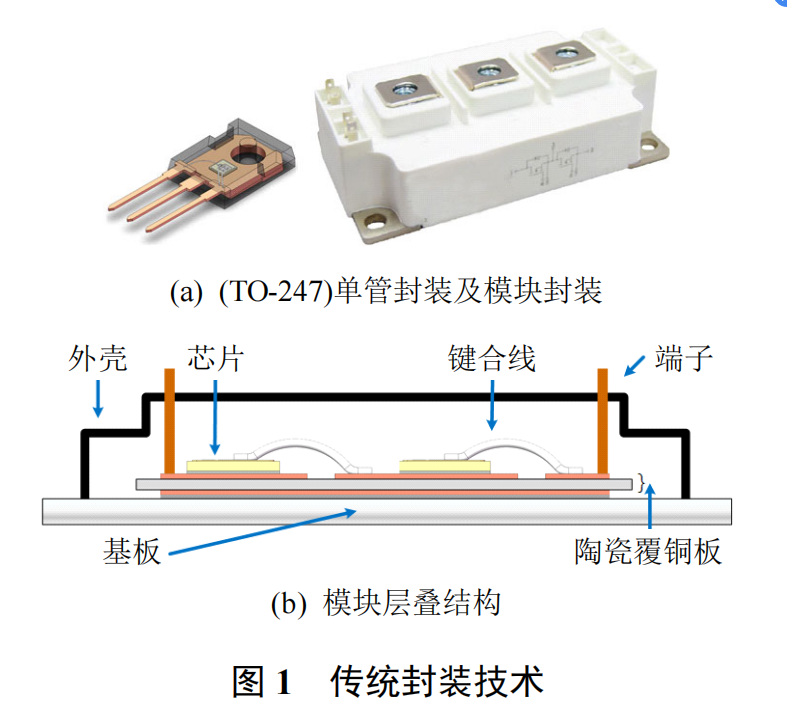

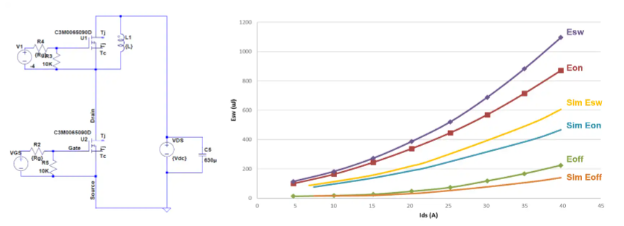

本文提及的是一款中壓 SiC MOSFET XHV-7,這是一款由 Cree Wolfspeed 制造的 6.5 kV SiC MOSFET 半連接模塊(圖 2)。該模型的批準(zhǔn)是通過將模型產(chǎn)量與來自雙脈沖測試的觀察波形進(jìn)行對比來執(zhí)行的,這些波形來自工作條件范圍直至模塊評估的范圍。

本文是針對中壓 SiC MOSFET 模塊缺乏普遍可訪問的 SPICE 模型的潛在進(jìn)展。

中壓 SiC MOSFET 模型

在對半導(dǎo)體器件建模時,從行為分析到器件物理,基本上有三個抽象層次:

- 行為的

- 半物理

- 物理

行為模型在不考慮其物理操作機(jī)制的情況下模擬功率器件,它們通常使用數(shù)學(xué)擬合方法實現(xiàn)。

使用半物理范例,標(biāo)準(zhǔn)低壓設(shè)備模型適用于解決高壓功率設(shè)備建模問題。因此,某些器件模型參數(shù)和方程的物理意義可能會丟失。

第三種模型類型基于半導(dǎo)體物理學(xué);熱和電行為的描述是通過數(shù)值求解物理方程得出的。

通常,可以使用具有 Level 3 NMOS 器件核心的子電路對 SiC MOSFET 進(jìn)行建模。

眾所周知,Level 3 NMOS 具有以下顯著優(yōu)勢:

- 它在計算上是有效的。

- 它以其合理的準(zhǔn)確性而聞名。

- 它具有在模擬中正確收斂的能力。

在 SiC MOSFET 模型中,CGS 使用線性電容器實現(xiàn),以對 SiC MOSFET 的電壓相關(guān)電容進(jìn)行建模,而行為電流源用于對偏置相關(guān) CGD 和 CDS 元件進(jìn)行建模,而無需大量計算開銷。

SPICE MOSFET 電平比較

第一代 SPICE 仿真程序使用的 MOSFET 模型可以分為三類:

- 級別 1 為時序計算和低仿真時間提供了高準(zhǔn)確度。也稱為 Schichman-Hodges 模型,級別 1 適用于柵極長度大于 10 μm 的器件。通道長度調(diào)制通過使用參數(shù) L 建模。跨導(dǎo)用于考慮體偏置。Level 1 模型不包括載流子飽和效應(yīng)、載流子遷移率退化或弱反轉(zhuǎn)模型。

- 在級別 2 中,考慮了大量電荷效應(yīng)。也稱為 Grove-Frohman 模型,假設(shè)閾值電壓恒定且僅隨襯底電壓變化,則不考慮短溝道效應(yīng)。它用于柵極長度約為 10 μm 的器件。級別 2 修改漏極電流以包括由 λ 參數(shù)建模的通道長度調(diào)制。

- 在 Level 3(經(jīng)驗?zāi)P停┲校扰c Level 3 相似,但仿真時間較短,并且有較大的收斂趨勢。包括通過橫向場(如物理效應(yīng))引起的漏極引起的勢壘降低和遷移率降低。經(jīng)驗?zāi)P瓦m用于大約 2 μm 的柵極長度。

模型驗證

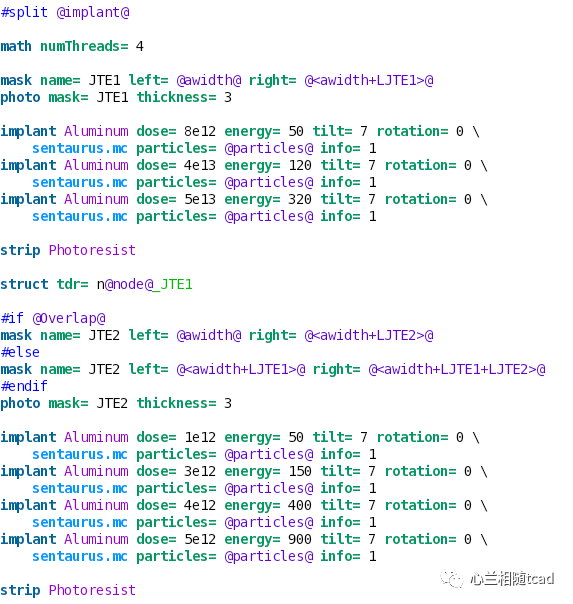

用于在中壓應(yīng)用中執(zhí)行 XHV-7 模型驗證的測試臺包括一個鉗位感性負(fù)載,以便在時域中生成波形。

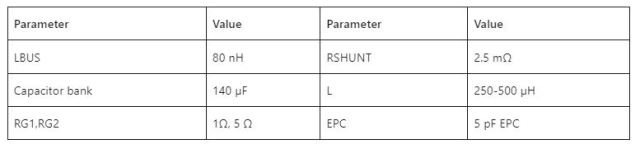

表 1 顯示了用于重建 LT SPICE 模型的參數(shù),特別是一個名為 RSHUNT 的電阻分流器,用于測量直流電流,其值為 2.5 mΩ。

參數(shù) EPC 在 Efficient Power Conversion 給出的模型中定義。

實驗裝置包括以下儀器:

- MS058 泰克八通道示波器

- TIVH05 泰克光電壓探頭 @ f = 500 MHz

- THDP0100 泰克 6-kV 差分探頭 @ f = 100 MHz

- T&M Research W-2-0025-4FC 25-mΩ 分流器 @ f = 400 MHz

- Pearson CT 型號 411 電流互感器 @ f = 20 MHz

實驗結(jié)果

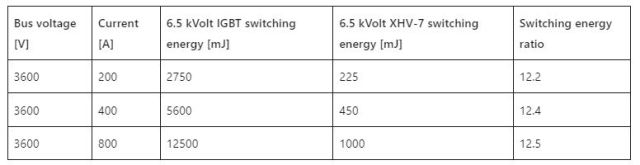

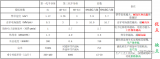

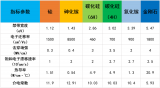

3,600-V 總線電壓和 200-、400- 和 800-A 負(fù)載電流的實驗結(jié)果還表明,6.5-kV XHV-7 模塊和 6.5-kV 硅 IGBT 之間的開關(guān)損耗降低了 12倍(表 2)模塊在 25°C 的溫度下用于以毫焦耳為單位的開關(guān)能量要求。

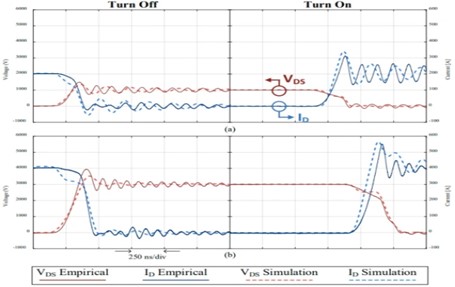

五種不同工作條件的時域經(jīng)驗預(yù)測(實線)和時域 LT SPICE 模型(虛線)之間的比較顯示出基本一致(圖 3)。

結(jié)論

對于能帶隙比硅更寬的半導(dǎo)體(例如碳化硅),到目前為止,我們還沒有專門構(gòu)思 SPICE 模型。因此,我們需要一個實驗測試平臺來繪制 I D與 V DS 的關(guān)系圖。

根據(jù)實驗數(shù)據(jù),我們在經(jīng)驗?zāi)P秃?a href="http://www.xsypw.cn/tags/凌力爾特/" target="_blank">凌力爾特標(biāo)準(zhǔn) PSPICE 實現(xiàn)之間得出了很大的一致性。

LT SPICE 仿真器中使用的合適模型可以通過從實驗設(shè)置中獲取的參數(shù)提取來推導(dǎo)出來。

審核編輯:湯梓紅

電子發(fā)燒友App

電子發(fā)燒友App

評論