中國上海,2024 年 3 月 19 日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布與 Arm 公司合作,提供基于芯粒的參考設(shè)計和軟件開發(fā)平臺,以加速軟件定義汽車(SDV)取得創(chuàng)新。

2024-03-19 11:41:16 234

234 近日,業(yè)界領(lǐng)先的電子設(shè)計自動化解決方案提供商Cadence宣布與Intel代工廠達(dá)成重要合作,共同開發(fā)并驗證了一項集成的先進(jìn)封裝流程。這一流程將利用嵌入式多晶粒互連橋接(EMIB)技術(shù),有效應(yīng)對異構(gòu)

2024-03-14 11:33:28 320

320 Cadence 與 Intel 代工廠合作開發(fā)并驗證了一項集成的先進(jìn)封裝流程。該流程能利用嵌入式多晶粒互連橋接(EMIB)技術(shù)來應(yīng)對異構(gòu)集成多芯粒架構(gòu)不斷增長的復(fù)雜性。

2024-03-11 11:48:05 209

209 電子發(fā)燒友網(wǎng)站提供《Cadence17.4使用問題匯總.docx》資料免費下載

2024-03-07 16:33:37 0

0 電子發(fā)燒友網(wǎng)站提供《cadence LOGO如何制作.docx》資料免費下載

2024-03-07 14:28:15 0

0 電子發(fā)燒友網(wǎng)站提供《Cadence中文教程介紹.zip》資料免費下載

2024-02-29 09:26:04 0

0 Cadence? 設(shè)計 IP 支持 Intel 代工廠的這一節(jié)點,并提供相應(yīng)的制程設(shè)計套件(PDK),用于加速一系列應(yīng)用的開發(fā),包括低功耗消費電子、高性能計算(HPC)、人工智能和移動計算設(shè)計。

2024-02-27 14:21:13 185

185 Cadence近日宣布,其數(shù)字和定制/模擬流程在Intel的18A工藝技術(shù)上成功通過認(rèn)證。這一里程碑式的成就意味著Cadence的設(shè)計IP將全面支持Intel的代工廠在這一關(guān)鍵節(jié)點上的工作,并提供

2024-02-27 14:02:18 159

159 電子發(fā)燒友網(wǎng)站提供《RTL9210B-CG數(shù)據(jù)表.rar》資料免費下載

2024-02-03 15:19:20 7

7 AD9610TH/883B: 級高性能模數(shù)轉(zhuǎn)換器,引領(lǐng)新一代信號處理潮流在高速、高精度的信號處理領(lǐng)域,一款卓越的模數(shù)轉(zhuǎn)換器(ADC)是不可或缺的。深圳市華灃恒霖電子科技有限公司為您隆重推薦 級別

2024-01-19 18:43:22

AD9610TH/883B:高性能模數(shù)轉(zhuǎn)換器,引領(lǐng)新一代信號處理潮流在高速、高精度的信號處理領(lǐng)域,一款卓越的模數(shù)轉(zhuǎn)換器(ADC)是不可或缺的。深圳市華灃恒霖電子科技有限公司為您隆重推薦級別

2024-01-19 14:55:58

中國上海,2024 年 1 月 11 日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布收購總部位于加利福尼亞州圣克拉拉的設(shè)計工程、嵌入式軟件和系統(tǒng)級解決方案領(lǐng)先提供

2024-01-11 12:26:40 502

502 日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布,領(lǐng)先技術(shù)服務(wù)提供商 Wistron 已采用并部署了新的 AI 驅(qū)動的電磁(EM)設(shè)計同步分析工作流程,包括 Cadence

2023-12-25 10:10:02 161

161

處理器共同推出米爾MYC-YD9360核心板及開發(fā)板,賦能新一代車載智能、電力智能、工業(yè)控制、新能源、機器智能等行業(yè)發(fā)展,滿足多屏的顯示需求。

2023-12-22 18:07:58

蘇州國芯科技股份有限公司(以下簡稱“公司”)研發(fā)的新一代汽車電子MCU產(chǎn)品“CCFC3007PT”于近日在公司內(nèi)部測試中獲得成功。

公司成功研發(fā)的汽車電子MCU新產(chǎn)品CCFC3007PT是基于公司

2023-12-20 16:56:53

功耗,走紅了全球。

今天給大家分享的是 TI 新一代明星CPU——AM62x,它相比上一代AM335x在工藝、外設(shè)、性能等多方面都有很大提升。

這里結(jié)合米爾電子的“MYC-YM62X核心板及開發(fā)板”給

2023-12-15 18:59:50

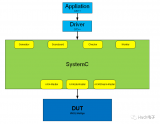

當(dāng)FPGA開發(fā)者需要做RTL和C/C++聯(lián)合仿真的時候,一些常用的方法包括使用MicroBlaze軟核,或者使用QEMU仿真ZYNQ的PS部分。

2023-12-13 10:13:45 353

353

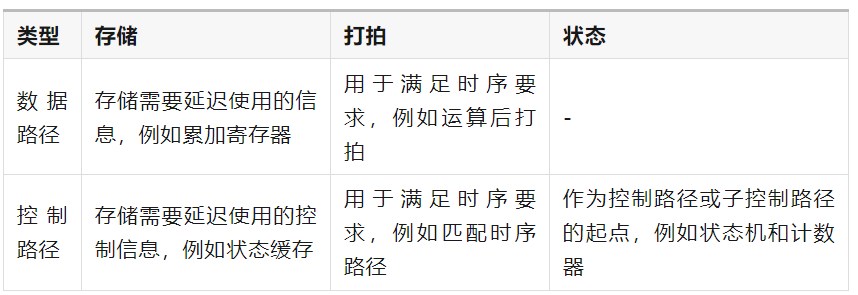

在數(shù)字前端領(lǐng)域,RTL幾乎與“設(shè)計代碼”概念相同。

2023-12-04 10:14:05 1909

1909

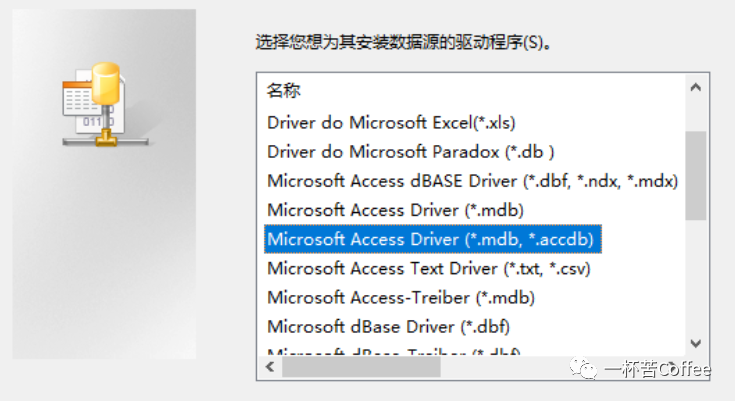

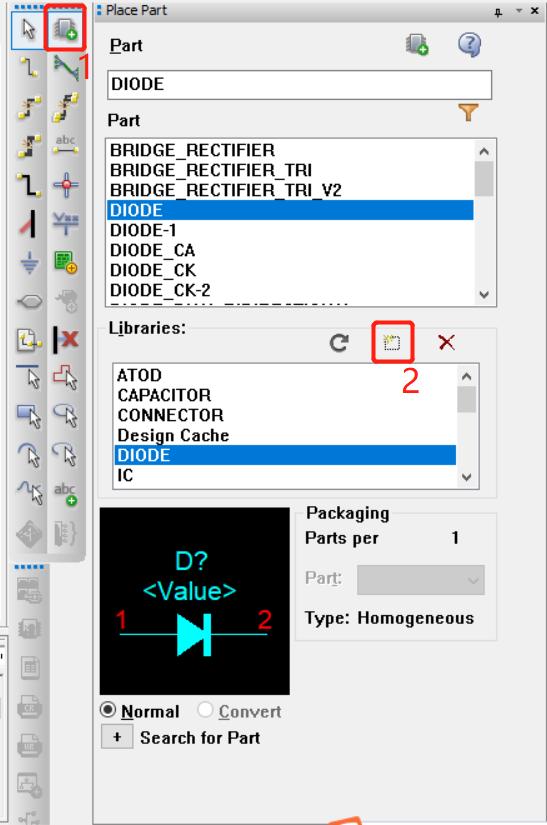

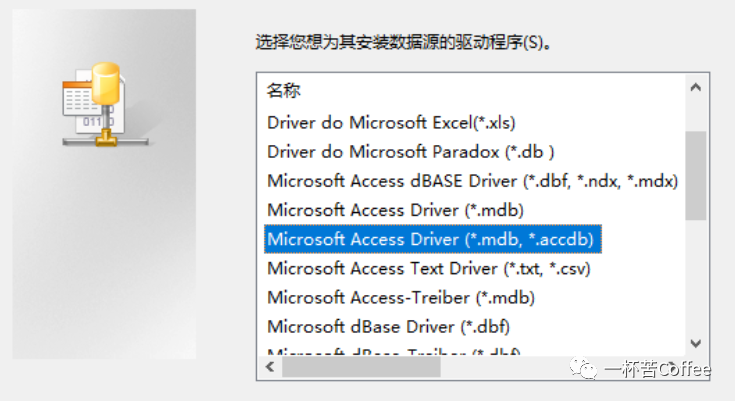

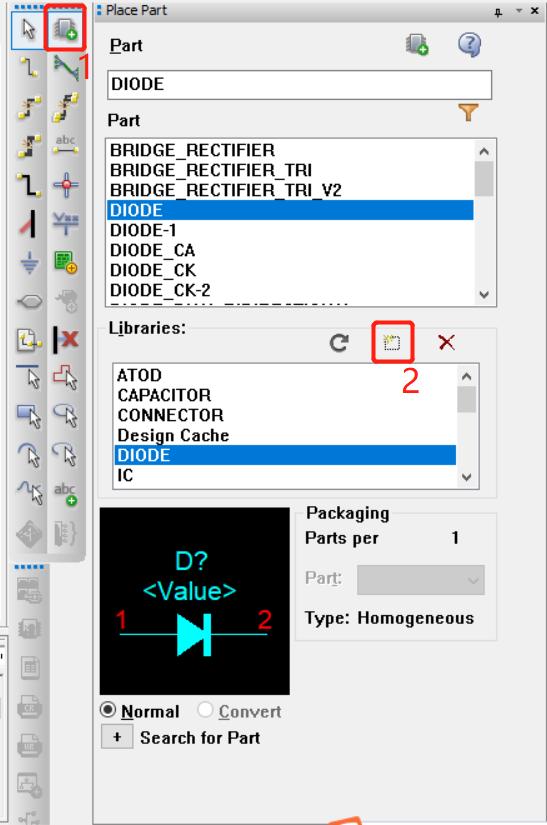

本文將主要介紹Cadence本地庫搭建從0到1的過程,并提供搭建過程中所需要的安裝軟件。搭建Cadence本地庫的目的主要是為了方便元器件的搜索與調(diào)用。

2023-11-20 17:21:16 817

817

運作流程,精通SMT生產(chǎn)設(shè)備及工藝流程,熟練掌握各工序制程及全制程工藝要求,對SMT異常分析,及不良問題改良具備成熟實戰(zhàn)經(jīng)驗。

參會福利

路線指引小貼示

自駕:導(dǎo)航定位至新一代產(chǎn)業(yè)園停車場 - P3

2023-11-17 14:42:57

運作流程,精通SMT生產(chǎn)設(shè)備及工藝流程,熟練掌握各工序制程及全制程工藝要求,對SMT異常分析,及不良問題改良具備成熟實戰(zhàn)經(jīng)驗。

參會福利

路線指引小貼示

自駕:導(dǎo)航定位至新一代產(chǎn)業(yè)園停車場 - P3

2023-11-17 14:40:39

中國上海,2023 年 11 月 8 日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布推出新產(chǎn)品 Cadence Voltus InsightAI,這是一款生成式 AI

2023-11-08 10:11:34 447

447 CEO 峰會上, Cadence 副總裁兼亞太區(qū)技術(shù)運營總經(jīng)理陳敏 發(fā)表了題為 《泛 AI 加速——新時代的 EDA 進(jìn)化》 的精彩演講,向與會者介紹了 AI 技術(shù)的發(fā)展現(xiàn)狀和未來趨勢

2023-11-03 19:15:03 555

555

英諾達(dá)發(fā)布了自主研發(fā)的EnFortius?凝鋒?RTL級功耗分析工具,可以在IC設(shè)計流程早期對電路設(shè)計進(jìn)行優(yōu)化。

2023-11-01 10:28:22 322

322 (摘要:英諾達(dá)發(fā)布了自主研發(fā)的EnFortius?凝鋒?RTL級功耗分析工具,可以在IC設(shè)計流程早期對電路設(shè)計進(jìn)行優(yōu)化。) (2023年11月1日,四川成都)英諾達(dá)(成都)電子科技有限公司發(fā)布

2023-11-01 09:51:31 122

122 ,電子信息制造業(yè)規(guī)模以上企業(yè)營業(yè)收入突破24萬億元。為貫徹落實《方案》精神,深圳新一代產(chǎn)業(yè)園積極組織了園區(qū)企業(yè)-華秋,開展了電子電路主題展,并邀請黨內(nèi)群眾學(xué)習(xí)。本次主題展也得到了相關(guān)領(lǐng)導(dǎo)的認(rèn)可和肯定

2023-10-27 11:15:03

,電子信息制造業(yè)規(guī)模以上企業(yè)營業(yè)收入突破24萬億元。為貫徹落實《方案》精神,深圳新一代產(chǎn)業(yè)園積極組織了園區(qū)企業(yè)-華秋,開展了電子電路主題展,并邀請黨內(nèi)群眾學(xué)習(xí)。本次主題展也得到了相關(guān)領(lǐng)導(dǎo)的認(rèn)可和肯定

2023-10-27 11:12:41

雙方的共同客戶可獲取 Cadence 的全流程系統(tǒng)級設(shè)計驗證和實現(xiàn)解決方案以及接口 IP,依托 Neoverse CSS 加速開發(fā)基于 Arm 的定制 SoC 中國上海,2023 年 10 月 25

2023-10-25 10:40:02 196

196

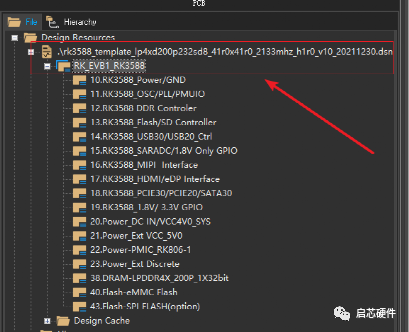

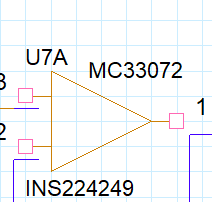

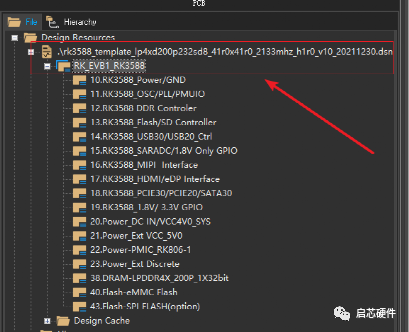

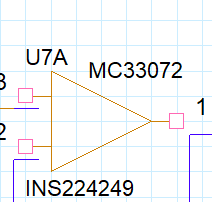

打開Cadence .DSN原理圖文件,注意選中整個DSN文件。

2023-10-18 16:07:21 4829

4829

內(nèi)容提要 1 通過利用 Cadence AI 驅(qū)動云端數(shù)字全流程,Imagination 成功將其最新 5nm 節(jié)點的漏電功耗降低 20%,將總功耗降低 6%,同時改善了面積和性能

2023-10-18 15:50:01 160

160 SystemVerilog引入了interface,這里我們從可綜合的RTL代碼的角度聊聊interface。

2023-10-12 09:06:45 747

747

RTL8211F參考原理圖

2023-10-11 15:26:43 21

21 RTL8305光纖收發(fā)器原理圖

2023-10-11 15:25:40 3

3 內(nèi)容提要 Cadence 數(shù)字全流程涵蓋關(guān)鍵的新技術(shù),包括一款高精度且支持大規(guī)模擴展的寄生參數(shù) 3D 場求解器 Cadence Cerebrus 由 AI 驅(qū)動,支持 N2 制程,可大幅提高客戶

2023-10-10 16:05:04 270

270 、即需即用,且通過 ISO 體系認(rèn)證的安全云平臺,可提供一個完全集成且經(jīng)過驗證的環(huán)境,快速啟動產(chǎn)品設(shè)計、驗證和實施工作。在我們演示 Cadence 數(shù)字和模擬設(shè)計流程的生產(chǎn)力功能時,您將看到該平臺的實際應(yīng)用。 線上研討會內(nèi)容要點 ● ?無論是完整還是局部設(shè)計流程,客戶皆可實現(xiàn)在云端加速

2023-10-09 19:25:08 294

294

多芯粒設(shè)計周轉(zhuǎn)時間 中國上海,2023 年 10 月 8 日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布推出新的系統(tǒng)原型驗證流程,該流程基于 Cade

2023-10-08 15:55:01 249

249 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布與臺積電(TSMC)合作將新推出的 Cadence Virtuoso Studio 集成到 TSMC N16 毫米波設(shè)計參考流程

2023-09-28 10:10:02 531

531 請教一下,我在HLS里面要將以下程序生成IP核,C Synthesis已經(jīng)做好了,但是在export RTL的時候一直在運行

int sum_single(int A int B

2023-09-28 06:03:53

流程,能兼容所有的 TSMC(臺積電)先進(jìn)節(jié)點,包括最新的 N3E 和 N2 工藝技術(shù)。 這款生成式設(shè)計遷移流程由 Cadence 和 TSMC 共同開發(fā),旨在實現(xiàn)定制和模擬 IC 設(shè)計在 TSMC

2023-09-27 10:10:04 301

301 Cadence Allegro 22.1-1-3-將網(wǎng)絡(luò)顯示在焊盤、走線、銅皮上

2023-09-25 09:12:19 1780

1780

中國上海,2023 年 9 月 20 日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布推出新一代 AI IP 和軟件工具,以滿足市場對設(shè)備端和邊緣 AI 處理不斷增長

2023-09-20 10:07:48 516

516 內(nèi)容提要 生成式 AI 自動化,將布局布線時間由幾天縮短到幾分鐘 集成 Cadence OnCloud,支持?jǐn)?shù)據(jù)管理和合作,與易于使用的新版 layout 界面一起配合,有效提升設(shè)計人員的生產(chǎn)力

2023-09-14 13:40:02 1480

1480

白皮書

第二代ClearClock?三次泛音晶體振蕩器

在這份全新的白皮書中,我們討論了最新一代超低抖動三次泛音晶體振蕩器的特點、優(yōu)勢、性能和特性,這些振蕩器旨在為各種高速應(yīng)用提供穩(wěn)定準(zhǔn)確的時鐘信號

2023-09-13 09:51:52

fpga中RTL simulation,打不開,但是我的modelsim,下載了呀,難道沒有破解的原因嗎?,并且我quartus軟件,也把modelsim的路徑引用了。

2023-09-08 23:46:58

工程應(yīng)用產(chǎn)學(xué)研融合發(fā)展。 交流會期間,西南某院在論文【模塊化緊湊型高壓電源系統(tǒng)的研制】中提出:為研究高比壓、高參數(shù)的聚變等離子體物理,我國建成了新一代“人造太陽”裝置中國環(huán)流三號裝置。要提高中性束注入

2023-09-07 10:39:35

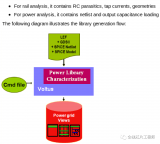

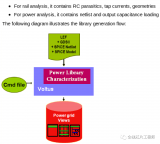

Cadence功耗分析首先需生成power grid library

2023-09-06 09:47:50 854

854

內(nèi)容提要 ● Cadence 優(yōu)化了其 AI 驅(qū)動的 RTL-to-GDS 數(shù)字流程,并為 Arm Neoverse V2 平臺提供了相應(yīng)的 5nm 和 3nm 快速應(yīng)用工具包(RAK),助力設(shè)計人

2023-09-05 12:10:01 3159

3159 STM32U599平衡圖顯性能與功耗的新一代產(chǎn)品,內(nèi)容包含: STM32U5x9 的高性能與高階圖形加速器 、STM32U5的矢量圖形 、STM32U5x9 的低功耗設(shè)計 、LPBAM - sensor hub等。

2023-09-05 07:21:11

RTL8812BU-CG 哪位大佬有這個物料的數(shù)據(jù)手冊,麻煩發(fā)一份給我。謝謝

2023-09-04 20:25:57

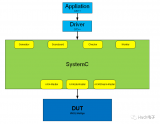

ARM周期模型工具提供了一個集成環(huán)境,該環(huán)境將系統(tǒng)驗證與硬件開發(fā)流程并行。

周期模型編譯器采用RTL硬件模型并創(chuàng)建一個高性能的可鏈接對象,稱為周期模型,它是周期和寄存器準(zhǔn)確的。

周期模型編譯器提供了與驗證環(huán)境交互的API:

2023-08-16 06:30:07

(V2M-MPS2+)平臺執(zhí)行硬件原型。

Cortex-M3 DesignStart Eval提供了一個圍繞?SSE-050子系統(tǒng)和Cortex-M3處理器構(gòu)建的示例系統(tǒng)。

該示例系統(tǒng)包括用于實施正常運行的ARM

2023-08-12 07:38:33

無線/BT模塊RTL8723DS原理圖

2023-08-09 15:41:13 39

39 業(yè)界卓越的 Tensilica Xtensa LX 平臺第 8 代已經(jīng)上線,可提供顯著的系統(tǒng)級性能增強,同時確保理想能效。 中國上海,2023 年 8 月 4 日——楷登電子(美國 Cadence

2023-08-04 11:05:02 396

396

中國上海,2023 年 7 月 28 日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布,雙方已就 Cadence 收購 Rambus SerDes 和存儲器接口 PHY

2023-07-28 17:11:51 988

988 推出 Cadence ?Joules RTL Design Studi o,這款新的解決方案可為用戶提供實用的洞察,有助于加快寄存器傳輸級(RTL)設(shè)計和實現(xiàn)流程。 前端設(shè)計人員可以在一個統(tǒng)一的界面使用數(shù)

2023-07-17 10:10:01 492

492

內(nèi)容提要 ● ?Cadence 流程已通過認(rèn)證,可立即投入生產(chǎn),該工藝下 Design IP 產(chǎn)品現(xiàn)已完備,可支持客戶進(jìn)行 Intel 16 工藝下 SOC 設(shè)計 ● ? 客戶可以基于已被充分認(rèn)證

2023-07-14 12:50:02 381

381

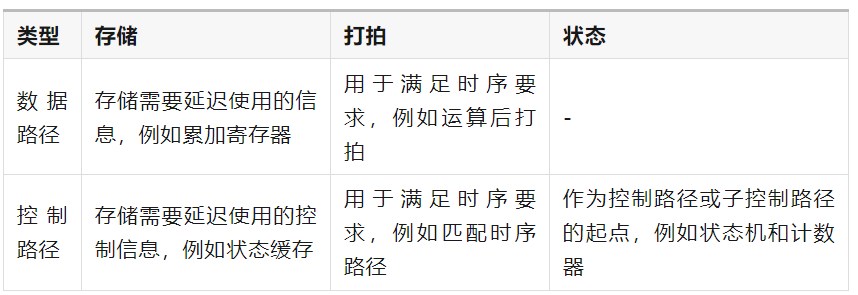

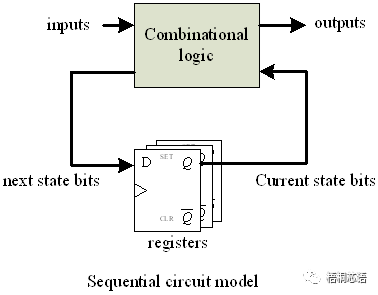

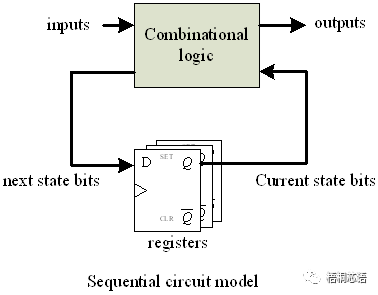

既然RTL是寄存器傳輸級電路,那么電路設(shè)計就一定是以寄存器的特性為基礎(chǔ)進(jìn)行設(shè)計。

2023-07-13 16:17:56 3149

3149

內(nèi)容提要 ●? 完整的背面布線解決方案,助力面向移動、汽車、人工智能和超大規(guī)模應(yīng)用的下一代高性能芯片設(shè)計 ●? Cadence SF2 數(shù)字全流程包括用于 nTSV 優(yōu)化的先進(jìn)技術(shù) ● 背面實現(xiàn)流程

2023-07-10 10:45:04 272

272

電子發(fā)燒友網(wǎng)站提供《MQTT瑞昱Ameba RTL8195開源分享.zip》資料免費下載

2023-07-06 11:28:34 1

1 平臺支持 Samsung 新的 3D CODE 標(biāo)準(zhǔn),助力設(shè)計人員創(chuàng)建多種先進(jìn)的封裝技術(shù)。 ?? Cadence 和 Samsung 的技術(shù)為客戶提供全面、定制化的解決方案。適用于能夠縮短 3D-IC

2023-07-06 10:05:04 329

329 已經(jīng)過 SF2 和 SF3 流程認(rèn)證 ●?Cadence 數(shù)字全流程針對先進(jìn)節(jié)點實現(xiàn)了最佳 PPA 結(jié)果 ●Cadence 定制/模擬工具,包括基于 AI 的 Virtuoso Studio,已針對

2023-07-05 10:12:14 381

381 已經(jīng)過 SF2 和 SF3 流程認(rèn)證 ●? Cadence 數(shù)字全流程針對先進(jìn)節(jié)點實現(xiàn)了最佳 PPA 結(jié)果 ● Cadence 定制/模擬工具,包括基于 AI 的 Virtuoso Studio

2023-07-05 10:10:01 322

322 FPGA的設(shè)計流程主要包括HDL代碼編寫、RTL綜合、布局布線、靜態(tài)時序分析、生成下載文件。下面將逐一介紹各部分。下面是FPGA設(shè)計的流程圖。

2023-07-04 12:06:08 791

791

?Studio 現(xiàn)已支持經(jīng)過認(rèn)證的節(jié)點到節(jié)點設(shè)計遷移流程。 該流程與 Samsung Foundry 的先進(jìn)節(jié)點兼容。Cadence 和 Samsung 共同開發(fā)了這個新的生成式設(shè)計遷移流程,可簡化和自動化遷移過程,為

2023-07-04 10:10:01 471

471 ,2023 年 6 月 30 日——楷登電子(美國? Cadence ?公司,NASDAQ:CDNS)近日宣布,基于 AI 的 Cadence?Virtuoso?Studio 設(shè)計工具和解決方案已獲得 Samsung Foundry 認(rèn)證。 雙方的共同客戶可以放心利用 Virtuoso Studio 和

2023-06-30 10:08:30 680

680 cadence元器件連不上線

2023-06-26 15:28:00 1375

1375

和混合信號 IP,與現(xiàn)有流程相比,在達(dá)到所需精度的同時,可幫助提升 2 倍性能。 Cadence 的這款解決方案助力 DB GlobalChip 加速了 IP 開發(fā)和驗證周期,可以更快將產(chǎn)品推向市場。 在客戶規(guī)定的時間內(nèi)滿足模擬和混

2023-06-25 12:25:02 512

512 電子發(fā)燒友網(wǎng)站提供《RTL8722DM現(xiàn)支持TensorFlowLite和AI計算.zip》資料免費下載

2023-06-15 09:38:42 0

0 電子設(shè)計自動化領(lǐng)域領(lǐng)先的供應(yīng)商 Cadence,誠邀您參加 “2023 CadenceCONNECT:HPC 芯片全流程驗證解決方案” 線下研討會北京站。 會議將聚焦提供業(yè)界領(lǐng)先的虛擬云計算、快速

2023-06-12 14:15:01 368

368

RTL8380MI模塊,RTL8382MI模塊,交換機核心模塊,千兆交換機模塊,工業(yè)級交換機模塊

2023-06-07 10:08:47 860

860

2023 年 6 月 2 日—3 日,Cadence 受邀出席了第七屆集微半導(dǎo)體峰會。在首日舉辦的 EDA IP 工業(yè)軟件峰會中,Cadence 高級 AE 經(jīng)理王正算作為代表向與會嘉賓介紹

2023-06-07 00:20:03 466

466

我們在網(wǎng)表里直接插入了RTL的always語句,對wr_data_7_進(jìn)行了打拍和簡單邏輯處理(新加的邏輯所需要的輸入信號都可以在原網(wǎng)表中找到),把處理后的信號wr_data_7_new_d接到原DFF的D端,如下圖中的箭頭。這種在網(wǎng)表里直接插入和修改的RTL也叫做RTL補丁。

2023-06-06 16:20:09 1132

1132

? 內(nèi)容提要: 新推出的 Arm TCS23 和 Cadence 工具為芯片流片提供了捷徑 Cadence 對其 RTL-to-GDS 數(shù)字流程進(jìn)行了精細(xì)優(yōu)化,為 Arm Cortex-X4

2023-06-03 09:44:22 329

329 “把算法用RTL實現(xiàn),怎么做?” 這個問題,對于芯片設(shè)計工程師、芯片算法工程師、FPGA工程師來講,是非常重要的問題。 算法時代來臨, 學(xué)習(xí) 將算法轉(zhuǎn)化為RTL電路 可以提升職場競爭力,提升在團隊

2023-06-02 15:35:16 497

497 設(shè)計過程。該平臺實現(xiàn)了跨學(xué)科的工作流程無縫協(xié)作、集成了Cadence一流的簽核級仿真分析工具,并提供了更強大的layout性能。

2023-05-22 15:40:10 1794

1794

IEEE 802.3標(biāo)準(zhǔn)的以太網(wǎng)收發(fā)器。它提供所有必要的物理層功能,通過CAT傳輸和接收以太網(wǎng)數(shù)據(jù)包。5UTP電纜。RTL8211FI和RTL8211DI是按照工業(yè)級標(biāo)準(zhǔn)制造的。RTL8211F(I)/RTL8211FD(I)使用最先進(jìn)的DSP技術(shù)和模擬前端(AFE)通過UTP電纜實現(xiàn)高速數(shù)據(jù)傳輸和

2023-05-15 10:16:51 44

44 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布與臺積電攜手,針對臺積電 N16 工藝 79GHz 毫米波設(shè)計參考流程,優(yōu)化 Cadence Virtuoso 平臺

2023-05-09 15:04:43 1302

1302 對設(shè)計的功能進(jìn)行仿真驗證,需要激勵驅(qū)動,是動態(tài)仿真。仿真驗證工具M(jìn)entor公司的 Modelsim, Synopsys的VCS,還有Cadence的NC-Verilog均可以對RTL級的代碼進(jìn)行設(shè)計驗證,該部分稱為前仿真,接下來邏輯部分綜合之后再一次進(jìn)行的仿真可稱為后仿真。

2023-05-09 10:16:53 669

669

楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布,Cadence 數(shù)字和定制/模擬設(shè)計流程已通過 TSMC N3E 和 N2 先進(jìn)工藝的設(shè)計規(guī)則手冊(DRM)認(rèn)證。兩家公司還發(fā)

2023-05-09 10:09:23 708

708 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布推出基于 Cadence Integrity 3D-IC 平臺的新設(shè)計流程,以支持 TSMC 3Dblox 標(biāo)準(zhǔn)。TSMC

2023-05-09 09:42:09 615

615 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布推出基于 Cadence Virtuoso Design Platform 的節(jié)點到節(jié)點設(shè)計遷移流程,能兼容所有的臺積電先進(jìn)節(jié)點

2023-05-06 15:02:15 801

801 臺積電 3DFabric? CoWoS-S 硅中介層技術(shù)實現(xiàn),可提供超高的帶寬密度、高效的低功耗性能和卓越的低延遲,非常適合需要極高算力的應(yīng)用。Cadence UCIe IP 為Chiplet裸片到裸片通信

2023-04-27 16:35:40 452

452

盡管對于工程師而言目標(biāo)始終是以原始形式對SoC源RTL進(jìn)行原型化,但在原型化工作的早期,SoC設(shè)計必須進(jìn)行必要的修改,以適應(yīng)FPGA原型系統(tǒng)。

2023-04-26 09:48:13 747

747 日 —— 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布,推出新一代定制設(shè)計平臺 Cadence? Virtuoso? Stu

2023-04-20 15:52:13 508

508

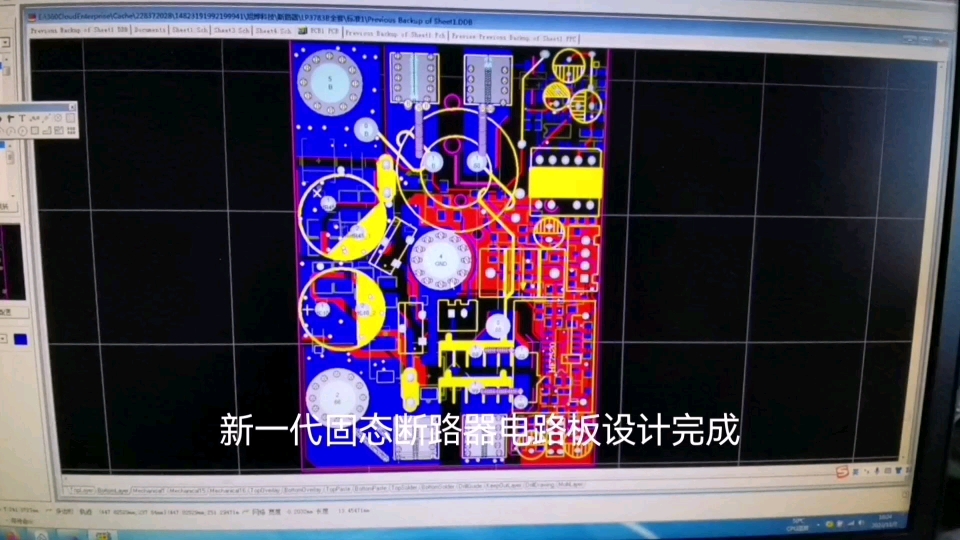

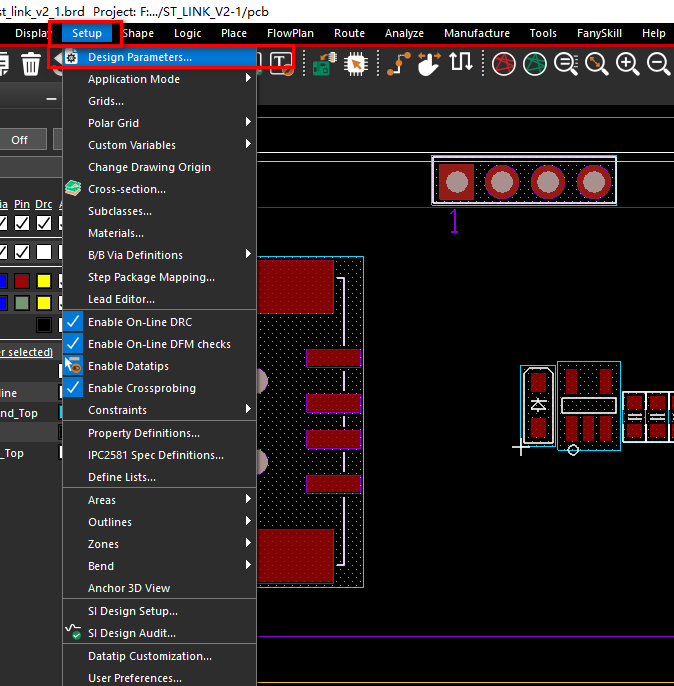

:CDNS)今日宣布推出CadenceAllegroXAItechnology,這是Cadence新一代系統(tǒng)設(shè)計技術(shù),在性能和自動化方面實現(xiàn)了革命性的提升。這款A(yù)I新產(chǎn)

2023-04-20 10:06:45 609

609

在Verilog中,IC設(shè)計工程師使用RTL構(gòu)造和描述硬件行為。但是RTL代碼中的一些語義,并不能夠準(zhǔn)確地為硬件行為建模。

2023-04-20 09:12:41 1210

1210 地址線和 32 個數(shù)據(jù)線,和外圍器件接口時帶到很困惑.不知有沒有高手看過周立功網(wǎng)站的提供的 lpc2104+RTL8019AS 的接口電路,SA0-SA4 和lpc2104 的哪個腳接在一起 請指點由

2023-04-19 16:51:23

楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布推出新產(chǎn)品 Cadence EMX Designer,這是一項無源器件綜合和優(yōu)化技術(shù),可在幾秒鐘內(nèi)提供通過設(shè)計規(guī)則檢查(DRC

2023-04-14 13:08:11 2162

2162 庫管理非常方便,對接生產(chǎn)采購很容易,畫出來的圖特別規(guī)整。所以大公司都喜歡用Cadence。然后利用PADS彌補Cadence的一些缺點。例如看圖不方便。

2023-04-10 09:44:38 1554

1554 Cadence 新一代系統(tǒng)設(shè)計技術(shù),在性能和自動化方面實現(xiàn)了革命性的提升。這款 AI 新產(chǎn)品依托于 Allegro X Design Platform 平臺,可顯著節(jié)省 PCB 設(shè)計時間,與手動設(shè)計電路板相比,在不犧牲甚至有可能提高質(zhì)量的前提下,將布局布線 (P&R) 任務(wù)用時從數(shù)天縮短至幾分鐘。

2023-04-07 10:27:59 608

608 在默認(rèn)情況下,SpinalHDL在生成代碼時會同時生成一個bin文件及一個RTL代碼文件。在RTL代碼中,會通過readmemb函數(shù)來載入初始化內(nèi)容

2023-04-01 15:27:59 521

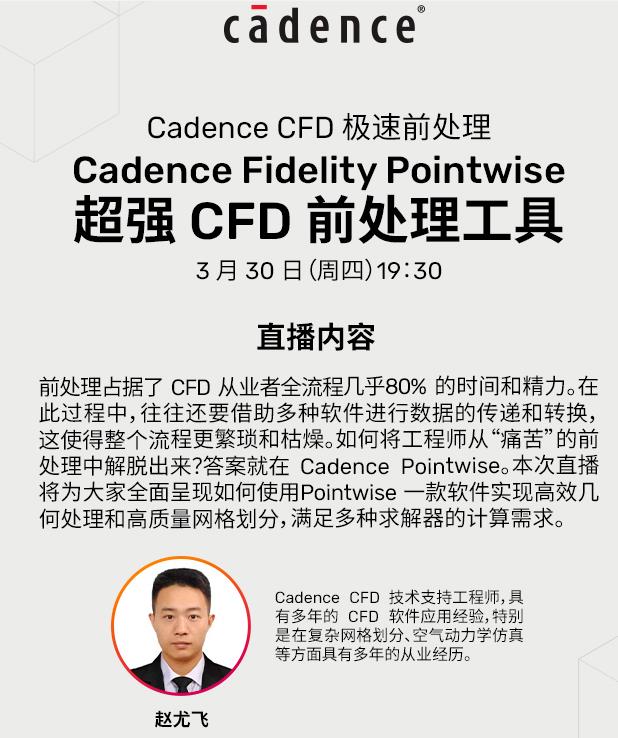

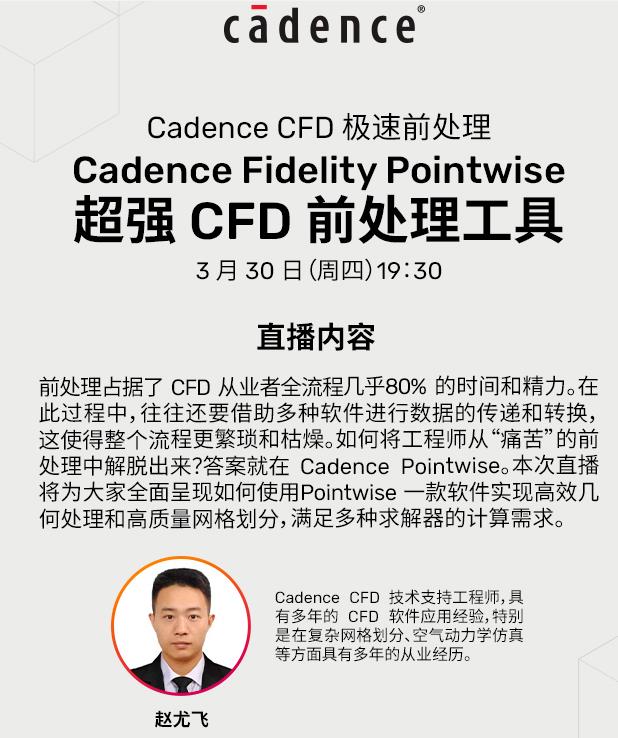

521 Cadence Pointwise。 本次直播將為大家呈現(xiàn)如何使用 Pointwise 這款軟件實現(xiàn)高效幾何處理和高質(zhì)量網(wǎng)格劃分,滿足多種求解器的計算的整體流程。 直播時間 2023 年 3 月 30

2023-03-30 14:50:37 1078

1078

CADENCE LIRARIES/INTRFC MAINT

2023-03-30 12:03:04

RTL8382L-VB-CG

2023-03-29 21:46:25

RTL8316E-CG

2023-03-29 21:41:56

RTL8367RB-CG

2023-03-29 17:32:59

RTL8821CU-CG

2023-03-28 18:07:42

在使用cadence進(jìn)行電子電路原理圖設(shè)計時,突然發(fā)現(xiàn)一個問題,那就是cadence添加和導(dǎo)出原理圖封裝庫的方式與altium designer還完全不一致。

2023-03-26 17:44:55 9021

9021

電子發(fā)燒友App

電子發(fā)燒友App

評論