在各種測試工作中,碼流的傳輸是必不可少的,常用的接口有:異步串行接口(ASI)、串行數(shù)字接口(SDI)、同步并行接口(SPI)、同步串行接口(SSI)。其中,ASI與SDI接口因為連線簡單(只需一根同軸電纜線傳輸),傳輸距離長,抗干擾能力強(qiáng),輸入反射損耗較小等原因被廣泛應(yīng)用為碼流的傳輸接口。

PC機(jī)是各種測試過程中最常用的測試工具,作為PC機(jī)最常用的接口的通用串行總線USB,因為標(biāo)準(zhǔn)統(tǒng)一,支持熱插拔,可連接多個設(shè)備等優(yōu)點,逐漸成為測試工具的常用接口,若能實現(xiàn)USB接口與傳輸碼流的ASI/SDI接口的連接,將給數(shù)字電視測試工作帶來極大便利。

設(shè)計ASI/SDI碼流播放器的目的是設(shè)計出手機(jī)大小的電路板,一端是USB接口,另一端是則ASI/SDI接口,通過FPGA、UB2.0等芯片實現(xiàn)ASI/SDI接口與USB接口之間的轉(zhuǎn)換,以達(dá)到TS流的錄制與播放和對碼流進(jìn)行分析的目的。

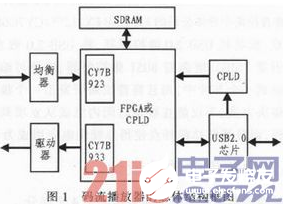

1 碼流播放器的整體結(jié)構(gòu)設(shè)計

目前,DVB-ASI接口的實現(xiàn)大多采用Cypress公司的CY78933和CY78923芯片與CPLD或FPGA相結(jié)合的方案,這種方法固然可以實現(xiàn)ASI信號的收發(fā),但芯片費(fèi)用和PCB面積的占用卻是數(shù)字電視前端設(shè)備追求低成本和微型化的障礙,針對這種情況,文中設(shè)計的ASI信號接收與發(fā)送系統(tǒng)采用同軸電纜作為其底層物理信道,用FPGA芯片完成了CY7B933和CY78923芯片的ASI信號的接收與發(fā)送功能,可有效節(jié)約成本,降低PCB的設(shè)計難度,并可用FPGA芯片完成其他功能。

國內(nèi)外絕大多數(shù)是使用PCI或PCI-E接口,只能在臺式機(jī)或服務(wù)器上使用,隨著PC機(jī)的微型化,筆記本電腦的普及,PCI或PCI-E接口已經(jīng)無法完全滿足數(shù)字電視測試工作的需求,所以本設(shè)計使用的是最通用的USB接口,大大降低數(shù)字電視測試工作的難度。

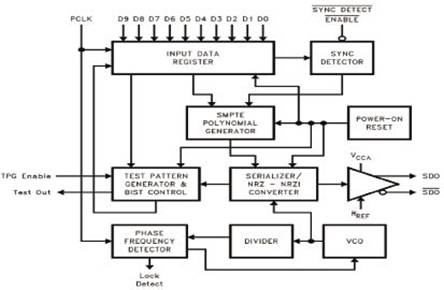

如圖1所示,ASI/SDI碼流播放器的設(shè)計是基于FPGA和USB2.0芯片來實現(xiàn)的,集成度高,方便輕巧,能在PC機(jī)上輕松實現(xiàn)碼流捕捉,分析,監(jiān)控和播放ASI/SDI數(shù)字流,現(xiàn)場錄制和分析MPEG-2碼流,還可以作為便攜式的演示設(shè)備。

2 碼流播放器的硬件模塊設(shè)計

使用FPGA實現(xiàn)了CY7B933和CY7B923芯片的功能,節(jié)約了大量成本;同時,用Cypress公司的USB2.0芯片CY7C68013A替代PCI或PCI-E接口,因為傳輸?shù)拇a率較大,理論最大值為216 Mb,F(xiàn)PGA內(nèi)部資源RAM資源無法滿足要求,添加一個SDRAM作為緩存,緩沖數(shù)據(jù),以免丟數(shù)。

另外,由于選擇了低端的FPGA芯片,在編寫版本FPGA程序時發(fā)現(xiàn),其內(nèi)部邏輯資源較少,無法裝下實現(xiàn)ASI和SDI的全部功能程序,而且實際工程應(yīng)用中并不需要同時實現(xiàn)ASI和SDI的功能,故添加了一個的CPLD,實現(xiàn)FPGA的PS模式的動態(tài)加載功能。

2.1 均衡器/驅(qū)動器

輸入前端均衡器(Equaliser)選用的GS9064是第二代的雙向性高速集成電路,均衡和恢復(fù)收到的信號(75Ω同軸電纜,速率從143 Mb/s到540 Mb/s),支持SMPTE 344 M和SMPTE 259 M標(biāo)準(zhǔn),且270 Mb/s時性能最佳。具有自動檢測線長并根據(jù)信號強(qiáng)弱自動匹配均衡的功能,也可根據(jù)特定需要設(shè)置均衡參數(shù)。

Driver選擇CLC001驅(qū)動器,CLC001是集成高速電纜驅(qū)動器,可用來傳輸SMPTE 259M標(biāo)準(zhǔn)的串行數(shù)字視頻和ITU-TG.703標(biāo)準(zhǔn)的串行數(shù)字?jǐn)?shù)據(jù)(75Ω傳輸線,速率高達(dá)622Mb/s)。CLC001輸出功耗小,十分適合長距離高速傳輸。

2.2 數(shù)據(jù)處理

輸入輸出信號都經(jīng)由差分線進(jìn)入FPGA,出于成本的考慮,選擇性價比較高的Altera公司生產(chǎn)的低端Cyclone I系列EP1C6F256C6。在FPGA內(nèi)部實現(xiàn)ASI/SDI輸入輸出的控制,信號的串/并轉(zhuǎn)換,碼流分析,數(shù)據(jù)緩存(讀寫SDRAM),碼流傳輸?shù)裙δ堋?/p>

因為TS流數(shù)據(jù)量較大,同樣出于成本的考慮,選擇在FPGA上外掛一個SDRAM,作為緩存(如果使用高性能FPGA,就可以使用FPGA內(nèi)部RAM資源,但是成本較高)。FPGA程序的編寫,尤其是控制SDRAM讀寫作為緩存的部分,是本設(shè)計的難點之一。

2.3 USB微控制器

FPGA控制的輸入輸出碼流都經(jīng)由USB2.0芯片傳送至PC機(jī)。賽普拉斯半導(dǎo)體公司的EZ-USB FX2LP(CY7C68013A)是高集成、低功耗USB 2.0微控制器,將USB 2.0收發(fā)器、串行接口引擎(SIE)、增強(qiáng)型8051微控制器,以及可編程外設(shè)接口集成到一個芯片中,而且賽普拉斯研發(fā)出一個極具成本優(yōu)勢的解決方案,不僅能在極短時間內(nèi)完成從立項到投放市場的過程,而且其低功耗特點使得總線供電應(yīng)用成為可能。

3 碼流播放器的軟件設(shè)計

碼流播放器軟件系統(tǒng)主要包括以下4個部分。

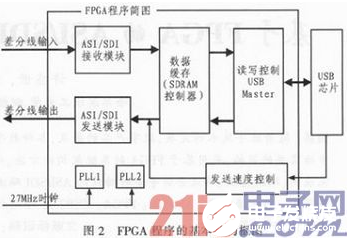

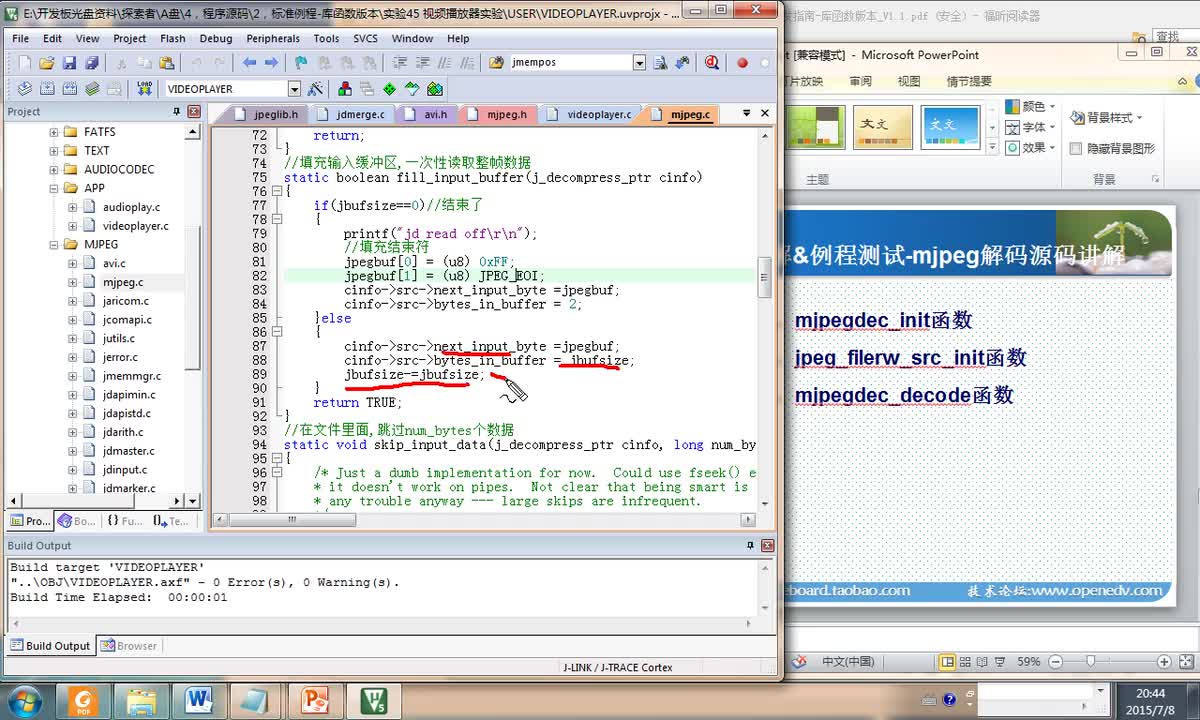

3.1 FPGA程序功能模塊

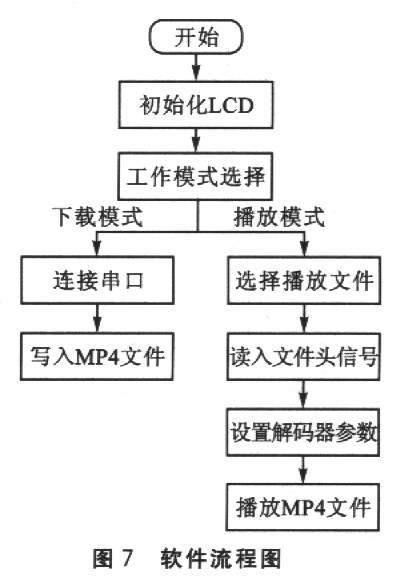

如圖2所示,系統(tǒng)輸入時鐘為27 MHz,由兩個PLL鎖相環(huán)倍頻得到270 MHz,135 MHz和兩個相位差90度的337.5 MHz時鐘。其中270 MHz是為ASI Transmitter提供,其余3個均為ASI Receiver所需。

ASI Transmitter模塊的作用是,先進(jìn)行8B10B編碼,再把并行的27 MHz數(shù)據(jù)按照標(biāo)準(zhǔn)協(xié)議轉(zhuǎn)成270 MHz的串行數(shù)據(jù)。

ASI Receiver模塊則是ASI Transmitter的逆過程,先進(jìn)行串并轉(zhuǎn)換,用5倍時鐘采樣對數(shù)據(jù)進(jìn)行校準(zhǔn),然后分析同步包頭等信息,再進(jìn)行8B10B解碼,得到8位并行數(shù)據(jù)。

SDI部分與ASI十分相似,不重復(fù)介紹。

碼流播放器是全雙工設(shè)計,但是,因為FPGA與USB芯片之間的數(shù)據(jù)傳輸管腳是復(fù)用的,不能同時雙向傳輸。所以,在FPGA與USB芯片之間需要不停的快速切換讀和寫(1μs切換一次),即可實現(xiàn)“同時”發(fā)送和接收數(shù)據(jù)。

同時發(fā)送和接收數(shù)據(jù)時,受切換的影響,速率減半,且USB接口時鐘最大支持僅為48 MHz,所以當(dāng)收發(fā)同時進(jìn)行的時候,傳輸速度無法達(dá)到理論最大的216 Mbps。如果只是單向發(fā)送或者接受數(shù)據(jù),系統(tǒng)會自動切換成接收或者發(fā)送模式,基本可以達(dá)到數(shù)據(jù)傳輸理論最大值的216 Mbps。

發(fā)送碼流時,可以在上位機(jī)軟件的操作界面上輸入發(fā)送速率(從0到216,000,000 bps),上位機(jī)通過USB芯片,把發(fā)送速率傳到FPGA,F(xiàn)PGA就可以按照所得速率,精確控制發(fā)送碼流的速度。

為了達(dá)到碼流收發(fā)的理論最大值,在FPGA上外掛一個RAM,通過對RAM的讀寫的控制,實現(xiàn)先入先出(FIFO)的緩存功能。FPGA對RAM的讀寫控制是編寫Verilog HDL的難點之一,為了節(jié)約成本,碼流播放器選擇價格低、體積小、速度快、容量大的SDRAM,給Verilog程序編寫增加了不少難度。相比控制簡單的SRAM,DRAM每隔一段時間必須自刷新和預(yù)充,且數(shù)據(jù)線與行列地址都是復(fù)用的,切換讀寫時極容易出現(xiàn)時序上的偏差,出現(xiàn)寫錯,讀錯,重復(fù)讀,丟數(shù)等等問題。

SDRAM上電復(fù)位后,計數(shù)器控制在200μs后,進(jìn)行SDRAM初始化配置,對所有BANK進(jìn)行預(yù)充,接著是多個Reflash,然后進(jìn)入SDRAM工作模式設(shè)置。之后進(jìn)入空閑狀態(tài),執(zhí)行讀寫數(shù)據(jù)和自刷新等任務(wù)。

由于USB程序設(shè)置為Slave-FIFO模式,將FIFO的空滿狀態(tài)發(fā)送到FPGA,而FPGA作為Master,需要根據(jù)USB內(nèi)FIFO的空滿信號,綜合SDRAM的空滿狀態(tài),對讀寫狀態(tài)進(jìn)行判斷,并給出讀寫使能。

3.2 USB收發(fā)器及控制器固件程序

賽普拉斯公司提供了非常好的程序框架,免去了用戶自己編寫一些通用性比較強(qiáng)、模式化的程序。在框架的基礎(chǔ)上,用戶只需在相應(yīng)的地方寫相應(yīng)的代碼即可完成USB工作。

碼流傳輸因為數(shù)據(jù)量大,而且傳輸和接受數(shù)據(jù)上又沒有帶寬和間隔時間要求所以采用的是Bulk傳輸方式。

計算機(jī)和USB外設(shè)端點0(EP0)之間的傳輸是典型的控制傳輸,主要進(jìn)行查詢配置和給USB設(shè)備發(fā)送通用的命令;控制傳輸是雙向傳輸,數(shù)據(jù)量通常較小,而且數(shù)據(jù)傳送是無損性的。

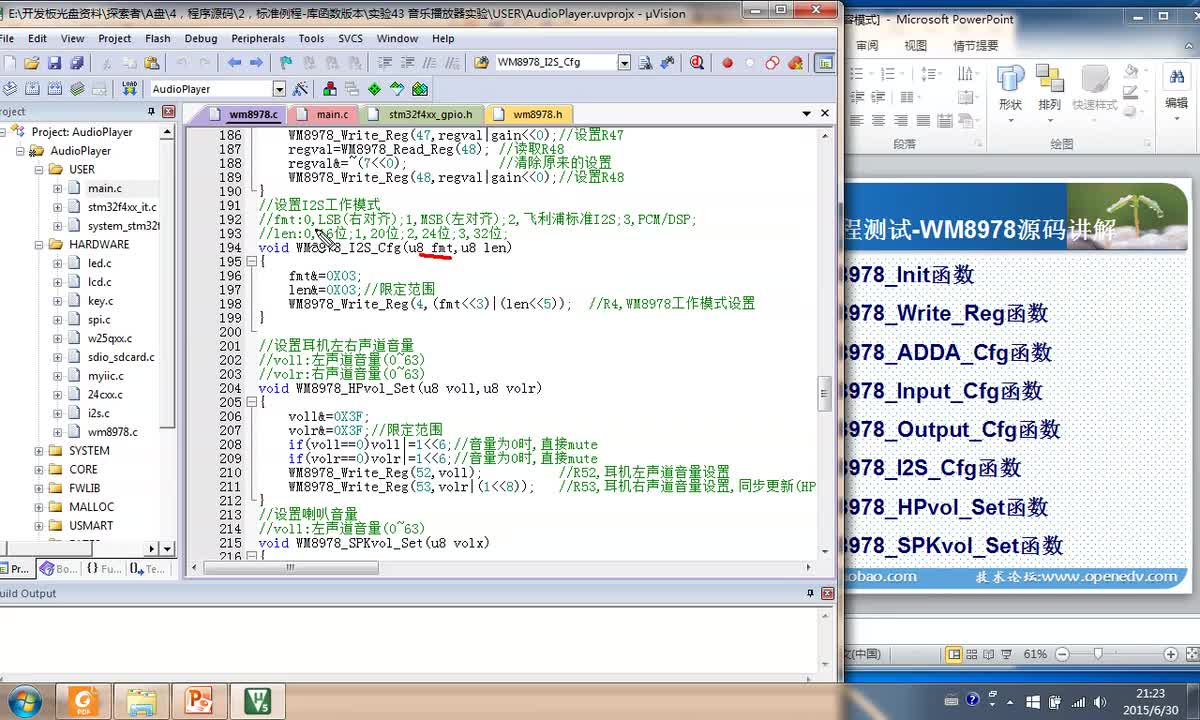

3.3 CPLD動態(tài)加載配置程序

CPLD通過USB芯片,接收上位機(jī)傳輸過來的FPGA配置文件(.rbf格式),然后按照固定的時序?qū)PGA進(jìn)行配置。需要注意的是,在動態(tài)加載過程中,F(xiàn)PGA的模式選擇需配置為PS模式,不同的FPGA芯片之間配置模式略有不同,電位要求也不盡相同。

配置過程為:CPLD將nCONFIG置低再拉高來初始化配置;等待FPGA返回應(yīng)答信號nSTATUS,檢測到nSTATUS變高后,將配置數(shù)據(jù)和移位時鐘分別送到DATA0和DCLK管腳;送完配置數(shù)據(jù)后,檢測CONF_DONE是否變高,若未變高,說明配置失敗,應(yīng)該重新啟動配置過程。在檢測CONF_D ONE變高后,根據(jù)器件的定時參數(shù)再送一定數(shù)量(40個)的時鐘到DCLK管腳;待FPGA初始化完畢后進(jìn)入用戶模式。

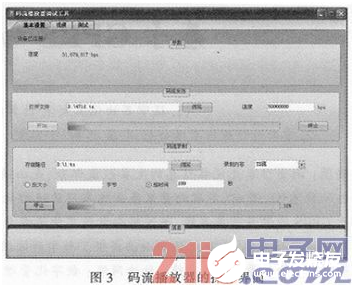

3.4 PC界面控制程序

由C#編寫的控制界面,主要實現(xiàn)與USB芯片間的碼流傳輸,發(fā)送控制命令,接收碼流分析結(jié)果等信息,如圖3所示。

4 結(jié)論

碼流播放器是USB供電,無需額外電源,輕巧方便攜帶;能輕松捕捉,播放,錄制和分析碼流;精確控制碼流發(fā)送速度;全雙工,同時進(jìn)行碼流的發(fā)送和接收。

用戶界面簡單明了。發(fā)送時選擇發(fā)送文件,再輸入發(fā)送速度,點擊開始即可;接收時選擇存儲路徑和錄制內(nèi)容,再選擇錄制方式,點擊開始。同時,用戶界面還能實時接收到FPGA分析得到的各種碼流參數(shù)信息。目前,本文所介紹的碼流播放器已進(jìn)入穩(wěn)定性測試階段,各項功能也在不斷完善和優(yōu)化中。

碼流播放器的電路板僅為6 mm*9 mm,小巧輕便,方便攜帶;操作簡單,界面友好;因為設(shè)計時嚴(yán)格控制成本,價格低廉,性價比高,是數(shù)字電視專業(yè)人員理想的測試工具。

電子發(fā)燒友App

電子發(fā)燒友App

評論