經常涉及對寬帶模擬信號進行數據采集和存儲,以便計算機進一步進行數據處理。為了對高速模擬信號進行不失真采集,根據奈奎斯特定理, 采樣頻率必須為信號頻率的2 倍以上,但在電阻抗多頻及參數成像技術中正

2023-09-15 09:45:01 1054

1054

130 萬,所以最大系統門數為170 萬。結論:FPGA 等效門數估計方法可以是把FPGA 資源基本單元(如LUT+FF,ESB)和實現相同功能的標準門陣列相比得到FPGA 基本單元等效的門數,然后

2012-03-01 10:08:53

個。與針對每一電機來復制多芯片器件配置相比,在一個芯片上支持兩個電機能夠降低53%的成本。調整FPGASoC來支持更多的電機和集成驅動系統以及多種協議也很容易。關鍵點采用FPGASoC技術的設計團隊

2021-07-14 08:00:00

【作者】:陳世海;裴東興;張琦;【來源】:《電子設計工程》2010年02期【摘要】:針對數據采集系統高速長時間的采樣和后端數據傳輸及存儲能力有限的問題,提出基于FPGA的數據壓縮解決方案。同時為平滑

2010-04-24 09:05:21

FPGA中等效邏輯門概念數的計算方法有兩種,一是把FPGA基本單元(如LUT+FF,ESB/BRAM)和實現相同功能的標準門陣列比較,門陣列中包含的門數即為該FPGA基本單元的等效門數,然后乘以

2012-08-10 14:05:35

1.1 FPGA設計思想與技巧1.1.1 本節目錄1)本節目錄;2)本節引言;3)FPGA簡介;4)FPGA雙沿采樣之IDDR原語實現;5)結束語。1.1.2 本節引言“不積跬步,無以至千里;不積

2021-07-26 06:37:06

1.1 FPGA雙沿采樣之Verilog HDL實現1.1.1 本節目錄1)本節目錄;2)本節引言;3)FPGA簡介;4)FPGA雙沿采樣之Verilog HDL實現;5)結束語。1.1.2 本節

2021-07-26 07:44:03

數字外圍器件是什么?FPGA在外圍器件實現方面有什么作用?

2021-05-07 07:01:38

的數目之外,就是采用可編程邏輯器件,主要是FPGA芯片來實現。本課程以DSP設計在FPGA芯片上的開發為主線,遵照由淺入深的基本步驟和思路進行詳細講解,每一個知識點都給出了基于ISE(HDL語言

2009-07-21 09:22:42

節省功耗的特性的實現和各種最少功耗數據存儲技術的實現。除此之外,設計中采用一些低功耗技巧,也可以降低靜態功耗。 IGLOO具有功耗友好的器件架構,能提供靜態、睡眠、Flash*Freeze功耗模式

2020-05-13 08:00:00

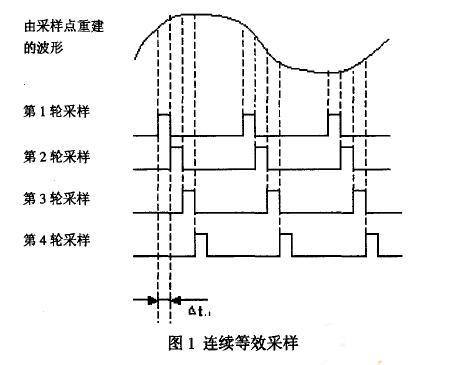

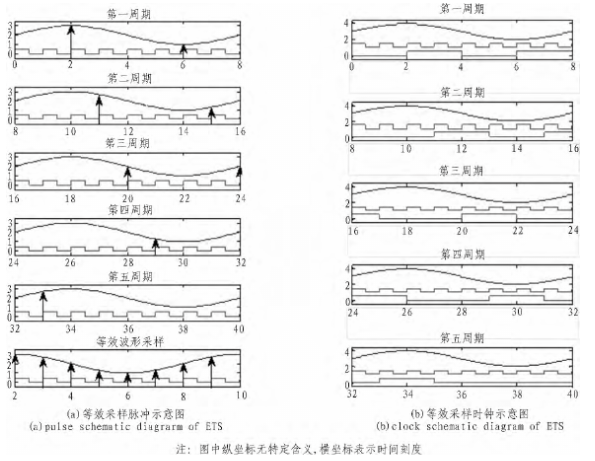

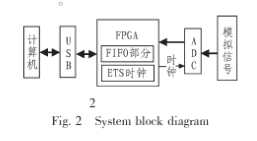

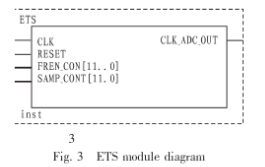

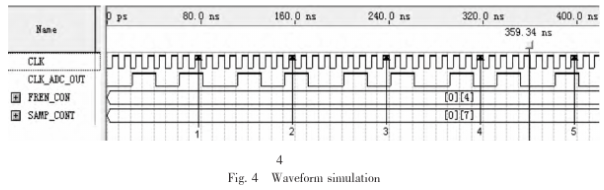

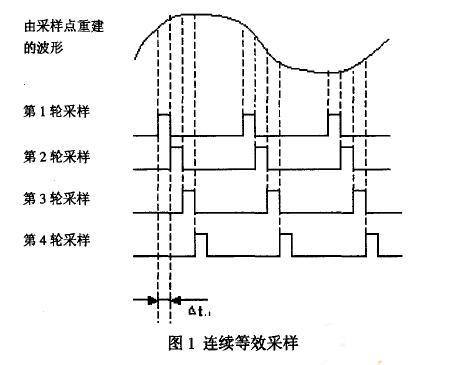

,分頻后的時鐘波形在時鐘的上升沿對信號進行采樣,那么就會得到如圖1(a)中所表示的等效時間采樣。等效時間采樣技術的原理作用及采用FPGA器件實現系統的設計圖1 等效時間采樣示意圖2 、基于FPGA的等效

2020-10-21 16:43:20

等效時間采樣中應用的ADC,應該注意哪些問題呢?一般采樣速率有何限制?對于ADC的模擬輸入帶寬呢?

2023-12-25 06:42:31

的AD985X系列)。從而為電路設計者提供了多種選擇。但在某些場合,專用DDS芯片在控制方式、置頻速率等方面與系統的要求仍然有很大差距,在這種情況下,采用高性能的FPGA器件設計符合自己需要的DDS

2019-06-18 06:05:34

通過ARM處理器建立操作系統實現任務調度。盡管采用DSP和ARM芯片可使系統的運算能力和管理事務的能力得到很大增強,但是構成完整的數據采集系統通常還需要外部邏輯控制器件,尤其不能將數據采集和刺激信號源

2019-05-16 07:00:09

1. 為什么要使用FPGA實現在全控型電力電子開關器件出現以后,為了改善交流電動機變壓變頻調速系統的性能,科技工作者在20世紀80年代開發出了應用脈寬調制(PWM)技術的變壓變頻器,由于它的優良

2022-01-20 09:34:26

XC2S200型FPGA器件實現。采用Spansion公司的NOR Flash存儲器來存放配置文件,其型號為S29GL512N,容量為512 Mb。系統總體框圖如圖3所示。上位機軟件包括Flash燒寫

2019-05-30 05:00:05

的測試技術研究,提出了采用J750EX測試系統的DSIO及其他模塊實現對SRAM VDSR16M32進行電性測試及功能測試。另外,針對SRAM的關鍵時序參數,如TAA(地址變化到數據輸出有效時間

2019-07-23 08:26:45

基于64通道(每通道等效50K)信號采集的需要,采用ad7606b+mux507的方式做了一個模塊,使用fpga控制采樣。測試時采用了400K的通道切換速度,發現通道切換之后,信號的建立時間

2023-12-01 07:20:41

基于magnum II測試系統的測試技術研究,提出了采用magnum II測試系統的APG及其他模塊實現對MRAM VDMR8M32進行電性測試及功能測試。其中功能測試包括全空間讀寫數據0測試,全空間讀寫

2019-07-23 07:25:23

只需要三分之一的器件面積。采用競爭技術和工具嘗試實現PCIe內核的用戶會發現,使用Altera硬核IP結合Qsys系統集成工具,在設計和調試時間上平均能夠節省6個星期的時間。Altera還在FPGA中

2015-02-09 15:02:06

什么是過采樣技術?STM32 ADC過采樣技術有何作用?

2021-10-21 06:36:13

處理器的數目之外,就是采用可編程邏輯器件,主要是FPGA芯片來實現。本課程以DSP設計在FPGA芯片上的開發為主線,遵照由淺入深的基本步驟和思路進行詳細講解,每一個知識點都給出了基于ISE(HDL語言

2009-07-21 09:20:11

處理器的數目之外,就是采用可編程邏輯器件,主要是FPGA芯片來實現。本課程以DSP設計在FPGA芯片上的開發為主線,遵照由淺入深的基本步驟和思路進行詳細講解,每一個知識點都給出了基于ISE(HDL語言

2009-07-24 13:07:08

項目名稱:等效隨機采樣的數字存儲式示波器試用計劃:利用fpga驅動高速adc模塊,構成數字存儲式示波器

2017-06-20 11:19:18

,同時具有開發時間較短、成本較低的優勢。基于FPGA實現的數字信號處理系統具有較高的實時性和嵌入性,并能方便地實現系統集成與功能擴展。基于FPGA的硬件實現FFT通常有兩種方法:(1)并行方法,其采用

2019-07-03 07:56:53

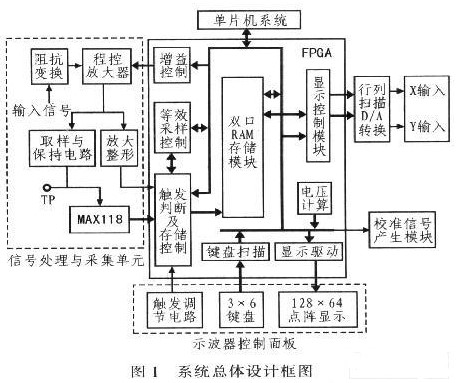

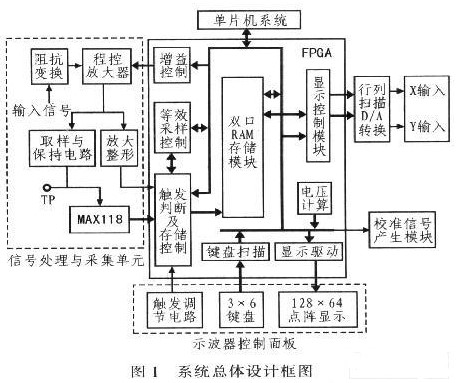

特點,采用數據流控制的方法實現了信息的并行處理,可以更加有效的實現多通道振動信號采集;同時為了提高數據的可靠性采用時間標定的方法進行數據的存儲和校驗。本文第一節介紹了該系統的整體設計方案,第二節

2019-07-01 06:11:15

高速、超寬帶信號采集技術在雷達、天文和氣象等領域應用廣泛。高采樣率需要高速的模/數轉換器(ADC)。目前市場上單片高速ADC的價格昂貴,分辨率較低,且采用單片超高速ADC實現的數據采集對FPGA的性能和PCB布局布線技術提出了嚴峻的挑戰。

2019-11-08 06:34:52

的功能,而且還可以大大縮短設計時間,減少PCB的面積,提高信號的傳輸質量,提高系統的可靠性,增加設計的靈活性和可維護性。本文采用FPGA技術實現一個MCU與串行通信外設進行簡易通信的平臺,一方面了解了計算機的一些控制原理和工作流程;另一方面可以了解利用FPGA進行電子設計的優越性。

2019-07-08 06:28:38

。為了實現高速、連續采樣的數據采集系統,本文介紹了一種基于 FPGA +AD7609的數據采集系統的構成及技術實現。采用 FPGA 作為主模塊,AD7609為數據采集模塊,并設計了硬件實現電路。實驗測試

2018-08-09 14:28:00

我想知道基于FPGA出租車計價系統實現的技術框架是什么?

2016-04-26 10:36:46

個。與針對每一電機來復制多芯片器件配置相比,在一個芯片上支持兩個電機能夠降低53%的成本。調整FPGASoC來支持更多的電機和集成驅動系統以及多種協議也很容易。關鍵點采用FPGASoC技術的設計團隊

2021-07-12 08:00:00

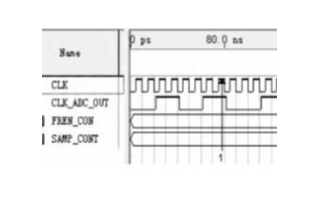

采集系統,A/D建立穩定的工作狀態需要相當長時間,頻繁地改變A/D的工作狀態會影響測量的精度,嚴重時會造成信號的失真。為此,同步命令不直接作用于高速A/D,而是用FPGA產生A/D采樣時鐘信號,并根據

2021-07-05 11:23:33

使用。 本文基于快速傅里葉IP核可復用和重配置的特點,實現一種頻域的FPGA數字脈壓處理器,能夠完成正交輸入的可變點LFM信號脈沖壓縮,具有設計靈活,調試方便,可擴展性強的特點。 1 系統功能硬件

2018-11-09 15:53:22

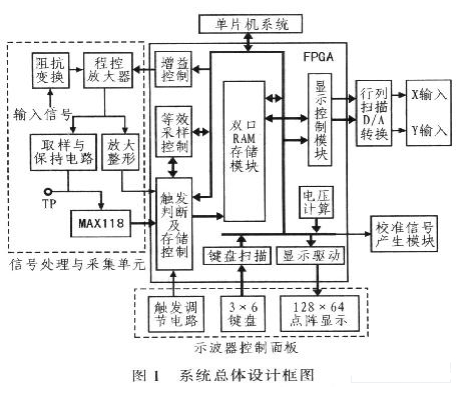

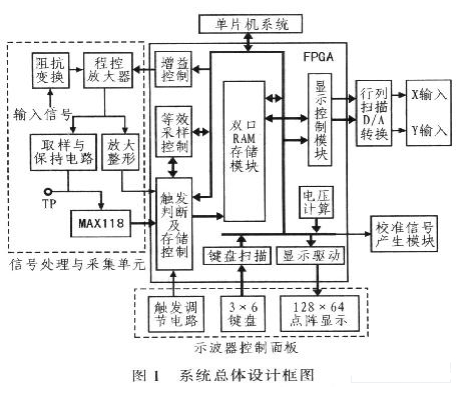

本文介紹一種基于等效和實時采樣的數字示波器設計。

2021-05-17 06:00:57

dB時能測到雷達信號,使雷達的有效作用間隔進步。本文主要先容基于DSP和FPGA技術的低信噪比情況下雷達信號的檢測。1 設計思想 本技術的設計思想主要是通過對接收到的雷達信號進行高速A/D采樣,然后

2018-08-15 09:43:14

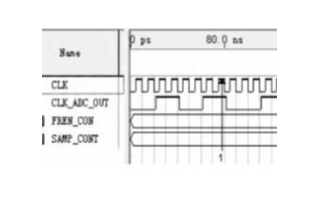

本文針對傳統實時操作系統內核占用系統資源、影響系統實時性的問題,提出了用單獨的硬件電路實現實時操作系統中的系統調用和任務調度器的方案。重點給出了采用FPGA實現μC/OS-Ⅱ任務管理模塊的過程。仿真結果表明,任務管理的硬件實現保持了系統調用的正確性,同時減少了系統調用的執行時間、降低了處理器系統開銷。

2021-04-26 06:14:59

如何采用FPGA實現視頻監視?

2021-04-29 06:24:06

如何采用A3P250器件實現汽車油改氣系統的設計?

2021-04-28 06:19:54

如何采用Altera的CPLD器件實現時間統一系統的B碼源設計?

2021-05-07 06:21:24

采用PCM編碼原理及FPGA編程技術實現PCM數字基群接口傳輸低速數據的接入

2021-04-30 07:09:04

本文介紹了采用Xilinx公司的Spartan-3 FPGA實現通用視頻采集系統的設計方案。

2021-06-08 06:34:30

本文選用FPGA實現數據處理、邏輯控制,充分利用PC機,結合Labwindows圖形化上層應用軟件界面生成的虛擬測試系統具有較強的競爭力。本系統在FPGA單板單片主控器件控制下,實現兩路獨立、幅值可控的信號發生器,一路虛擬存儲示波器,具有外部觸發信號和采樣時鐘的16路高速邏輯分析儀。

2021-05-12 06:58:02

數字化測量系統具有與上述不同的一些特點,需要考慮以下一些技術特性。1.最高數字化速率(采樣速率)最高數字化速率是單位時間 對模擬輸入信號的采樣數。常以每秒采樣樣本點數(Sample/second

2018-01-25 11:38:18

等效時間采樣中應用的ADC,應該注意哪些問題呢?一般采樣速率有何限制?對于ADC的模擬輸入帶寬呢?

2018-11-26 09:46:09

實時技術到底有什么意義?到底選擇實時采樣還是等效時間采樣?

2021-05-10 06:57:27

IJF編碼是什么原理?如何實現IJF編碼?采用FPGA和集成器件來實現IJF編碼

2021-04-13 06:56:04

根據軟件無線電的思想,用可編程器件FPGA 實現了QPSK 解調,采用帶通采樣技術對中頻為70MHz 的調制信號采樣,通過對采樣后的頻譜進行分析,用相干解調方案實現了全數字解調

2009-08-27 11:00:14 68

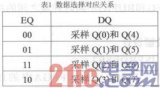

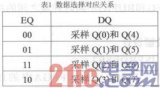

68 在數字示波器技術中!常用的采樣方法有兩種" 實時采樣和等效采樣# 實時采樣通常是等時間間隔的!它的最高采樣頻率是奈奎斯特極限頻率# 等效采樣$3456789:;<$8=>96;?% 是指

2010-07-08 16:30:04 42

42 1. 把FPGA 基本單元(如LUT+FF,ESB/BRAM)和實現相同功能的標準門陣列比較,門陣列中包含的門數即為該FPGA 基本單元的等效門數,然后乘以基本單元的數目就可以得到FPGA 門數

2010-07-19 16:49:20 22

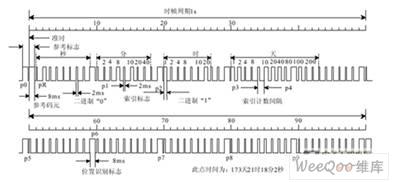

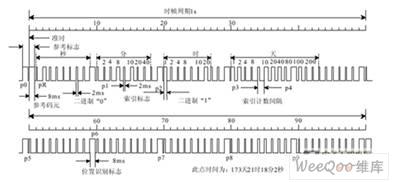

22 本文在介紹了等效采樣的原理和方法的基礎上提出了一種基于EDA技術的實現方案。借助高速發展的EDA技術,可以方便地產生采樣信號,大大簡化采樣觸發電路,解決了傳統等效采樣

2010-08-03 10:48:54 19

19 摘要:介紹了基于單片機系統的精密時鐘發生電路對高頻信號(1MHz~80MHz)進行等效采樣的方法,設計并實現一個模擬帶寬為1Hz~80MHz的簡易數字示波器。

2006-03-24 13:13:02 1373

1373

用FPGA實現音頻采樣率的轉換

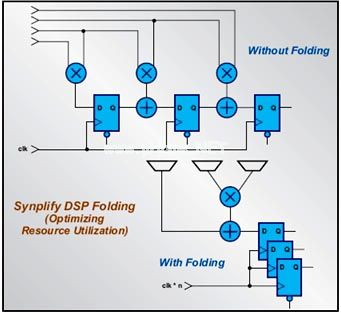

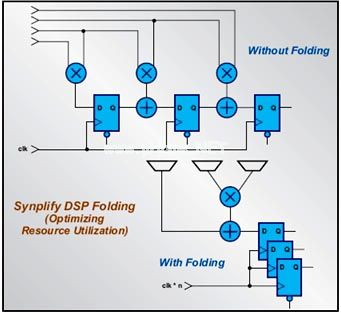

如今,即使低成本FPGA也能提供遠遠大于DSP的計算能力。目前的FPGA包含專用乘法器甚至DSP乘法/累加(MAC)模塊,能以550MHz以上的時鐘速度處理

2010-03-01 10:50:05 3788

3788

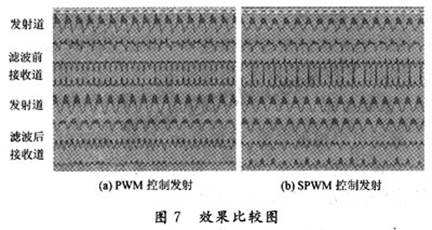

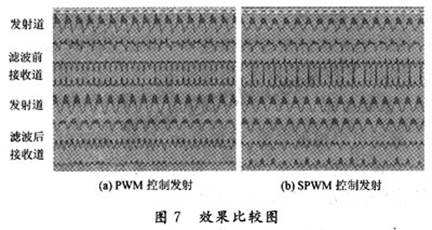

采用FPGA的SPWM變頻系統設計

0 引 言由于脈寬調制技術是通過調整輸出脈沖的頻率及占空比來實現輸出電壓的變壓

2010-03-02 10:46:39 1175

1175

采用FPGA的可編程電壓源系統原理及設計計

概述:介紹一種基于FPGA的可編程電壓源系統的設計與實現。采用FPGA為控制芯片,應用Quartus

2010-03-22 14:31:44 2096

2096

捅要:為了實現是彈武器瞄準自動化,本文設計了基于DSP和FPGA的高速高精確度雙通道CCD圖像采集系統,采用QUartuBn在AJtera的FPGA器件CYCLONEII上設計了CCD驅動時序電路,采用PsPICE設計了可以

2011-02-25 13:48:05 187

187 提出了一種應用于便攜式數字存儲示波器等效采樣的實現方案。詳細講述了FPGA和微處理器LPC2138對高頻信號隨機等效采樣的處理過程,利用一種全新的方法即主要利用FPGA內部邏輯單元完成對觸發時刻到與下一采樣時刻的時間間隔的測量。給出了FPGA對采樣點的處理方

2011-03-16 12:12:35 126

126 為了降低系統成本和功耗, 采用基于ARM 系統的精密時鐘發生電路對高頻信號(6. 25MHz~100MHz) 進行等效采樣, 配合高速AD、F IFO 和FPGA 電路設計并實現一個手持式存儲示波表。該樣機在人機

2011-06-21 16:33:41 114

114 對超寬帶系統中采樣門前置電路進行了理論分析和系統研究,對其產生電路中輸入信號的幅度和寬度、采樣信號的寬度和上升時間、等效采樣的時間間隔等因素的影響進行了分析,給出

2011-10-11 14:58:57 28

28 信系統器件所提供的接口技術種類繁多,令人困惑。設計者應根據所需功能選擇器件,采用FPGA解決當中的接口和互用性問題。

2012-05-22 11:26:47 1471

1471 2015-08-24 18:14:00 18

18 基于FPGA多通道采樣系統設計資料,有興趣的同學可以下載學習

2016-04-28 14:29:56 48

48 基于FPGA實現變采樣率FIR濾波器的研究

2017-01-08 15:59:09 19

19 基于FPGA的高速多通道AD采樣系統的設計與實現_徐加彥

2017-01-18 20:23:58 12

12 等效采樣

2017-03-04 17:52:58 13

13 在現代電子測量、通訊系統以及生物醫學等領域,經常涉及對寬帶模擬信號進行數據采集和存儲,以便計算機進一步進行數據處理。為了對高速模擬信號進行不失真采集,根據奈奎斯特定理,采樣頻率必須為信號頻率

2017-11-16 16:12:18 7

7 針對LVDS接口,研究并實現了一種基于FPGA的LVDS過采樣技術,重點對LVDS過采樣技術中系統組成、ISERDESE2、時鐘采樣、數據恢復單元、時鐘同步狀態機等關鍵技術進行了描述

2017-11-18 05:13:01 6915

6915

項目背景及可行性分析 1.項目名稱、項目的主要內容及目前的進展情況 項目名稱: 基于FPGA的高速采樣顯示電路的實現 主要內容:通過對被測信號的實時采樣,利用等效采樣原理,可以將采樣率為1MHz等效

2017-11-22 11:18:29 14

14 由于存在內部熱噪聲、孔徑抖動和渡越時間不確定性等因素,面臨采樣速度和精度相互制約的影響,出現了瓶頸。而由多通道時間交織ADC(Time-lnterleaved ADC.TIADC)采用M個相同型號的ADC單元依次交替完成采樣。理論上,TIADC的采樣率可以到達單ADC的M倍,同時保持采樣精度基本不

2018-02-07 13:51:17 2

2 誤差、增益誤差以及時間相位誤差將嚴重降低數據采集系統性能[2]。基于數字信號處理方法的數字后端修正技術可有效抑制以上失配造成的失真。近年來,已有文獻應用FPGA實現數字后端修正技術。文獻[3]采

2018-06-25 11:45:00 7047

7047

數據采集系統的總體架構如圖1所示,其中PCI核、DMA控制器與A/D控制器均在FPGA內部實現。為實現多路并行采樣,可選用多片A/D器件并行處理的方式,在FPGA的高速狀態機控制下,完成模擬信號經過

2018-08-28 10:16:07 12734

12734

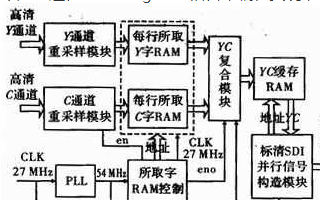

選擇實時采樣和等效采樣相結合的方式,實時采樣速率小于1 MS/s,水平分辨率至少為20點/div,故系統50 kHz以下采用實時采樣方式,而50 kHz~10 MHz采用等效時間采樣方式,最高等效采樣速率可達到200 Ms/s。

2019-05-05 08:19:00 2266

2266

隨著電子技術的發展,對遙測信號的幀結構的可編程度、集成度的要求越來越高,用于時間統一系統的B碼源的設計也趨于高度集成化。為了適應現代靶場試驗任務的要求,我們采用Altera的CPLD器件,將用于產生

2019-02-06 09:32:00 2555

2555

有兩種等效采樣的方法:隨機等效采樣和連續等效采樣。連續等效采樣在每個觸發捕獲一個樣值,而不依賴于時間/格的設置和掃描速度,每發現一個觸發經過一個雖然很短卻明確的延遲(deltat) ,就獲得

2018-11-08 08:40:00 6715

6715

的頻率,但是由于系統的ADC 器件時鐘速率并不能達到要求的高頻速率或者存儲處理速度等不能滿足要求因此我們可以采用低速ADC 器件通過等效時間采樣來對寬帶模擬信號進行數據采集從而使系統易于實現。

2018-11-08 09:56:47 2137

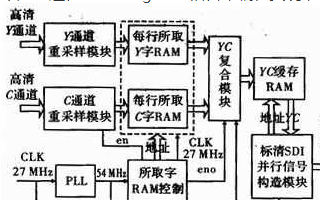

2137 升級。而利用FPGA開發,就可以體現出周期短、成本低、集成度和可移植性好,可隨時更改程序以適應電視制式標準的變更等優點,本文提出了一種基于FPGA采用重采樣技術的HD-SDI到SD-SDI的下變換實現方法。

2019-03-11 14:21:22 1934

1934

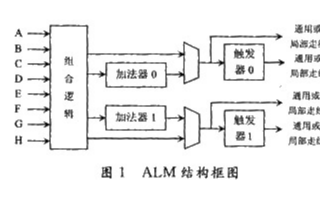

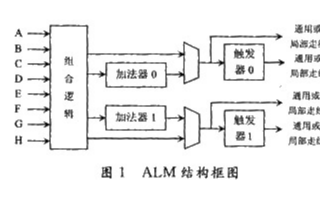

圖2列出了和傳統的4輸入LUT結構的FPGA相比較,采用ALM的StratixⅡFPGA器件例化3輸入加法器的優勢。從圖2中可以清楚地看出,對于同樣3個2 b數據相加的邏輯結構,傳統4輸入LUT結構

2020-03-03 10:45:37 1015

1015

信號傳輸中,數字信號將對模擬信號產生干擾,目前采用的解決方法是利用單片機來實現模擬信號和數字信號在單線中的混合傳輸,而這其中的測試和調試就要求示波器必須能夠對數字信號和模擬信號同時進行分析和顯示。因此,這里介紹一種基于等效和實時采樣數字示波器的設計。

2020-08-18 10:25:05 2001

2001

本文檔的主要內容詳細介紹的是基于FPGA的AD采樣的實現免費下載。

2021-01-21 15:33:54 31

31 基于FPGA的VPX時間統一系統設計與實現

2021-06-01 09:26:40 4

4 的稱為上采樣,小于的則稱為下采樣。上采樣是下采樣的逆過程,也稱增取樣或內插。 ??? 本文介紹一種使用Virtex-6器件和WebPACK工具實現實時四倍上采樣的方法。 ??? 許多信號處理應用都需要進行上采樣。從概念上講,對數據向量進行

2023-06-08 17:15:03 732

732 用于等效時間采樣應用的空間多路單腔雙光梳激光器1介紹雙光學頻率梳(簡稱雙光梳)[1]的概念在光頻梳被提出后不久被引入[2-4]。在時域上,雙光梳可以理解為兩個相干光脈沖序列,它們的重復頻率有輕微

2022-05-26 09:47:05 460

460

,就需要提高采樣時鐘的頻率,但是由于系統的ADC 器件時鐘速率并不能達到要求的高頻速率或者存儲處理速度等不能滿足要求因此我們可以采用低速ADC 器件通過等效時間采樣來對寬帶模擬信號進行數據采集從而使系統易于實現。 1 等效時間采

2023-07-29 09:00:01 537

537

什么是示波器的實時采樣率? 什么是示波器的等效時間采樣? 示波器是一種測試儀器,用于顯示波形和信號的性質。實時采樣率是指示波器在一個時間單位內(通常是1秒),可以將信號進行采樣的次數。它是示波器

2023-10-17 16:16:07 920

920 2023-11-07 08:31:41 0

0 示波器實時采樣與等效采樣有何區別? 示波器實時采樣和等效采樣是示波器在測量電信號時使用的兩種不同的方法。它們在采樣速度、信號還原精度、存儲和處理能力等方面有所不同。下面將詳細介紹這兩種采樣方法的區別

2023-12-21 14:02:19 319

319 等效時間采樣示波器與實時示波器的對比,有什么不同? 等效時間采樣示波器和實時示波器是電子測試設備中常用的兩種示波器。它們在運行原理、應用場景、優點和缺點等方面存在一些顯著差異。 一、等效時間采樣

2024-01-19 11:29:28 321

321

電子發燒友App

電子發燒友App

評論