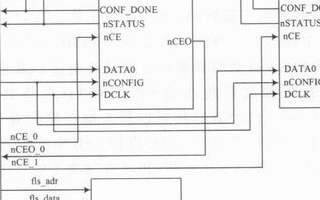

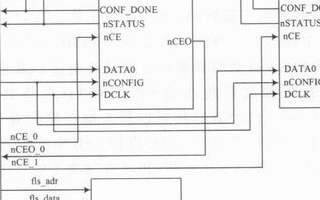

在需要多個FPGA芯片的應用中,如果JTAG鏈上所有FPGA采用相同配置,可以通過“成組”加載方式同時加載;

2023-02-20 10:18:27 3783

3783

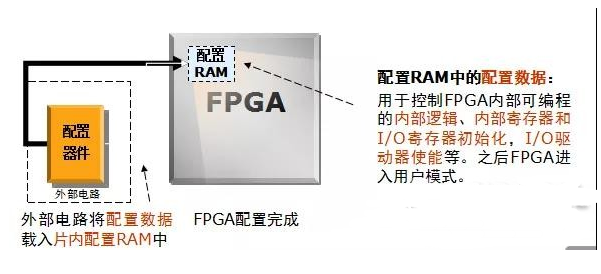

大多數FPGA芯片是基于 SRAM 的結構的, 而 SRAM 單元中的數據掉電就會丟失,因此系統上電后,必須要由配置電路將正確的配置數據加載到 SRAM 中,此后 FPGA 才能夠正常的運行。

2019-07-01 17:16:45 16228

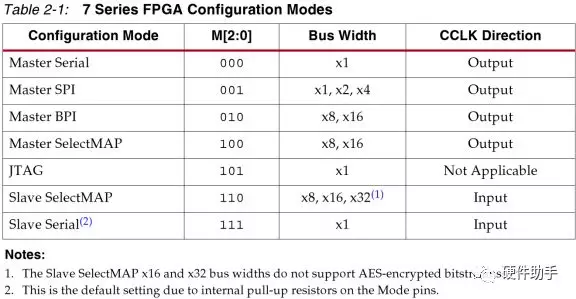

16228 本文主要介紹Xilinx FPGA的配置模式。

2021-01-01 10:12:00 21577

21577

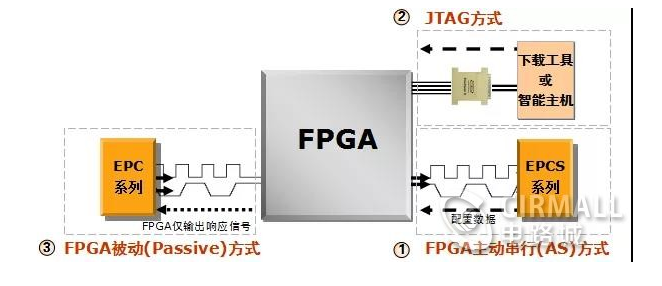

FPGA配置方式靈活多樣,根據芯片是否能夠自己主動加載配置數據分為主模式、從模式以及JTAG模式。典型的主模式都是加載片外非易失( 斷電不丟數據) 性存儲器中的配置比特流,配置所需的時鐘信號( 稱為

2022-09-22 09:13:59 3375

3375 在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束和時序例外約束才能實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是一個重點。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 1382

1382 目前,大多數FPGA芯片是基于 SRAM 的結構的, 而 SRAM 單元中的數據掉電就會丟失,因此系統上電后,必須要由配置電路將正確的配置數據加載到 SRAM 中,此后 FPGA 才能夠正常的運行。

2022-10-24 14:52:00 612

612 目前,大多數 FPGA 芯片是基于 SRAM 的結構的, 而 SRAM 單元中的數據掉電就會丟失,因此系統上電后,必須要由配置電路將正確的配置數據加載到 SRAM 中,此后 FPGA 才能夠正常

2022-12-26 18:10:00 1780

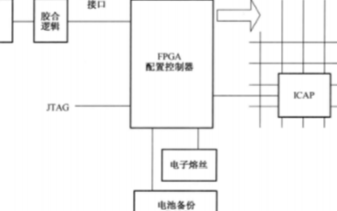

1780 我們所說的FPGA配置電路,一方面要完成從PC上把bit文件下載到FPGA或存儲器的任務,另一方面則要完成FPGA上電啟動時加載配置數據的任務。

2023-06-10 10:09:52 317

317

在FPGA設計中,時序約束對于電路性能和可靠性非常重要。在上一篇的文章中,已經詳細介紹了FPGA時序約束的主時鐘約束。

2023-06-12 17:29:21 1230

1230 前面講解了時序約束的理論知識FPGA時序約束理論篇,本章講解時序約束實際使用。

2023-08-14 18:22:14 842

842

`FPGA 上電配置時候IO口會有一個短暫的3.3V 10ms 的電平,導致我控制端出現問題,我想問下如何可以避免這個電平`

2020-11-23 10:31:40

FPGA配置模式

2012-08-17 22:24:05

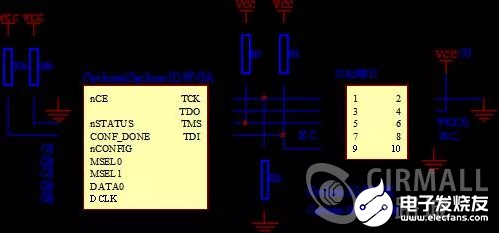

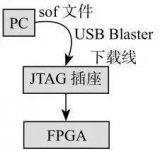

下載配置模式應該要選擇PS模式,從數據手冊查到,連接MSEL[3..0]全部到地。即為選擇PS模式下載,并且支持3.3/3.0/2.5的編程電壓。 如下圖所示,為ALTERA官方提供的PS模式下載示意

2012-04-26 14:27:03

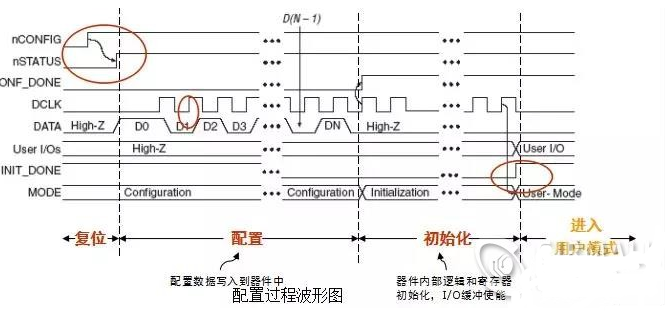

FPGA配置引腳說明使用EMCCLK引腳,全速加載程序FPGA加載時序

2021-02-03 06:47:35

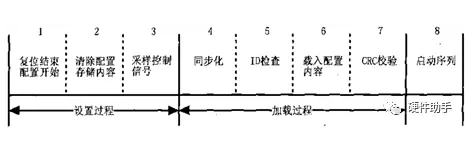

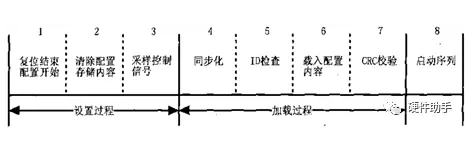

。使用BITSTREAM.CONFIG.EXTMASTERCCLK_EN屬性在Vivado中設置ExMasterCclk_en選項 三、FPGA加載時序 上電時序圖 上電時序圖 上電配置流程 其配置過程分解為8個步驟。 1、上電 7

2021-01-15 16:43:43

使用的是SPARTAN-3E的開發板,在fpga配置文件時,.bit文件的下載時,程序可以在線正常運行。但使用.mcs文件配置時,ISE上顯示program success,但板子上的FPGA并沒有加載

2015-03-16 17:05:25

發出低脈沖 后,FPGA芯片經過一個初始化序列清空內部FPGA配置存儲器。此序列開始時,DONE和INIT_B引腳均轉為低。初始化完成后,INIT_B引腳轉 為高,并采樣芯片的配置模式及變量選擇引腳

2012-08-12 11:56:42

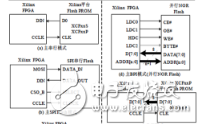

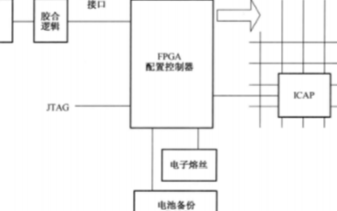

]圖1]3 基于CPLD 的FPGA 加載方案3.1]在 設備端通信產品中,基于CPLD 的FPGA 從并加載框如圖2 所示,配置數據存儲在FLASH 中,且在加載數據之前,CPU 通過局部總線和雙倍

2019-07-12 07:00:09

和邊界掃描模式,其中主模式使用內部振蕩器提供時鐘,從模式和邊界掃描模式使用器件外部提供的時鐘。在FPGA器件上電初始化后,配置模塊向FPGA發送配置碼流和配置時鐘來配置FPGA器件。因為配置速度越快

2019-06-10 05:00:08

的設置以及時序分析455.3.4綜合高手揭秘XST的11個技巧515.4 大規模設計帶來的綜合和布線問題525.5 FPGA相關電路設計知識545.5.1 配置電路545.5.2 主串模式——最常

2012-02-27 15:44:02

進行編程。用戶可以根據不同的配置模式,采用不同的編程方式。FPGA 的使用非常靈活。目前,大部分的 FPGA 在使用時都需要外接一個 EPROM 保存其程序,加電時,FPGA 芯片將 EPROM 中

2018-09-06 09:11:58

; (3)加載FPGA 電路配置數據流; (4)FPGA 電路配置完成,啟動電路就緒序列。 主串模式電路連接圖見圖1。圖1 FPGA 配置主串模式連接圖 系統或芯片上電后,信號引腳PROG_B被拉低

2011-09-13 09:22:08

攝像頭系統的快速啟動時間要求就是很好的一個例子——車輛啟動后后視圖像在儀表板顯示屏上的顯示速度是最為突出的設計挑戰。上電后,FPGA立即加載存儲于NOR器件中的配置比特流。傳輸完成后,FPGA轉換

2021-09-03 07:00:00

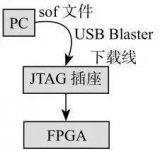

”信息。在彈出的界面中,點擊OK,如下圖所示:圖 4雙擊FPGA芯片圖標,在彈出的對話框中選擇需要加載的.bit文件,例如光盤“Demo\app\LED\bin”路徑下的led.bit文件,然后

2020-09-25 09:57:45

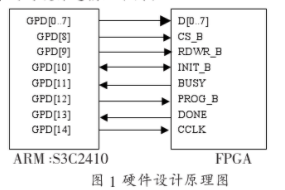

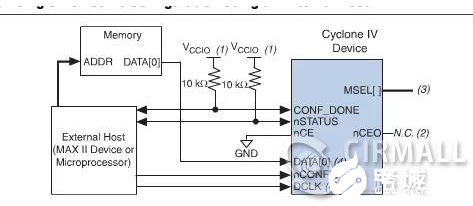

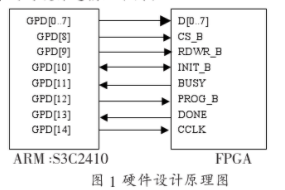

FPGA加載程序時,可以采用串行從模式、并行從模式,甚至于 JTAG模式。本文選擇并行從模式,原因在于更高的配置速率。2、 FPGA程序數據的產生FGPA的程序加載即是要把好的程序文件按一定的時序寫入

2019-12-10 17:42:18

板子簡介:FPGA在PS配置模式下通過ARM配置;整個電路設計正常,有其他板子已經正常跑起來了。問題板子有以下幾個問題:問題一:上電cfg,sta管腳狀態異常:分別為0v,1.7v;正常的都是

2017-06-05 11:48:20

安路 EG4X FPGA 器件支持多種程序加載模式。本手冊主要介紹從動串行(SS)加載模式以及從動串行級聯加載模式的使用。內容包括使用從動串行加載模式的軟件配置,使用從動串行加載模式和從動串行級聯加載模式的硬件電路連接,另外包括 MCU 作為控制 FPGA 從動串行加載的主控器件時的軟件工作流程。

2022-10-27 08:03:06

安路 EG4X FPGA 器件支持多種程序加載模式。本手冊主要介紹從動并行(SP)加載模式以及從動并行級聯加載模式的使用。內容包括使用從動并行加載模式的軟件配置,使用從動并行加載模式和從動并行級聯加載模式的硬件電路連接,另外包括 MCU 作為控制 FPGA 從動并行加載的主控器件時的軟件工作流程。

2022-10-27 07:31:16

安路 SALEAGLE?4(以下簡稱為 EG4)X FPGA 器件支持的程序加載模式如表 1 所示。本手冊主要介紹 SS,SP,MSPI 和 JTAG 加載模式,及 EG4X 器件相關加載模式

2022-10-27 07:21:17

1.同樣的板子,用過好多塊,都沒有問題,就這塊無法加載,應該不是PCB設計問題。2.我設計的是主串加載模式(Master Serial)。硬件上將FPGA的M2~M0直接接到GND上。3.上電以后

2015-08-15 09:20:26

用vhdl實現cpld配置fpga,配置成功后在usermode下設置一個重新配置信號,當信號有效時對fpga進行重新配置;fpga配置程序放在flash內;現在遇到的問題是,上電cpld能夠正常配置fpga并且進入usermode ,但是加上重新配置語句過后就不能成功配置fpga,求高人指點~

2013-01-17 22:35:39

的內部的一些特性來試圖解決這個問題。 要解決這個問題首先要了解FPGA上電初始化過程,這里我們是以ALTERA的ArriaGX的AS模式來進行研究。第一步控制POR時間 FPGA的AS配置主要分為

2015-01-22 14:41:34

時后視圖像在儀表板上顯示的速度是一階設計挑戰。 上電后的FPGA會立即加載已存儲在NOR器件中的配置位流。傳輸完成后的FPGA轉換為活動(已配置)狀態。FPGA包含許多配置接口選項,通常包括并行

2020-09-18 15:18:38

是用于設置FPGA初上電時的啟動模式,我們的FPGA上電使用Standard AS模式從SPI Flash里面加載配置數據。 圖2.24 MSEL引腳配置說明的截圖有了前面的理論做鋪墊,我們的設計也就

2016-08-10 17:03:57

我用的是Spartan-3E系列的芯片。我想有兩種下載方式,方式一是通過JTAG直接給FPGA下載程序,方便調試。方式二是將程序燒到PROM里面,在上電時FPGA自動從PROM進行配置。現在的問題是

2013-10-18 10:06:47

,我們肯定不希望每次重新上電后都用PC去下載一次,工程實現也不允許我們這么做。所以,通常FPGA旁邊都有一顆配置芯片,它通常是一片FLASH,或者是并行或者是串行接口的。不管是串行還是并行的FLASH

2018-03-04 22:12:49

過程。FPGA上電后,內部的控制器首先工作,確認當前的配置模式,如果是外部配置芯片啟動,則通過和外部配置芯片的接口(如我們的SPI接口)將配置芯片的數據加載到FPGA的RAM中,配置完成后開始正式運行

2018-03-05 16:30:35

對配置模式需要作出合適的選擇。 2.2 Viretex 系列FPGA 的配置模式 Viretex 系列FPGA 的配置模式是由上電時其專用配置管腳的狀態決定的,對應的關系 如下表所示:因在系統中使

2015-03-05 15:31:07

稱為可編程開關。可配置邏輯塊(CLB)可配置用于所需組合和順序邏輯功能的邏輯塊稱為CLB。在FPGA上實現邏輯時,邏輯被分解為小密度邏輯塊并映射到多個CLB上。邏輯密度FPGA中每單位面積的邏輯量稱為

2022-10-27 16:43:59

,設計人員就會縮減電源。電壓軌時序控制許多FPGA要求不同電源電壓軌以特定順序上電。內核電壓的供應往往需要早于I/O電壓的供應,否則一些FPGA會被損壞。為了避免這種情況,電源需要按正確的順序上電

2018-08-13 09:29:10

攝像頭系統的快速啟動時間要求就是很好的一個例子——車輛啟動后后視圖像在儀表板顯示屏上的顯示速度是最為突出的設計挑戰。上電后,FPGA立即加載存儲于NOR器件中的配置比特流。傳輸完成后,FPGA轉換

2021-05-26 07:00:00

我正在研究Zedboard,我需要將FPGA配置文件(.mcs文件)存儲到Flash上??。Zedboard在JTAG模式下工作正常。但是,如果我選擇加載文件的flash方法,FPGA

2020-05-20 10:31:51

需要將FPGA程序通過I2C或者RS232加載到FPGA內部,然后通過FPGA存儲到SPI FLASH中,再次上電后從SPI FLASH加載。 這個過程中,有以下幾個問題:1.怎樣將.v文件轉換成

2016-04-29 14:46:21

的內部的一些特性來試圖解決這個問題。 要解決這個問題首先要了解FPGA上電初始化過程,這里我們是以ALTERA的ArriaGX的AS模式來進行研究。第一步控制POR時間 FPGA的AS配置主要分為三個過程

2015-01-20 17:37:04

各位前輩,FPGA采用并行加載方式,現CPLD外掛一片FLASH,要求用CPLD控制加載時序,從FLASH讀取代碼,送入FPGA,應該怎么用CPLD控制加載時序,程序應該怎么寫,有可以參考的資料嗎,謝謝各位了!

2013-02-21 12:07:34

現在的FPGA還嚴格要求上電時序嗎?想請教一下大家

2017-09-26 15:39:07

目前,大多數FPGA芯片是基于 SRAM 的結構的, 而 SRAM 單元中的數據掉電就會丟失,因此系統上電后,必須要由配置電路將正確的配置數據加載到 SRAM 中,此后 FPGA 才能夠正常的運行

2019-07-18 08:10:11

設計者對于FPGA的配置設計是一個基本要求,當然一般不可能要求每個FPGA硬件設計者對每一種配置模式都很熟悉,但是由于每個人的設計習慣、方法以及使用的器件不同從而在產品研發中設計FPGA的加載模式也

2015-01-28 10:27:03

概述EasyGo FPGA Solver是EasyGo開發的專門部署在FPGA 硬件上的解算器軟件。根據不同的應用需求,會有不同的FPGA Solver 選擇

2022-05-19 09:21:43

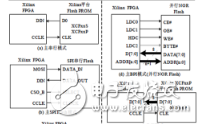

介紹如何用PowerPC860(MPC860)進行FPGA(Xilinx 的Virtex-II 系列)的配置;給出進行FPGA 配置所需的詳細時序圖和原理圖。本配置基本原理對其它FPGA 的配置也適用。

2009-04-16 14:11:36 18

18 什么是FPGA?FPGA是什么意思,本內容詳加描述了FPGA的相關知識包括FPGA配置模式,PPGA特點及應用

2011-12-07 13:39:00 79099

79099 摘要:介紹如何用PowerPC860(MPC860)進行FPGA(Xilinx的Virtex-II系列)的配置;給出進行FPGA配置所需的詳細時序圖和原理圖。本配置基本原理對其它FPGA的配置也適用。

2009-06-20 11:02:38 942

942

介紹了一種基于SRAM技術的FPGA可編程邏輯器件的編程方法,能在系統復位或上電時自動對器件編程。有效地解決了基于SRAM的FPGA器件掉電易失性問題,針對當前系統規模的日益增大,本文提出了一種用單片機對多片FPGA自動加載配置的解決方案.

2011-03-15 16:41:22 21

21 根據FPGA芯片加載時序分析,本文提出了采用通過市面上常見的Flash ROM芯片替代專用PROM的方式,通過DSP的外部高速總線進行FPGA加載;既節約了系統成本,也能達到FPGA上電迅速加載的目的

2011-08-16 16:26:14 1558

1558

FPGA有多種配置模式:并行主模式為一片FPGA加一片EPROM的方式;主從模式可以支持一片PROM編程多片FPGA;串行模式可以采用串行PROM編程FPGA;外設模式可以將FPGA作為微處理器的外設,由微處理

2011-09-08 17:50:27 1734

1734 3 FPGA設計流程 完整的FPGA 設計流程包括邏輯電路設計輸入、功能仿真、綜合及時序分析、實現、加載配置、調試。FPGA 配置就是將特定的應用程序設計按FPGA設計流程轉化為數據位流加載

2013-01-16 11:52:22 16

16 當你的FPGA設計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現工具來優化設計從而滿足時序要求,也需要設計者具有明確目標和診斷/隔離時序問題的能力。

2014-08-15 14:22:10 1169

1169 FPGA時序約束方法很好地資料,兩大主流的時序約束都講了!

2015-12-14 14:21:25 19

19 如何有效地管理FPGA設計中的時序問題

2017-01-14 12:49:02 14

14 當你的FPGA設計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現工具來優化設計從而滿足時序要求,也需要設計者具有明確目標和診斷/隔離時序問題的能力。設計者現在有一些

2017-02-09 01:59:11 264

264 Xilinx FPGA編程技巧常用時序約束介紹,具體的跟隨小編一起來了解一下。

2018-07-14 07:18:00 4129

4129

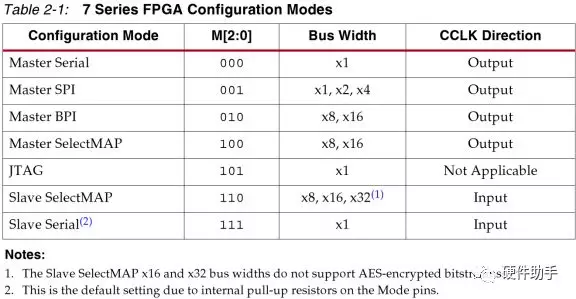

FPGA配置方式靈活多樣,根據芯片是否能夠自己主動加載配置數據分為主模式、從模式以及JTAG模式。典型的主模式都是加載片外非易失( 斷電不丟數據) 性存儲器中的配置比特流,配置所需的時鐘信號( 稱為CCLK) 由FPGA內部產生,且FPGA控制整個配置過程

2017-02-11 16:36:09 1446

1446

fpga時序收斂

2017-03-01 13:13:34 23

23 一個好的FPGA設計一定是包含兩個層面:良好的代碼風格和合理的約束。時序約束作為FPGA設計中不可或缺的一部分,已發揮著越來越重要的作用。毋庸置疑,時序約束的最終目的是實現時序收斂。時序收斂作為

2017-11-17 07:54:36 2326

2326

通過SELECTMAP32接口配置和回讀XILINX公司生產的V5系列SRAM型FPGA,被配置的FPGA以下簡稱DUT,產生配置時序的FPGA簡稱配置FPGA。首先硬件上應將M[2:0]接成110

2017-11-17 10:16:01 8730

8730 滿足設計需求。FPGA的多重加載可以解決可編程資源不足的難題。FPGA多重加載是將設計的多個模式的比特文件存儲到Flash,用戶可以根據需要選擇加載不同模式的比特文件。FPGA的多重加載解決了可編程資源不足的問題,提高了FPGA可編程資源的利用率。

2017-11-18 04:41:50 5879

5879

時序以及各階段I/O 管腳狀態,說明了FPGA上電配置對電路功能的嚴重影響,最后針對不同功能需求的FPGA外圍電路提出了有效的設計建議。

2017-11-22 07:18:34 6221

6221

FPGA配置方式靈活多樣,根據芯片是否能夠自己主動加載配置數據分為主模式、從模式以及JTAG模式。典型的主模式都是加載片外非易失(斷電不丟數據)性存儲器中的配置比特流,配置所需的時鐘信號(稱為

2017-11-22 09:24:02 6452

6452 FPGA配置方式靈活多樣,根據芯片是否能夠自己主動加載配置數據分為主模式、從模式以及JTAG模式。典型的主模式都是加載片外非易失( 斷電不丟數據) 性存儲器中的配置比特流,配置所需的時鐘信號( 稱為

2017-11-26 08:12:51 7889

7889

盡管FPGA的配置模式各不相同,但整個配置過程中FPGA的工作流程是一致的,分為三個部分:設置、加載、啟動。

2018-08-01 15:32:54 4736

4736

FPGA 的配置數據通常存放在系統中的存儲器件中,上電后控制器讀取存儲器中的bit 文件并加載到FPGA 中,配置方式有JTAG、從并、從串、主從4 種,不同廠家叫法不同,但實現方式基本都是一樣的。

2018-10-30 08:58:00 7921

7921

FPGA有多種配置/加載方式。粗略可以分為主動和被動兩種。主動加載是指由FPGA控制配置流程,被動加載是指FPGA僅僅被動接收配置數據。

2018-10-05 10:12:00 17251

17251 單片機是基于FLASH結構的,所以單片機上電直接從本地FLASH中運行。但SRAM 架構的FPGA是基于SRAM結構的,掉電數據就沒了,所以需要借助外部電路來配置運行的數據,其實我們可以借助Vivado來學習FPGA的各種配置模式。

2018-11-05 15:12:57 7298

7298 Altera FPGA支持AS,PS,JTAG等幾種較常見的配置方法。 當為AS配置模式時,FPGA為主設備,加載外部FLASH中的數據至內部RAM中運行。當為PS配置模式時,FPGA為從設備,外部

2018-11-18 18:05:01 481

481 加載系統。該系統通過USB芯片將PC中的配置文件傳送給CPLD,CPLD再將其寫入FLASH芯片,FLASH芯片可以長久地存儲配置文件。這樣FPGA每次上電后CPLD將FLASH中的配置文件讀出來配置

2019-02-20 15:36:23 2799

2799

本文檔詳細介紹的是FPGA教程之CPLD和FPGA的配置與下載的詳細資料說明主要內容包括了:一、CPLD/FPGA器件的配置,二、MAX系列非易失性器件的下載配置,三、FLEX/ACEX系列FPGA的下載配置,四、ALTERA的編程文件

2019-02-28 09:56:18 17

17 根據需要有選擇的加載時不能采用這種方法。本文實現了一種基于外部處理器的加載方法,速度快,而且可以根據設置給FPGA加載相應的程序。

2019-03-22 16:20:14 952

952 FPGA是基于SRAM編程的,編程信息在系統掉電時會丟失,每次上電時,都需要從器件外部的FLASH或EEPROM中存儲的編程數據重現寫入內部的SRAM中。FPGA在線加載需要有CPU的幫助,并且在加載前CPU已經啟動并工作。FPGA的加載模式主要有以下幾種:

2020-04-07 08:00:00 16

16 FPGA要加載的程序可以根據需要有選擇的加載時不能采用這種方法。本文實現了一種基于外部處理器的加載方法,速度快,而且可以根據設置給FPGA加載相應的程序。

2020-08-13 17:16:46 1805

1805

賽靈思公司的FPGA芯片具有IEEE 1149.1/1532協議所規定的JTAG接口,只要FPGA上電,不論模式選擇管腳M[1:0] 的電平,都可用采用該配置模式。JTAG模式不需要額外的掉電

2020-12-31 17:30:55 13

13 所有現代FPGA的配置分為兩類:基于SRAM的和基于非易失性的。其中,前者使用外部存儲器來配置FPGA內的SRAM后者只配置一次。 Lattice和Actel的FPGA使用稱為反熔絲的非易失性配置

2021-07-02 16:01:40 2781

2781

典型的主模式都是加載片外非易失( 斷電不丟數據) 性存儲器中的配置比特流,配置所需的時鐘信號( 稱為CCLK) 由FPGA內部產生,且FPGA控制整個配置過程。

2022-03-14 14:02:50 1366

1366 本文章探討一下FPGA的時序約束步驟,本文章內容,來源于配置的明德揚時序約束專題課視頻。

2022-03-16 09:17:19 3255

3255

上一篇《FPGA時序約束分享01_約束四大步驟》一文中,介紹了時序約束的四大步驟。

2022-03-18 10:29:28 1323

1323

時序分析時FPGA設計中永恒的話題,也是FPGA開發人員設計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2022-03-18 11:07:13 2096

2096 本文章探討一下FPGA的時序input delay約束,本文章內容,來源于配置的明德揚時序約束專題課視頻。

2022-05-11 10:07:56 3462

3462

電子發燒友網站提供《安路EG4X FPGA從動串行加載模式.pdf》資料免費下載

2022-09-27 10:55:18 1

1 電子發燒友網站提供《安路EG4X FPGA從動并行加載模式.pdf》資料免費下載

2022-09-27 10:44:27 1

1 盡管FPGA的配置模式各不相同,但整個配置過程中FPGA的工作流程是一致的,分為三個部分:設置、加載、啟動。

2022-10-10 14:37:57 1272

1272 數據模式。 FPGA配置方式 根據FPGA配置過程控制者的不同,我們將配置方式主要分為三類: FPGA控制配置過程 第一種最常見的模式是,從片外FLASH中加載配置所需的比特流,FPGA內部產生時鐘,整個過程有FPGA自主控制。FPGA 上電以后,將配置數據從FLASH中,讀入到

2022-11-21 21:45:10 955

955 Lattice和Actel的FPGA使用稱為反熔絲的非易失性配置技術,其主要優點是系統設計更加簡單、不需要外部存儲器和配置控制器、功耗低、成本低和FPGA配置時間更快。最大的缺點在于配置是固定的。

2022-12-01 11:08:45 862

862 典型的主模式都是加載片外非易失( 斷電不丟數據) 性存儲器中的配置比特流,配置所需的時鐘信號( 稱為CCLK) 由FPGA內部產生,且FPGA控制整個配置過程。

2023-02-15 09:57:24 618

618 總結Xilinx? FPGA 的上電模式可以分為以下4類型: 主模式 從模式 JTAG模式(調試模式) 系統模式(多片配置模式) 1、主模式 典型的主模式都是加載片外非易失( 斷電不丟數據

2023-03-29 14:50:06 535

535 在不帶內置ARM核的AMD FPGA產品系列中,FPGA的程序加載方式并沒有發生大的變化

2023-07-07 14:14:58 981

981

FPGA高級時序綜合教程

2023-08-07 16:07:55 3

3

電子發燒友App

電子發燒友App

評論