LVDS 采用了差分傳輸機制,每一 LVDS 信號使用兩條走線。 這兩條走線之間的電壓差定義了 LVDS 信號值。

2020-03-22 15:54:00 2970

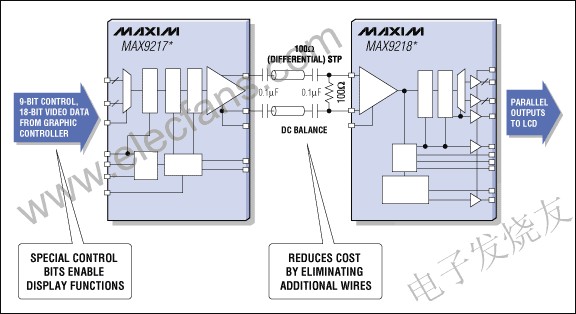

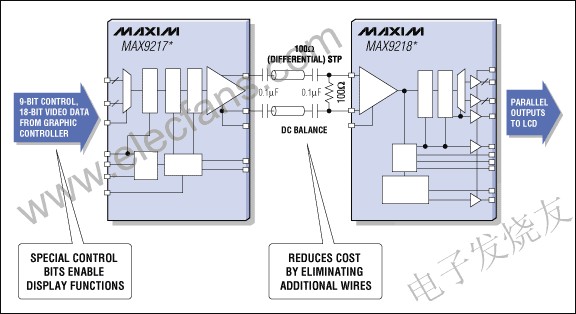

2970 這種接口電路中,采用單路方式傳輸,每個基色信號采用6位數據,共18位RGB數據,因此,也稱18位或18bit LVDS接口。此,也稱18位或18bit LVDS接口。

2023-03-28 11:46:23 2931

2931 LVDS是一種低擺幅的差分信號技術,它使得信號能在差分PCB線對或平衡電纜上以幾百Mbps的速率傳輸,其低壓幅和低電流驅動輸出實現了低噪聲和低功耗。

2023-10-02 16:44:00 592

592

采用LVDS緩沖器來驅動和接收底板上傳來的信號。它會將信號傳輸路徑再細分為很短的區段,以遮蔽阻抗誤配的問題,并減少信號衰減。而且在類似機器人這種工業應用中,通常都需要將LVDS緩沖器隔離起來,避免安全風險。

2022-02-22 08:00:00 3298

3298 電子發燒友網報道(文/李寧遠)LVDS,經常會使用的低電壓差分信號,又稱RS-644總線接口,是20世紀90年代才出現的一種數據傳輸和接口技術。低電壓差分信號以低功耗、低誤碼率、低串擾和低輻射優勢

2023-10-19 09:02:01 981

981 、65MSPS、8通道并行模數轉換器(ADC)。提供了內部參考,簡化了系統設計要求。低功耗允許最高的系統集成密度。串行LVDS(低壓差分信號)輸出減少了接口線的數量和封裝尺寸。集成鎖相環將輸入的ADC采樣

2020-09-23 15:33:56

奈奎斯特區之外ADC12D1x00RF提供了一個靈活的LVDS接口,該接口具有多個SPI可編程選項,以簡化電路板設計和FPGA / ASIC數據捕獲。LVDS輸出與IEEE 1596.3-1996兼容,并支持可編程共模電壓。該產品采用無鉛292球耐熱增強BGA封裝,額定溫度范圍為–40°C至85°

2021-01-08 09:15:08

奈奎斯特區之外ADC12D1x00RF提供了一個靈活的LVDS接口,該接口具有多個SPI可編程選項,以簡化電路板設計和FPGA / ASIC數據捕獲。LVDS輸出與IEEE 1596.3-1996兼容,并支持可編程共模電壓。該產品采用無鉛292球耐熱增強BGA封裝,額定溫度范圍為–40°C至85°

2021-01-08 09:15:08

range of –40°C to 85°C.ADC12D1X00 RF提供了一個靈活的LVDS接口,具有多個SPI可編程選項,以方便電路板設計和FPGA / ASIC數據采集。LVDS輸出與IEEE

2018-07-30 07:21:58

QJ1600EVM,ADC12QJ1600EVM,,現貨ADC12QS065CISQ/NOPB,ADC12QS065,-40 to 85,7,173ADC12

2020-12-14 08:56:49

ADC12DL065 Dual 12-Bit, 65 MSPS, 3.3V, 360mW A/D Converter datasheet (Rev. D)

2022-11-04 17:22:44

BOARD EVALUATION FOR ADC12DL065

2023-03-30 11:47:32

ADC12DS065 - Dual 12-Bit, 65/80/95/105 MSPS A/D Converter with Serial LVDS outputs - National Semiconductor

2022-11-04 17:22:44

ADC12QS065 Quad 12-Bit 65 MSPS A/D Converter with LVDS Serialized Outputs datasheet (Rev. I)

2022-11-04 17:22:44

IC ADC 12BIT PIPELINED 60WQFN

2023-04-06 17:07:15

IC ADC 12BIT PIPELINED 60WQFN

2023-03-23 07:44:37

BOARD DEMO FOR ADC1415S065F2

2024-03-14 21:23:12

(1)ADC、DAC選型時候的有個data input format 是lvds和cmos什么意思啊?1. lvds是不是那個DCO+和DCO-?。這兩個信號是不是必須要從時鐘專用引腳輸入

2017-01-23 15:17:38

機輸出線是51PIN的線,液晶模組的連接座是60PIN的,需要有個轉接板,把51PIN信號連接到60pin上,現在要做這個轉接板。在設計之前我有個問題不太確定,我知道51PIN傳輸線特性阻抗是100Ω,那

2018-12-16 16:55:27

這種做法的矛盾評論,我更愿意知道確切的答案。這只是為了進行健全性檢查,因為我對這種設計并不熟悉。所有銀行(LA,HA,HB)的1.8V電源僅用于單端信號嗎?特別是,我們的LVDS信號(共模電壓1.25V)是否可以毫無問題地傳輸?非常感謝你的時間和答案。

2019-09-20 11:56:39

問一下各位大神們 LVDS接口的數據傳輸速率是怎么計算的?跟頻率的關系是怎樣的?一般用多少頻率傳輸?假如是單路8位(4對差分數據)LVDS接口,知道時鐘速率,數據傳輸速率怎么計算?

2017-01-14 12:24:53

顯示器輸出需要傳輸相當長的距離,圖像格式是稱為復合視頻基帶信號(CVBS)的模擬信號。 近幾年,隨著汽車電子技術的發展,對視頻源、顯示設備和視頻傳輸線的開發取得了較大進展,本文討論了相關的發展趨勢

2019-04-23 07:00:11

LVDS:Low-Voltage Differential Signaling 低電壓差分信號。一種信號傳輸模式,是一種電平標準,LVDS接口又稱RS-644總線接口,是一種數據傳輸和接口

2016-04-15 16:13:33

問一下各位大神們 LVDS接口的數據傳輸速率是怎么計算的?跟頻率的關系是怎樣的?一般用多少頻率傳輸?假如是單路8位(4對差分數據)LVDS接口,知道時鐘速率,數據傳輸速率怎么計算?

2017-01-02 15:31:50

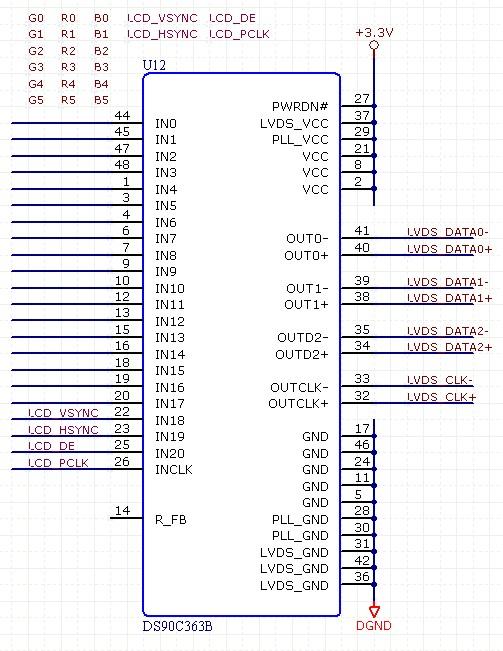

) 輸入信號:28 bits LVTTL/LVCMOS數據和1路LVTTL/LVCMOS時鐘信號;h) 輸出信號:滿足EIA/TIA-644標準的4路LVDS數據流和1路LVDS時鐘信號;i) 封裝

2013-12-11 15:49:06

1 概述GM8284C型28位可編程數據選通接收器主要用于視頻/圖像傳輸中的接收部分,實現的功能是將高速串行LVDS信號解碼為并行TTL數據,完成數據的解碼功能。該器件可將4對串行LVDS差分信號在

2013-12-11 15:42:06

這是ADC的lvds時序圖,目前遇到的問題時,我用一片Artix-7系列fpga同時采集4篇上述的ADC值,單片adc數據采集是正常的,多篇同時采集時,發現數據就不對了,望大神門幫忙解答使用了IDDR這個原語!

2023-04-17 15:28:34

什么元器件嗎?還是跟平時低頻的一樣,直接連接就好?總結問題:1.用168M的單片機如何采集200MHz的信號2.200Msps的ADC由CMOS和DDR LVDS輸出,怎么接收輸出信號,硬件電路上需要加電阻嗎?感謝各位大佬。

2020-12-06 22:26:35

LVDS(Low Voltage Differential Signaling)即低壓差分信號傳輸,是一種滿足當今高性能數據傳輸應用的新型技術。由于其可使系統供電電壓低至 2V,因此它還能滿足未來

2019-12-11 09:51:59

我用FPGA跟一個ADC通過LVDS進行通信,FPGA規定用LVDS時,相應BANK的電壓為2.5V,這樣出來的LVDS信號的共模電壓在1.2V左右,而ADC使用的電源是1.8V,出來的L號共模電壓

2019-03-01 15:43:37

01 概述GM8284DD型28位LVDS圖像收器主要用于視頻/圖像傳輸中的接收部分,實現的功能是將高速串行LVDS信號解碼為并行TTL數據,完成數據的解碼功能。該器件可將4對串行LVDS差分信號在

2020-08-19 15:11:28

RK3288設置lvds信號輸出附上配置代碼由于硬件關系這里我配置的不是標準的1080p60視頻格式,并且最后屏幕點亮成功,代碼中還包括加強電流強度(附圖)這段代碼復用了gpio的功能,然后是否配置

2022-05-27 11:27:50

1、RK3288設置lvds信號輸出 附上配置代碼 由于硬件關系這里我配置的不是標準的1080p60視頻格式,并且最后屏幕點亮成功,代碼中還包括加強電流強度(附圖)原作者:I&You

2022-11-07 17:43:19

rk3399怎么才能輸出lvds信號?

2022-03-07 07:09:07

過程。大部分過程在QS30-1輝光管電子時鐘的制作貼里介紹的很詳盡了,這里就把根QS30-1設計和制作過程不同的地方說一說。 SHOWTIME: 一、本次DIY的QS18-12輝光數碼管電子鐘功能及特點

2011-12-08 11:00:15

大家好,我正在使用Spartan 6 FPGA,我嘗試生成LVDS差分時鐘來為ADC提供時鐘。我使用SP601評估板,并在FMC連接器的一對引腳上發送差分信號。這個時鐘工作頻率高達650Mhz,但我

2019-08-09 09:34:19

雷擊所造成的浪涌等外部因素所帶來的影響。精密測量可能也需要與噪聲源(像是更為局部的微型電力電路和高速數字處理等)隔離。低壓差分信號傳輸(LVDS)是一種在更高性能轉換器和高帶寬 FPGA或ASIC I

2018-10-30 14:44:43

顯示器輸出需要傳輸相當長的距離,圖像格式是稱為復合視頻基帶信號(CVBS)的模擬信號。 近幾年,隨著汽車電子技術的發展,對視頻源、顯示設備和視頻傳輸線的開發取得了較大進展,本文討論了相關的發展趨勢

2019-05-05 09:29:30

親愛的大家,我希望將高速ADC與串行LVDS輸出連接到virtex 7 fpga。我使用的ADC評估板是AD9635_125EBZ。我想知道如何將串行LVDS接口到FMC HPC。我對FPGA很陌生。問候,薩蘭

2020-07-26 18:27:20

怎樣進行CAN和LVDS信號的檢測,思路是想用LED燈的點亮來檢測信號的正常傳輸,怎樣實現CAN信號電平驅動LED燈,用哪個片子比較好,有經驗的大神們給點方案

2019-08-13 15:09:55

親愛的大家,我的問題是如何通過LVDS將ADC AFE 5804 12位http://www.ti.com/product/afe5804連接到Spartan 3E入門套件。首先,我想模擬知道ADC

2019-07-10 08:19:23

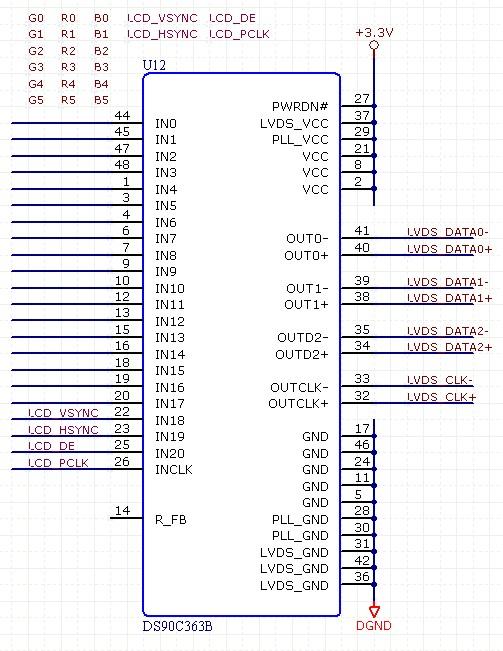

TTL信號按照SPWG/JEIDA格式轉換成LVDS信號進行傳輸,MIPI DSI接口則按照特定的握手順序和指令規則傳輸屏幕控制所需的視頻數據和控制數據。從傳輸的內容可以更直觀看到兩種接口的區別,具體

2016-06-13 20:18:24

為8bit并行數據,各子板逐一上傳到母板;各子板和母板間用8bit并行總線連接,差分信號形式(LVTTL-->LVDS)傳輸,我選用了SN65LVDS389/388;當前子板傳輸數據時,其他差分芯片

2019-05-09 08:00:18

:請教是要根據什么來選擇對的數據格式的作為輸入輸出?我看了ADC DAC資料里并沒有說到用的什么格式。2:當從ADC接收到的音頻數據進行如PEQ及其他處理時,是不是要把這些數據轉換成什么格式后來做些算法處理會好些(Blackfin和SHARC)?以及好在哪里?謝謝!

2018-10-29 10:31:24

1 LVDS信號介紹LVDS:Low Voltage Differential Signaling,低電壓差分信號。LVDS傳輸支持速率一般在155Mbps(大約為77MHZ)以上。LVDS是一種低擺幅的差分信號技術,它使得信號能在差

2008-10-16 13:44:45 153

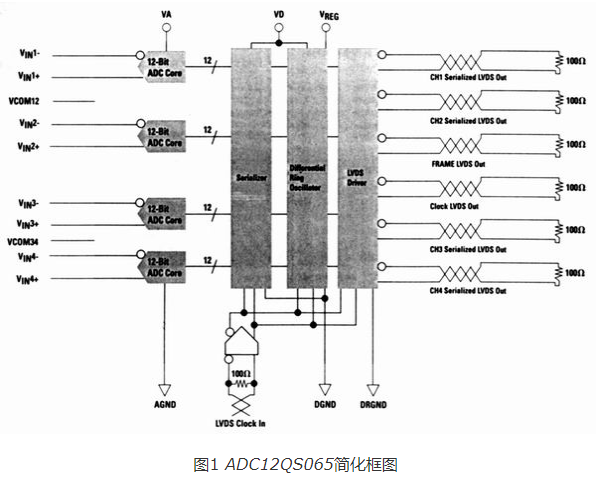

153 四通道、12 位、65MSPS 模數轉換器 (ADC) Sample rate (Max) (MSPS) 65 Resolution (Bits) 12 Number

2022-12-06 09:46:42

ADC和DAC的靜態傳輸函數和DC誤差:對于DAC和ADC這兩者來說,最重要的是記住輸入或輸出都是數字信號,所以,信號是被量化的。也就是說,N比特字代表2的N次方個可能狀態之一,因此

2009-09-28 14:25:20 12

12 The ADC12DL065 is a dual, low power monolithic CMOSanalog-to-digital converter capable

2009-10-10 09:43:57 13

13 The ADC12QS065 is a low power, high performance CMOS4-channel analog-to-digital converter with LVDS

2009-10-10 10:10:06 8

8 The ADC10DL065 is a dual, low power monolithic CMOSanalog-to-digital converter capable

2009-10-10 10:27:13 10

10 介紹了LVDS 接口的原理和優點,接口機的硬件組成以及在設計LVDS 接口時需注意的事項。關鍵詞 LVDS;數據傳輸;時序

當聲吶在海洋中執行任務時,前置預處理機設備接收

2010-09-22 08:27:26 67

67 基于低電壓差分信號(LVDS)的高速信號傳輸

2010-12-17 17:21:46 40

40 什么是LVDS?現在的液晶顯示屏普遍采用LVDS接口,那么什么是LVDS呢?LVDS(Low Voltage Differential Signaling)即低壓差分信號傳輸,是一種滿足當今高性能數據傳輸應

2007-09-26 11:45:09 5157

5157 什么是lvds信號

LVDS:Low Voltage Differential Signaling,低電壓差分信號。LVDS傳輸支持速率一般在155Mbps(大約為77MHZ)以上。LVDS是一種低擺幅的差分信號

2008-10-16 13:49:11 7845

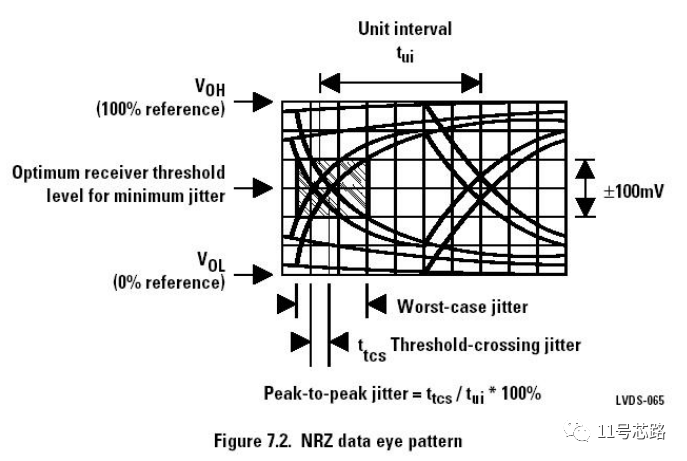

7845 LVDS信號電平特性

LVDS物理接口使用1.2V偏置電壓作為基準,提供大約400mV擺幅。LVDS驅動器由一個驅動差分線對的電流源組成(通常電

2008-10-16 13:50:25 16632

16632 LVDS差分信號抗噪特性

從差分信號傳輸線路上可以看出,若是理想狀況,線路沒有干擾時,在發送側,可以形象理解為:

2008-10-16 13:53:16 1508

1508 摘要:ANSI EIA/TIA-644標準定義的低電壓差分信號(LVDS)非常適合包括時鐘分配、點對點以及多點之間的信號傳輸。本文描述了使用LVDS將高速通訊信號分配到多個目的端的方法。

2009-04-24 16:05:19 1274

1274

摘要:ANSI EIA/TIA-644標準定義的低電壓差分信號(LVDS)非常適合包括時鐘分配、點對點以及多點之間的信號傳輸。本文描述了使用LVDS將高速通訊信號分配到多個目的端的方法。

2009-05-01 11:14:27 1655

1655

低電壓差分信號傳輸(LVDS)已經在眾多應用中得到驗證,LVDS在傳送高數據率信號的同時還具有其它優勢: 與低電源電壓的兼容性;低功耗;低輻射;高抗干擾性;簡單的布線和終端匹

2010-08-31 11:14:52 1732

1732

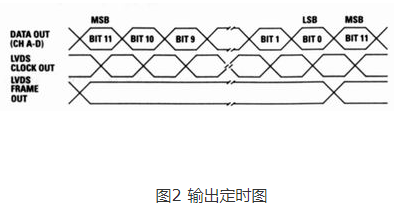

MAX1436具有自對齊的數據、時鐘以及幀對齊信號串行LVDS輸出。輸出數據以二元補碼或二進制格式表示。

2011-04-12 12:00:59 1392

1392

LVDS是低壓差分信號的簡稱,由于其優異的高速信號傳輸性能,目前在高速數據傳輸領域得到了越來越多的應用。其典型架構如下: 一般LVDS的傳輸系統由FPGA加上LVDS的Serdes芯片組成,

2012-04-24 11:31:53 14698

14698

什么是LVDS?

現在的液晶顯示屏普遍采用LVDS接口,那么什么是LVDS呢?

LVDS(Low Voltage Differential Signaling)即低壓差分信號傳輸,是一種滿足當今高性能數據傳輸應用的新型技術。

2016-06-17 15:42:45 16

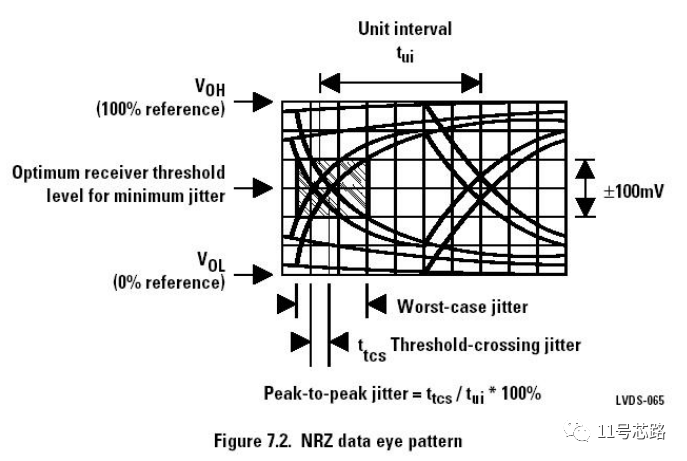

16 超高速ADC通常采用LVDS電平傳輸數據,高采樣率使輸出數據速率很高,達到百兆至吉赫茲量級,如何正確接收高速LVDS數據成為一個難點。本文以ADS42LB69芯片的數據接收為例,從信號傳輸和數據解碼兩方面,詳述了實現LVDS數據接收應該注意的問題及具體實現方法,并進行實驗測試、驗證了方法的正確性。

2017-11-17 10:40:01 6131

6131 高速轉換器三種最常用的數字輸出是互補金屬氧化物半導體(CMOS)、低壓差分信號(LVDS)和電流模式邏輯(CML)。ADC中每種數字輸出類型都各有優劣,設計人員應根據特定應用仔細考慮。這些因素取決于ADC的采樣速率和分辨率、輸出數據速率、系統設計的電源要求,以及其他因素。本文將討論每種輸出類型的電

2017-11-17 20:08:48 15266

15266

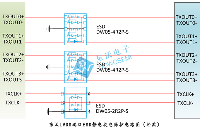

集成鎖相環(PLL)將輸入ADC采樣時鐘乘以12倍。該高頻LVDS時鐘用于數據串行化和傳輸過程。每個內部ADC的字輸出被串行化,并且首先傳送MSB或LSB。除了四個數據輸出之外,還傳輸位時鐘和字時鐘。位時鐘是采樣時鐘速度的6X,而字時鐘與采樣時鐘的速度相同。

2018-05-14 11:02:10 3

3 ADS527x是一個高性能的模數轉換器(ADC)系列,其特點是串行化的低電壓差分信號(LVDS)輸出。每個通道中的數據被保留并在LVDS格式的一對引腳上發送出去。除了減少多通道ADC的小數和封裝大小外,串行化還簡化了多通道ADC輸出到接收機的路由。

2018-05-16 08:44:24 4

4 EQCD系列高數據速率電纜組件來傳輸和接收TI ADS8410/13 ADC的數字信號的指南。高速同軸電纜SAMTEC EQCD-02040.00 TBL-SBR-1被用作ADS8410/13提供高速(200 Mbps)LVDS接口。

2018-05-24 10:13:24 1

1 ,且抗電磁干擾(EMI)能力也比較差,會對RGB數據造成一定的影響;另外,TTL多路數據信號采用排線的方式來傳送,整個排線數量達幾十路,不但連接不便,而且不適合超薄化的趨勢。采用LVDS輸出接口傳輸數據,可以使這些問題迎刃而解,實現數據的高速率、

2018-08-28 08:00:00 19

19 本文檔的主要內容詳細介紹的是LVDS接口分類和時序及輸出格式的詳細資料說明。

2019-04-30 08:00:00 9

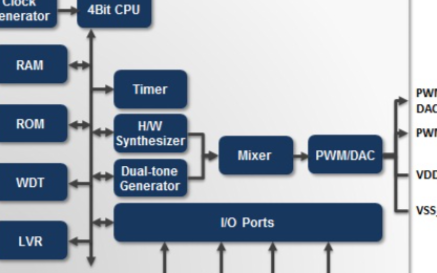

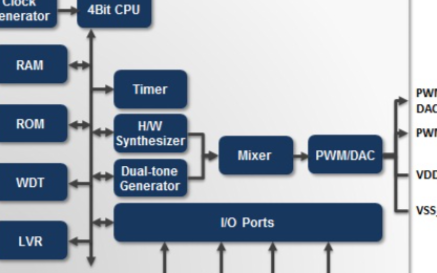

9 范圍從2.2V ~ 5.5V。可以透過軟件及韌體(F/W library)Ultra-IO功能,提供W584A065程序設計者從而簡化了過程定義的輸出模式。 W584A065還提供了數字模擬轉換器

2020-02-03 11:21:53 696

696

LVDS信號不僅是差分信號,而且還是高速數字信號。因此LVDS傳輸媒質不管使用的是PCB線還是電纜,都必須采取措施防止信號在媒質終端發生反射,同時應減少電磁干擾以保證信號的完整性。

2020-03-08 13:14:00 1810

1810 當共模信號較難處理或對系統有負面影響的時候,需要進行信號調理。部分系統的設計會將模擬變換器輸出的單端信號轉為全差分信號,然后將這些信號傳送到差分輸入ADC。這種設計的優點是,大部分混入差分線路的噪聲會同時出現在兩條線路上 (假設差分線路都是按差分方式平衡布局)。

2020-04-12 10:00:11 1246

1246 LVDS信號的電壓擺幅只有350MV, 為電流驅動的差分信號方式工作,最長的傳輸距離可以達到10米以上。為了確保信號在傳輸線當中傳播時,不受反射信號的影響,LVDS信號要求傳輸線阻抗受控,其中單線

2020-12-30 16:57:25 11

11 AD9229:4通道、12位、50/65 MSPS、串行LVDS、3 V ADC

2021-03-19 13:23:40 7

7 ADCLK846:1.8 V、6 LVDS/12 CMOS輸出低功耗時鐘扇出緩沖器

2021-03-20 11:31:10 9

9 AD9222:8通道、12位、40/50/65 MSPS、串行LVDS、1.8 V ADC 數據手冊

2021-03-21 09:24:35 7

7 AD9522-5:12 LVDS/24 CMOS輸出時鐘發生器數據表

2021-04-28 10:53:01 0

0 具有LVDS輸出的LTM9011 ADC的AN147-Altera Stratix IV FPGA接口

2021-05-09 21:19:53 14

14 電子發燒友網為你提供ADI(ti)DC065A-B相關產品參數、數據手冊,更有DC065A-B的引腳圖、接線圖、封裝手冊、中文資料、英文資料,DC065A-B真值表,DC065A-B管腳等資料,希望可以幫助到廣大的電子工程師們。

2021-08-17 08:00:02

嵌入式log打印格式輸出技巧Log 信息格式條件編譯可變參數宏C標準中一些預定義的宏格式輸出16進制數組Log 信息格式參考目前主流嵌入式、安卓等輸出方式:[日志級別] 文件名 : 日志信息

2021-10-20 21:06:01 5

5 GM8827C實現以7:1的壓縮比將27位CMOS/TTL信號(RGB 8位和HSYNC、VSYNC、 DE)換成串行 LVDS 輸出數據流。輸入時鐘經內部鎖相后,同頻率輸出,同時轉換為 LVDS

2021-11-30 21:06:05 8

8 產品概述 ? ? GM8285C型1.8V低功耗28位LVDS發送器,其功能是將并行數據編碼為高速串行數據,實現信號的快速可靠傳輸。該器件可將28位并行數據轉換為4對串行LVDS差分信號,同時并行

2022-06-02 17:01:40 4419

4419 在數據傳輸過程中,還必須有時鐘信號的參與,LVDS端口無論傳輸數據還是傳輸時鐘,都采用差分信號對的形式進行傳輸。所謂信號對,是指LVDS端口電路中,每一個數據傳輸通道或時鐘傳輸通道的輸出都為兩個信號

2023-08-03 17:16:06 763

763

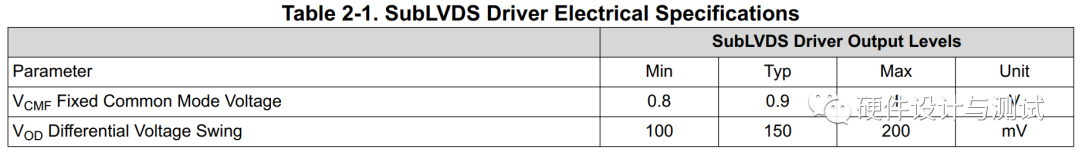

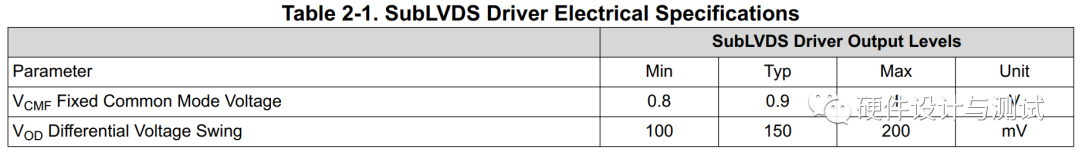

的性能水平時,由于有比傳統模式更好的抗電源噪聲能力,它可以在噪聲容限低得多,而且擺幅也低得多的情況下工作。目前,Sub-LVDS技術在Sony的Camera/Sensor中比較常見,主要傳輸的數據格式為RAW10或者RAW12。SUB-LVDS的電壓更低,共模電壓為1.8V,差模電壓為150mV。

2023-09-15 14:47:10 1558

1558

LVDS發送芯片的輸入信號來自主控芯片,輸入信號包含RGB數據信號、時鐘信號和控制信號三大類。

2023-10-17 17:28:13 583

583

LVDS傳輸的是什么信號?判斷LVDS信號正常的方法 一、LVDS傳輸的是什么信號? LVDS是一種低電壓差分信號,有兩種電壓狀態,即高電平和低電平,它類似于RS485協議。LVDS信號作為一種數字信號

2023-10-18 15:38:13 2929

2929 什么是LVDS和RSDS圖象信號?幫忙解釋一下LVDS和RSDS這兩種傳輸協議吧? LVDS和RSDS都是用于傳輸數字圖像信號的串行通信協議。它們都是由電子工業界制定的標準,旨在提高圖像傳輸速度

2023-10-18 15:38:16 1232

1232 什么叫做LVDS信號?請問TTL信號與LVDS信號有什么區別? LVDS信號 LVDS(Low Voltage Differential Signaling)又稱低壓差分信號傳輸技術,是一種采用

2023-10-18 15:38:18 1265

1265 LVDS中的時鐘脈沖信號是干什么的? LVDS(Low Voltage Differential Signaling)中的時鐘脈沖信號(Clock)是用于同步數據傳輸的,是整個LVDS接口的重要

2023-10-18 15:38:20 662

662 雙路LVDS信號和單路的時鐘頻率有什么關系?是一個時鐘內傳輸兩個像素的數據嗎? 雙路LVDS信號是一種在高速數據傳輸上應用廣泛的接口,它利用微小的電壓擺動來傳輸數據。在雙路LVDS信號中,數據被分成

2023-10-18 15:38:22 972

972 請教關于LVDS阻抗匹配的問題 LVDS輸出阻抗偏大會出現什么情況? LVDS(Low Voltage Differential Signaling)是差分信號傳輸技術,能夠提供較高的數據傳輸速率

2023-10-18 16:48:38 1074

1074 供應SD8666QS12V3ASSR反激電源管理芯片,提供sd8666qs數據手冊及相關資料,更多產品手冊、應用料資請向驪微電子申請。>>

2022-12-13 14:23:00 8

8

電子發燒友App

電子發燒友App

評論