本文介紹了一種基于NIOS II軟核處理器實(shí)現(xiàn)對LCD-LQ057Q3DC02控制的新方法。在設(shè)計中利用FPGA的Altera的SOPC Builder定制NIOS II軟核處理器及其與顯示功能相關(guān)的“軟” 硬件模塊來協(xié)同實(shí)現(xiàn)顯示控

2011-11-09 11:30:07 2000

2000

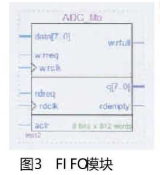

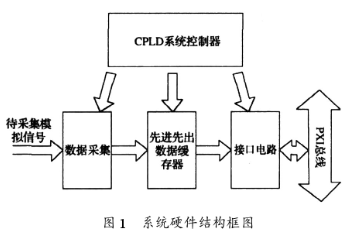

FIFO緩沖后連續(xù)不斷的通過PCIe接口傳輸?shù)街鳈C(jī)內(nèi)存或硬盤中。。北京坤馳科技有限公司基于數(shù)據(jù)采集與控制部分,為用戶提供一套解決方案,涉及到信號的采集存儲或處理。二、系統(tǒng)框圖 三、系統(tǒng)組成1、采集模塊

2016-07-25 11:35:43

我用EP3C16F芯片搭建了一個圖像采集、處理和顯示系統(tǒng),sdram設(shè)計為一個輸入兩個輸出,一個輸出送給vga控制器,另外一個輸出送到nios上的圖像處理模塊。vga沒有掛在sopc builder上,我想問一下,從sdram中輸出的數(shù)據(jù)在nios上處理后,怎樣再讓它顯示到vga上?

2015-05-19 16:43:49

系統(tǒng)的設(shè)計提出兩個方面的要求:一方面,要求接口簡單靈活且有較高的數(shù)據(jù)傳輸率;另一方面,由于數(shù)據(jù)量通常都較大,要求主機(jī)能夠?qū)?b class="flag-6" style="color: red">數(shù)據(jù)做出快速反應(yīng),并及時分析和處理。那么想要實(shí)現(xiàn)數(shù)據(jù)的高速采集,具體還要哪些方法呢?

2019-07-31 07:25:28

AD,DA,COUNTER等轉(zhuǎn)換芯片開始,數(shù)據(jù)采集卡不過是集合了各種AD,DA,COUNTER等芯片,結(jié)合專門的微處理器和總線通訊在一起,使板卡具有了綜合采集功能。數(shù)據(jù)采集卡都有AD轉(zhuǎn)換精度,速度和通道數(shù)

2009-07-01 16:12:46

偏硬件:接口電路中的門組合電路;偏軟件:算法、接口控制器實(shí)現(xiàn)中的狀態(tài)機(jī)群或時序電路。隨著邏輯設(shè)計的深入,復(fù)雜功能設(shè)計一般基于同步時序電路方式。此時,邏輯設(shè)計基本上就是在設(shè)計狀態(tài)機(jī)群或計數(shù)器等時序電路

2021-11-10 06:39:25

多個AD7656-1級聯(lián)形成菊花鏈實(shí)現(xiàn)多個通道同時進(jìn)行數(shù)據(jù)采集,并通過一個或多個串口發(fā)送數(shù)據(jù)給主控處理器。以S3C2410A為主控處理器,多個AD7656-1組成菊花鏈實(shí)現(xiàn)多通道、高精度的ADC,在很大程度

2018-11-26 11:16:15

ARM I2C 總線接口模塊在數(shù)據(jù)采集中的應(yīng)用在以ARM S3C44BOX為核心處理器的新型流量積算儀表的設(shè)計中,利用ARM自帶的12C總線接口模塊擴(kuò)展了A/D轉(zhuǎn)換芯片

2009-03-14 18:06:30

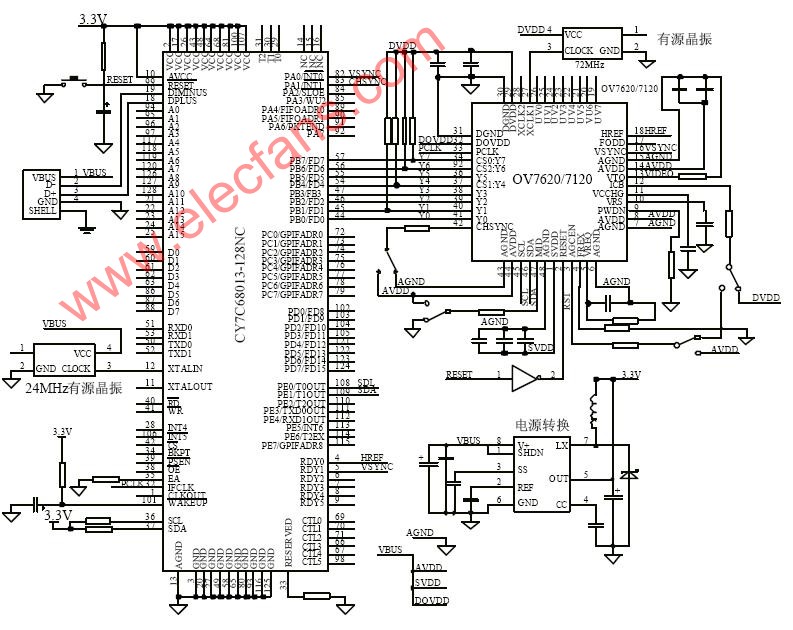

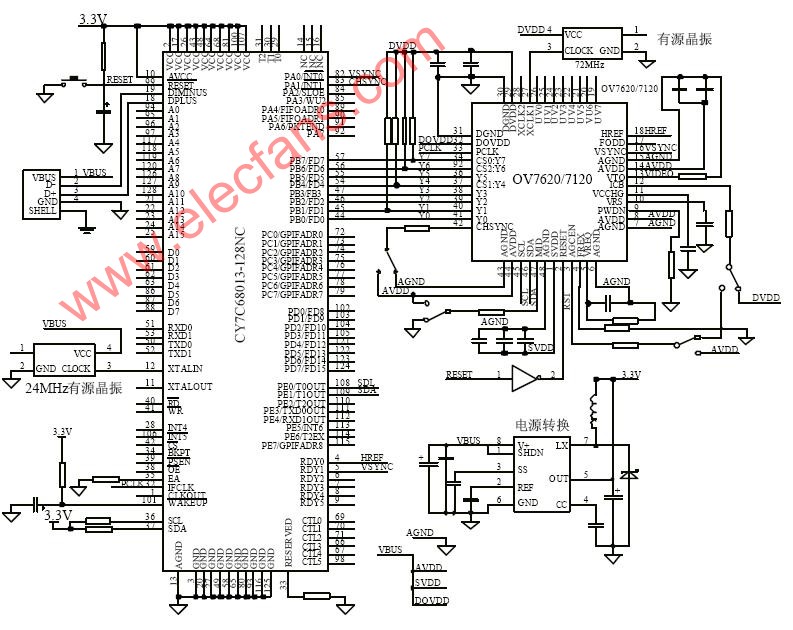

核心,以WinCE為軟件平臺,能實(shí)時、連續(xù)地采集清晰的視頻數(shù)據(jù)。1 系統(tǒng)結(jié)構(gòu)框圖及視頻數(shù)據(jù)采集原理視頻數(shù)據(jù)采集系統(tǒng)結(jié)構(gòu)如圖1所示。從圖1中可以看出。系統(tǒng)由嵌入式微處理器S3C2440、存儲器(包括

2019-08-06 08:30:15

在其業(yè)內(nèi)領(lǐng)先的低成本Cyclone TM FPGA系列和Nios軟核嵌入式處理器成功的基礎(chǔ)上,Altera現(xiàn)在推出了第二代產(chǎn)品系列。Cyclone II器件為用戶提供更高的邏輯密度和新增硬件性能,比

2019-07-18 07:43:25

TMS320VC5509 為核心的數(shù)據(jù)采集處理系統(tǒng),通過對FIFO、SDRAM 和TMS320VC5509 DMA 控制器的介紹,分別給出了具體的接口電路硬件設(shè)計和實(shí)際軟件的代碼示例。關(guān) 鍵 詞

2009-04-28 10:47:02

的EZ-USB FX2系列智能USB接口芯片。其作用是將主機(jī)所發(fā)送的命令序列經(jīng)USB2.0端口輸出,實(shí)現(xiàn)對數(shù)據(jù)采集系統(tǒng)的控制;同時把A/D轉(zhuǎn)換器采集的數(shù)據(jù)以高速的數(shù)據(jù)序列形式發(fā)送到主機(jī)。其中,USB2.0端口

2020-01-07 07:00:00

FPGA處理數(shù)據(jù)的時間,所以整個系統(tǒng)實(shí)現(xiàn)了流水線操作。1 系統(tǒng)的總體設(shè)計系統(tǒng)硬件主要由信號采集模塊、FIFO、FPGA和SEP3203處理器組成。信號采集模塊主要包括信號接收器和A/D轉(zhuǎn)換模塊。接收

2019-04-26 07:00:06

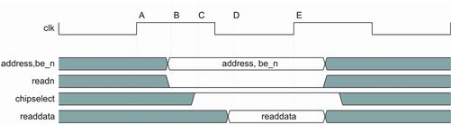

到IDT7202的寫端口。確保采集到的數(shù)據(jù)為有效數(shù)據(jù)。 圖3是SEP3203處理器輸入到FPGA內(nèi)部的控制信號的仿真波形圖。in_rst_n_a是復(fù)位信號,in_we_n和in_cs_n是SEP3203

2018-12-05 10:13:09

圖像數(shù)據(jù)進(jìn)入預(yù)處理模塊,經(jīng)預(yù)處理后的圖像數(shù)據(jù)送入SDRAM存儲器,由Nios II處理器進(jìn)行圖像的后續(xù)處理和控制。處理后的圖像經(jīng)數(shù)模轉(zhuǎn)換在監(jiān)視器上實(shí)時顯示。 1.1 圖像采集接口電路設(shè)計 本系統(tǒng)

2018-10-31 16:54:52

數(shù)據(jù)采集與控制單元,以CYPRESS公司的高速USB接口芯片CY7C68001為基礎(chǔ),利用DSP片上A/D轉(zhuǎn)換器采集數(shù)據(jù),經(jīng)處理后把數(shù)據(jù)通過USB總線傳輸至PC機(jī),PC機(jī)接收到數(shù)據(jù)后按照用戶的要求通過

2014-12-16 11:32:57

數(shù)據(jù)采集模塊、碰撞壓力處理電路等組成的外圍設(shè)備,還有以32位Nios II CORE為主體的核心邏輯兩個主要部分組成,系統(tǒng)終端硬件框圖如圖1所示。1.1 外圍設(shè)備外圍設(shè)備是指某些具體控制電路或模塊接口

2015-01-30 11:05:50

采集。對于兩路數(shù)據(jù)采集電路,A/D與DSP的接口連接是一樣的。兩個A/D同時將和路與差路信號采樣,并分別送入兩個FIFO;DSP分時從兩個FIFO中讀出采集的數(shù)據(jù),完成數(shù)據(jù)的采集。1 數(shù)據(jù)采集系統(tǒng)組成

2012-12-25 15:45:49

對數(shù)據(jù)采集與處理系統(tǒng)提出了新的更高的要求,即高速度、高精度和高實(shí)時性。對數(shù)據(jù)采集與處理系統(tǒng)的設(shè)計,有以下3種方案可供選擇:(1)A/D+DSP方案在傳統(tǒng)的高速信號處理中,大多采用這種方案。將A/D、D

2019-07-05 06:41:27

。本系統(tǒng)的高速信號采集卡主要由信號調(diào)制電路、數(shù)據(jù)采集模塊、采集時鐘控制模塊、數(shù)據(jù)緩存和邏輯控制模塊、PCI Express總線接口控制等部分組成。其中邏輯控制模塊負(fù)責(zé)接收來自PCIExpress接口的主機(jī)

2019-06-11 05:00:06

、學(xué)術(shù)界和研究實(shí)驗(yàn)室所接受,越來越多地應(yīng)用在虛擬儀器、測試測量、數(shù)據(jù)分析、信號處理以及遠(yuǎn)程控制中。本設(shè)計中,遠(yuǎn)程數(shù)據(jù)采集系統(tǒng)采用基于ARM和嵌入式Linux的方案來實(shí)現(xiàn)。采用高性能的ARM嵌入式微處理器

2019-04-11 09:40:06

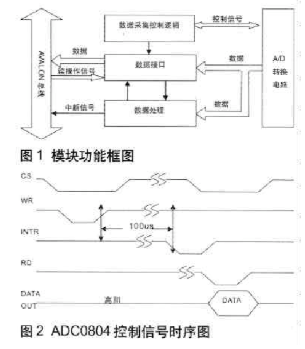

`一、項目設(shè)計背景及概述 本文介紹了基于單片機(jī)的數(shù)據(jù)采集系統(tǒng)。數(shù)據(jù)采集技術(shù)是信息科學(xué)的重要分支之一, 它研究信息數(shù)據(jù)的采集、存儲、處理以及控制等問題。它是對傳感器信號的測量與處理, 以微型計算機(jī)等高

2014-01-11 18:15:49

GPS 新型授時方法,結(jié)合 DSP 技術(shù)和 USB 通信技術(shù)設(shè)計的數(shù)據(jù)采集系統(tǒng)能較好地解決這個問題。1 數(shù)據(jù)采集系統(tǒng)的總體硬件構(gòu)成與工作原理數(shù)據(jù)采集系統(tǒng)模擬量輸人、同步采樣控制、A/D 轉(zhuǎn)換以及微處理器

2020-09-05 19:12:19

基于NIOS II 軟核處理器的SOPC 技術(shù)摘要:介紹了基于NIOS II 軟核處理器的SOPC 技術(shù),分析了傳統(tǒng)方法和基于SOPC 技術(shù)的方法實(shí)現(xiàn)擴(kuò)頻收發(fā)機(jī)的優(yōu)劣,詳細(xì)說明了嵌有雙NIOS II

2009-10-06 15:05:24

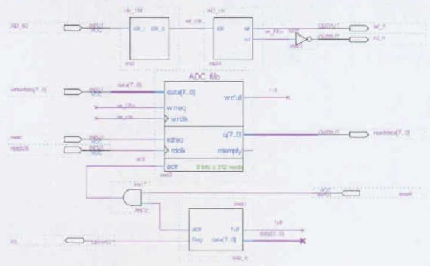

在FPGA系統(tǒng)中,實(shí)現(xiàn)對外部A/D數(shù)據(jù)采集電路的控制接口邏輯,由于其邏輯功能不是很復(fù)雜,因此可采用自定義的方式。采用這種方法進(jìn)行設(shè)計有兩種途徑。①從軟件上去實(shí)現(xiàn)。這種方案將NIOS處理器作為一個主控制器

2019-04-17 07:00:01

在FPGA系統(tǒng)中,實(shí)現(xiàn)對外部A/D數(shù)據(jù)采集電路的控制接口邏輯,由于其邏輯功能不是很復(fù)雜,因此可采用自定義的方式。采用這種方法進(jìn)行設(shè)計有兩種途徑。①從軟件上去實(shí)現(xiàn)。這種方案將NIOS處理器作為一個主控制器

2019-04-25 07:00:02

摘要:設(shè)計了一種在Nios II處理器上的CCD數(shù)據(jù)采集系統(tǒng)。電荷耦合器件(Charge-Coupled Device,CCD)采集到的信號經(jīng)過前端的差分運(yùn)放處理后再進(jìn)行A/D轉(zhuǎn)換,轉(zhuǎn)換后的數(shù)據(jù)存儲

2019-06-03 05:00:06

CMOS傳感器件,本指紋采集系統(tǒng)采用傳感器的微處理器總線(MCU)模式,傳感器的8位數(shù)據(jù)線直接與DE2開發(fā)板的擴(kuò)展口相接,采用Nios II自定義外設(shè)的接口形式來對FPS200指紋圖像傳感器進(jìn)行初始化控制

2019-04-29 07:00:08

的數(shù)據(jù)采集系統(tǒng)設(shè)計。上位PC則采用了C#語言編程,將采集到的數(shù)據(jù)實(shí)時顯示、處理分析、數(shù)據(jù)保存和打印。 硬件電路設(shè)計 本系統(tǒng)以ADI公司的ADuC841為核心實(shí)現(xiàn)數(shù)據(jù)采集和控制。此單片機(jī)具有單指令周期

2018-12-12 10:23:10

的網(wǎng)絡(luò)數(shù)據(jù)傳輸。3、 系統(tǒng)結(jié)構(gòu)高速同步數(shù)據(jù)采集系統(tǒng)主要包括以下幾個部分:ARM控制器、存儲電路、FPGA邏輯控制電路、A/D轉(zhuǎn)換電路、FIFO緩存、電源電路、接口電路等。系統(tǒng)具備多通道數(shù)據(jù)采集接口

2010-08-31 09:14:55

接口,它使電路工作在更加平穩(wěn)、簡潔而易丁控制,同時也提高了ARM的工作效率。為了提高通信速度,這里采用通用申行總線(USB)技術(shù)米與PC進(jìn)行通信。ARM是用來控制主處理器的數(shù)據(jù)采集,數(shù)據(jù)的計算和數(shù)據(jù)傳輸。結(jié)果證明,整個系統(tǒng)能高效運(yùn)作。該系統(tǒng)可應(yīng)用于高速數(shù)據(jù)采集及多路模擬信號的工作環(huán)境下。

2023-09-26 07:41:28

/模轉(zhuǎn)換器DAC0832構(gòu)成一個數(shù)據(jù)采集系統(tǒng),并用CPLD/FPGA實(shí)現(xiàn)數(shù)據(jù)采樣、D/A轉(zhuǎn)換輸出、有關(guān)數(shù)據(jù)顯示的控制,單片機(jī)完成對A/D轉(zhuǎn)換數(shù)據(jù)運(yùn)算。電路如圖1所示。系統(tǒng)功能如下:系統(tǒng)按一定速率采集輸入

2018-12-10 10:18:34

1 背景知識隨著信息技術(shù)的發(fā)展,特別是各種數(shù)字處理器處理速度的提高,人們對數(shù)據(jù)采集系統(tǒng)的要求越來越高,特別是在一些需要在極短時間內(nèi)完成大量數(shù)據(jù)采集的場合,對數(shù)據(jù)采集系統(tǒng)的速度提出了非常高的要求

2018-08-09 14:28:00

了如何通過FPGA實(shí)現(xiàn)RS 232接口的時序邏輯設(shè)計。關(guān)鍵詞:FPGA;時序電路;RS 232;串行通信

2019-06-19 07:42:37

基于FPGA的數(shù)據(jù)采集系統(tǒng)IEE ... 介紹了數(shù)據(jù)采集系統(tǒng)中以FPGA為處理核心、采用TI公司接口芯片的IEEE1394接口設(shè)計,給出了系統(tǒng)硬件設(shè)計和FPGA邏輯設(shè)計,討論了IEEE1394總線

2012-08-11 15:43:47

的輸入輸出接口設(shè)計就顯得尤為重要。1 高速采集系統(tǒng)介紹 數(shù)據(jù)采集系統(tǒng)原理框圖如圖1所示,輸入的中頻信號經(jīng)A/D采樣電路采樣后,轉(zhuǎn)換成LVDS信號送入FPGA中,或通過FPGA的端口RocketIO從高速接口

2018-12-18 10:22:18

數(shù)據(jù)采集與控制單元,以CYPRESS公司的高速USB接口芯片CY7C68001為基礎(chǔ),利用DSP片上A/D轉(zhuǎn)換器采集數(shù)據(jù),經(jīng)處理后把數(shù)據(jù)通過USB總線傳輸至PC機(jī),PC機(jī)接收到數(shù)據(jù)后按照用戶的要求通過

2018-12-26 07:00:05

A/D轉(zhuǎn)換器采集數(shù)據(jù),暫存于數(shù)據(jù)緩沖區(qū),再根據(jù)主機(jī)命令發(fā)給主機(jī)。這部分功能由一個單片機(jī)及接口來實(shí)現(xiàn)是最優(yōu)方式。 數(shù)據(jù)通信部分應(yīng)包含:簡單、高效、通用的數(shù)據(jù)通信模式和軟硬件支持。它應(yīng)能在數(shù)據(jù)采集和數(shù)據(jù)處理

2018-07-02 05:07:53

基于PIC單片機(jī)USB接口的數(shù)據(jù)采集系統(tǒng)設(shè)計 我們把所設(shè)計的數(shù)據(jù)采集系統(tǒng)功能分解為三大部分:數(shù)據(jù)采集部分、數(shù)據(jù)通信部分、數(shù)據(jù)處理部分。 數(shù)據(jù)采集部分應(yīng)包含:A/D轉(zhuǎn)換器,時序、模式控制,數(shù)據(jù)緩沖

2017-08-23 11:30:01

、BD429A;? PCI總線接口電路PCI9054;? 邏輯控制電路XC95288XL;? 提供+5V轉(zhuǎn)+15V、-15V電路DCP020515DP,負(fù)載80mA。處理器及存儲電路處理器處理器選用TI

2019-05-22 05:01:15

數(shù)據(jù)采集與控制單元,以CYPRESS公司的高速USB接口芯片CY7C68001為基礎(chǔ),利用DSP片上A/D轉(zhuǎn)換器采集數(shù)據(jù),經(jīng)處理后把數(shù)據(jù)通過USB總線傳輸至PC機(jī),PC機(jī)接收到數(shù)據(jù)后按照用戶的要求通過

2019-05-07 09:40:04

A/D轉(zhuǎn)換和預(yù)處理,通過RS-232串行口與主機(jī)進(jìn)行信息傳送,插拔方便。主機(jī)通過數(shù)據(jù)處理軟件對數(shù)據(jù)進(jìn)行處理和分析。用戶可以通過主機(jī)的軟件界面對單片機(jī)(從機(jī))進(jìn)行控制,使之能按照不同的要求對信號進(jìn)行數(shù)據(jù)采集和處理。

2011-03-09 15:52:25

.應(yīng)用可編程邏輯器件EPM7128SLC和8路模擬多路選擇器ADG508A實(shí)現(xiàn)采集信號的選通設(shè)計,介紹單片機(jī)80C196KB內(nèi)A/D轉(zhuǎn)換器在采集電路中的使用方法,使用雙端口存儲器IDT7130實(shí)現(xiàn)數(shù)據(jù)的雙機(jī)傳輸

2011-03-08 14:24:55

1 引言 圖像采集是數(shù)字圖像處理、圖像識別和機(jī)器視覺的基礎(chǔ),其應(yīng)用領(lǐng)域非常廣泛。主要采用CCD或CMOS等光電轉(zhuǎn)換器件把光學(xué)影像轉(zhuǎn)化為數(shù)字信號,然后利用相應(yīng)的接口將數(shù)據(jù)輸入到處理器中進(jìn)行圖像

2019-07-02 08:11:34

該文檔為基于FPGA的多路模擬數(shù)據(jù)采集接口設(shè)計講解文檔,介紹一種基于 8,RQ 的多路模擬數(shù)據(jù)采集接口的設(shè)計方案。該方案使用Max1281 作為模數(shù)轉(zhuǎn)換芯片,在 APA150 FPGA 中設(shè)計和實(shí)現(xiàn)了相關(guān)的接口控制、配置和數(shù)據(jù)存儲模塊;給出了系統(tǒng)設(shè)計框圖、FPGA開發(fā)要點(diǎn)和仿真波形。

2018-09-21 14:37:00

高質(zhì)量的A/D采集卡及調(diào)理放大器是影響其發(fā)展的一個重要因素,如何設(shè)計一款基于USB接口的實(shí)用型數(shù)據(jù)采集卡?

2021-04-07 06:40:16

在FPGA系統(tǒng)中,如何實(shí)現(xiàn)對外部A/D數(shù)據(jù)采集電路的控制接口邏輯?如何設(shè)計NIOS系統(tǒng)外設(shè)方面?

2021-04-12 07:16:31

本文使用符合PCI電氣特性的FPGA芯片進(jìn)行簡化的PCI接口邏輯設(shè)計,實(shí)現(xiàn)了33MHz、32位數(shù)據(jù)寬度的PCI從設(shè)備模塊的接口功能,節(jié)約了系統(tǒng)的邏輯資源,且可以將其它用戶邏輯集成在同一塊芯片,降低了成本,增加了設(shè)計的靈活性。

2021-05-08 08:11:59

前言FPGA 可以實(shí)現(xiàn)高速硬件電路,如各種時鐘,PWM,高速接口,DSP計算等硬件功能。這是Cortex-M 處理器軟件無法比擬的。要實(shí)現(xiàn)FPGA 的邏輯設(shè)計,對于嵌入式系統(tǒng)工程師又是比較復(fù)雜和具有

2021-12-21 06:13:49

的可編程邏輯器件EPM7256A完成對數(shù)據(jù)的緩存和傳輸?shù)母鞣N時序控制以及開關(guān)量采樣時序、路數(shù)判別。采用FIFO器件作為高速A/D與DSP處理器間的數(shù)據(jù)緩沖,有效地提高了處理器的工作效率。

2020-12-31 07:52:43

CLC5958的內(nèi)部結(jié)構(gòu)及基本特性CLC5958應(yīng)用的注意事項有哪些采用可編程邏輯器件和A/D轉(zhuǎn)換器組成的高速數(shù)據(jù)采集卡的設(shè)計方案

2021-04-15 06:50:05

。FPGA - 包含數(shù)據(jù)采集控制和邏輯(包括觸發(fā)邏輯)、檢錯、DSP 接口、存儲器地址解碼器、計數(shù)器和輸出控制。控制邏輯選擇一個數(shù)據(jù)采集時鐘,處理各種觸發(fā)器,并將獲取的數(shù)據(jù)傳輸至數(shù)據(jù)采集通道的內(nèi)部存儲器中

2012-12-12 11:48:15

或者DSP為核心,控制數(shù)據(jù)采集并對數(shù)據(jù)進(jìn)行相應(yīng)處理,A/D轉(zhuǎn)換器的啟動、通道選擇、數(shù)據(jù)傳輸和讀取均依靠軟件編程來實(shí)現(xiàn)。

2019-08-15 07:07:46

或者DSP為核心,控制數(shù)據(jù)采集并對數(shù)據(jù)進(jìn)行相應(yīng)處理,A/D轉(zhuǎn)換器的啟動、通道選擇、數(shù)據(jù)傳輸和讀取均依靠軟件編程來實(shí)現(xiàn)。由于受MCU或者DSP執(zhí)行指令時間的限制,這種采集方案的速率和效率較低,難以適應(yīng)

2019-08-16 06:57:48

.ARM的功能過于復(fù)雜,適合于設(shè)計好的人機(jī)界面的場合.有些器件將接口協(xié)議處理器和采集卡處理器集成在一體,這些芯片應(yīng)該有更好的使用價值.第五步,選擇數(shù)據(jù)采集電路。很多公司提供采樣芯片:ADI,TI

2013-02-27 15:02:06

數(shù)據(jù)采集邏輯原理圖/電路圖

2019-10-10 09:00:31

”的設(shè)備,既能充分滿足傳感器前端的模擬性能要求,又具備與系統(tǒng)主機(jī)處理器接口相連的足夠靈活性。這樣做還有更多好處。圖 1 闡述了這一理念及上述各種方法。 圖 1. 智能 ADC 數(shù)據(jù)采集系統(tǒng)的發(fā)展 小智慧

2018-11-01 14:40:19

”的設(shè)備,既能充分滿足傳感器前端的模擬性能要求,又具備與系統(tǒng)主機(jī)處理器接口相連的足夠靈活性。這樣做還有更多好處。圖 1 闡述了這一理念及上述各種方法。圖 1. 智能 ADC 數(shù)據(jù)采集系統(tǒng)的發(fā)展 小智慧有大作

2018-12-11 11:06:14

本文設(shè)計了一種在多處理器系統(tǒng)中的Nios II軟核處理器的啟動方案,這個方案在外部處理器向Nios II的程序存儲器和數(shù)據(jù)存儲器加載數(shù)據(jù)時,可以控制Nios II處理器的啟動。

2021-04-27 06:52:42

的采集和處理,多數(shù)是以單片機(jī)或未處理器為控制核心,雖編程簡單、控制靈活,但缺點(diǎn)是單片機(jī)的速度慢、控制周期長。基于FPGA的數(shù)據(jù)采集系統(tǒng)設(shè)計具有開發(fā)周期短,靈活性強(qiáng)、通用性能好、易于開發(fā)、擴(kuò)展等優(yōu)點(diǎn)。下圖

2012-11-05 12:29:34

近年來,隨著可編程邏輯器件(CPLD/FPGA)的迅猛發(fā)展,可編程邏輯器件在數(shù)據(jù)采集、邏輯接口設(shè)計、電平接口轉(zhuǎn)換和高性能數(shù)字信號處理等領(lǐng)域取得越來越廣泛的應(yīng)用。CPLD/FPGAD不僅可以解決電子系

2020-03-05 06:20:45

本系統(tǒng)的電原理如上圖,CH371是USB接口芯片,MAX197多路AD轉(zhuǎn)換器做數(shù)據(jù)采集,電腦對采集的數(shù)據(jù)進(jìn)行處理。 CH371是南京沁恒電子出品的一種簡單易用的USB接口芯片,它包括芯片本身和計算機(jī)

2021-05-10 07:31:23

怎么實(shí)現(xiàn)A/D數(shù)據(jù)采集接口的設(shè)計?

2021-04-20 07:19:20

怎么設(shè)計一種高速數(shù)據(jù)采集系統(tǒng)?數(shù)據(jù)采集系統(tǒng)的組成及原理是什么?如何實(shí)現(xiàn)高速A/D轉(zhuǎn)換器與DSP的接口設(shè)計?

2021-04-12 06:10:22

是整個溫控系統(tǒng)的硬件基礎(chǔ),其中涉及到溫度采集,與微處理器通信,串口輸出,控制數(shù)模轉(zhuǎn)換芯片等多個組成部分。本文提出一種高效實(shí)用的FPGA接口設(shè)計,它能夠完成協(xié)調(diào)各個組成部分有序工作,準(zhǔn)確、快速實(shí)現(xiàn)數(shù)據(jù)

2020-08-19 09:29:48

的硬件邏輯和外部設(shè)備接口,以及整個系統(tǒng)設(shè)計的邏輯譯碼電路。達(dá)到高度集成的目的。本系統(tǒng)的特點(diǎn)是: 1)NIOSⅡ嵌入式微處理器成本低。開發(fā)周期短,提高了產(chǎn)品的性價比和研發(fā)速度。2)采用可編程邏輯器件使

2019-04-29 07:00:06

的硬件電路SD卡采用SPI總線方式與處理器連接,其電路原理如圖2所示。圖2 SD 卡接口電路圖1.5 NiosII的構(gòu)建過程首先要考慮到的是使用什么樣的Nios II,Nios II分為幾個等級,有標(biāo)準(zhǔn)

2019-05-29 05:00:04

采用sopc內(nèi)嵌32位的軟核處理器nios,實(shí)現(xiàn)了一個uart串行口和以太網(wǎng)接口的轉(zhuǎn)換器(以下簡稱轉(zhuǎn)換器),并基于microtronix公司針對nios處理器移植的μclinux開發(fā)了應(yīng)用程序.其系統(tǒng)結(jié)構(gòu)

2019-04-18 07:00:07

廣泛。 一個實(shí)用的USB數(shù)據(jù)采集系統(tǒng)硬件一般包括微控制器、USB通信接口以及根據(jù)系統(tǒng)需要添加的A/D轉(zhuǎn)換器和EPROM、 SRAM等。為了擴(kuò)展其用途,還可以加上多路模擬開關(guān)和數(shù)字I/O端口。系統(tǒng)的A/D

2019-05-31 07:40:05

廣泛。 一個實(shí)用的USB數(shù)據(jù)采集系統(tǒng)硬件一般包括微控制器、USB通信接口以及根據(jù)系統(tǒng)需要添加的A/D轉(zhuǎn)換器和EPROM、 SRAM等。為了擴(kuò)展其用途,還可以加上多路模擬開關(guān)和數(shù)字I/O端口。系統(tǒng)的A/D

2019-05-28 07:40:01

輸入信號經(jīng)過信號調(diào)理電路濾波、放大后送給C8051F000,此單片機(jī)自帶的A/D轉(zhuǎn)換器將輸入的模擬信號轉(zhuǎn)換為數(shù)字信號,并通過USB接口傳送給計算機(jī)。計算機(jī)也可以通過USB接口向C8051F000發(fā)送

2019-05-23 05:01:03

USB接口的數(shù)據(jù)采集卡原理圖,USB接口的數(shù)據(jù)采集卡電路圖

2009-06-22 19:18:25 814

814 本文介紹一種基于FPGA 和DSP 的高性能PCI 數(shù)據(jù)采集處理卡的電路原理設(shè)計和PCI接口軟件設(shè)計。該數(shù)據(jù)采集處理卡主要采用TI 公司的TMS320C6416 數(shù)字信號處理器和XILINX公司VIRTEX2 系列的

2009-08-24 10:55:32 34

34 本文以Nios II 嵌入式軟處理器為核心,利用USB 控制芯片CH372,設(shè)計了基于Nios II 嵌入式軟處理器的USB 通信接口。本文重點(diǎn)介紹了USB 接口的硬件實(shí)現(xiàn)方案,分析了CH372 的通信流程,并

2009-08-28 11:34:28 33

33 針對圖像處理中數(shù)據(jù)采集與處理的現(xiàn)狀,介紹了基于DSP 和PCI 控制器的高速數(shù)據(jù)的實(shí)時采集、存儲和處理的方法,并分別對電路原理圖的硬件設(shè)計和PCI 接口的軟件設(shè)計做了闡述。

2009-12-31 14:15:32 22

22 在NIOS-II 系統(tǒng)中A/D 數(shù)據(jù)采集接口的設(shè)計與實(shí)現(xiàn)摘要:進(jìn)行 SOPC 開發(fā),很有必要學(xué)習(xí)一下定制NIOS 外設(shè)的方法和技巧。本文就是基于這種目的,詳細(xì)的論述了在NIOS 系統(tǒng)中A/D 數(shù)據(jù)

2010-02-08 09:55:43 23

23 摘要:給出了基于A S M 圖的數(shù)字集成電路控制器的設(shè)計的主要電路實(shí)現(xiàn)方法,并給出了目前最常采用的方法——EDA法.關(guān)鍵詞: A S M 圖; 邏輯設(shè)計; E DA; On e Ho t

2010-04-26 11:25:44 14

14 換體DMA高速數(shù)據(jù)采集電路的CPLD實(shí)現(xiàn)

介紹了換體DMA高速數(shù)據(jù)采集電路原理及其CPLD實(shí)現(xiàn)。用CPLD設(shè)計雙端口RAM緩存、控制譯碼、時序邏輯電路,很好地解決了電路元件所占體積

2009-03-28 15:09:18 666

666

數(shù)據(jù)采集邏輯原理圖

2009-03-29 09:01:31 1728

1728

數(shù)據(jù)采集邏輯原理圖/電路圖

2009-04-17 20:16:17 2913

2913

摘要: 提出了一種基于ISP技術(shù)實(shí)現(xiàn)高速數(shù)據(jù)采集的方法,給出了使用VHDL語言和原理圖完成數(shù)據(jù)采集模塊中地址發(fā)生器和比較電路的部分邏輯設(shè)計,只要將所設(shè)計的

2009-06-20 14:51:20 788

788

本文設(shè)計了一種以嵌入式微處理器Nios為核心的電纜故障檢測儀,應(yīng)用A/D器件和FPGA組成可變頻率的高速數(shù)據(jù)采集系統(tǒng),利用低壓脈沖反射法原理來實(shí)現(xiàn)線纜的斷路、短路、斷路點(diǎn)、短路點(diǎn)

2011-04-23 10:47:07 997

997

基于Nios II 軟核處理器和USB 接口設(shè)計了一種工業(yè)CT 數(shù)據(jù)采集模塊測試系統(tǒng). 論述了系統(tǒng)的方案設(shè)計、硬件設(shè)計、軟件設(shè)計. 利用Nios II 進(jìn)行設(shè)計簡化了系統(tǒng)結(jié)構(gòu),提高了設(shè)計靈活性,優(yōu)化了

2011-09-14 15:12:01 37

37 基于軟核Nios_Ⅱ的SOPC數(shù)據(jù)采集系統(tǒng)的設(shè)計

2016-02-17 10:07:11 36

36 基于ARM處理器的USB數(shù)據(jù)采集系統(tǒng)

2017-09-25 13:41:09 5

5 在現(xiàn)代工業(yè)生產(chǎn)控制系統(tǒng)中,需要實(shí)現(xiàn)大量數(shù)據(jù)的實(shí)時采集和處理,以使生產(chǎn)過程得到及時控制。參考文獻(xiàn)[1]介紹了基于一個模擬開關(guān)CD4052和A/D轉(zhuǎn)換器AD574設(shè)計的數(shù)據(jù)采集卡,可以實(shí)現(xiàn)8路信號采集

2017-12-02 10:05:01 615

615

基于Nios軟核的SoPC系統(tǒng)設(shè)計是整個系統(tǒng)硬件設(shè)計的核心,包括Nios軟核處理器的設(shè)計、數(shù)據(jù)采集控制的設(shè)計、圖像信號FFT分析的實(shí)現(xiàn)、參數(shù)顯示以及RS232通信模塊的設(shè)計等。另外,使用Nios進(jìn)行嵌入式設(shè)計在硬件上必需使用Altera公司的FPGA。

2019-08-21 14:22:37 1074

1074

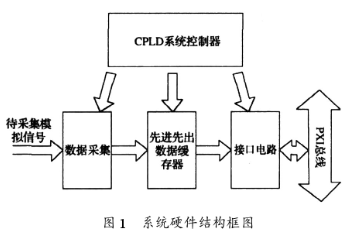

該數(shù)據(jù)采集系統(tǒng)的硬件結(jié)構(gòu)框圖如圖1所示,該系統(tǒng)包括數(shù)據(jù)采集模塊、F先進(jìn)先出數(shù)據(jù)緩存模塊、接口電路模塊和CPLD系統(tǒng)控制器模塊4個部分。待采樣的模擬信號經(jīng)由數(shù)據(jù)采集模塊進(jìn)行數(shù)據(jù)采集,采樣后經(jīng)過轉(zhuǎn)換

2020-04-10 09:17:27 917

917

基于FPGA+STM32雙處理器的高速數(shù)據(jù)采集系統(tǒng)

2021-06-25 10:38:04 64

64

電子發(fā)燒友App

電子發(fā)燒友App

評論