八十年代中期,高密度可編程邏輯器件(Programmable Logic Device,簡稱PLD)的出現(xiàn)開辟了一種數(shù)字邏輯電路實(shí)現(xiàn)的新方式。高密度的PLD可以分成兩大類:復(fù)雜可編程邏輯器件(Complex Programmable Logic Device,簡稱CPLD)和現(xiàn)場可編程門陣列(Field Programmable GateArray,簡稱FPGA),主要基于三種編程技術(shù):有限編程次數(shù)(一般數(shù)百次到上萬次)的EEPROM(電可擦除只讀存儲(chǔ)器)、無限編程次數(shù)的SRAM(靜態(tài)隨機(jī)存儲(chǔ)器)和僅可編程一次的Antifuse(反熔絲)。當(dāng)前,主流的CPLD都是采用基于EEPROM的乘積項(xiàng)(Product Term,簡稱P-Term)結(jié)構(gòu),而主流的FPGA則采用基于SRAM的查找表(Look-up Table,簡稱LUT)結(jié)構(gòu)和基于Antifuse的多路開關(guān)單元結(jié)構(gòu)。其中,基于SRAM的FPGA由于可以在系統(tǒng)中重構(gòu)甚至動(dòng)態(tài)重構(gòu),所以應(yīng)用靈活性最大。

近十年來興起的可重構(gòu)技術(shù)起源于FPGA可編程結(jié)構(gòu)的思想。該技術(shù)在應(yīng)用中可以獲得很好的速度和靈活性之間的折衷,填補(bǔ)了傳統(tǒng)的軟、硬件應(yīng)用實(shí)現(xiàn)方案之間的空白。可重構(gòu)技術(shù)是指利用具有硬件可重構(gòu)結(jié)構(gòu)的電路構(gòu)建系統(tǒng)來滿足較寬范圍應(yīng)用的實(shí)現(xiàn)技術(shù)。采用FPGA作為重構(gòu)系統(tǒng)的核心既可以大大縮短系統(tǒng)開發(fā)時(shí)間,又可以獲得很高的靈活性以節(jié)約資源。FPGA中含有大量的觸發(fā)器(多達(dá)上千個(gè))和結(jié)構(gòu)靈活的LUT,適合實(shí)現(xiàn)細(xì)顆粒度的且基于流水線的通用計(jì)算。對(duì)于可重構(gòu)多總線控制和網(wǎng)絡(luò)中數(shù)據(jù)包相關(guān)的不同協(xié)議處理等應(yīng)用,需要時(shí)時(shí)變換的譯碼和控制。重構(gòu)系統(tǒng)在完成上述應(yīng)用時(shí),需要可以動(dòng)態(tài)重構(gòu)的復(fù)雜狀態(tài)機(jī)和譯碼電路。由于這些電路中組合邏輯復(fù)雜且輸入數(shù)目大而觸發(fā)器很少,因此,用FPGA實(shí)現(xiàn)會(huì)造成單元中觸發(fā)器大量浪費(fèi),而且利用多個(gè)LUT的級(jí)連實(shí)現(xiàn)大輸入的組合邏輯,會(huì)使性能大大降低,難以滿足速度上的要求。

CPLD的結(jié)構(gòu)非常適于實(shí)現(xiàn)上述邏輯功能。但是,CPLD的EEPROM編程速度低且編程次數(shù)有限又不適合要求快速頻繁重構(gòu)的動(dòng)態(tài)重構(gòu)系統(tǒng)的應(yīng)用。

顯然,設(shè)計(jì)基于SRAM編程技術(shù)的CPLD可以很好解決上述應(yīng)用問題。CPLD的設(shè)計(jì)和實(shí)現(xiàn)的關(guān)鍵問題是核心可編程電路結(jié)構(gòu)的實(shí)現(xiàn)。因此,本文主要探討針對(duì)CPLD的核心可編程結(jié)構(gòu),如何設(shè)計(jì)具有相似功能且基于SRAM編程技術(shù)的電路結(jié)構(gòu),從而更好滿足動(dòng)態(tài)重構(gòu)系統(tǒng)中實(shí)現(xiàn)復(fù)雜狀態(tài)機(jī)和譯碼電路的應(yīng)用。

CPLD的核心可編程結(jié)構(gòu)介紹

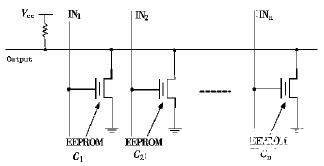

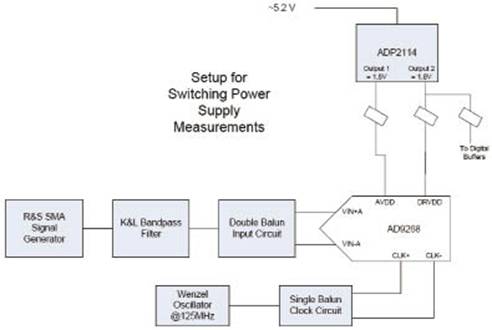

CPLD由若干宏單元和可編程互連線構(gòu)成。每個(gè)宏單元包括5個(gè)乘積項(xiàng)、1個(gè)異或門、1個(gè)5輸入或門和1個(gè)觸發(fā)器。乘積項(xiàng)是宏單元的核心可編程結(jié)構(gòu),可以靈活實(shí)現(xiàn)大輸入數(shù)目寬與門功能。如圖1a所示,P-Term是一個(gè)由EEPROM晶體管構(gòu)成的陣列。該陣列中每個(gè)EEPROM晶體管相當(dāng)于一個(gè)可編程開關(guān),編程之后,處于“開”狀態(tài)的EEP2ROM晶體管同普通晶體管一樣,受柵極輸入控制充當(dāng)寬與門的下拉開關(guān),而處于“關(guān)”狀態(tài)的EEP2ROM晶體管是斷路,柵極的輸入對(duì)寬與門無貢獻(xiàn)。這樣,P-Term所實(shí)現(xiàn)的邏輯功能可由式(1)給出:

(a) 基于EEPROM的可編程寬與門結(jié)構(gòu)

(b) MAX7000中的PIA可編程結(jié)構(gòu)

圖1 電路結(jié)構(gòu)圖

式(1)中,C1~Cn對(duì)應(yīng)圖1(a)中的n個(gè)EEPROM晶體管編程后所處的狀態(tài)。當(dāng)?shù)趇(i=1~n)個(gè)位置的EEPROM晶體管開時(shí),Ci為0,反之,Ci為1。當(dāng)前,主流的CPLD全部采用這種結(jié)構(gòu),比如Altera公司的MAX7000系列和MAX9000系列、Xilinx公司的XC9500系列以及Lattice公司的ispLSI系列等。

可編程互連線是CPLD中另一個(gè)核心可編程結(jié)構(gòu)。該結(jié)構(gòu)是包含大量可編程開關(guān)的互連網(wǎng)絡(luò),提供芯片的I/O引腳和宏單元的輸入輸出之間的靈活互連。具有固定的延時(shí)是CPLD中可編程互連線的最顯著特點(diǎn)。不同于FPGA的分段式可編程互連方式,CPLD結(jié)構(gòu)采用全局式的可編程互連網(wǎng)絡(luò)來集中分配互連線資源,這樣可以使連線路徑的起點(diǎn)到終點(diǎn)延時(shí)固定。而FPGA中連線路徑的起點(diǎn)到終點(diǎn)之間經(jīng)過的分段連線數(shù)目不固定,因此延時(shí)也是不固定的。相比之下,CPLD在實(shí)現(xiàn)較復(fù)雜的組合邏輯時(shí)可以消除信號(hào)之間的歪斜,更容易消除競爭冒險(xiǎn)現(xiàn)象。目前,主流的CPLD全部采用連續(xù)式互連線結(jié)構(gòu),比如MAX7000中的PIA結(jié)構(gòu)和XC9500中的FastCONNECT結(jié)構(gòu)。圖1(b)給出了MAX7000中PIA的邏輯結(jié)構(gòu)。該結(jié)構(gòu)中,每個(gè)編程節(jié)點(diǎn)的EEPROM晶體管控制2輸入與門的1個(gè)輸入端來決定另一輸入端信號(hào)的取舍。

綜上所述,CPLD的核心可編程結(jié)構(gòu)是P-Term和具有固定延時(shí)的可編程互連線結(jié)構(gòu)。

基于SRAM編程技術(shù)的PLD電路結(jié)構(gòu)設(shè)計(jì)

針對(duì)CPLD的核心可編程結(jié)構(gòu)——P-Term和具有固定延時(shí)的可編程互連線,設(shè)計(jì)了基于SRAM編程技術(shù)的新電路結(jié)構(gòu),下面做詳細(xì)介紹。

SRAM編程單元的電路結(jié)構(gòu)設(shè)計(jì)

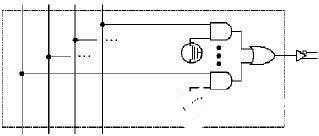

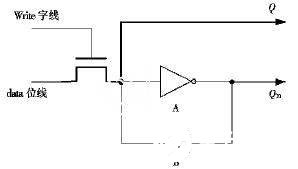

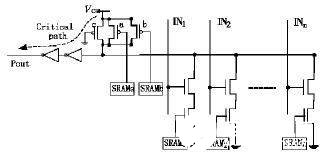

基于SRAM的編程技術(shù)是將PLD的每一位配置數(shù)據(jù)相應(yīng)存儲(chǔ)在SRAM單元中。如圖2a所示,

(a) SRAM編程單元結(jié)構(gòu)

圖2 電路結(jié)構(gòu)與仿真結(jié)果圖

本設(shè)計(jì)采用5管單元的SRAM結(jié)構(gòu)。該結(jié)構(gòu)由2個(gè)CMOS反向器組成環(huán)路形成雙穩(wěn)態(tài)。不同于普通的SRAM,PLD的SRAM編程單元不需要讀出功能,僅需寫入的字線和位線。圖2(a)中的輸出信號(hào)Q和Qn直接控制晶體管開或關(guān)來完成可編程的功能。這種結(jié)構(gòu)設(shè)計(jì)的關(guān)鍵之處在于選擇適當(dāng)?shù)木w管尺寸以保證當(dāng)字線選通位線時(shí),data信號(hào)的正常邏輯值可以改變單元的狀態(tài)。因此,本設(shè)計(jì)確定字線控制的晶體管和反向器A具有較強(qiáng)的驅(qū)動(dòng)能力,而反向器B的驅(qū)動(dòng)能力較弱,適當(dāng)調(diào)節(jié)晶體管的寬長比,以保證編程數(shù)據(jù)的快速寫入。圖2(b)給出了本設(shè)計(jì)中SRAM單元的Hspice仿真結(jié)果(基于2.5V、0.25μmCMOS工藝庫的模型參數(shù),后面的仿真結(jié)果都是基于這個(gè)工藝庫),圖中a和b兩條曲線分別代表信號(hào)Q和Qn。圖2(b)中的(1)和(2)圖分別表示Q和Qn在寫入高電平(單元中存儲(chǔ)的是低電平)和低電平(單元中存儲(chǔ)的是高電平)時(shí)的變化情況。從圖中可以看出,寫入的最大延時(shí)約為650ps,發(fā)生在寫入高電平時(shí)。這樣,該結(jié)構(gòu)完全可以滿足高速重構(gòu)的配置速度要求。

基于SRAM編程技術(shù)的P-Term電路結(jié)構(gòu)設(shè)計(jì)

基于SRAM的P-Term結(jié)構(gòu)的設(shè)計(jì)核心是可編程寬與門的結(jié)構(gòu)設(shè)計(jì),即設(shè)計(jì)能夠?qū)崿F(xiàn)式(1)功能的結(jié)構(gòu)。理論上,實(shí)現(xiàn)式(1)功能的結(jié)構(gòu)有很多,比如采用靜態(tài)CMOS邏輯門或傳輸門構(gòu)成的邏輯,但是P-Term的輸入數(shù)目巨大,可達(dá)88個(gè)輸入,這樣,采用上述結(jié)構(gòu)在電路面積和性能上根本無法接受。而采用類NMOS電路結(jié)構(gòu)在面積和性能上可以獲得很好的效果,但是這種電路在輸出低電平時(shí)存在電源到地的直流通路,存在靜態(tài)功耗,而且輸出低電平不是0,而決定于上拉和下拉倒通電阻的分壓比。可見,這種電路的設(shè)計(jì)重點(diǎn)在于上拉結(jié)構(gòu)的設(shè)計(jì)。本文設(shè)計(jì)的基于SRAM的可編程寬與門電路結(jié)構(gòu)就是以類NMOS結(jié)構(gòu)為基礎(chǔ)的,采用可編程上拉結(jié)構(gòu)控制功耗和性能的折衷。

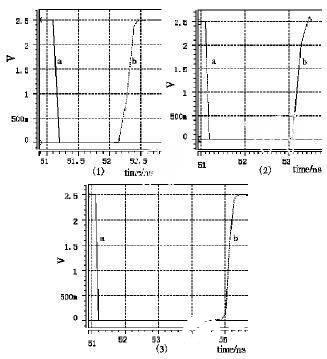

本文設(shè)計(jì)的電路結(jié)構(gòu)如圖3(a)所示,輸入個(gè)數(shù)n=88。采用NMOS晶體管構(gòu)成下拉網(wǎng)絡(luò),對(duì)應(yīng)每一個(gè)輸入的下拉結(jié)構(gòu)是輸入控制的NMOS管串聯(lián)SRAM控制的NMOS管。SRAM中的編程數(shù)據(jù)控制對(duì)應(yīng)晶體管的開關(guān)來決定相應(yīng)的與門輸入的取舍。輸出采用2個(gè)反向器構(gòu)成緩沖,解決類NMOS電路輸出低電平不是0的問題。可編程的上拉結(jié)構(gòu)由a、b、c三個(gè)PMOS管并聯(lián)構(gòu)成,其中PMOS管c常通,a和b受SRAM編程控制開或關(guān)。這樣,該結(jié)構(gòu)在SRAMa和SRAMb的編程控制下,具有三種不同的速度和功耗模式:高速高功耗(PMOS管a和b都通)、中速而功耗中等(a通而b不通)和低速低功耗(a、b都不通)。由于三個(gè)PMOS管的導(dǎo)通電阻要比下拉NMOS管的大很多,本結(jié)構(gòu)的關(guān)鍵路徑是圖中虛線表示的高電平充電路徑。

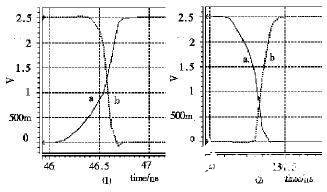

在上述三種工作模式下,關(guān)鍵路徑的Hspice仿真結(jié)果如圖3(b)所示,其中(1)、(2)和(3)圖分別表示三種模式下,輸入信號(hào)由高電平到低電平的變化導(dǎo)致輸出Pout由低電平到高電平的變化情況,曲線a為輸入信號(hào),b為輸出信號(hào)Pout。在高速模式下,關(guān)鍵路徑延時(shí)約為1 .2ns,但電源到地的靜態(tài)電流也達(dá)到了56μA;在中速模式下,關(guān)鍵路徑延時(shí)約為2.2ns,靜態(tài)電流為29μA;在低功耗模式下,關(guān)鍵路徑延時(shí)約為4ns,靜態(tài)電流僅為14μA。

(a) 基于SRAM的可編程寬與門電路結(jié)構(gòu)

(b) 寬與門關(guān)鍵路徑的Hspice仿真結(jié)果

圖3 電路結(jié)構(gòu)與仿真結(jié)果圖

基于SRAM編程技術(shù)的可編程互連線電路結(jié)構(gòu)設(shè)計(jì)

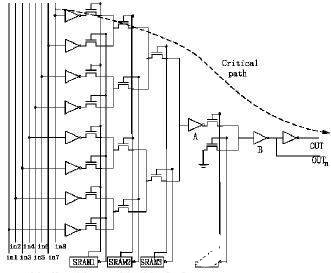

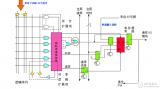

CPLD中可編程互連線的作用是集中分配輸入信號(hào)以固定延時(shí)輸出到宏單元的輸入端(P- Term的輸入端)。本文所設(shè)計(jì)的可編程互連線是由結(jié)構(gòu)完全相同的可編程連線單元組成的二維陣列。可編程連線單元之間不存在互連關(guān)系,每個(gè)單元的輸入信號(hào)直接來自于輸入總線,輸出信號(hào)直接到宏單元,這樣可以保證延時(shí)固定。因此,這種結(jié)構(gòu)的設(shè)計(jì)實(shí)質(zhì)上是可編程連線單元的結(jié)構(gòu)設(shè)計(jì)。

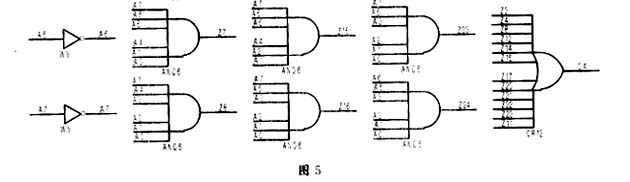

本文設(shè)計(jì)的基于SRAM的可編程連線單元結(jié)構(gòu)如圖4(a)所示。該結(jié)構(gòu)的作用是在8條輸入線中選擇1條或者都不選而僅選擇低電平輸出,然后將選擇的輸出變成正反兩個(gè)信號(hào)輸出到宏單元中P-Term的輸入端。核心結(jié)構(gòu)是SRAM控制的多路選擇器,其中的SRAM編程控制位SRAM1~SRAM3

(a) 基于SRAM的可編程互連單元電路結(jié)構(gòu)

(b) 可編程互連單元關(guān)鍵路徑的Hspice仿真結(jié)果

圖4 電路結(jié)構(gòu)與仿真結(jié)果圖

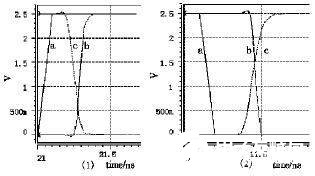

控制多路選擇器實(shí)現(xiàn)8選1的連線狀態(tài),而SRAM4控制開關(guān)管實(shí)現(xiàn)輸出低電平。本設(shè)計(jì)僅用單NMOS管構(gòu)成多路選擇器,相對(duì)于采用傳輸門的情況,每個(gè)開關(guān)減少了1個(gè)晶體管。但是,NMOS傳送高電平存在閾值損耗,因此,在選擇適當(dāng)晶體管尺寸的同時(shí),在第3、4級(jí)開關(guān)處分別加了反向器A和B,保證輸出高電平的幅值和足夠的驅(qū)動(dòng)能力。可編程互連線延時(shí)對(duì)PLD的速度起決定性作用。圖4 (a)中的虛線是本結(jié)構(gòu)的關(guān)鍵路徑,圖4(b)給出了關(guān)鍵路徑的Hspice仿真結(jié)果,(1)和(2)圖分別為輸入信號(hào)上升和下降引起輸出的變化情況,a、b和c三條曲線分別表示輸入總線信號(hào)、輸出的正反信號(hào)OUT和OUTn。仿真結(jié)果表明,本結(jié)構(gòu)的最大延時(shí)僅為300ps。

特別指出,本結(jié)構(gòu)僅用了4bitSRAM編程就實(shí)現(xiàn)了MAX7000的PIA單元中1組開關(guān)的功能,而圖1(b)中的結(jié)構(gòu)需要8bitEEPROM。這樣,本結(jié)構(gòu)同基于EEPROM的結(jié)構(gòu)相比,減少了4bit編程數(shù)據(jù),從而使基于本結(jié)構(gòu)的可編程互連線的編程數(shù)據(jù)減少了50%。編程數(shù)據(jù)的減少,可以縮短器件配置的時(shí)間,提高在重構(gòu)系統(tǒng)應(yīng)用中動(dòng)態(tài)重構(gòu)的效率。

結(jié)論

本文針對(duì)傳統(tǒng)CPLD的核心可編程結(jié)構(gòu)——P-Term和可編程互連線,采用2.5V、0.25μmCMOS工藝設(shè)計(jì)了新的、基于SRAM的可重構(gòu)電路結(jié)構(gòu)。本設(shè)計(jì)中的P-Term結(jié)構(gòu)具有可編程的3種工作模式,可以根據(jù)需要獲得較好的速度和功耗折衷。基于SRAM的、延時(shí)固定的可編程互連線僅有300ps的延時(shí)時(shí)間,可以獲得很高的速度,而且同基于EEPROM的互連線相比編程數(shù)據(jù)減少了50%,可獲得更短的配置時(shí)間,更適合動(dòng)態(tài)重構(gòu)應(yīng)用。采用上述新結(jié)構(gòu)構(gòu)成的PLD比FPGA更適合在可重構(gòu)系統(tǒng)中實(shí)現(xiàn)復(fù)雜狀態(tài)機(jī)和譯碼電路。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論