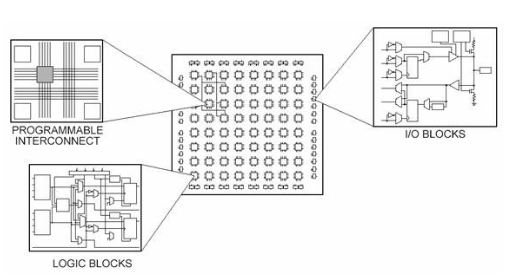

圖2. FPGA的不同部分

FPGA資源規(guī)范通常包括可配置邏輯塊的數(shù)量,固定功能邏輯塊(例如乘法器)的數(shù)量以及存儲(chǔ)器資源(例如嵌入式Block RAM)的大小。在許多FPGA規(guī)范中,當(dāng)為特定應(yīng)用選擇和比較FPGA時(shí),這些規(guī)范通常是最重要的。

可配置邏輯塊(CLB)是FPGA的基本邏輯單元。有時(shí)稱為切片或邏輯單元,CLB由兩個(gè)基本組件組成:觸發(fā)器和查找表(LUT)。各種FPGA系列在觸發(fā)器和LUT封裝在一起的方式上有所不同,因此了解觸發(fā)器和LUT非常重要。

人字拖

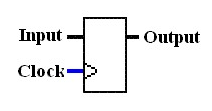

觸發(fā)器是二進(jìn)制移位寄存器,用于在FPGA電路內(nèi)的時(shí)鐘周期之間同步邏輯并保存邏輯狀態(tài)。在每個(gè)時(shí)鐘沿,觸發(fā)器會(huì)在其輸入上鎖存1或0(TRUE或FALSE)值,并將該值保持恒定,直到下一個(gè)時(shí)鐘沿為止。

圖3.觸發(fā)器符號(hào)

觸發(fā)器是二進(jìn)制移位寄存器,用于在FPGA電路內(nèi)的時(shí)鐘周期之間同步邏輯并保存邏輯狀態(tài)。在每個(gè)時(shí)鐘沿,觸發(fā)器會(huì)在其輸入上鎖存1或0(TRUE或FALSE)值,并將該值保持恒定,直到下一個(gè)時(shí)鐘沿為止。

查找表(LUT)

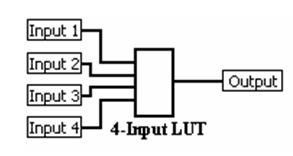

圖4.四輸入LUT

CLB中的許多邏輯都是使用少量LUT形式的RAM來實(shí)現(xiàn)的。很容易假設(shè)FPGA中的系統(tǒng)門數(shù)是指特定芯片中的NAND門和NOR門的數(shù)量。但是,實(shí)際上,所有組合邏輯(AND,OR,NAND,XOR等)都被實(shí)現(xiàn)為L(zhǎng)UT存儲(chǔ)器中的真值表。真值表是每個(gè)輸入組合的預(yù)定義輸出列表。

這是數(shù)字邏輯課的快速入門。

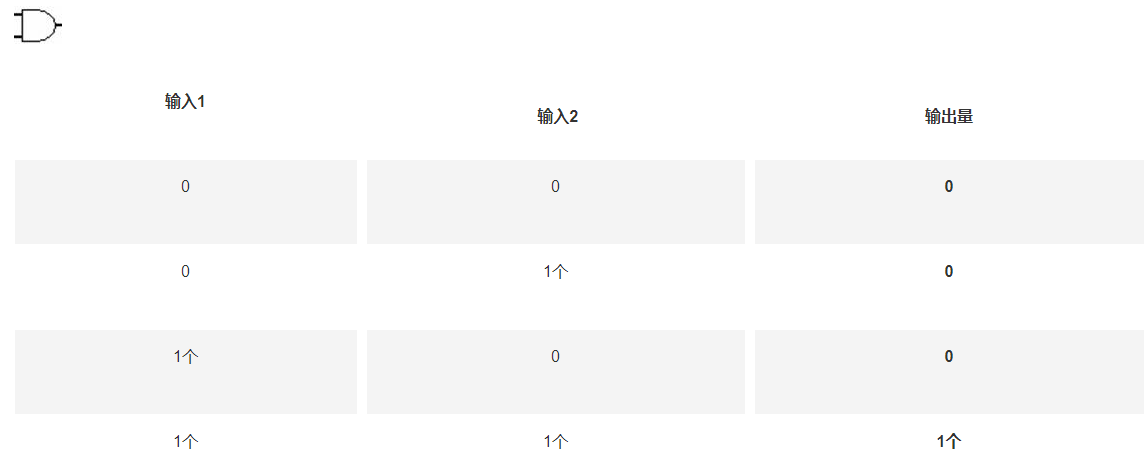

例如,布爾AND操作如圖5所示:

圖5. NI LabVIEW布爾與運(yùn)算

表2列出了與運(yùn)算的兩個(gè)輸入對(duì)應(yīng)的真值表。

表1.布爾“與”運(yùn)算的真值表

乘法器和DSP Slice

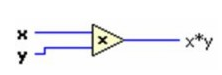

圖6. NI LabVIEW乘函數(shù)

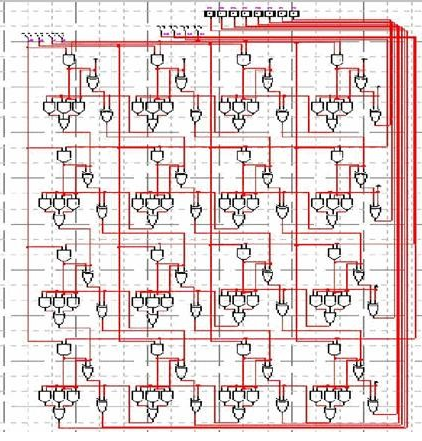

將兩個(gè)數(shù)字相乘的看似簡(jiǎn)單的任務(wù)可能會(huì)占用大量資源,并且在數(shù)字電路中實(shí)現(xiàn)起來非常復(fù)雜。為了提供參考框架,圖6給出了使用組合邏輯實(shí)現(xiàn)4位乘4位乘法器的一種方法的示意圖。

圖7. 4位乘4位乘法器的示意圖

現(xiàn)在想象一下將兩個(gè)32位數(shù)字相乘,一次乘以2,000次運(yùn)算。因此,F(xiàn)PGA預(yù)先構(gòu)建了乘法器電路,以節(jié)省數(shù)學(xué)和信號(hào)處理應(yīng)用中的LUT和觸發(fā)器使用。

許多信號(hào)處理算法都涉及保持連續(xù)的總數(shù)被相乘,因此,諸如Xilinx Virtex-5 FPGA之類的高性能FPGA已預(yù)先構(gòu)建了乘法器累加電路。這些預(yù)構(gòu)建的處理模塊(也稱為DSP48 Slice)將25位乘18位乘法器與加法器電路集成在一起。

塊RAM

存儲(chǔ)器資源是選擇FPGA時(shí)要考慮的另一個(gè)關(guān)鍵指標(biāo)。用戶定義的RAM嵌入整個(gè)FPGA芯片,對(duì)于存儲(chǔ)數(shù)據(jù)集或在并行任務(wù)之間傳遞值很有用。根據(jù)FPGA系列的不同,您可以按16或36 kb的塊配置板載RAM。您仍然可以選擇使用觸發(fā)器將數(shù)據(jù)集實(shí)現(xiàn)為數(shù)組。但是,大型陣列對(duì)于FPGA邏輯資源而言很快變得昂貴。一個(gè)100個(gè)元素的32位數(shù)組可以占用Virtex-II 1000 FPGA中超過30%的觸發(fā)器,或占不到嵌入式Block RAM的1%。數(shù)字信號(hào)處理算法通常需要跟蹤整個(gè)數(shù)據(jù)塊或一個(gè)復(fù)雜方程式的系數(shù),并且沒有板載存儲(chǔ)器,

FPGA固有的并行執(zhí)行功能允許由不同的時(shí)鐘驅(qū)動(dòng)獨(dú)立的硬件邏輯。在以不同速率運(yùn)行的邏輯之間傳遞數(shù)據(jù)可能很棘手,板載內(nèi)存通常用于使用先進(jìn)先出(FIFO)內(nèi)存緩沖區(qū)來平滑傳輸。

回到頂部將FPGA設(shè)計(jì)到系統(tǒng)中盡管FPGA有許多優(yōu)勢(shì),例如速度,可靠性和靈活性,但也存在與FPGA相關(guān)的折衷。FPGA沒有微處理器體系結(jié)構(gòu)和OS具有的驅(qū)動(dòng)程序生態(tài)系統(tǒng)和代碼/ IP基礎(chǔ)。此外,與操作系統(tǒng)結(jié)合的微處理器為文件結(jié)構(gòu)以及與用于許多通常是必不可少的任務(wù)(例如將數(shù)據(jù)記錄到磁盤)的外圍設(shè)備進(jìn)行通信提供了基礎(chǔ)。

結(jié)果,在過去的十年中,出現(xiàn)了一種混合架構(gòu),有時(shí)也稱為異構(gòu)架構(gòu),其中微處理器與FPGA配對(duì),然后將FPGA連接到I / O。現(xiàn)代FPGA通常將邏輯門與處理器結(jié)合到一個(gè)稱為片上系統(tǒng)(SoC)的芯片中,以提高計(jì)算性能。這種方法利用了這兩個(gè)目標(biāo)所提供的好處。

圖8. NI提供了整個(gè)系列的FPGA支持的設(shè)備,包括封裝的和板級(jí)的,您可以基于結(jié)合微處理器和FPGA的理想混合架構(gòu),使用LabVIEW進(jìn)行編程。

美國(guó)國(guó)家儀器公司(National Instruments)在其支持FPGA的設(shè)備中實(shí)現(xiàn)了這種功能強(qiáng)大的微處理器加FPGA體系結(jié)構(gòu)。這些設(shè)備跨越多種不同的外形尺寸,從堅(jiān)固到高性能的系統(tǒng),都基于相同的體系結(jié)構(gòu)。

回到頂部FPGA設(shè)計(jì)工具既然您知道了FPGA芯片的組成部分,您可能會(huì)問:“如何配置所有這數(shù)百萬個(gè)組件來構(gòu)建需要執(zhí)行的邏輯?”

答案是,您可以使用開發(fā)工具在軟件中定義數(shù)字計(jì)算任務(wù),然后將其編譯為包含有關(guān)如何將組件連接在一起的信息的配置文件或位流。過去,F(xiàn)PGA技術(shù)面臨的挑戰(zhàn)是,只有對(duì)數(shù)字硬件設(shè)計(jì)有深刻理解的工程師才能使用低級(jí)FPGA設(shè)計(jì)工具。但是,諸如LabVIEW之類的高級(jí)綜合(HLS)設(shè)計(jì)工具的興起改變了FPGA編程的規(guī)則,并提供了將圖形框圖轉(zhuǎn)換為數(shù)字硬件電路的新技術(shù)。

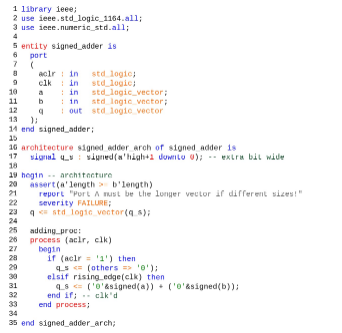

傳統(tǒng)FPGA設(shè)計(jì)工具

在FPGA開發(fā)的前20年中,諸如VHDL和Verilog之類的硬件描述語言(HDL)演變?yōu)橛糜谠O(shè)計(jì)FPGA芯片上運(yùn)行的算法的主要語言。這些低級(jí)語言集成了其他文本語言提供的一些優(yōu)勢(shì),并意識(shí)到在FPGA上您正在構(gòu)建電路。產(chǎn)生的混合語法要求將信號(hào)從外部I / O端口映射或連接到內(nèi)部信號(hào),這些內(nèi)部信號(hào)最終連接到包含算法的功能。這些功能按順序執(zhí)行,并可以引用FPGA內(nèi)的其他功能。但是,很難在連續(xù)的逐行流程中可視化FPGA上任務(wù)執(zhí)行的真正并行性。HDL反映了其他文字語言的某些屬性,

為了驗(yàn)證由FPGA程序員創(chuàng)建的邏輯,通常的做法是在HDL中編寫測(cè)試平臺(tái),以通過斷言輸入和驗(yàn)證輸出來環(huán)繞并執(zhí)行FPGA設(shè)計(jì)。測(cè)試平臺(tái)和FPGA代碼在仿真環(huán)境中運(yùn)行,該仿真環(huán)境對(duì)FPGA芯片的硬件時(shí)序行為進(jìn)行建模,并將所有輸入和輸出信號(hào)顯示給設(shè)計(jì)人員以進(jìn)行測(cè)試驗(yàn)證。與創(chuàng)建原始FPGA HDL設(shè)計(jì)本身相比,創(chuàng)建HDL測(cè)試平臺(tái)和執(zhí)行仿真的過程通常需要更多時(shí)間。

使用HDL創(chuàng)建FPGA設(shè)計(jì)并對(duì)其進(jìn)行驗(yàn)證后,需要將其饋入采用基于文本的邏輯的編譯工具,并通過幾個(gè)復(fù)雜的步驟將HDL合成為一個(gè)包含以下信息的配置文件或位流:組件應(yīng)如何連接在一起。作為此多步驟手動(dòng)過程的一部分,通常需要您指定信號(hào)名稱到所使用的FPGA芯片上的引腳的映射。

圖9. VHDL中的簡(jiǎn)單計(jì)數(shù)器FPGA設(shè)計(jì)

最終,該設(shè)計(jì)流程中的挑戰(zhàn)在于,傳統(tǒng)HDL編程所需的專業(yè)知識(shí)并不廣泛,因此,絕大多數(shù)工程師和科學(xué)家都無法使用FPGA技術(shù)。

高級(jí)綜合設(shè)計(jì) 工具

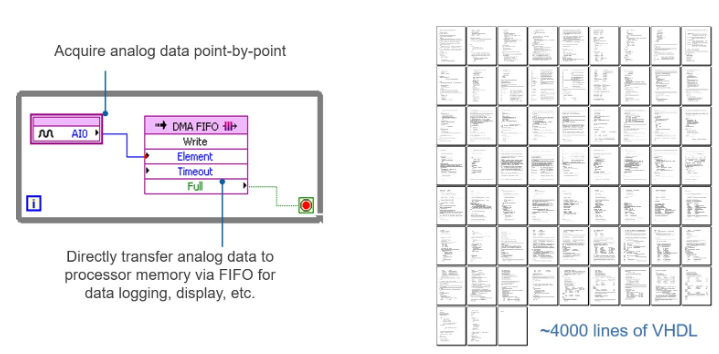

圖形HLS設(shè)計(jì)工具(例如LabVIEW)的出現(xiàn)消除了傳統(tǒng)HDL設(shè)計(jì)過程中的一些主要障礙。LabVIEW編程環(huán)境非常適合FPGA編程,因?yàn)樗宄乇硎玖瞬⑿行院蛿?shù)據(jù)流,因此在傳統(tǒng)FPGA設(shè)計(jì)過程中經(jīng)驗(yàn)豐富和經(jīng)驗(yàn)不足的用戶都可以利用FPGA技術(shù)。此外,為了不丟失以前的知識(shí)產(chǎn)權(quán)(IP),您可以使用LabVIEW將現(xiàn)有的VHDL集成到LabVIEW FPGA設(shè)計(jì)中。由于LabVIEW FPGA與硬件高度集成,因此無需像許多HLS代碼生成器一樣,可以用VHDL重寫代碼來滿足時(shí)序或資源限制。

圖10.左側(cè)是LabVIEW,它是FPGA的高級(jí)設(shè)計(jì)工具。它為創(chuàng)建和擴(kuò)展VHDL設(shè)計(jì)時(shí)經(jīng)常發(fā)現(xiàn)的低級(jí)復(fù)雜性提供了抽象。

然后,為了仿真和驗(yàn)證FPGA邏輯的行為,LabVIEW直接在開發(fā)環(huán)境中提供了功能。在不了解底層HDL語言的情況下,您可以創(chuàng)建測(cè)試平臺(tái)以行使設(shè)計(jì)邏輯。此外,LabVIEW環(huán)境的靈活性還可以通過導(dǎo)出到周期精確的仿真器(例如Xilinx ISim)來幫助更高級(jí)的用戶對(duì)設(shè)計(jì)的時(shí)序和邏輯進(jìn)行建模。

LabVIEW FPGA編譯工具可自動(dòng)執(zhí)行編譯過程,因此您只需單擊一個(gè)按鈕即可啟動(dòng)該過程,并在完成編譯階段時(shí)接收?qǐng)?bào)告和錯(cuò)誤(如果有)。如果由于您的FPGA設(shè)計(jì)而確實(shí)發(fā)生了時(shí)序錯(cuò)誤,LabVIEW將以圖形方式突出顯示這些關(guān)鍵路徑,以加快調(diào)試過程。

結(jié)局

隨著諸如LabVIEW之類的高級(jí)工具使FPGA更加易于使用,F(xiàn)PGA技術(shù)的采用持續(xù)增長(zhǎng)。但是,重要的是要查看FPGA內(nèi)部并了解將框圖編譯為可在硅片中執(zhí)行時(shí)實(shí)際上發(fā)生了多少事情。根據(jù)觸發(fā)器,LUT,乘法器和Block RAM比較和選擇硬件目標(biāo)是為您的應(yīng)用選擇合適的FPGA芯片的最佳方法。在開發(fā)期間,尤其是在優(yōu)化大小和速度時(shí),了解資源的使用非常有幫助。本文無意成為所有FPGA基本構(gòu)建模塊的全面清單。您可以從下面的資源中了解有關(guān)FPGA和數(shù)字硬件設(shè)計(jì)的更多信息。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論