高速成像應用中,CCD的輸出通道數較多,且每個通道的速度也很高。多通道輸出需要多個放大器對信號進行放大。當放大器數量較多時,電路板布局時很難使放大器靠近CCD放置。然而,較長的電路板走線產生

2013-10-10 12:02:00 1793

1793

為了實現激光-水聲淺海地形遙感探測中水聲信號的實時解調與處理,本文提出了一種基于FPGA的激光多普勒測振計信號采集與處理系統的設計方案。以Cyclone Ⅱ系列FPGA為核心控制模塊,結合

2013-10-29 10:10:02 2157

2157

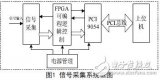

為解決現場測試系統中微弱信號的高速實時采集處理和及時可靠存儲的問題,本文提出了基于PCI總線的數據采集電路的設計方案,該方案將模擬信號通過高速A/D芯片有效采樣,在FPGA的控制下將數據上傳到PC

2014-01-24 09:45:29 1605

1605

接收器的 3.2Gsps 1.5GHz 多通道高速模擬前端通道間的時鐘偏斜小于 5ps符合 JESD204B 標準的多通道時鐘解決方案可擴展的平臺,適用于具有引腳兼容性的 ADC12DJxx00 系列支持 TI 的高速轉換器和采集卡 (TSW14J56/TSW14J57)

2018-10-11 11:59:37

的多通道流量,那么單純基于DSP的硬件系統就可能需要更大的面積,成本或功耗。一個FPGA僅在一個器件上就能高提供多達550個并行乘法和累加運算,從而以較少的器件和較低的功耗提供同樣的性能。但對于定期系數更新,決策控制任務或者高速串行處理任務,FPGA的優化程度遠不如DSP。

2019-08-30 06:31:29

FPGA實現高速FFT處理器的設計介紹了采用Xilinx公司的Virtex - II系列FPGA設計高速FFT處理器的實現方法及技巧。充分利用Virtex - II芯片的硬件資源,減少復雜邏輯,采用

2012-08-12 11:49:01

和ASIC中實現的硬核IP等。圖1即使如此,通用嵌入式系統也很難滿足現代設計需求。多芯片解決方案實現起來相對容易一些,但是成本高,缺乏設計人員所要求的靈活性以及性能/功耗指標。采用了軟核處理器的單芯片

2021-07-14 08:00:00

的設計方案。利用JESD204B協議的確定性延遲特性,只要保證通道間下行數據的相互延遲不超過一個多幀時鐘周期,通過關鍵控制信號的設計和處理,通道間可以實現數據的同步,有效控制板內多片ADC之間進行

2019-12-03 17:32:13

超過一個多幀時鐘周期,通過關鍵控制信號的設計和處理,通道間可以實現數據的同步,有效控制板內多片ADC之間進行同步采樣,從而解決數字相控陣雷達下行數據因采集帶來的相位一致性問題。2、雷達多通道同步采集實現

2019-12-04 10:11:26

1、FPGA內部AD多通道采樣實驗設計與實現編寫程序,使用Anlogic 自帶的ADC進行四通道數據輪詢采集,同時介紹TD軟件IP核的用法。本實驗設計使用FPGA自帶的12位串行AD芯片工作,將直流

2022-07-15 18:18:37

至關重要。 TigerSHARC系列DSP芯片與外部進行數據通信主要有兩種方式:總線方式和鏈路口方式。鏈路口方式更適合于FPGA與DSP之間的實時通信。隨著實時信號處理運算量的日益增加,多DSP并行

2019-06-21 05:00:04

湊,節約空間。FPGA由于其高度的并行和 靈活的配置特性,以高速、實時、低成本、高靈活性的優點應用于數字信號處理領域。本文敘述了采用FPGA實現光纖微擾動傳感器的數據處理的具體方案,提供 了一種高速實時數據處理

2020-09-04 09:56:23

FPGA的并行多通道激勵信號產生模塊FPGA的并行多通道激勵信號產生模塊.docx

2012-08-11 10:35:50

描述TIDA-01016 是一款適合高動態范圍高速 ADC 的時鐘解決方案。射頻輸入信號由高速 ADC 直接采用射頻取樣法捕獲。ADC32RF80 是一款雙通道 14 位 3GSPS 射頻取樣

2018-09-30 09:26:09

有沒有多通道(數量在100以上,也可能上千通道)ADC采樣的一個方案?目前能想到的方案(1)模擬信號先經過數字開關,然后選通,再到ADC采樣口。(2)有沒有多通道ADC的cpu(類似于fpga)的CPU?希望大家能給點建議。

2019-03-18 09:17:54

[tr][td]多通道adc dma處理數據上有干擾我改變一個通道的采集電壓值,對其他通道的采集的數值產生影響,這個該怎么解決?

2017-12-20 15:58:28

納米軟件NSAT-4000多通道信號高速采集記錄存儲回放系統主要用于對多通道信號進行長時間高速連續實時采集記錄和回放產生,適用于雷達、無線通信、軟件無線電、電子對抗、電子偵察、衛星導航、復雜電磁環境

2021-08-11 17:32:07

波段采樣解決方案。集成式射頻采樣高速轉換器最新版本的高速轉換器在單片硅上集成了ADC,DAC和數字信號處理模塊。圖1所示的MxFE ?四通道,16位,12 GSPS,RF DAC和四通道,12位,4

2020-08-21 14:24:29

、高度模塊化整合,使得傳感器輸入量劇增。如何在超小尺寸的PLC模塊內構建通用的模擬 信號和溫度測量成為工業4.0的關鍵。為滿足工業客戶的這一需求,我們以Maxim的高精度ADC為核 心,分別設計了多通道

2019-03-25 21:47:18

、高度模塊化整合,使得傳感器輸入量劇增。如何在超小尺寸的PLC模塊內構建通用的模擬 信號和溫度測量成為工業4.0的關鍵。為滿足工業客戶的這一需求,我們以Maxim的高精度ADC為核 心,分別設計了多通道

2022-03-16 11:23:20

大家好,我想設計一個醫用高速DAC激勵信號源,直接通過電極作用于人體,然后用4片AD4003進行采集。整體電路需要滿足IEC 60601醫用儀器隔離標準。但是對于高速DAC的隔離和多片ADC的隔離

2018-08-13 09:14:52

減輕計算密集型 2D FFT 運算負載的 FFTC 硬件加速器,可實現低延遲和高精度附加了 JESD 的寬帶采樣信號處理解決方案,包含數字信號處理器 (DSP)、ADC 和 DAC 板、演示軟件、配置

2018-09-20 09:07:06

子系統的性能要求和設計方案的基礎上,提出了高速緩存和海量緩存方案,并將該方案成功地應用于DSP多通道超聲信號采集與處理系統中。 對高速多通道采樣數據存儲的性能要求:一是高速性,現在高速數據采集

2020-12-04 15:59:14

`多通道超聲波高速信號采集開發套件(以下簡稱采集板)是我司新推出的多通道超聲波信號采集和二次開發平臺,集成了超聲波高壓發射、回波信號接收、放大、AD 采集及處理功能、信號存儲,并且提供了二次開發功能

2020-09-07 10:50:31

描述ADC12D1600RFRB 參考設計提供了展示高速數字轉換器應用(其中整合了時鐘、電源管理和信號處理)的平臺。此參考設計利用 1.6 GSPS ADC12D1600RF 器件、板載 FPGA

2018-12-17 16:16:17

隨著計算機和微電子技術的發展,雷達、通信等眾多應用領域對于數據采集系統提出了更高的要求,數據采集正在向著多通道、高采樣率、高分辨率、大容量存儲和高速傳輸速率方向快速發展。 通用的數據采集卡多為八通道

2021-10-08 14:23:04

基于SDRAM控制器實現FPGA模塊化和通用性的解決方案設計

2020-12-22 07:58:55

湊,節約空間。FPGA由于其高度的并行和 靈活的配置特性,以高速、實時、低成本、高靈活性的優點應用于數字信號處理領域。本文敘述了采用FPGA實現光纖微擾動傳感器的數據處理的具體方案,提供 了一種高速實時數據處理

2020-08-31 18:54:17

【背景】針對當前生理電信號采集設備多為異步數據采集設備,高速模擬復用開關無法實現理想開、關狀態,各信號通道串擾較大,開關的開啟、關閉無法實現時域同步;依據數字信號處理理論:時域信號時移導致頻域信號

2012-06-14 00:11:59

,BANANA PI作為嵌入式上位機可以更好的人機交互,數據處理速度可以更快,經濟便宜,現申請一塊作為開發使用,后期可大量采購。項目描述:開發項目:嵌入式多通道數據采集器初步方案:傳感器接入后進行硬件信號調理

2016-06-20 15:54:53

與PC機實現高速通信,例如將FPGA使用高速ADC采集到的數據發送到PC機上進行進一步分析處理。為了實現FPGA與PC機實現高速通信,我們特開發了USB2.0通信模塊,模塊使用經典的USB2.0芯片

2015-09-14 21:41:41

/A芯片直接與DSP相連,由DSP來完成數字信號處理算法。目前主要的高端數字信號處理器有TI公司的DSP和AD公司的ADSP。該方案的優點在于:設計簡潔,所需芯片數量少。缺點是:在數據轉換通道多

2019-07-05 06:41:27

特點,采用數據流控制的方法實現了信息的并行處理,可以更加有效的實現多通道振動信號采集;同時為了提高數據的可靠性采用時間標定的方法進行數據的存儲和校驗。本文第一節介紹了該系統的整體設計方案,第二節

2019-07-01 06:11:15

本文提出了一個通用微處理器(ARM)與DSP的接口設計方案,以實現兩者的實時通信。

2021-06-08 06:36:41

分享一種通用家電遙控設備的設計方案

2021-06-04 06:54:48

提出一種基于FPGA和USB的通用CCD采集系統設計方案。該系統在不改變硬件的情況下可以采集多種CCD,并上傳至PC機,使用軟件處理采集到的數據。

2021-04-22 06:23:40

本文研究了中頻軟件無線電的實現方案,并設計了基于FPGA的通用硬件平臺。在此平臺上,通過PC機下載軟件,實時實現了軟件無線電中頻至基帶的波形處理和多種不同的調制解調方式。

2021-04-29 06:27:47

多通道綜合測試系統實物測試結果圖3 結語本設計以FPGA為核心控制單元,實現了一種多通道綜合測試系統,具備開關切換、通道選擇、數據采集、TCP/IP協議數據傳輸等功能,充分利用和體現了FPGA的優勢,提供了一種功能完善、性能優良的綜合測試系統設計方案。

2018-08-07 10:08:19

降低輸出數據率,也可以方便地與多種類型的高速FPGA直接相連,實現高速率的數據存儲和處理。為補償由于器件參數離散和傳輸路徑差異所造成的采樣時鐘時延,該ADC具有采樣延時校準功能,可通過片內的數字采樣延時

2019-04-30 07:00:11

度、高可靠性等特點,因此FPGA 應用于高速多通道雷達信號模擬器可大大提高系統設計的靈活性和系統的擴展性。本文設計的高速多通道信號模擬器系統可廣泛應用于通信、雷達信號的模擬產生, 為雷達設備, 特別是接收機

2019-07-10 08:16:48

場景進行監控,不僅視頻的視野范圍有限,而且不能對同一個物體的不同方位進行監控。這里提出了一種多通道視頻監控系統,通過對不同視頻通道穩定、可靠地切換控制,實現監控不同場景。該系統不僅彌補了傳統監控視頻范圍

2012-12-12 17:00:21

本文提出了一種基于TMS320C6701信號處理器的高性能信號處理模塊的設計方案,設計了具有一定通用性的并行信號處理模塊,該模塊具有高速互連接口,可以根據應用系統的需求構成不同的并行系統,完成各種信號處理任務。

2021-04-02 07:30:14

軟件無線電是在無線通信中建立一個通用、標準的硬件平臺,把收發信號的數字化處理(A/D 和D/A 轉換)盡量靠近天線,從而可以在保持硬件平臺不變的情況下,通過僅修改數字信號的處理軟件來非常方便地實現

2017-08-02 19:42:27

、較高的靈敏度、大的動態范圍,能夠檢測和處理同時到達的信號、準確的參數測量能力和一定的信號識別能力。直接信道化接收機的運算量大且輸出速率與采樣速率相同,實現困難,后續處理的壓力很大,高速ADC與慢速信號

2019-08-22 08:01:34

如何去實現stm32 ADC多通道連續采集的功能呢?

2021-11-16 08:42:29

本文介紹了采用Xilinx公司的Spartan-3 FPGA實現通用視頻采集系統的設計方案。

2021-06-08 06:34:30

怎么實現多通道ADC通過DMA數據采集?

2021-11-18 06:46:07

本文以并行多通道信號產生模型為依據,設計并實現了以FPGA為核心器件的并行多通道信號產生模塊,主要包括FPGA系統設計和多通道波形產生模塊設計。通過模塊測試后發現,該模塊具備產生高質量并行多通道激勵信號的能力。

2021-04-29 06:17:38

本文介紹在分級Ad Hoc網絡中多協議路由器的地位及功能,在此基礎上提出一種多協議路由器設計方案。結合設計方案,介紹實現方案中所采用的Motorola公司的ColdFire嵌入式處理器MCF5272、uClinux操作系統,以及在該平臺上運行的路由協議A0DV。

2021-06-07 06:12:10

求一種多通道同步數據采集及壓縮系統的設計方案。

2021-04-28 06:13:04

討論了一種基于FPGA的64點FFT處理器的設計方案,輸入數據的實部和虛部均以16位二進制數表示,采用基2DIT-FFT算法,以Altera公司的QuartusⅡ軟件為開發平臺對處理器各個的模塊進行設計,在Stratix系列中的EP1S25型FPGA通過了綜合和仿真,運算結果正確。

2021-04-29 06:25:54

你好,我使用AD9239-210,設計中工作時鐘外部信號源輸入200MHz,所有8個通道使用同一個時鐘源。

板子上兩片AD9239,采樣后的數據通過GTX接口進入FPGA的內部邏輯。邏輯中數據處理

2023-12-13 09:17:30

Broadkey 6416板是一款高端的PCI總線數據采集卡,該卡可作軟件無線電數字中頻接收、數據采集、數據分析和信號處理等使用。該卡采用ADC+FPGA+DSP 的通用架構,都采用高速、高性能

2010-02-05 15:04:28

項目簡介任務:通過CubeMx實現ADC多通道掃描采集DMA方式(無中斷)采集內部溫度傳感器的溫度通道:采集A0、A1、A2、B0、B1端口電壓,采集內部溫度傳感器通道16、內部電壓通道17顯示方式

2021-08-11 08:14:45

針對遙感系統的工作環境特點、待處理信號的頻譜特征以及系統信噪比等要求,綜合比較多種信號采集系統方案的優缺點,本文提出了一種基于FPGA的激光多普勒測振計信號采集與處理系統的設計方案,該方案可以實現光

2019-06-24 07:16:30

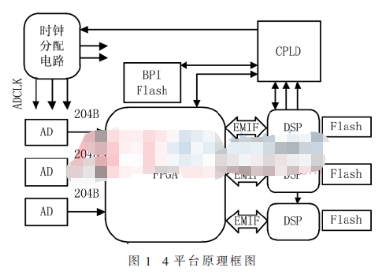

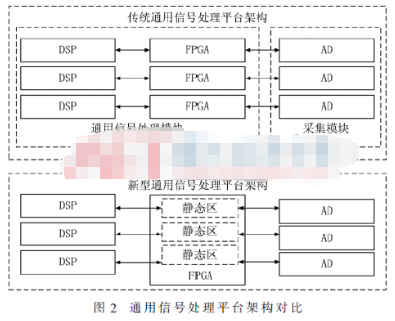

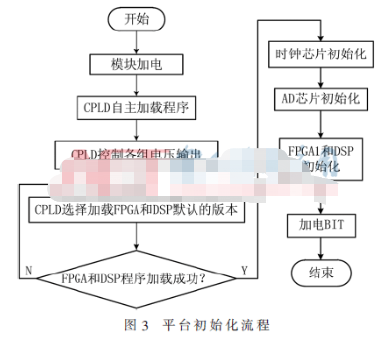

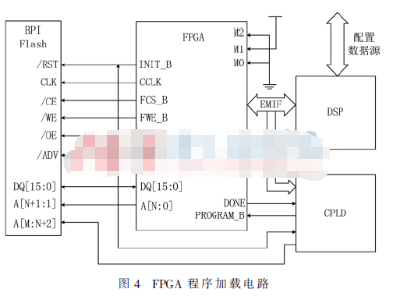

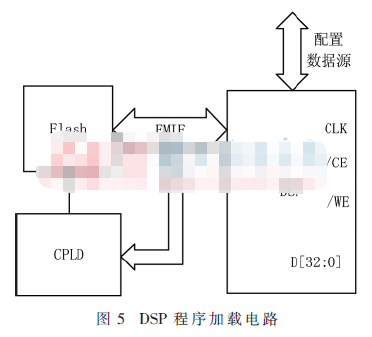

架構的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-03-02 13:52:47

架構的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-03-09 10:12:15

架構的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-03-16 11:00:00

架構的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-03-30 11:12:53

架構的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-04-07 10:40:35

架構的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-04-14 11:09:20

架構的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-04-25 11:21:12

架構的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA XC7K325T

2016-03-23 11:03:18

了一種基于TMS320C6701信號處理器的高性能信號處理模塊的設計方案,設計了具有一定通用性的并行信號處理模塊,該模塊具有高速互連接口,可以根據應用系統的需求構成不同的并行系統,完成各種信號處理任務。1

2016-05-31 17:53:59

提出了一種基于LPC2142且具有USB (通用串行總線) 接口的高速數據采集卡的設計方案,給出了基于ARM7處理器LPC2142和FPGA芯片的軟硬件設計方法,該設計方案解決了高速實時信號與

2009-03-07 10:05:07 9

9 本文詳細介紹了一種借助VHDL 硬件描述性語言實現基于FPGA 硬件平臺的通用微處理器設計的完整方案。該型CPU 具有實現簡單快捷、成本低、通用性強、擴展容易的特性。本文分兩

2009-11-30 15:41:28 20

20 為解決目前高速信號處理中的數據傳輸速度瓶頸以及傳輸距離的問題,設計并實現了一種基于FPGA 的高速數據傳輸系統,本系統借助Altera Cyclone III FPGA 的LVDS I/O 通道產生LVDS 信號,穩

2010-11-02 15:27:43 42

42 設計一種基于DSP和FPGA架構的通用圖像處理平臺,運用FPGA實現微處理器接口設計,并對圖像數據進行簡單預處理,利用DSP進行復雜圖像處理算法和邏輯控制,實現圖像數據的高速傳輸

2010-12-25 17:06:54 60

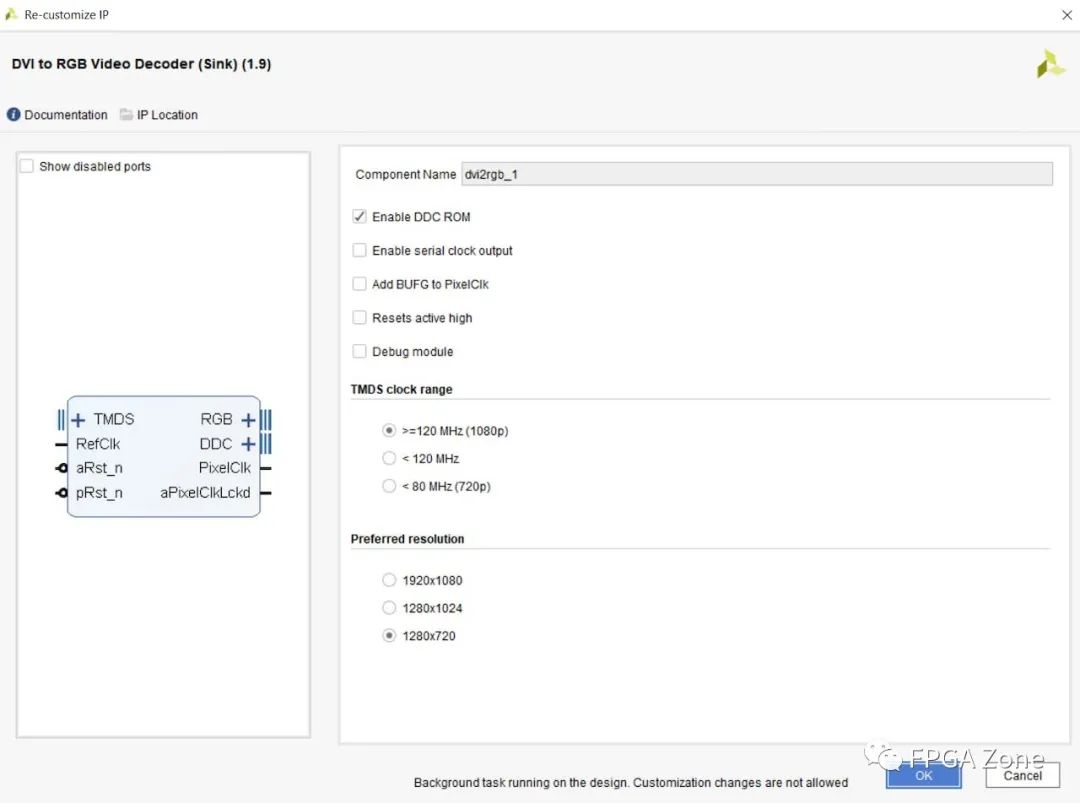

60 基于CPCI總線的通用FPGA信號處理板的設計

?隨著雷達信號處理技術的不斷發展以及現代國防對雷達技術的需求,系統對雷達信號處理的要求也越來越高,需要實時處

2009-11-28 15:07:38 922

922

基于ADC和FPGA脈沖信號測量的設計方案

0引言

測頻和測脈寬現在有多種方法。通常基于MCU的信號參數測量,由于其MCU工作頻率很低,所以能夠達到的精度也

2009-12-21 09:13:23 1501

1501

基于DSP和FPGA的通用圖像處理平臺設計

摘要:設計一種基于DSP和FPGA架構的通用圖像處理平臺,運用FPGA實現微處理器接口設計,并對圖像數據進行簡單預處理,利用DSP

2010-02-01 11:10:21 1379

1379

基于FPGA的高速定點FFT算法的設計方案

引 言 快速傅里葉變換(FFT)作為計算和分析工具,在眾多學科領域(如信號處理、圖像處理、生物信息學、計算物理

2010-02-09 10:47:50 992

992

本文在分析現有的解決方案優缺點的基礎上提出了一種在FPGA上實現ORB的改進設計方案,不但為彼此分離的、工作于多處理器平臺上的各個GPP,DSP和FPGA開發小組提供了通用的CORBA通信機制

2011-12-22 10:18:54 3341

3341

文中提出了一種基于FPGA的八通道超聲探傷系統設計方案。該系統利用低功耗可變增益運放和八通道ADC構成高集成度的前端放大和數據采集模塊;采用FPGA和ARM作為數字信號處理的核心和

2013-06-09 16:30:29 54

54 基于FPGA的高速多通道AD采樣系統的設計與實現_徐加彥

2017-01-18 20:23:58 12

12 基于FPGA的通用傳感器信號處理系統設計_李輝

2017-03-19 19:07:17 3

3 摘要:高速中頻采樣信號處理平臺在實際應用中有很大的前景,提出采用FPGA+DSP的處理結構,結合高性能A/D和D/A處理芯片,設計了一個通用處理平臺,并對其主要性能進行了測試。實驗與實際應用表明

2017-10-30 11:46:08 2

2 高速中頻采樣信號處理平臺在實際應用中有很大的前景,提出采用FPGA+DSP的處理結構,結合高性能A/D和D/A處理芯片,設計了一個通用處理平臺,并對其主要性能進行了測試。

2018-10-18 16:36:48 4637

4637

本文提出了一種實現信號采集方案,介紹了由ARM 處理器S3C2410 和EP2C8 FPGA 組成的高速信號采集系統的系統設計,并著重介紹前端硬件的設計,并就ARM 處理器和FPGA 的互聯設計進行探討。利用FPGA 硬件控制A/D 轉換,達到了較好的效果,實現了信號的采集與存儲。

2018-11-02 15:46:01 10

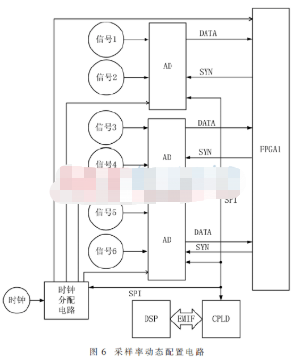

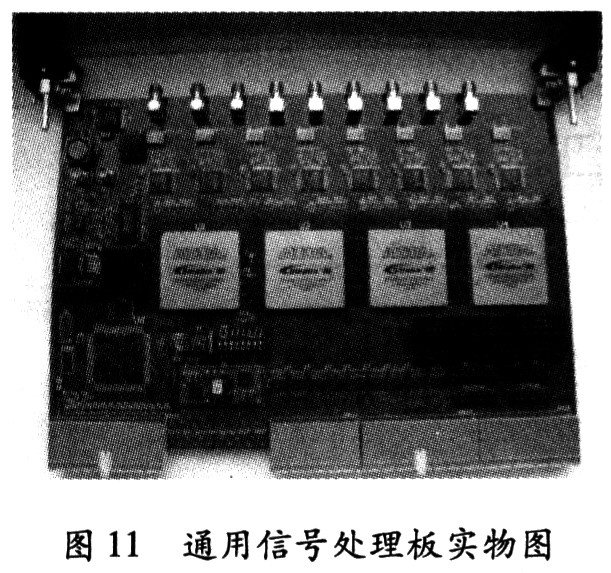

10 本文通過GA3816、FPGA和DSP構建了一個高速、通用、可擴展的多功能信號處理平臺,該信號處理平臺經過動態配置GA3816處理芯片可實現一些信號處理領域常用的運算,也可以通過對DSP、FPGA芯片的編程來實現一些其它算法,所以該平臺能夠廣泛的應用于信號處理等領域。

2021-05-22 15:29:05 1594

1594

基于FPGA的嵌入式信號處理系統設計方案

2021-06-02 11:04:33 0

0 基于FPGA的嵌入式信號處理系統設計方案

2021-06-02 11:04:33 0

0 本文詳細描述了FPGA實現圖像去霧的實現設計方案,采用暗通道先驗算法實現,并利用verilog并行執行的特點對算法進行了加速;

2023-06-05 17:01:45 862

862

一種基于FPGA 實現的800G信號處理平臺

2023-07-31 10:23:11 375

375

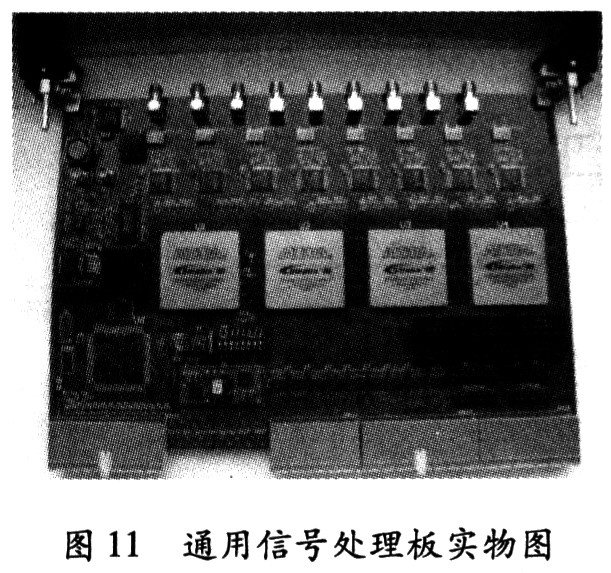

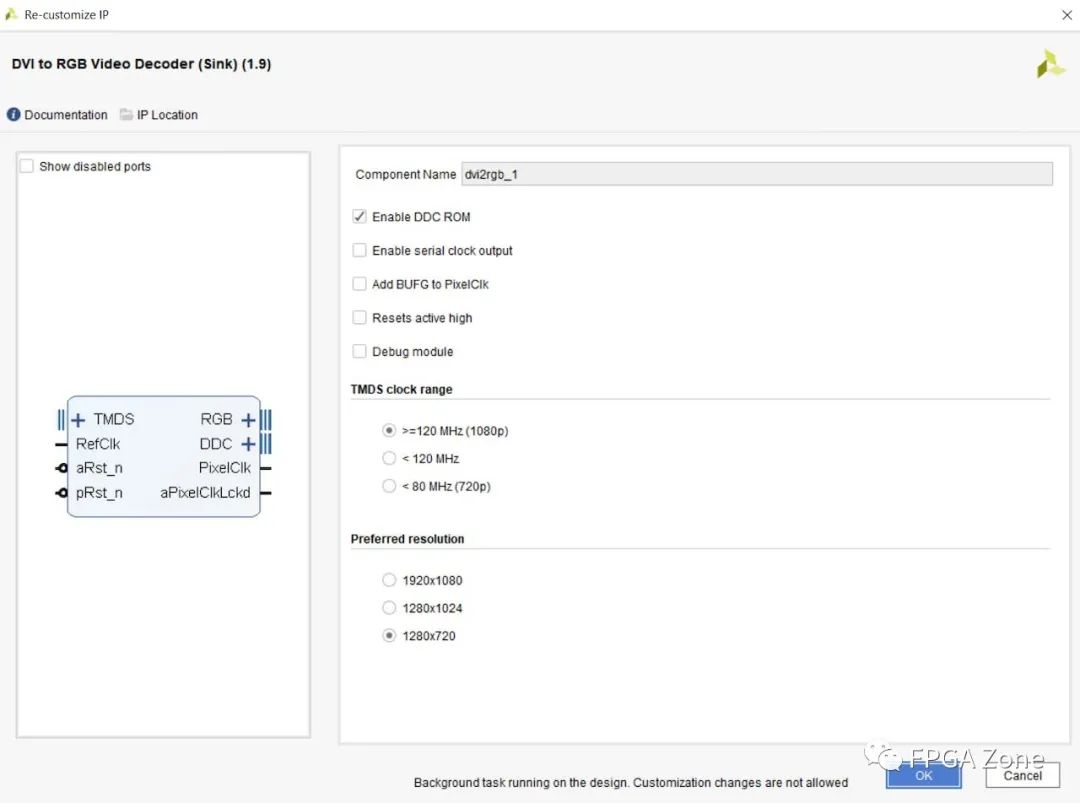

本文介紹如何搭建一個通用的圖像處理平臺,采用HDMI接口進行輸入、輸出,可用于測試基于HLS的FPGA圖像處理項目。

2023-09-04 18:20:19 1050

1050

電子發燒友網站提供《高速ADC電源設計方案.pdf》資料免費下載

2023-11-10 16:20:26 0

0

電子發燒友App

電子發燒友App

評論