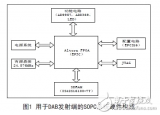

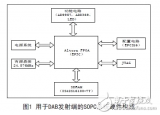

基于FPGA 芯片EP3C16Q240C8N 的片上可編程系統(tǒng),該系統(tǒng)可用于實(shí)現(xiàn)IFFT運(yùn)算和接口模塊,利用可嵌入到此FPGA 芯片的NiosII 軟核處理器來(lái)實(shí)現(xiàn)數(shù)據(jù)傳輸和控制。

2015-02-03 15:08:23 1185

1185

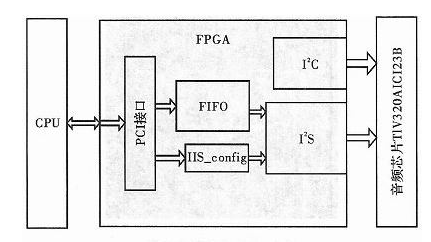

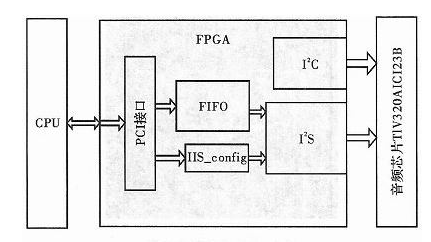

電路主要通過(guò)PCI接口芯片與音頻接口芯片等專用集成電路芯片在板級(jí)電路進(jìn)行組合從而實(shí)現(xiàn)基于PCI的音頻播放設(shè)備。此種電路雖然成熟可靠,但電路設(shè)計(jì)復(fù)雜、靈活性小而且需要占用大量的電路板空間。

2016-01-18 09:58:33 4033

4033

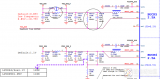

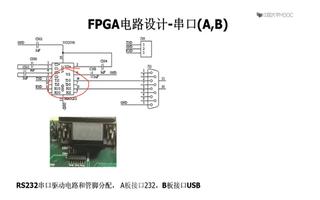

硬件電路設(shè)計(jì)總結(jié)主要包括以下幾個(gè)主要的模塊:電源模塊,存儲(chǔ)模塊,顯示模塊,和對(duì)外接口模塊。

2024-02-21 14:52:28 445

445

串行接口常用于芯片至芯片和電路板至電路板之間的數(shù)據(jù)傳輸。隨著系統(tǒng)帶寬不斷增加至多吉比特范圍,并行接口已經(jīng)被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨(dú)立

2019-10-23 07:16:35

引言 現(xiàn)場(chǎng)可編程邏輯門陣列FPGA器件的出現(xiàn)是超大規(guī)模集成電路技術(shù)和計(jì)算機(jī)輔助設(shè)計(jì)技術(shù)發(fā)展的結(jié)果。FPGA器件集成度高、體積小,具有通過(guò)用戶編程實(shí)現(xiàn)專門應(yīng)用功能。它允許電路設(shè)計(jì)者利用基于計(jì)算機(jī)的開(kāi)發(fā)

2018-12-18 09:51:38

系統(tǒng)工程師第一階段的課程主要幫助學(xué)員了解FPGA系統(tǒng)設(shè)計(jì)的基礎(chǔ)知識(shí),掌握FPGA最小系統(tǒng)硬件電路設(shè)計(jì)方法,學(xué)會(huì)操作QuartusII軟件來(lái)完成FPGA的設(shè)計(jì)和開(kāi)發(fā)。1.可編程邏輯設(shè)計(jì)技術(shù)簡(jiǎn)介2.下一代

2014-11-30 17:38:06

FPGA應(yīng)用可分為三個(gè)層面:電路設(shè)計(jì)、產(chǎn)品設(shè)計(jì)、系統(tǒng)設(shè)計(jì)1.系統(tǒng)級(jí)應(yīng)用 系統(tǒng)級(jí)的應(yīng)用是FPGA與傳統(tǒng)的計(jì)算機(jī)技術(shù)結(jié)合,實(shí)現(xiàn)一種FPGA版的計(jì)算機(jī)系統(tǒng)如用XilinxV-4, V-5系列的FPGA

2012-03-16 09:43:55

FPGA控制的PS2接口電路設(shè)計(jì)

2021-03-07 11:47:27

下載配置與調(diào)試接口電路設(shè)計(jì)FPGA是SRAM型結(jié)構(gòu),本身并不能固化程序。因此FPGA需要一片F(xiàn)lash結(jié)構(gòu)的配置芯片來(lái)存儲(chǔ)邏輯配置信息,用于進(jìn)行上電配置。以Altera公司的FPGA為例,配置芯片

2019-06-11 05:00:07

FPGA板級(jí)電路設(shè)計(jì)五要素本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 和純粹基于PC機(jī)的各種軟件編程

2019-01-25 06:27:02

): 5.1FPGA管腳設(shè)計(jì) 5.2下載配置與調(diào)試接口電路設(shè)計(jì) 5.3高速SDRAM存儲(chǔ)器接口電路設(shè)計(jì) 5.4異步SRAM(ASRAM)存儲(chǔ)器接口電路設(shè)計(jì) 5.5FLASH存儲(chǔ)器接口電路設(shè)計(jì) 5.6開(kāi)關(guān)、按鍵

2014-04-23 15:28:29

接口電路設(shè)計(jì)指南,設(shè)計(jì)手冊(cè)更為強(qiáng)壯的接口IC,邏輯端和RS232端所有IO引腳都具有正負(fù)15V ESD保護(hù)。下載地址:接口電路設(shè)計(jì)指南

2009-10-24 12:04:48

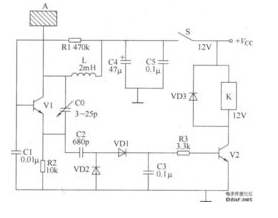

的,輸出功率基本接近其輸入功率,因此,對(duì)于一個(gè)升壓變壓器來(lái)說(shuō),它可以有較高的輸出電壓,但是卻只能給出較低的電流。此外,變壓器的高頻和低頻特性并不讓人樂(lè)觀,但是它的最大特點(diǎn)就是可以實(shí)現(xiàn)阻抗變換,當(dāng)匹配得當(dāng)時(shí),負(fù)載可以獲得足夠大的功率,因此,變壓器耦合接口在功率放大電路設(shè)計(jì)中很“吃香”。

2019-07-04 03:26:28

今天與大家一起學(xué)習(xí)--電路設(shè)計(jì)技術(shù)與技巧,很好的資料。從簡(jiǎn)單的電路設(shè)計(jì)開(kāi)始,分析和設(shè)計(jì)常見(jiàn)的電路,方便大家學(xué)習(xí)和設(shè)計(jì)電路。歡迎學(xué)習(xí)。

2016-03-16 21:37:10

電路設(shè)計(jì)[FPGA]設(shè)計(jì)經(jīng)驗(yàn)

2012-05-23 19:49:45

電路設(shè)計(jì)[FPGA]設(shè)計(jì)經(jīng)驗(yàn)

2012-08-20 15:37:36

電路設(shè)計(jì)[FPGA]設(shè)計(jì)經(jīng)驗(yàn)

2019-01-03 14:19:28

電路設(shè)計(jì)中必須掌握的7個(gè)常用接口知識(shí)我們知道,在電路系統(tǒng)的各個(gè)子模塊進(jìn)行數(shù)據(jù)交換時(shí)可能會(huì)存在一些問(wèn)題導(dǎo)致信號(hào)無(wú)法正常、高質(zhì)量地“流通”,例如有時(shí)電路子模塊各自的工作時(shí)序有偏差(如CPU與外設(shè))或者

2017-04-21 11:42:28

功率,因此,對(duì)于一個(gè)升壓變壓器來(lái)說(shuō),它可以有較高的輸出電壓,但是卻只能給出較低的電流。 此外,變壓器的高頻和低頻特性并不讓人樂(lè)觀,但是它的最大特點(diǎn)就是可以實(shí)現(xiàn)阻抗變換,當(dāng)匹配得當(dāng)時(shí),負(fù)載可以獲得足夠大的功率,因此,變壓器耦合接口在功率放大電路設(shè)計(jì)中很“吃香”。

2017-08-29 20:35:19

典型的CAN總線接口電路原理圖接口電路設(shè)計(jì)中的關(guān)鍵問(wèn)題

2021-02-25 07:01:31

過(guò)程。 實(shí)際的設(shè)計(jì)中,CDR部分是由純邏輯電路完成的,為設(shè)計(jì)的核心的部分,下面將介紹數(shù)字CDR在HR03的實(shí)現(xiàn)方案。 2 數(shù)字CDR: CDR模塊作用是從數(shù)據(jù)中恢復(fù)嵌入的時(shí)鐘,然后接收器按照恢復(fù)的時(shí)鐘進(jìn)行

2019-05-29 17:52:03

SPCE061A單片機(jī)與指紋識(shí)別模塊的接口電路設(shè)計(jì)

2019-10-30 09:11:00

SPI接口主模式電路設(shè)計(jì)。(1)輸出時(shí)鐘頻率可調(diào): 主時(shí)鐘2/4/8/32/64分頻;(2 )具有主動(dòng)首發(fā)功能;(3 )發(fā)送、接收數(shù)據(jù)位數(shù)可通過(guò)輸入數(shù)據(jù)設(shè)定;(4 )可實(shí)現(xiàn)數(shù)據(jù)次序選擇,數(shù)據(jù)最高

2017-11-25 23:23:12

`本節(jié)知識(shí)介紹:FPGA接口實(shí)現(xiàn)文本液晶顯示模塊文本液晶顯示模塊是基于廉價(jià)和易于使用微控制器或FPGA接口實(shí)現(xiàn)的。下面是一個(gè)1行×16字符模塊:要控制液晶顯示模塊,你需要11個(gè)IO引腳來(lái)驅(qū)動(dòng)一個(gè)8

2012-03-14 11:11:15

系統(tǒng)工程師第一階段的課程主要幫助學(xué)員了解FPGA系統(tǒng)設(shè)計(jì)的基礎(chǔ)知識(shí),掌握FPGA最小系統(tǒng)硬件電路設(shè)計(jì)方法,學(xué)會(huì)操作QuartusII軟件來(lái)完成FPGA的設(shè)計(jì)和開(kāi)發(fā)。1.可編程邏輯設(shè)計(jì)技術(shù)簡(jiǎn)介2.下一代

2018-09-19 11:34:03

關(guān)于以太網(wǎng)到多路E1適配電路設(shè)計(jì)及FPGA實(shí)現(xiàn)你想知道的都在這

2021-05-06 06:17:04

分 塊的邊界框,選擇置信度最大的邊界框輸出。

2.2 FPGA加速電路設(shè)計(jì)方案本項(xiàng)目設(shè)計(jì)的硬件電路主要有兩個(gè)模塊模塊:數(shù)據(jù)讀取與傳輸模塊。首先需要讀取圖片和模型參數(shù)的數(shù)據(jù),并對(duì)輸入的圖片數(shù)據(jù)進(jìn)行歸一化

2023-06-20 19:45:12

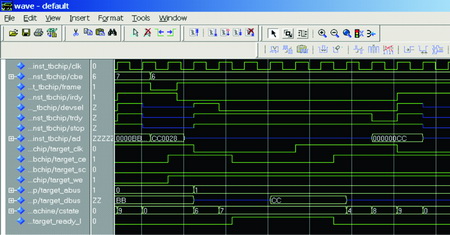

本文介紹了一種基于 FPGA 技術(shù)的IDE 硬盤接口的設(shè)計(jì)。該卡提供兩個(gè)符合ATA-6 規(guī)范的接口,采用FPGA 實(shí)現(xiàn)了兩套IDE 接口功能,設(shè)計(jì)支持PIO和Ultra DMA 傳輸模式,文章側(cè)重于介紹用FPGA 實(shí)現(xiàn)IDE 接口協(xié)議的具體方法。

2011-01-12 14:38:42

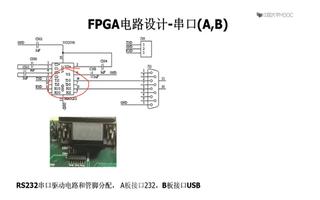

摘要:RS 232接口是現(xiàn)在最常用的一種通信接口。隨著FPGA技術(shù)的高速發(fā)展,一些常見(jiàn)的接口電路的時(shí)序電路可以通過(guò)FPGA實(shí)現(xiàn),通過(guò)這種設(shè)計(jì)可減少電路系統(tǒng)元件的數(shù)量,提高系統(tǒng)集成度和可靠性。詳細(xì)闡述

2019-06-19 07:42:37

文章出處:電子工程師 作者:徐軍 王華東 江蘇財(cái)經(jīng)職業(yè)技術(shù)學(xué)院引言 在許多嵌入式系統(tǒng)的實(shí)際應(yīng)用中,需要擴(kuò)展FP-GA(現(xiàn)場(chǎng)可編程門陣列)模塊,將CPU實(shí)現(xiàn)有困難或實(shí)現(xiàn)效率低的部分用FPGA實(shí)現(xiàn),如數(shù)

2019-05-06 09:18:16

的電子電路設(shè)計(jì)。FPGA是一種高密度可編程邏輯器件,其邏輯功能的實(shí)現(xiàn)是通過(guò)把設(shè)計(jì)生成的數(shù)據(jù)文件配置進(jìn)芯片內(nèi)部的靜態(tài)配置數(shù)據(jù)存儲(chǔ)器來(lái)完成的,具有可重復(fù)編程性,可以靈活實(shí)現(xiàn)各種邏輯功能。與ASIC

2016-02-01 14:44:30

基于FPGA的數(shù)字脈沖壓縮技術(shù)1.數(shù)字脈沖壓縮實(shí)現(xiàn)原理2.電路設(shè)計(jì)2.1APEX2OKE系列FPGA 簡(jiǎn)介2.2 基于FPGA 的算法研究及實(shí)現(xiàn) 2.3 脈沖壓縮在FPGA 上的實(shí)現(xiàn)

2011-03-02 09:41:50

分析汽車尾燈控制 電路設(shè)計(jì)原理 ,采用 和硬件描述語(yǔ)言 實(shí)現(xiàn)汽車尾燈控制 電路的設(shè)計(jì),具有可編程性、線路簡(jiǎn)單、可靠性高等特點(diǎn) ,并通過(guò)仿真對(duì)結(jié)果進(jìn)行了驗(yàn)證。 隨著集成電路工藝 技術(shù)的高速發(fā)展

2011-11-10 09:14:35

立創(chuàng)EDA電路設(shè)計(jì)與制作基于STM32核心板的電路設(shè)計(jì)與制作流程什么是STM32核心板組成:通信——下載模塊接口電路、電源轉(zhuǎn)換電路、JTAG/SWD調(diào)試接口電路、獨(dú)立按鍵電路、OLED顯示屏接口電路

2021-11-11 08:17:03

如何實(shí)現(xiàn)CMOS圖像敏感器驅(qū)動(dòng)電路設(shè)計(jì)?CMOS圖像敏感器STAR250的技術(shù)指標(biāo)是什么?如何實(shí)現(xiàn)Verilog HDL驅(qū)動(dòng)時(shí)序設(shè)計(jì)?

2021-04-20 06:59:27

如何實(shí)現(xiàn)GY-906 MLX90614ESF非接觸式紅外測(cè)溫模塊電路設(shè)計(jì)?

2022-02-23 06:41:29

HSDI接口的硬件結(jié)構(gòu)以及接口信號(hào)的時(shí)序和功能操作基于FPGA實(shí)現(xiàn)HSDI接口的設(shè)計(jì)

2021-04-09 06:40:16

EC20 R2.1 Mini PCIe-C模塊是什么?如何去實(shí)現(xiàn)EC20 R2.1 Mini PCIe-C模塊的硬件電路設(shè)計(jì)?

2021-11-01 06:50:57

FPGA芯片是由哪些部分組成的?如何去實(shí)現(xiàn)一種基于FPGA芯片的可重構(gòu)數(shù)字電路設(shè)計(jì)?

2021-11-05 08:38:57

怎么實(shí)現(xiàn)ACS712電流傳感器模塊電路設(shè)計(jì)?

2021-11-09 07:49:38

怎么實(shí)現(xiàn)基于msp430和電容式觸控技術(shù)的門禁控制面板電路設(shè)計(jì)?

2021-06-16 08:20:09

USB的主要優(yōu)點(diǎn)有哪些?USB結(jié)構(gòu)與工作原理是什么?USB外設(shè)控制器怎么實(shí)現(xiàn)?怎么實(shí)現(xiàn)帶DMA視頻信號(hào)接口功能的USB接口電路設(shè)計(jì)?

2021-05-31 06:25:17

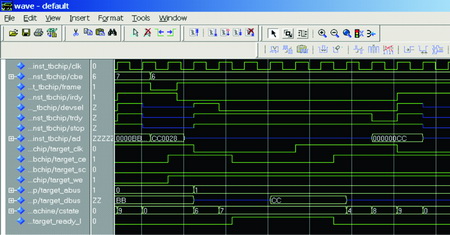

SPI接口主模式電路設(shè)計(jì)。(1)輸出時(shí)鐘頻率可調(diào):主時(shí)鐘2/4/8/32/64分頻;(2)具有主動(dòng)收發(fā)功能;(3)發(fā)送、接收數(shù)據(jù)均為16bit;(4)完成全部流程:設(shè)計(jì)規(guī)范文檔、模塊設(shè)計(jì)、代碼輸入、功能仿真、約束與綜合、布局布線、下載驗(yàn)證等。

2016-11-25 00:00:58

,數(shù)字控制信號(hào)經(jīng)過(guò) DA轉(zhuǎn)換后輸出模擬控制電壓到后端控制電路,實(shí)現(xiàn)對(duì)七路溫度的閉環(huán)控制。 4.FPGA與外圍電路之間的通信接口 FPGA與外圍電路之間的通信接口主要包括與溫度傳感器,DSP,232接口

2020-08-19 09:29:48

章禮宏 范全潤(rùn)1 引言隨著電路規(guī)模不斷擴(kuò)大,以及競(jìng)爭(zhēng)帶來(lái)的上市時(shí)間的壓力,越來(lái)越多的電路設(shè)計(jì)者開(kāi)始利用設(shè)計(jì)良好的、經(jīng)反復(fù)驗(yàn)證的電路功能模塊來(lái)加快設(shè)計(jì)進(jìn)程。這些電路功能模塊被稱為IP

2019-07-29 08:33:45

本文用FPGA 設(shè)計(jì)并實(shí)現(xiàn)了JTAG(即節(jié)點(diǎn)測(cè)試動(dòng)作群)接口電路。首先介紹了JTAG 的定義和引腳的定義;闡述了JTAG 的結(jié)構(gòu),特點(diǎn)和工作原理;然后在Altera FLEX10K100 系列芯片上完成了硬件

2009-07-08 15:18:15 10

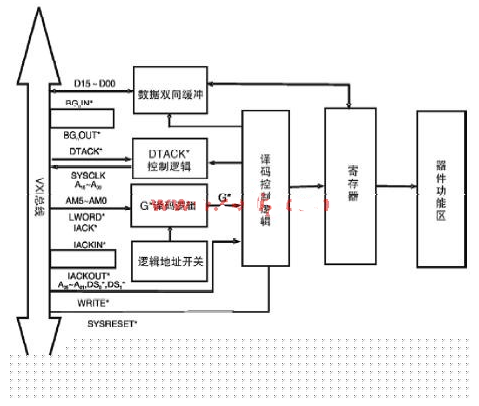

10 TCP/IP-VXIbus接口規(guī)范,用于把Vxibus 儀器用標(biāo)準(zhǔn)方式連接到一個(gè)TCP/IP計(jì)算機(jī)網(wǎng)絡(luò)。文章給出了這個(gè)規(guī)范的目標(biāo)以及網(wǎng)絡(luò)儀器協(xié)議在TCP/IP-VXIbus接口設(shè)備內(nèi)實(shí)現(xiàn)的LAN-to-VXI 映射圖,并用一個(gè)

2009-07-08 17:22:01 13

13 本文介紹了一種基于FPGA 技術(shù)的IDE 硬盤接口的設(shè)計(jì)。該卡提供兩個(gè)符合ATA- 6 規(guī)范的接口,采用FPGA 實(shí)現(xiàn)了兩套IDE 接口功能,設(shè)計(jì)支持PIO 和Ultra DMA 傳輸模式,文章側(cè)重于介紹用FPGA 實(shí)現(xiàn)IDE

2009-07-22 15:58:08 0

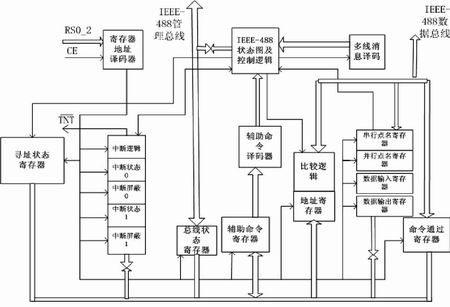

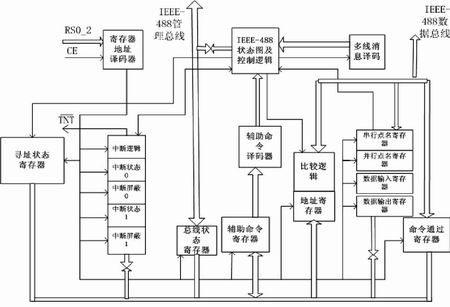

0 GPIB接口是測(cè)量?jī)x器中常用的接口方式。通過(guò)將接口設(shè)計(jì)分解為同步狀態(tài)機(jī)設(shè)計(jì)和寄存器讀寫電路設(shè)計(jì)。

2009-07-22 16:05:25 0

0 文章介紹了一種采基于FPGA 實(shí)現(xiàn)UART電路的方法,并對(duì)系統(tǒng)結(jié)構(gòu)進(jìn)行了模塊化分解以適應(yīng)自頂向下的設(shè)計(jì)方法。采用有限狀態(tài)機(jī)對(duì)接收器模塊和發(fā)送器模塊進(jìn)行了設(shè)計(jì),所有功能的

2009-08-15 09:27:55 46

46 以太網(wǎng)到多路E1適配電路設(shè)計(jì)及FPGA實(shí)現(xiàn)

摘要:介紹了一種基于現(xiàn)場(chǎng)可編程門陣列(FPGA)的以太網(wǎng)數(shù)據(jù)-多路E1反向復(fù)用器同步電路設(shè)計(jì),分析了FPGA具體實(shí)現(xiàn)過(guò)程中的一些常

2009-11-13 20:59:00 22

22 利用現(xiàn)場(chǎng)可編程門陣列FPGA 實(shí)現(xiàn)單片機(jī)的外設(shè)接口電路可以簡(jiǎn)化單片機(jī)系統(tǒng)的硬件電路,提高系統(tǒng)的集成度、可靠性和系統(tǒng)設(shè)計(jì)的靈活性。本文介紹了基于FPGA 的單片機(jī)外設(shè)接口電

2009-12-26 16:43:27 80

80 本文介紹了一種基于FPGA 的光纖陀螺慣導(dǎo)系統(tǒng)溫控電路接口設(shè)計(jì)。主要說(shuō)明了溫控電路整體結(jié)構(gòu),溫控電路工作流程,FPGA 與外圍電路的通信接口和FPGA 的邏輯設(shè)計(jì)等幾個(gè)方面。

2010-01-13 15:20:38 24

24 摘要:介紹了LVDS(Low Voltage Differential Signals)技術(shù)的原理及其典型應(yīng)用,并討論了在實(shí)際電路設(shè)計(jì)中使用LVDS接口時(shí)應(yīng)注意的問(wèn)題。關(guān)鍵詞:LVDS 接口 PCB

2010-05-14 09:29:00 59

59 人機(jī)對(duì)話接口電路設(shè)計(jì)與實(shí)現(xiàn)摘 要: 語(yǔ)音是人類交往的重要手段, 當(dāng)被應(yīng)用在電子系統(tǒng)中關(guān)鍵的一點(diǎn)就是人機(jī)界面要良好。文中就語(yǔ)音或其他音頻信號(hào)的人

2010-06-13 18:16:31 27

27 本文介紹了一種基于FPGA技術(shù)的IDE硬盤接口的設(shè)計(jì)。該卡提供兩個(gè)符合ATA-6規(guī)范的接口,采用FPGA實(shí)現(xiàn)了兩套IDE接口功能,設(shè)計(jì)支持PIO和Ultra DMA傳輸模式,文章側(cè)重于介紹用FPGA實(shí)現(xiàn)IDE接

2010-08-09 15:11:32 22

22 為了滿足某測(cè)控平臺(tái)的設(shè)計(jì)要求,設(shè)計(jì)并實(shí)現(xiàn)了基于FPGA的六通道HDLC并行通信系統(tǒng)。該系統(tǒng)以FPGA為核心,包括FPGA、DSP、485轉(zhuǎn)換接口等部分。給出了系統(tǒng)的電路設(shè)計(jì)、關(guān)鍵模塊及軟件

2010-09-30 16:49:30 43

43 摘 要:GPIB接口是測(cè)試儀器中常用的接口方式。通過(guò)將接口設(shè)計(jì)分解為同步狀態(tài)機(jī)設(shè)計(jì)和寄存器讀寫電路設(shè)計(jì),采用Verilog語(yǔ)言實(shí)現(xiàn)了滿足IEEE488.1協(xié)議的IP Core設(shè)計(jì)。將

2006-03-24 13:32:10 4527

4527

基于PCI總線的GP-IB接口電路設(shè)計(jì)

摘要:?主要介紹作為從設(shè)備如何根據(jù)PCI總線協(xié)議設(shè)計(jì)PCI總線接口電路,從而實(shí)現(xiàn)基于PCI總線的GP-IB接口電路設(shè)計(jì),重點(diǎn)闡述PCI總

2008-12-26 15:14:36 1168

1168

摘要:為了實(shí)現(xiàn)高速HDLC通訊協(xié)議,設(shè)計(jì)了DSP+FPGA結(jié)構(gòu)的485通訊接口,接口包括DSP、FPGA、485轉(zhuǎn)換等硬件電路,以及DSP與FPGA之間的數(shù)據(jù)交換程序和FPGA內(nèi)部狀態(tài)機(jī);其中DSP用于實(shí)現(xiàn)數(shù)據(jù)控制,FPGA用于實(shí)現(xiàn)HDLC通訊協(xié)議,DSP與FPGA之間采用XINTF方式,通過(guò)雙FI

2011-02-25 17:24:34 98

98 集成電路設(shè)計(jì)越來(lái)越向系統(tǒng)級(jí)的方向發(fā)展,解決模塊間的接口問(wèn)題顯得尤為重要。SPI 串行總線是一種常用的標(biāo)準(zhǔn)接口,其使用簡(jiǎn)單方便而且占用系統(tǒng)資源少,應(yīng)用相當(dāng)廣泛。本文將介紹

2011-06-10 16:32:53 52

52 在本文工作的基礎(chǔ)上,可以進(jìn)一步發(fā)揮FPGA的靈活性。如可以利用FPGA實(shí)現(xiàn)DSP功能,從而提供音頻DSP處理或編碼解碼;也可以與SoPC相結(jié)合,作為音頻接口模塊,為片上系統(tǒng)提供音頻接口

2011-06-24 10:38:33 7291

7291

高速SDRAM存儲(chǔ)器接口電路設(shè)計(jì)(Altera FPGA開(kāi)發(fā)板)如下圖所示:

2012-08-15 14:33:41 3326

3326

異步SRAM存儲(chǔ)器接口電路設(shè)計(jì)(Altera FPGA開(kāi)發(fā)板)如圖所示:

2012-08-15 14:37:05 3862

3862

本文設(shè)計(jì)一個(gè)通信接口模塊,通過(guò)光纖接口與中心機(jī)連接,實(shí)現(xiàn)對(duì)前端受控模塊的遠(yuǎn)程控制和狀態(tài)監(jiān)測(cè)。

2012-09-03 15:59:18 4808

4808

電子發(fā)燒友網(wǎng)核心提示 :RS 232接口是現(xiàn)在最常用的一種通信接口。隨著FPGA技術(shù)的高速發(fā)展,一些常見(jiàn)的接口電路的時(shí)序電路可以通過(guò)FPGA實(shí)現(xiàn),通過(guò)這種設(shè)計(jì)可減少電路系統(tǒng)元件的數(shù)量

2012-11-27 10:28:11 5937

5937 基于FPGA的慣性平臺(tái)測(cè)試保護(hù)電路設(shè)計(jì)..

2016-01-04 17:03:55 7

7 基于FPGA的光電系統(tǒng)同步自適應(yīng)電路設(shè)計(jì)與實(shí)現(xiàn)

2016-01-04 17:03:55 10

10 AD與DA接口電路設(shè)計(jì),有興趣的同學(xué)可以下載學(xué)習(xí)

2016-05-04 11:31:56 0

0 電路設(shè)計(jì)[FPGA]設(shè)計(jì)經(jīng)驗(yàn),有需要的下來(lái)看看

2016-05-20 11:16:35 46

46 基于FPGA的串口通信電路設(shè)計(jì)

2017-01-24 17:30:13 33

33 基于FPGA技術(shù)的RS232接口時(shí)序電路設(shè)計(jì)方案

2017-01-26 11:36:55 29

29 高速串行接口鏈路層的電路設(shè)計(jì)與實(shí)現(xiàn)

2017-01-19 21:22:54 11

11 基于FPGA的以太網(wǎng)接口設(shè)計(jì)與實(shí)現(xiàn)_李勛

2017-01-19 21:54:24 8

8 在論壇里有人發(fā)帖子,問(wèn)關(guān)于FPGA的硬件電路問(wèn)題,我想涉及到這個(gè)問(wèn)題的基本都是硬件工程師或者在讀學(xué)生,所以我介紹一下我是怎么學(xué)習(xí)FPGA的硬件電路設(shè)計(jì)的吧!

2017-02-11 12:55:11 25430

25430 語(yǔ)言來(lái)開(kāi)發(fā)波特率發(fā)生器、接收模塊和發(fā)送模塊這三個(gè)模塊,以及系統(tǒng)各個(gè)模塊的具體設(shè)計(jì)方法和原理,用 QuartusII軟件進(jìn)行仿真并給出結(jié)果,分別驗(yàn)證各個(gè)模塊的正確性及用 FPGA實(shí)現(xiàn)串行通信的可行性。

2017-09-01 10:16:10 7

7 基于FPGA的高速DSP與液晶模塊接口的實(shí)現(xiàn)

2017-10-19 13:46:23 3

3 DSP和FPGA的HDLC協(xié)議通訊電路設(shè)計(jì)

2017-10-19 14:46:11 7

7 在基于FPGA芯片的工程實(shí)踐中,經(jīng)常需要FPGA與上位機(jī)或其他處理器進(jìn)行通信,為此設(shè)計(jì)了用于短距離通信的UART接口模塊。該模塊的程序采用VHDL語(yǔ)言編寫,模塊的核心發(fā)送和接收子模塊均采用有限狀態(tài)機(jī)

2017-11-18 11:33:01 5153

5153 隨著存儲(chǔ)技術(shù)的不斷進(jìn)步,F(xiàn)lash Memory的存儲(chǔ)容量越來(lái)越大,讀寫數(shù)度越來(lái)越快。本文實(shí)現(xiàn)的NAND Flash控制器放置在CPU和NANF Flash器件之間,實(shí)現(xiàn)了NAND Flash

2017-11-23 14:15:35 2812

2812 介紹了采用CPLD和Flash器件對(duì)FPGA 實(shí)現(xiàn)快速并行配置,并給出了具體的硬件電路設(shè)計(jì)和關(guān)鍵模塊的內(nèi)部編程思路。

2018-10-24 15:15:49 7

7 中國(guó)大學(xué)MOOC

本課程以目前流行的Xilinx 7系列FPGA的開(kāi)發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語(yǔ)言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開(kāi)發(fā)開(kāi)始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進(jìn)階應(yīng)用。

2019-08-06 06:08:00 3083

3083 中國(guó)大學(xué)MOOC

本課程以目前流行的Xilinx 7系列FPGA的開(kāi)發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語(yǔ)言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開(kāi)發(fā)開(kāi)始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進(jìn)階應(yīng)用。

2019-12-02 07:08:00 2118

2118

本教程介紹Quartus Prime CAD系統(tǒng)。本文概述了用fpga器件實(shí)現(xiàn)的典型電路設(shè)計(jì)CAD流程,并說(shuō)明了該流程是如何在quartus prime軟件中實(shí)現(xiàn)的。通過(guò)給出使用quartus prime軟件在intel-fpga設(shè)備中實(shí)現(xiàn)非常簡(jiǎn)單的電路的逐步說(shuō)明,說(shuō)明了設(shè)計(jì)過(guò)程。

2019-09-20 08:00:00 6

6 VXIbus是VMEbus在儀器領(lǐng)域的擴(kuò)展,是計(jì)算機(jī)操縱的模塊化自動(dòng)儀器系統(tǒng)。它依靠有效的標(biāo)準(zhǔn)化,采用模塊化的方式,實(shí)現(xiàn)了系列化、通用化以及VXIbus儀器 的互換性和互操作性,其開(kāi)放的體系結(jié)構(gòu)和Plug&Play方式完全符合信息產(chǎn)品的要求。

2019-09-26 14:24:20 1244

1244

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA的硬件電路設(shè)計(jì)教程和FPGA平臺(tái)資料簡(jiǎn)介包括了:FPGA技術(shù)概述;主流FPGA器件介紹;VIRTEX-5 FPGA電路設(shè)計(jì);V4LX160 FPGA平臺(tái)介紹;

2020-07-06 18:11:22 158

158 UART作為RS232協(xié)議的控制接口得到了廣泛的應(yīng)用,將UART的功能集成到FPGA芯片中,可使整個(gè)系統(tǒng)更為靈活、緊湊,減小整個(gè)電路的體積,提高系統(tǒng)的可靠性和穩(wěn)定性。提出了一種基于FPGA的UART

2020-07-07 17:28:03 10

10 現(xiàn)場(chǎng)可編程邏輯陣列(FPGA)資源豐富,結(jié)構(gòu)靈活,近年來(lái)發(fā)展迅猛。針對(duì)其特點(diǎn),本文設(shè)計(jì)了基于FPGA的增量式光電編碼器的接口電路,實(shí)現(xiàn)了對(duì)增量式編碼器脈沖信號(hào)的倍頻、鑒相及計(jì)數(shù)等功能。

2021-04-27 13:57:50 3886

3886

利用FPGA的在系統(tǒng)下載或重新配置功能,可以在電路設(shè)計(jì)和調(diào)試時(shí)改變整個(gè)電路的硬件邏輯關(guān)系,而不需要改變印制電路板的結(jié)構(gòu)。

2021-05-12 10:46:10 25

25 FPGA CPLD數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)分享.(電源技術(shù)發(fā)展怎么樣)-FPGA CPLD數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)分享? ? ? ? ? ? ? ? ? ??

2021-09-18 10:58:03 51

51 高頻電源模塊驅(qū)動(dòng)電路設(shè)計(jì)(現(xiàn)代高頻開(kāi)關(guān)電源技術(shù)及應(yīng)用 百度網(wǎng)盤)-本文介紹了驅(qū)動(dòng)器M57962AL的特點(diǎn)以及選用該驅(qū)動(dòng)器實(shí)現(xiàn)的IGBT~動(dòng)電路

2021-09-29 17:51:16 29

29 電路設(shè)計(jì)模塊電路設(shè)計(jì)模塊參考資料電路設(shè)計(jì)模塊注意事項(xiàng)知識(shí)點(diǎn)補(bǔ)充電源和地之間并聯(lián)電容作用:共模干擾和差模干擾電路設(shè)計(jì)模塊參考資料17種常見(jiàn)的單片機(jī)電路設(shè)計(jì)模塊電路模塊設(shè)計(jì)合集參考之前項(xiàng)目中所用到的電路

2021-11-06 16:21:01 54

54 ? 串行接口常用于芯片至芯片和電路板至電路板之間的數(shù)據(jù)傳輸。隨著系統(tǒng)帶寬不斷增加至多吉比特范圍,并行接口已經(jīng)被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨(dú)立

2023-07-27 16:10:01 1565

1565

電子發(fā)燒友網(wǎng)站提供《基于LPC2131的的CAN接口模塊硬件電路設(shè)計(jì).rar》資料免費(fèi)下載

2023-11-10 10:46:01 0

0 FPGA開(kāi)發(fā)板是一種基于FPGA(現(xiàn)場(chǎng)可編程門陣列)技術(shù)的開(kāi)發(fā)平臺(tái),它允許工程師通過(guò)編程來(lái)定義和配置FPGA芯片上的邏輯電路,以實(shí)現(xiàn)各種數(shù)字電路和邏輯功能。FPGA開(kāi)發(fā)板通常包括FPGA芯片、時(shí)鐘模塊、電源模塊、輸入輸出接口等組件,并提供相應(yīng)的編程軟件和開(kāi)發(fā)工具,方便工程師進(jìn)行電路設(shè)計(jì)和調(diào)試。

2024-03-14 18:20:29 553

553

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論