目前,天基電子系統(tǒng)開(kāi)發(fā)人員面臨的壓力越來(lái)越大,在項(xiàng)目日程安排越來(lái)越緊張且預(yù)算一再削減的情況下,他們卻需要提供更高的系統(tǒng)性能。然而,天基系統(tǒng)具有一套獨(dú)特而嚴(yán)格的尺寸、重量和功耗(SWAl?)限制,這對(duì)于設(shè)計(jì)人員來(lái)說(shuō)無(wú)疑是一個(gè)棘手的問(wèn)題。

為達(dá)到事半功倍的效果,各大公司紛紛采用FPGA等商用成品(COTS)器件。從SWAP限制、成本與工作效率方面來(lái)說(shuō),可重構(gòu)的FPGA所固有的靈活性為天基系統(tǒng)的開(kāi)發(fā)人員提供了巨大的幫助。

充分利用現(xiàn)有工程設(shè)計(jì)與預(yù)算資源的一種方式是創(chuàng)建能部署到多個(gè)太空任務(wù)中的靈活的有效負(fù)載。SEAKR工程公司采用可重構(gòu)的賽靈思Virtex FPGA創(chuàng)建了靈活的高性能計(jì)算平臺(tái)作為各種天基系統(tǒng)的核心。使用該可重構(gòu)的汁算(RCC)方法,可在多個(gè)太空任務(wù)的SWAP、成本與時(shí)間限制范圍內(nèi)實(shí)現(xiàn)高要求的性能目標(biāo)。最引人注目的例子包括:SEAKR為美國(guó)雷神公司(Raytheon)的先進(jìn)反應(yīng)戰(zhàn)術(shù)效能軍用成像光譜儀(Artemis)開(kāi)發(fā)的板載處理器、可編程太空收發(fā)器以及目前尚在開(kāi)發(fā)過(guò)程中的可編程太空IP調(diào)制解調(diào)器和獵戶(hù)座視覺(jué)處理器。

應(yīng)用獨(dú)立處理器的架構(gòu)

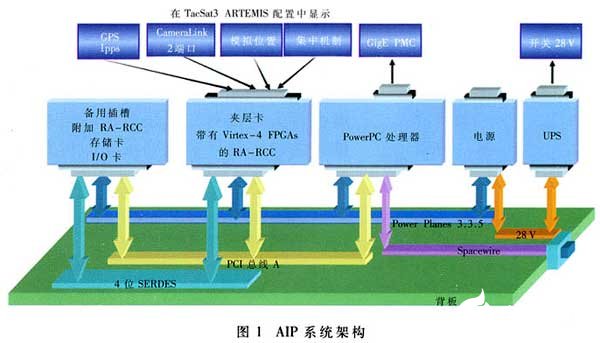

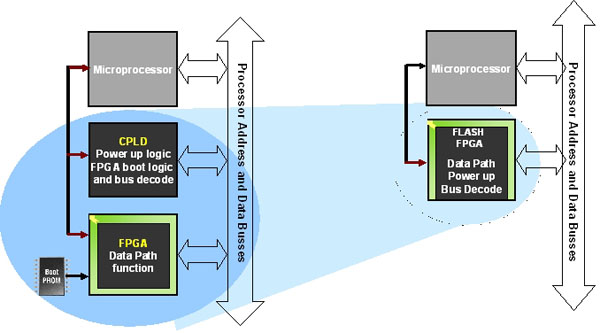

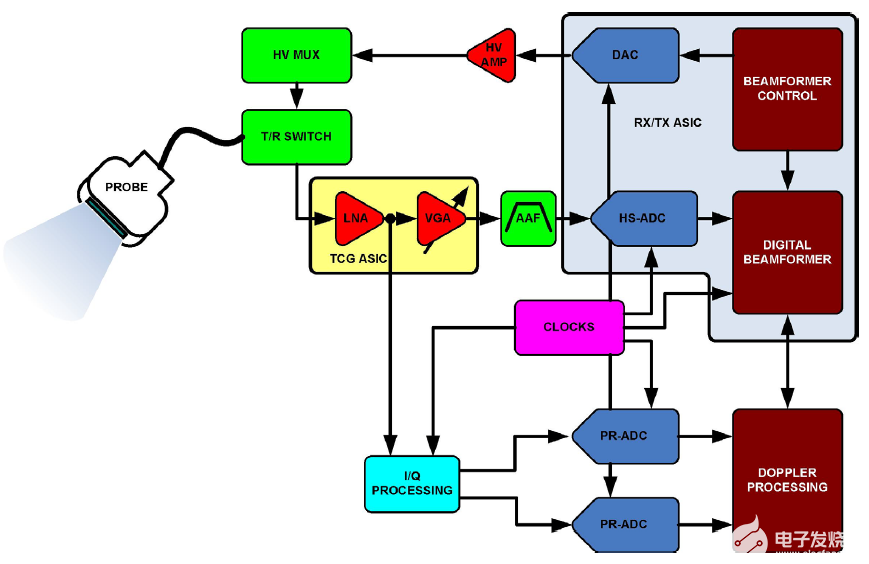

這款全新平臺(tái)稱(chēng)為應(yīng)用獨(dú)立處理器(AIP),在靈活、可擴(kuò)展的架構(gòu)中集成了一系列標(biāo)量處理器與RCC,可支持開(kāi)放式標(biāo)準(zhǔn),如圖1所示。由于該處理器具有靈活的I/O架構(gòu),可以?昆搭各種板卡以創(chuàng)建最適合應(yīng)用要求的不同配置,稱(chēng)之為專(zhuān)門(mén)任務(wù)功能。AIP利用賽靈思基于SRAM的FPGA的獨(dú)特功能,允許在軌重構(gòu),從而獲得更高的靈活性與SWAP優(yōu)勢(shì)。Ail?還支持各種抗單粒子效應(yīng)(SEE)輻射技術(shù),確保在不同軌道中都能夠可靠地進(jìn)行操作。

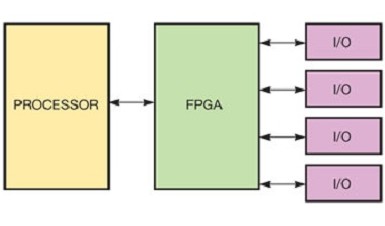

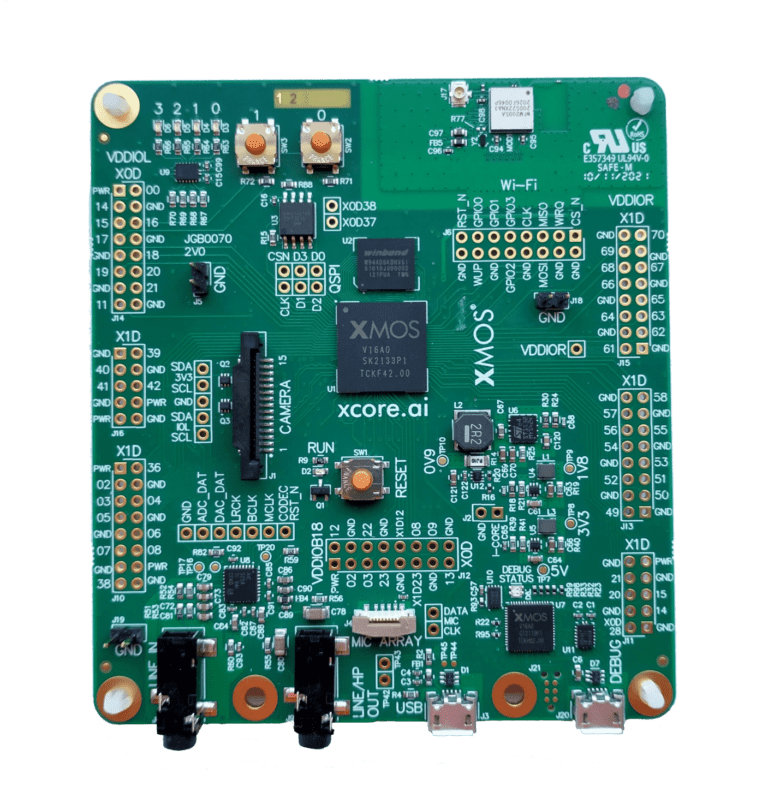

AIP系統(tǒng)架構(gòu)的核心是一塊可重構(gòu)的計(jì)算機(jī)板卡,其上包括3個(gè)Virtex-4 FPGA,如圖2所示。SEAKR對(duì)目前可用的組件進(jìn)行了調(diào)研,結(jié)果表明Virtex FPGA是惟一能達(dá)到性能目標(biāo)并具有航天飛行特性要求的設(shè)備。針對(duì)要求最苛刻的應(yīng)用,賽靈思提供了Virtex-4QV太空級(jí)設(shè)備。這些太空級(jí)FPGA 采用了與商用級(jí)FPGA相同的架構(gòu),但經(jīng)過(guò)特殊處理和篩選以達(dá)到Q類(lèi)與V類(lèi)要求。

ViHex-4 FPGA通過(guò)與順序處理器協(xié)調(diào)工作,可充當(dāng)協(xié)處理器以加速關(guān)鍵處理密集型任務(wù)的進(jìn)展。三重FPGA板的架構(gòu)具有高度的靈活性,可滿(mǎn)足不同任務(wù)的獨(dú)特需求。例如,在抗SEE技術(shù)中使用3個(gè)FPGA,可滿(mǎn)足該技術(shù)對(duì)組件級(jí)冗余性的要求;多個(gè)設(shè)備間共享一個(gè)大型協(xié)處理器并使用環(huán)形總線通過(guò)LVDS接口連接3個(gè) FPGA,可實(shí)現(xiàn)設(shè)備間的高速通信。采用擴(kuò)展的6U外形,板卡上將有2個(gè)連接器用于板卡間通信:一個(gè)用于CompactPCI背板,另一個(gè)用于高速串行網(wǎng)絡(luò)。

每個(gè)FPGA都可直接訪問(wèn)RCC板上的專(zhuān)用高速存儲(chǔ)器以及支持通過(guò)高速夾層卡進(jìn)行擴(kuò)展與定制的連接器。使用此架構(gòu),可以利用特定I/O、存儲(chǔ)器、模擬電路甚至附加邏輯來(lái)擴(kuò)展RCC板的功能。特定應(yīng)用中的抗SEE輻射架構(gòu)的組件夾層卡,通過(guò)3個(gè)連接器與RCC板連接起來(lái),每個(gè)連接器可提供170 LVDS I/O。

將特定任務(wù)的功能模塊移動(dòng)到夾層卡,可以在多種獨(dú)特應(yīng)用中使用相同的基于FPGA的處理卡。該通用架構(gòu)有助于降低項(xiàng)目風(fēng)險(xiǎn)、減少成本并縮短時(shí)間。

FPGA中的抗輻射效應(yīng)

基于SRAM的配置電路在受到輻射時(shí)極易發(fā)生翻轉(zhuǎn),因此在太空中飛行的基于FPGA的可重構(gòu)系統(tǒng)需要給予特別考慮,以確保其在高輻射環(huán)境中可靠運(yùn)行。首先要考慮組件的選擇。除了工業(yè)和軍事溫度級(jí)選項(xiàng)外,賽靈思還提供V級(jí)Virtex-4與Virtex-5 FPGA,這些FPGA經(jīng)過(guò)特殊處理,可以防止因輻射而導(dǎo)致的閉鎖現(xiàn)象,保證總劑量輻射效應(yīng)下的性能。這些器件還能經(jīng)受中子和質(zhì)子i七束的進(jìn)一步錘煉,可靠地預(yù)測(cè)出特定軌道上單粒子翻轉(zhuǎn)(SEU)及單粒子功能中斷的頻率。此數(shù)據(jù)可指導(dǎo)工程師選擇適用于應(yīng)用與軌道的抗翻轉(zhuǎn)方案。

可重構(gòu)FPGA的抗翻轉(zhuǎn)功能一般需要組合使用硬件三重冗余與配置存儲(chǔ)器清除。硬件三重冗余包括三重關(guān)鍵電路,即使在某一組件發(fā)生輻射引發(fā)的翻轉(zhuǎn)后也能確保連續(xù)運(yùn)行。此外,它還增加了一個(gè)表決電路,該電路將來(lái)自3個(gè)邏輯分支的、信號(hào)進(jìn)行比較并拒絕因翻轉(zhuǎn)而產(chǎn)生的無(wú)效信號(hào)。

設(shè)計(jì)人員可從一系列方案中進(jìn)行選擇,以滿(mǎn)足系統(tǒng)性能與可用性要求。其中一種方法是使用冗余FPGA與一個(gè)抗輻射的外部表決電路。另一種方法是設(shè)備級(jí)抗輻射,即在一個(gè)FPGA中配置三重關(guān)鍵任務(wù)邏輯并使用相關(guān)聯(lián)的表決電路。傳統(tǒng)上,工程師手動(dòng)實(shí)現(xiàn)三模冗余(TMR)設(shè)計(jì)方法。現(xiàn)在,賽靈思提供了專(zhuān)門(mén)的設(shè)計(jì)工具,可在FPGA內(nèi)自動(dòng)實(shí)現(xiàn),F(xiàn)MR。選擇抗輻射方案時(shí),會(huì)受到一些因素的影響,比如目標(biāo)電路的尺寸、選定軌道中的輻射級(jí)別及電路的運(yùn)行時(shí)間要求等。

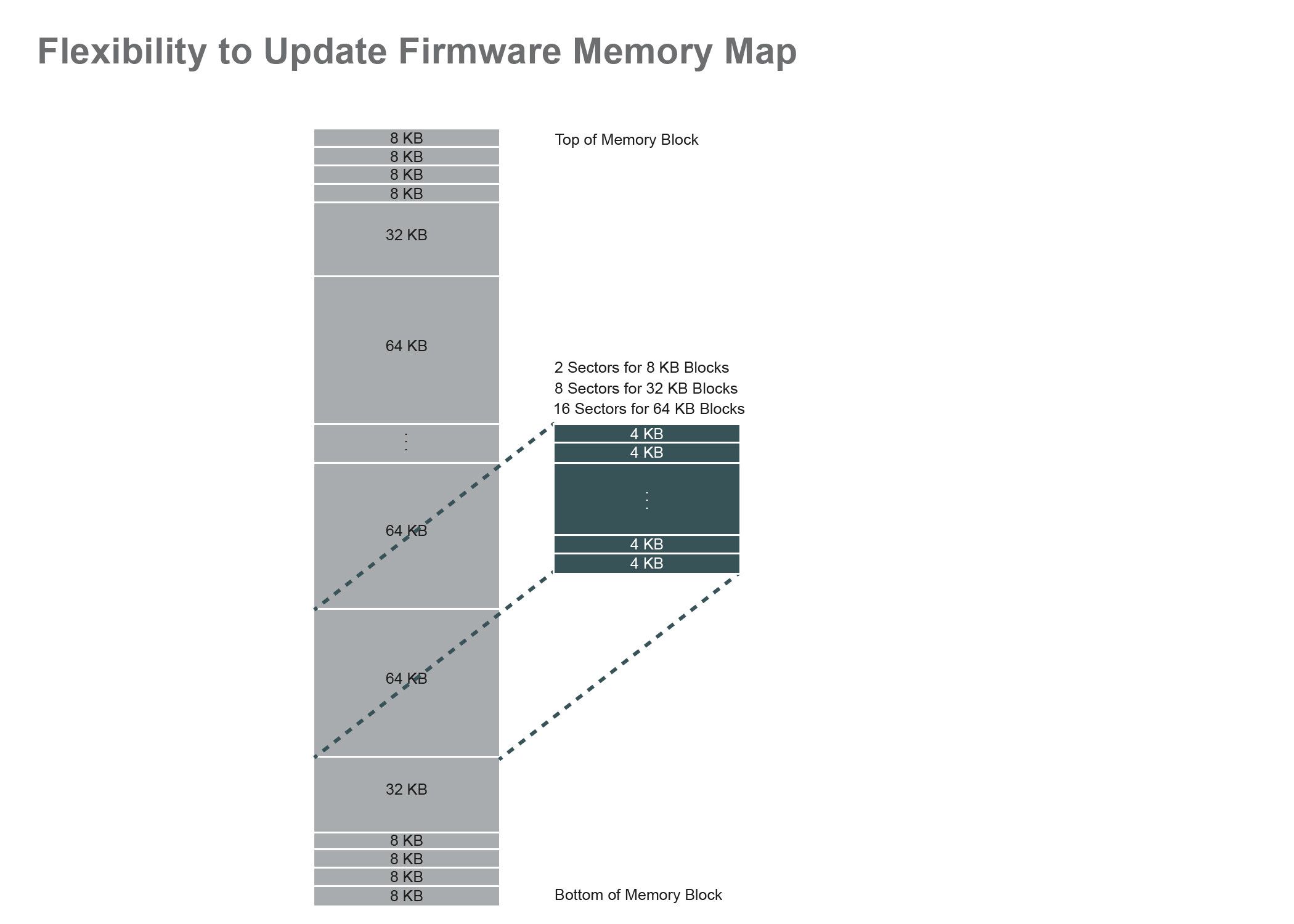

存儲(chǔ)器清除的基本概念是比累計(jì)翻轉(zhuǎn)次數(shù)更頻繁地重寫(xiě)配置存儲(chǔ)器。設(shè)計(jì)人員可從一系列存儲(chǔ)器清除方法中進(jìn)行選擇,以適應(yīng)不同的翻轉(zhuǎn)頻率與運(yùn)行時(shí)間要求。最簡(jiǎn)單的方法就是將完整比特流重新加載到配置存儲(chǔ)器中。該方法開(kāi)銷(xiāo)低,但要求電路至少在1個(gè)配置周期內(nèi)保持不工作。對(duì)于在運(yùn)行時(shí)間方面要求更嚴(yán)格、翻轉(zhuǎn)率更高或同時(shí)存在這2種情況的應(yīng)用,還可采用更高級(jí)的方法。例如充分利用VirtexFPGA的部分重構(gòu)功能,包括檢測(cè)存儲(chǔ)器翻轉(zhuǎn)然后只重構(gòu)存儲(chǔ)器陣列的選定子集的電路。

AIP應(yīng)用現(xiàn)狀

AIP架構(gòu)已成功應(yīng)用于4個(gè)不同的太空任務(wù)。通過(guò)組合使用基于FPGA的RCC板與靈活的夾層卡,工程師可以快速構(gòu)建各種處理與通信系統(tǒng)并實(shí)施適合每次太空任務(wù)獨(dú)特要求的抗輻射方案。

第一個(gè)采用AlP的真實(shí)產(chǎn)品是先進(jìn)的反應(yīng)戰(zhàn)術(shù)效能軍用成像光譜儀Artemis,該設(shè)備將在計(jì)劃于2009年第2季度發(fā)射的TacSat-3衛(wèi)星上運(yùn)行。Artemis旨在提供戰(zhàn)場(chǎng)情景意識(shí),它利用衛(wèi)星收集的數(shù)據(jù)執(zhí)行先進(jìn)的影像處理,然后通過(guò)窄帶下行鏈路將這些影像傳送給現(xiàn)場(chǎng)的士兵。工程師意識(shí)到,需要采用RCC方案才能滿(mǎn)足太空船對(duì)尺寸、重量和功耗的要求:大小為7.8×11.41×10英寸;重量為18英磅;功耗為40W(硬限制為50W)。

Artemis系統(tǒng)中,2個(gè)Virtex-4 FPGA負(fù)責(zé)執(zhí)行傳感器數(shù)據(jù)采集與校準(zhǔn)等預(yù)處理功能,,基于Micro-BlazeTM軟處理器內(nèi)核的嵌入式處理系統(tǒng)可協(xié)調(diào)存儲(chǔ)器訪問(wèn)與處理器調(diào)整,而 PowerPC單板計(jì)算機(jī)用于實(shí)現(xiàn)影像生成與目標(biāo)提示。圖1顯示了Artemis系統(tǒng)架構(gòu)。

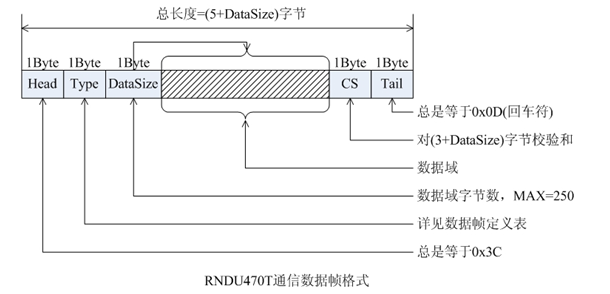

由于影像數(shù)據(jù)路徑不是關(guān)鍵任務(wù)型,所以配置存儲(chǔ)器清除為Artemis提供了合適的抗輻射功能。設(shè)計(jì)人員無(wú)需采取3個(gè)邏輯或冗余設(shè)備就能夠滿(mǎn)足可用性要求。不僅如此,還可以使用商用級(jí)FPGA來(lái)構(gòu)建閃存;每個(gè)比特流都配置FPGA以處理特定波形和頻率。這樣,系統(tǒng)將能夠使用最少的硬件數(shù)來(lái)支持多種波形,如表1所示。

高度靈活的RCC板為初始系統(tǒng)開(kāi)發(fā)前期帶來(lái)了諸多優(yōu)勢(shì)。請(qǐng)求與接收一系列頻隙之間的延遲時(shí)間可能超過(guò)一年。使用可重構(gòu)的硬件,設(shè)計(jì)人員能夠在接收到這些頻隙之前著手開(kāi)發(fā),從而降低了系統(tǒng)成本。2個(gè)Virtex-4 FPGA共享影像處理工作負(fù)荷,而第3個(gè)FPGA保留空閑以最小化功耗。

AIP首次應(yīng)用后極大地提高了工作效率,顯著降低了一次性工程費(fèi)用,從而使接下來(lái)的每個(gè)項(xiàng)目都能節(jié)省約一年的開(kāi)發(fā)時(shí)間。

RCC幫助實(shí)現(xiàn)靈活的收發(fā)器

AIP的第二個(gè)太空任務(wù)應(yīng)用是可編程衛(wèi)星收發(fā)器。PST系統(tǒng)提供了可在多個(gè)無(wú)線電波段上進(jìn)行頻率捷變衛(wèi)星通信的功能。SEAKR工程師最后得出的結(jié)論是,即使是高端的PowerPC處理器也無(wú)法在SWAP要求(即3.86×6.85×7英寸、10磅以及10W的接收功耗與45W發(fā)射功耗)的范圍內(nèi)提供必需的重吊能力。

為了滿(mǎn)足上述要求,設(shè)計(jì)人員利用Vinex FPGA的系統(tǒng)內(nèi)重構(gòu)功能。該系統(tǒng)在頻譜分配中存儲(chǔ)多個(gè)配置比特流,以實(shí)現(xiàn)所需頻率。此外,該功能還可使開(kāi)發(fā)人員修改系統(tǒng)以滿(mǎn)足后續(xù)任務(wù)要求。SEAKR 正在為未來(lái)的部署開(kāi)發(fā)更多的波形。

PST任務(wù)的本質(zhì)是簡(jiǎn)化了抗輻射要求。通信系統(tǒng)保持對(duì)通道的端對(duì)端控制,同時(shí)還能夠容許數(shù)據(jù)錯(cuò)誤:一旦數(shù)據(jù)出現(xiàn)損壞,系統(tǒng)將重新傳輸受影響的數(shù)據(jù)包。該固有的容錯(cuò)功能意味著配置存儲(chǔ)器清除為控制路徑提供了合適的抗SEU輻射功能。為了保護(hù)中間處理結(jié)果,在夾層卡上設(shè)立了3個(gè)存儲(chǔ)器。

為了完成系統(tǒng),需將AIP板與RF模塊、電源模塊通過(guò)擴(kuò)展的6U形底板連接起來(lái),該底板可承受震動(dòng)及發(fā)射時(shí)的其他壓力。

太空中的因特網(wǎng)

太空中的分組網(wǎng)絡(luò)有望提供與地面網(wǎng)絡(luò)相同的靈活性和穩(wěn)健性。長(zhǎng)期以來(lái),可重構(gòu)的FPGA一直是主流的有線網(wǎng)絡(luò)設(shè)備,正如在可編程衛(wèi)星因特網(wǎng)協(xié)議調(diào)制解調(diào)器中所展示的優(yōu)勢(shì)一樣,它可為天基應(yīng)用提供卓越的性能、高度的靈活性并能加速設(shè)計(jì)進(jìn)程。PSIM可從標(biāo)準(zhǔn)衛(wèi)星通信波形中提取以太網(wǎng)幀,同時(shí)還便于太空船上的IP路由。使用分組衛(wèi)星通信,可通過(guò)虛擬電路來(lái)路由與電子束和波形無(wú)關(guān)的數(shù)據(jù)。與標(biāo)準(zhǔn)彎管式衛(wèi)星通信通道相比,分組網(wǎng)絡(luò)提高了可擴(kuò)展性與流量,實(shí)現(xiàn)了分散式多播,且足夠靈活,能夠提供出色的服務(wù)質(zhì)量。

PSIM包括12個(gè)貼裝在4個(gè)RCC卡上的Videx-4V FPGA,以及位于堅(jiān)固耐用的底板上的2個(gè)順序處理器與1個(gè)模擬開(kāi)關(guān)卡。FPGA負(fù)責(zé)執(zhí)行波形處理,而順序處理器提供以太網(wǎng)接口和分組交換功能。

該太空任務(wù)在可用性方面要求采用比Artemis或PST中使用的抗輻射能力更強(qiáng)的方案。因?yàn)殄e(cuò)誤恢復(fù)需要很長(zhǎng)時(shí)間,而且還會(huì)降低可用性,不能達(dá)到目標(biāo)要求。因此,系統(tǒng)必須能夠提供不間斷的端對(duì)端控制。SEAKR工程師實(shí)施了一種既可實(shí)時(shí)糾正錯(cuò)誤又可提供不間斷服務(wù)的抗輻射方案。

在每個(gè)RCC板上的3個(gè)設(shè)備中設(shè)立了三重FPGA邏輯。夾層卡上的抗輻射邏輯設(shè)備充當(dāng)主力表決器。在后臺(tái)進(jìn)行存儲(chǔ)器清除操作,這對(duì)網(wǎng)絡(luò)操作而言是完全透明的。此外,夾層卡還提供到路由器的物理接口。

采用PSIM的太空任務(wù)計(jì)劃于2009年第2季度啟動(dòng)。

載人航天的高性能視頻

AIP架構(gòu)的最新應(yīng)用是獵戶(hù)座載人太空船的視覺(jué)處理單元(VPU)。VPU可為處理影像算法提供可重構(gòu)的平臺(tái),有利于位姿估計(jì)、光學(xué)導(dǎo)航以及壓縮/ 解壓縮。該系統(tǒng)從星象跟蹤儀、視覺(jué)導(dǎo)航傳感器、空間對(duì)接照相機(jī)以及情景意識(shí)攝像機(jī)等各種傳感器處接收影像數(shù)據(jù)。

處理如此龐大的數(shù)據(jù)需要結(jié)合順序處理器與基于FGPA的RCC卡。Virtex-4 FPGA可實(shí)施功能識(shí)別、圖形覆蓋、平鋪以及視頻壓縮等視頻處理算法。此外,它們還集成了MicroBlaze軟處理器內(nèi)核以協(xié)調(diào)算法核心和處理器通信。基于LEON容錯(cuò)處理器的單板計(jì)算機(jī)旨在協(xié)調(diào)系統(tǒng)、處理錯(cuò)誤、配置與監(jiān)控RCC并控制互連。

夾層卡提供傳感器接口,實(shí)施與所有3個(gè)FPGA相連的LVDS鏈路,最大限度地提高視頻流選擇與抗輻射方案的靈活性。

由于VPU所執(zhí)行的任務(wù)“受監(jiān)測(cè)入主觀限制”,SEAKR工程師選擇了Virtex-4QV太空級(jí)FPGA,并實(shí)施了更強(qiáng)大的抗輻射方案。通過(guò)結(jié)合使用TMR方法和配置存儲(chǔ)器清除,可確保透明地糾正控制路徑錯(cuò)誤。

總之,通過(guò)Virtex FPGA,SEAKR工程師不僅已為太空應(yīng)用開(kāi)發(fā)了應(yīng)用獨(dú)立的處理器,同時(shí)還在多次太空任務(wù)中展示了該處理器的高度靈活性。RCC在基于衛(wèi)星的影像處理與通信、高靈活性的無(wú)線電通信、天基網(wǎng)絡(luò)以及人類(lèi)太空飛行導(dǎo)航等領(lǐng)域中充當(dāng)了主要組件。

太空級(jí)Virtex FPGA是COTS組件,可為要求苛刻的數(shù)據(jù)處理和通信系統(tǒng)提供所需性能。使用這些可重構(gòu)的FPGA,可建立高靈活性可擴(kuò)展架構(gòu),從而降低開(kāi)發(fā)成本并縮短設(shè)計(jì)周期。除了支持快速開(kāi)發(fā)與靈活的地面制造外,Virtex FPGA還提供在軌重構(gòu)功能,從而可獲得更多顯著的SWAP優(yōu)勢(shì)。

新一代的V級(jí)可重構(gòu)FPGA可提供更高的邏輯容量、更高的硬化IP塊集成度、更高的性能以及更低的功耗,因此可獲得更多尺寸、重量和功耗等方面的優(yōu)勢(shì)。抗輻射可重構(gòu)的Virtex FPGA消除了邏輯級(jí)或設(shè)備級(jí)的冗余實(shí)施,這不僅簡(jiǎn)化了設(shè)計(jì)人員的工作,同時(shí)還進(jìn)一步擴(kuò)展了SWAP優(yōu)勢(shì)。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論