根據Nyquist第一準則,基帶信號成形能夠消除碼間串擾的影響。隨著超高速數字集成電路的發展,成形濾波器已經由過去的基帶頻域模擬成形濾波器變成現在的基帶時域數字成形濾波器。與基帶模擬成形濾波器相比,基帶數字成形濾波器具有高精度、高可靠性和高靈活性等優點;同時還具有便于大規模集成、易于實現線性相位等特點。實現基帶數字成形的方法很多,與傳統算法相比,分布式算法可以極大地減少硬件電路的規模,提高電路的執行速度。本文采用基于分布式算法思想的時域成形方法來實現基帶信號成形。

1 分布式算法的基本原理

一個線性時不變網絡的輸出可以用下式表示:

其中,y(n)為第n時刻網絡的輸出;xk(n)為第n時刻的第k個輸入變量;Ak為第k個輸入變量的權值。在線性時不變系統中,對于所有n時刻,Ak都是常量。如果該網絡表現為濾波器,常量Ak即為濾波器抽頭系數,變量xk為單一數據源的抽樣數據。仔細觀察(1)式可以看出,輸出單個y(n)需要將k個乘積累加,這種累加可以通過查找表來實現,大大提高了運算的效率。為了使乘法之后的數據寬度不至于展寬,先把數據源數據格式規定為浮點數2的補碼形式。需要注意的是,常量Ak不一定要進行格式轉換來匹配輸入數據的格式,它可以根據所要求的精度進行定義。變量xk可用下式表示:

式中,xkb為二進制數,即取值為0或1;xk0為符號位,“1”表示數據為負,“0”表示數據為正。式中,時間參數“n”已經被省略掉,因為在以下的推導中與時間參數無關。將(2)式代入(1)式中,得:

從(4)式可以看出,每個方括號中進行的是輸入變量的某一個數據位和所有常量A1~Ak的每一位進行位相“與”然后求和,而指數部分則說明了求和結果的位加權,這種加權可以通過移位來實現。而方括號中的計算可以通過建立查找表來實現,具體的操作可通過所有輸入變量的同一位進行尋址來完成。通過(4)式,(1)式就可以用加法、減法和二進制除法來計算了,這樣就避免了頻繁地使用乘法器,從而節約了系統的資源,并且大大縮短了運算的時間[1]。

2 時域成形的原理

(4)式中的查找表方法可以縮短運算的時間,但是二進制除法還是會消耗掉大量的系統時鐘。因為要設計的是基帶信號成形濾波器,所以可以通過直接在時域上成形的方法來完成。

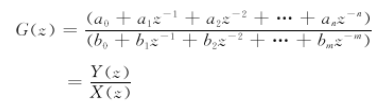

如果輸入為二進制雙極性數據,采用升余弦滾降濾波器進行脈沖成形,其系統函數為:

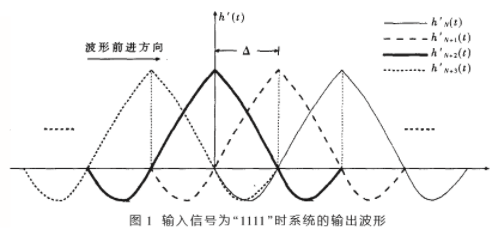

若取截短長度為輸入信號碼元寬度的4倍,則當輸入信號為“1111”時,系統的輸出波形如圖1所示。

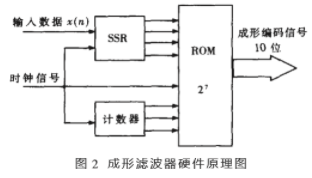

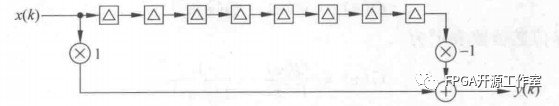

圖中,h′(t)為h(t)的截短。由圖1可知,只需要求出Δ時間段的波形疊加值,依次輸出,就可以得到輸入信號的成形波形。若在段內抽樣8點,則每個樣點有24個可能值,共有24×8=128個數據。將這128個數據存入查找表中,用連續四個輸入信號進行尋址,就可以不必計算二進制除法,從而提高系統的運算速度。其硬件原理圖如圖2所示。

圖中,SSR是一個四位移位寄存器,數據串行輸入,并行輸出,初始狀態預置為“0000”,每一時鐘信號讀入一位數據,同時串行移位;計數器為8位,每次時鐘從000計數至111;ROM的寬度為7位,存儲27個數據,對應各個樣點的數值,每次時鐘到來時,輸出8個10比特寬的數據[2]。

3 用FPGA實現

由圖2可知,系統主要由移位寄存器、計數器和查找表組成,其中查找表(ROM)對系統運算速度的影響最大。如果直接用寬度為7的查找表進行尋址的話,最長的尋址路徑需要27個系統時鐘,這樣損失太大。所以考慮用尋址寬度小的查找表。假定系統輸入數據的碼速率為4.352Mbps,濾波器的滾降系數α=0.35,則用FPGA可實現成形濾波器。

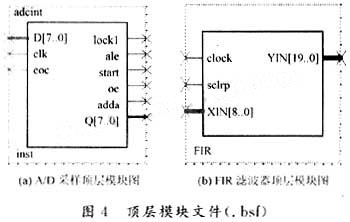

3.1 輸入單元

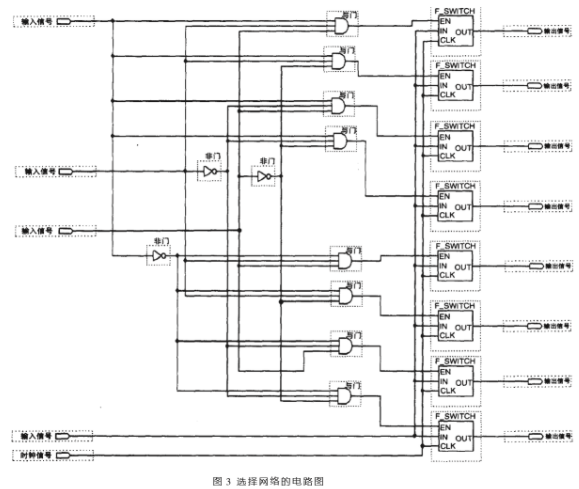

輸入單元由移位寄存器和選擇網絡組成。移位寄存器是由四個帶異步復位端的D觸發器級連而成,數據串行輸入,并行輸出,共用同一個時鐘和異步復位信號,其作用是將輸入數據讀入查找表中。選擇網絡是為了減小查找表的尋址寬度,根據前三個輸入數據的值來選擇對應的查找表。選擇網絡的電路圖如圖3所示。

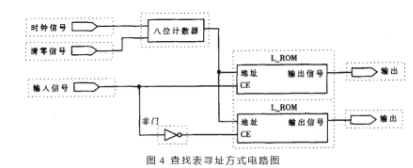

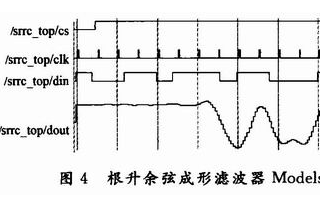

圖中的“F_SWITCH”模塊是一個開關電路,當使能端為高電平時,將輸入端的數據輸出,否則輸出端為高阻態。根據圖3的原理,當前三個輸入信號為100時,選中第5個開關。這樣,只要將第5個開關選通的查找表中數據依次輸出,就可以得到成形信號。這時查找表的尋址寬度為3位,大大節約了尋址時間。查找表尋址方式的電路圖如圖4所示。

在圖4中,計數器的作用是在第四位數據到來時,激勵查找表將其存儲的8個數據依次輸出。L_ROM是尋址寬度為3位的查找表。

3.2 查找表

在圖1中的Δ段內抽樣8點,且濾波器為升余弦滾降濾波器,則有下式成立:

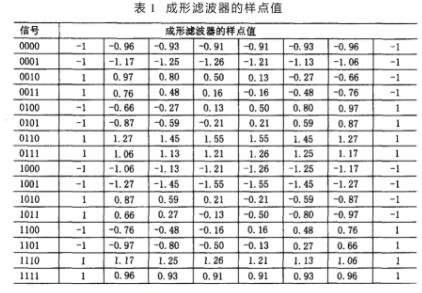

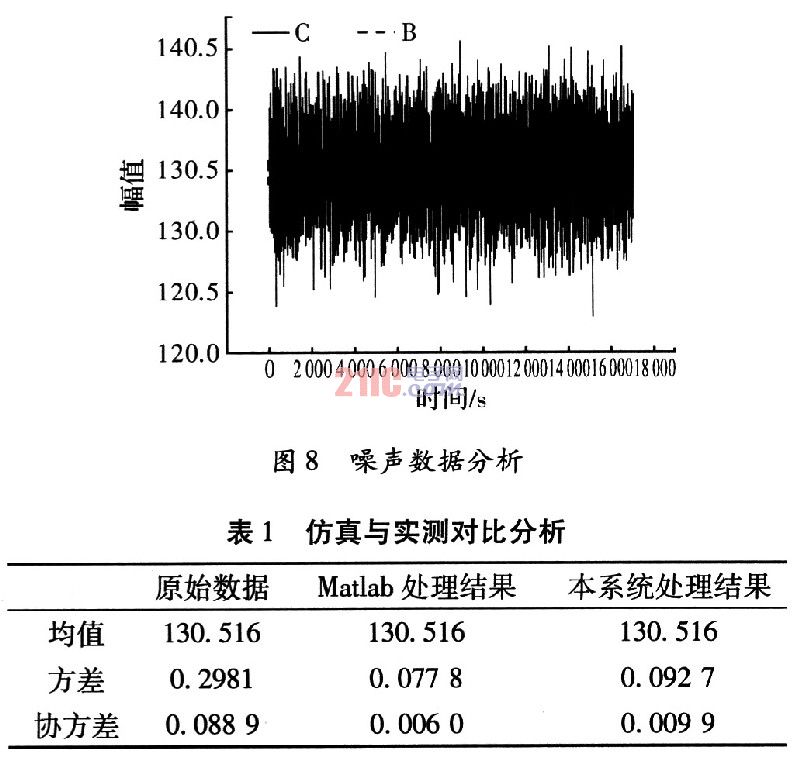

對(7)式進行計算,列出所有可能的樣點值,如表1所示。

將表1中每一行的值轉化為二進制補碼形式,寫入尋址寬度為3位的16個查找表中。此查找表帶有使能端,當使能端為高電平時,輸出端選中數據,否則輸出端為高阻態。這種查找表對于時鐘上升沿的延時最大為14.5ns,而輸入信號的碼元周期為230ns,所以能夠很好地滿足系統的要求。

4 設計結果

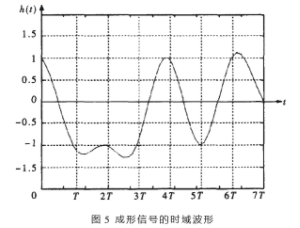

用FLEX10k30A器件實現成形濾波器,將得到的輸出數據轉化為十進制數,并畫出相應的波形。當輸入信號為“1010001”時,成形信號的時域波形如圖5所示。

由圖5可以看出,在各個取樣點碼之間串擾很小,達到了基帶信號成形的目的。

本設計基于分布式算法思想,在時域上對基帶信號直接成形。利用FPGA豐富的查找表資源,提出了一種高效的成形算法。通過FPGA驗證,證明工作正常,性能良好。

責任編輯:gt

電子發燒友App

電子發燒友App

評論