來源:微計算機信息? ? 作者:李鵬程,顏永紅,帥金曉

在通信領域,采用數字化,能夠大大提高傳輸的容量。模擬的話音信號經過脈沖編碼調制,即PCM 處理(包括抽樣、量化以及編碼三個步驟)后,被變換為一個64Kbit/s 速率的數字信號。在北美,數字 復接設備將24 路話音信號即24 路64Kbit/s 速率的數字信號按字節交錯復接成1.544Mbit/s 的高速率信號; 而在歐洲,將30 個獨立64Kbit/s 信道與兩個用于信息控制信道一起同步復接為一個32 個數字信道幀結 構,其幀重復頻率是8000 幀/秒,復接后比特率是2.048Mbit/s。這就是所謂的E1 信號,它是數字通信的 基礎,由E1 復接而成的各高次群形成的數字系列,稱為準同步數字系列(PDH)。雖然同步數字系列 (SDH)正逐步取代PDH,但PDH 設備以低廉,靈活的特點仍然發揮著它的作用。

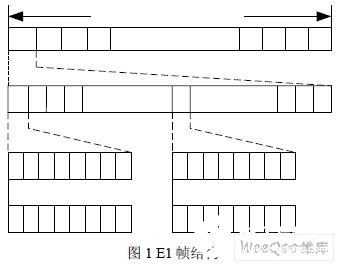

1.幀結構

符合G.704 標準的E1 幀結構如圖1 所示,每基本幀由32 個路時隙(ts0“ts31)組成,分別分配給30 個話音數據流和相應輔助信息。每個路時隙由8bit 碼組成,基本幀幀頻為8K,而每16 基本幀(F0”F15) 構成一個復幀,故每個復幀共由4096 比特組成。

復幀結構中的ts1“ts15,ts17”ts31 分別用來傳30 個64kbit/s 數字信息的數據時隙,而ts0 和ts16 用 來傳各種輔助信號,下面分別介紹。

在一個復幀中,基本幀可以分為兩類:奇幀和偶幀。奇幀和偶幀的區分是通過ts0 的第2bit 來區分的, 奇幀的bit2 為‘1’。偶幀ts0 時隙的bit2“bit8 是用來傳基本幀對準信號FAS 的。G.704 協議規定幀對準信 號FAS 為“0011011”。整個復幀又可以看成由兩個CRC-4 校驗快構成,前8 個基本幀為第一校驗塊,根 據協議要求的方式對其進行CRC-4 校驗,校驗結果共4bit 放在偶幀(F0,F2,F4,F6)ts0 的bit1,同 理對后一校驗塊校驗的結果放在偶幀(F8,F10,F12,F14)ts0 的bit1。同時奇幀的第3bitA1 為對告bit, A1 為‘1’時表示有告警,當收到lof 或者los 時,則將A1 置為‘1’。奇幀ts0 的第1bit 傳復幀定位信號MFAS, 協議規定MFAS 為“001011”。可以看到復幀定位信號為6bit,而一個CRC 復幀中有8 個奇幀,所以協議 規定奇幀(F13,F15)ts0 的第1bit 用來傳誤塊指示比特E0 和E1,當其為‘0’時表示有誤塊。還有奇幀的 第4 至第8bit 為備用bit,不用時應置為‘1’。

基本幀的ts16 用來傳信令信號,既可以傳共路信令,也可以傳隨路信令,同樣當其傳隨路信令時每 16 基本幀的ts16 可構成16 字節的信令復幀。復幀的第一幀ts16 的前四個碼位分配給復幀定位使用,其 定位碼組是“0000”,第6bit 為復幀對告比特,無報警時固定為‘1’。復幀中第2”16 幀的ts16 作為30 個話 路的信令時隙,每路信令占4 個碼位(a,b,c,d),在這里以4 比特為單位實現30 路信令的同步交錯 復用,同時(a,b,c,d)不能為“0000”。但由于目前國內使用的是公共信令,所以一般使用的幀應該 是PCM31 即31 路話路,ts16 傳也為數據,本設計也是針對這種幀結構。

2.系統設計

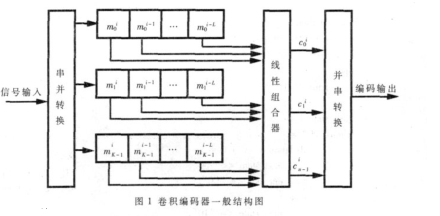

本系統包括e1_framer,e1_deframer,e1pi 三個模塊,e1_framer 模塊對待發送的數據組成符合G.704 協議規定的E1 幀結構;e1_deframer 模塊對接收到的數據進行解幀,即對幀組成部分的進行分離并加以 解釋;e1pi 模塊負責將數據發送到線路側同時從線路上接收數據,這其中包括對數據進行檢測、從數據 中恢復出時鐘(收方向)、進行碼型的轉換(hdb3 編解碼)、對編碼違例進行檢查。

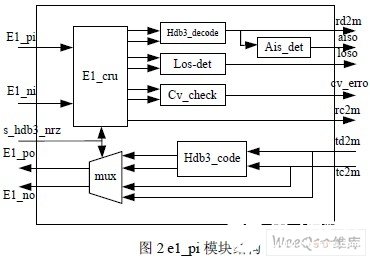

2.1 e1_pi 模塊設計

E1_pi 模塊從功能上來說需要處理收發兩個方向的數據。e1_pi 模塊結構如圖2 所示,在收方向上: E1_cru 模塊從輸入信號中提取時鐘完成定時功能;hdb3_decode 和cv_check 模塊分別完成hdb3 的解碼和 做編碼違例檢查;los_det 和ais_det 模塊對輸入信號進行檢測,如果在兩幀時間內(512bit)收到的‘0’的 個數少于或等于2,則給出全1(ais)告警,反之若收到的‘1’的個數少于或等于2 則給出信號丟失(los) 告警。在發方向則只需就待發信息做hdb3 編碼然后發送到線路上。

E1_cru 模塊是時鐘恢復模塊,設計思想是先用一個高速的時鐘(本設計中為65MHz)去采樣頻率為 2.048 MHz 的E1 信號,得到數據的變化沿;再根據變化沿的位置,由高速時鐘分頻產生2.048 MHz 時鐘。

HDB3碼是一種AMI碼的改進型,不僅克服了當AMI碼中出現連“0” 碼定時提取困難的缺點,而且具 有頻譜能量主要集中在基波頻率以下,占用頻帶較窄的優點。其編碼原則可以簡述為:(1) 當連“0” 碼 的個數不大于3時, “1” 碼變為“+1”、“-1” 交替脈沖;(2) 當代碼序列中出現4個連“0” 碼或超過4 個連“0”碼時,把連“0” 段按4個“0” 分節,即“0000”,并使第4個“0” 碼變為“1” 碼,用V 脈沖(破壞脈沖) 表示,且V脈沖極性與其前一個“1” 脈沖極性相同;(3) 必須使相鄰的破壞點之間有奇數個“1” 碼。 如果原序列中破壞點之間的“1” 碼為偶數,則必須補為奇數,即將破壞節中的第一個“0” 碼變為“1”,用 B脈沖表示。B脈沖極性與其前一個“1” 脈沖極性相反。

假設 hdb3 數據線分別為hdb3p 和hdb3n,從hdb3 編碼規則可以得出hdb3 編碼違例的發生包括在以 下四種情況中:(1)hdb3p 和hdb3n 上同時出現‘1’;(2)將hdb3p 和hdb3n 或操作,得到合路數據,此 數據上出現4 連0 或者大于4 連0 的情況;(3)hdb3p 或者hdb3n 上出現連續‘1’的情況,即數據中出現 連續的正極性/負極性B 脈沖;(4)兩次破壞點之間的B 脈沖個數不為奇數個;若檢測到以上四種情況中 的一種,就會產生編碼違例告警(cv)。

2.2 e1_framer 模塊設計

該模塊為成幀模塊,根據G.704 幀結構標準,在每復幀不同的基本幀ts0 時隙插上開銷比特(包括幀 同步碼,復幀同步碼和對告等),同時需要對整幀做crc-4 校驗,crc-4 產生方法采用 x4 + x + 1 序列(10011), 把校驗結果放在下一幀的相應位置上,然后依次將開銷比特和數據發出。

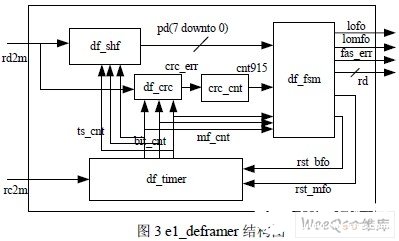

2.3 e1_deframer 模塊設計

e1_deframer 模塊結構如圖3 所示,關于e1 幀的解幀,最重要的是做到基本幀和復幀的同步,只有同 步了才能依次取出各話路信息,另一方面就是如果檢測到傳輸過程中出現了問題需要給出告警指示。 df_timer 是定時模塊為其他模塊提供時隙計數(ts_cnt),基本幀計數(bf_cnt),復幀計數(mf_cnt);df_shf 為移位寄存器,實現數據從串行輸入到并行輸出的作用;df_crc 模塊完成crc_4 校驗并比較結果,出錯則 給出告警,crc_cnt 模塊用來對crc 誤塊進行計數,這是判斷lof 的條件之一。df_fsm 是核心模塊主要做基 幀和復幀同步,然后產生告警。

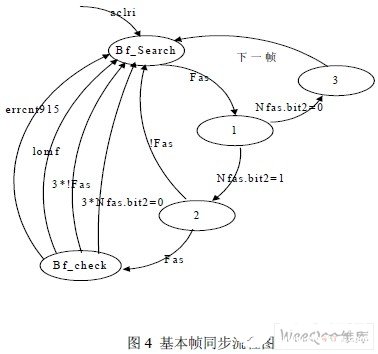

根據G.706 規定的幀同步算法,基本幀同步的過程如圖4 所示,系統復位即進入基本幀搜索狀態, 當收到正確的幀定位信號(FAS=“0011011”)后進入狀態1;在狀態1 檢測下一幀ts0 的bit2,看是否為1, 如果為1 則進入狀態2 反之則進入狀態3 后回到搜索態;在狀態2 時檢查下一幀是否包含正確的FAS, 如果正確則進入同步態,反之回到搜索態。

在基本幀同步的情況下如若出現以下情況,則會出現幀失步,狀態機恢復到搜索態:(1)檢測到三 個偶幀連續的錯誤FAS;(2)奇幀ts0 的bit2 出現三個連續的錯誤;(3)出現復幀丟失(lomf);(4)在 1s 內,即1000 個CRC-4 塊中出現大于等于915 個誤塊。在幀失步狀態后自動回到基本幀搜索狀態,并給 出lof 告警、向下插AIS、發對告A=‘1’、停止CRC-4 性能監視。

對于復幀同步采用的算法是:在8ms 時間(4 個CRC 復幀)內至少出現2 次復幀同步信號“001011” (由奇幀ts0 第1 比特構成),則認定復幀已經同步;而在復幀已同步的情況下連續4 幀沒有找到正確的 MFAS 則認為復幀已經失步,需重新定位。復幀失步需給出lomf 告警。另外對于傳隨路信令的幀結構還 存在ts16 復幀同步問題,由于國內不常采用,在此就不贅述。

3.仿真驗證

本設計采用VHDL 語言進行了RTL 級的描述,用modelsim 對設計進行了仿真,經過FPGA 驗證后, 各功能都得到正確地實現,最后采用FUJITSU 的CS86MN 工藝得到ASIC 實現。

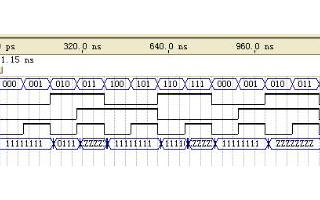

下圖給出了系統部分RTL 級仿真波形。 仿真系統采用的是E1 環回模式,即從E1 接口出來的hdb3 信號又給到接口的輸入,從圖a 中可以反映 出發送前的nrz 信號跟接收后解碼出來的nrz 信號是一樣的,只是時間上有些延遲,由此證明編解碼模塊是 正確的。 圖b 反映的是E1 解幀模塊中基本幀同步的過程,從圖中可以看到基本幀的同步經歷了找到FAS,下一 幀為奇幀,再一幀又找到FAS,這樣三個步驟,這也是符合G.706 標準的。

4.結論

本文描述了E1 幀的基本結構,詳細介紹了E1 基本幀和CRC 復幀同步的算法,采用VHDL語言對符 合G.704 和G.706 標準的成/解幀電路進行了RTL 描述,并最終得到ASIC實現。實驗證明,該系統的時鐘 恢復模塊能達到通信的指標,HDB3 編解碼模塊能有效進行編解碼工作,并能正確檢測到線路上編碼違例的情況,各項告警均符合標準的要求,具有很強的實用價值。同時該電路設計相對于以往的設計來說具有面 積小的特點,在保證質量的前提下節約了成本。

本文作者創新點:1.充分利用了標準中規定的預留比特形成了新的CRC 復幀結構,有利于在通信中發現錯誤; 2.對編解碼模塊進行了優化設計,達到縮小芯片面積的目的。

責任編輯:gt

電子發燒友App

電子發燒友App

評論