作者:譚安菊,陳泉根,許晏

1 APTIX MP3C介紹

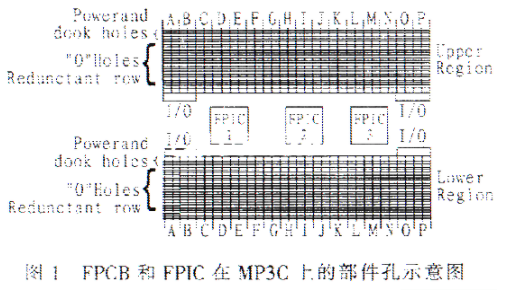

MP3C系統是Aptix公司的產品,是一種價格低、驗證速度快、基于層次化和模塊化的硬件驗證平臺,可以逐步驗證每一個邏輯模塊直到驗證整個系統功能。MP3C硬件中的現場可編程互連電路板(FPCB)和現場可編程互連元件(FPIC)是Aptix公司的專利技術,圖1給出了FPCB和FPIC在MP3C上的部件孔模塊。通過該系統可以40MHz的最快速度調試百萬門級的片上系統;可實時運行軟件作為系統測試矢量;加速仿真與遞歸測試速度和加速完成設計變更;還可隨時利用最新FPGA技術滿足更大的設計規模需要。此外,MP3C也可以對復雜數字系統進行快速驗證,其中包括ASIC、DSP、微控制器、微處理器、RAM和ROM等。MP3C系統比較適合小批量、多品種的生產。

1.1 現場可編程電路板FPCB

MP3C的FPCB是一個22×16、16層的插孔板,根據應用和設計需求,可以把一些外圍器件、接口和多個FPGA等放置在FPCB上,就像面包板一樣,因此非常靈活方便,這些外圍部件再通過FPIC互相連接起來。MP3C FPCB由許多硬件組成。

(1)插孔區(freehole area)

插孔區分為上下二部分,分別用A到P標記,共64列,每列有40個可用插孔,有2560個插孔可以使用,除去16列作為I/O,共有1920個插孔連接到FPIC上。每列有15個FPGA特殊引腳,包括CLK、GDN和VCC等。

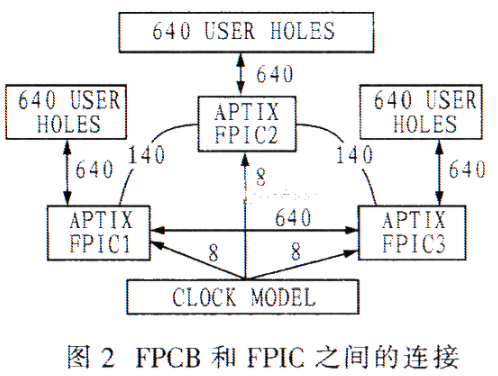

(2)全局互連(global interconnects)

全局連接是FPIC到FPIC的布線源,3個FPIC中每一個都有140根連線連接到其他兩個FPIC,這樣就會提供280個FPIC到FPIC之間的連接,而每一個FPIC的920個布線網中有280個用于FPIC到FPIC之間的連接,其余640個用于連接FPCB上的部件插孔區域,這樣就可以實現部件之間的互連,如圖2所示。

(3)總線(bus)

除了通過FPIC的布線網和全局連接來實現部件之間的互連外,還可以通過MP3C提供的一個總線結構來實現互連。MP3C系統共有4個總線模板連接器,每一個模板連接器有40個總線引腳,而一個FPGA能夠訪問二個總線模板,這就可以獲得80個總線引腳。

(4)I/O信號

I/O信號使得MP3C FPCB可以和其他設備之間進行通信,它們是進出FPCB的信號。

(5)微控制器(microcontroller)

微控制器能為主機系統和MP3C FPCB上的可重配置FPGA之間的通信提供智能接口,微控制器控制FPCB上的能量時序。微控制器的操作系統是存儲在被保護的Flash memory的根塊區,僅需128kByte,這個3.4Mbyte的Flash存儲器主要用來存儲FPIC和FPGA之間的配置數據。

(6)現場可編程互連電路(FPIC)

MP3C含有3塊FPIC,每一塊FPIC有1024個緩沖器,排列成一個32×32矩陣形式,FPIC是可重構的雙向連接,每一個緩沖器之間都可以任意布線,使得插接到FPCB上的外圍設備達到互連,而每一個FPIC之間都有140根連線連接到另二個FPIC中的任意一個,這樣,對于每一個FPIC來說就有280根互連線來實現FPIC與FPIC之間的互連。實際上,FPIC就是一個由軟件控制的可編程接口,它能使用戶對設計的修改變得非常靈活。圖2表明了它們之間的連接關系。

1.2 與MP3C配套的EXPLORER軟件

Aptix Explorer軟件可以提供一個圖形用戶接口GUI(Graphical User Interface),這上GUI能夠生成設計,并對設計進行編輯和調試。通過Explorer軟件可以提供一個直觀有效的接口來對設計做一系列的操作。EXPLORER軟件主要完成整個系統的搭建、FPGA的布局布線和FPCB的編譯。其操作步驟如下:

(1)設置FPCB參數

用來配置FPCB參數,如說明所使用的Fpcb板類型、FPIC序列和說明使用的是那一個FPIC等。

(2)對網表文件(netlist)和設計文件進行設置。

主要輸入網表文件和與設計有關的文件,Explorer軟件支持EDIF和XNF格式的網表文件。

(3)設置Power和Ground

主要是為了說明在部件和針插孔上的Power和Ground引腳是被拉高還是拉低。

(4)設計節點(net)/終端特征

主要設置節點驅動值,其值的范圍為0~100,驅動值的大小決定了節點在FPIC內部的布線順序。驅動值越大就越先布線,因此,可以優先選擇最短的路徑。

(5)在FPCB上放置部件

把數字系統設計中的模塊放到FPCB上。

(6)對設計進行編譯

編譯可以使被仿真的部件之間實現布線連接,還能控制Explorer軟件和FPCB硬件之間的互連。

(7)對設計進行調試

這是幫助下載帶有新信號布線信息的FPCB信息到MP3C硬件上的過程,做完這一步就可以對設計進行驗證、測試和調試。

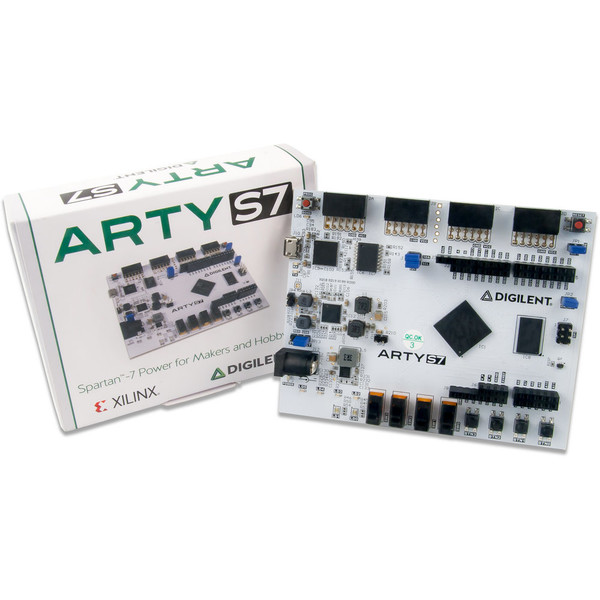

2 Spartan-IIE FPGA

2.1 Spartan-IIE FPGA的組成

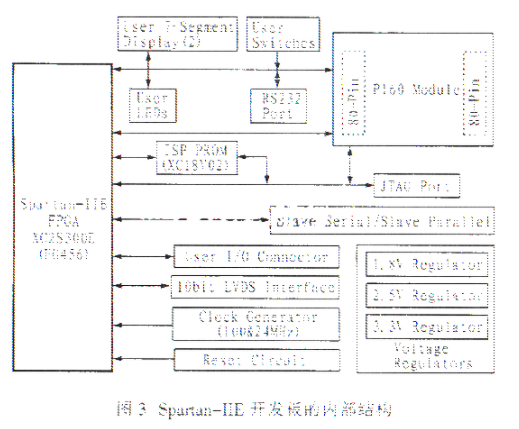

Spartan-IIE FPGA提供了創建成本優化、應用靈活、功能豐富的產品所需要的一切,它的開發過程遠比任何采用ASIC的方案要容易得多(成本也更低)。該系統板主要包括兩個時鐘源、通用I/O、電源供給、P160擴展槽、LVD 10位接收和傳輸端口、開關按鈕、7段顯示器、JTAG端口、RS-232端口、ISP PROM和XC2S300E-5FG456C FPGA等。其中XC2S300E-5FG456C FPGA和ISP PROM是比較重要的部件。圖3是Spartan-IIE開發板內部結構。

2.2 FPGA與PC連接

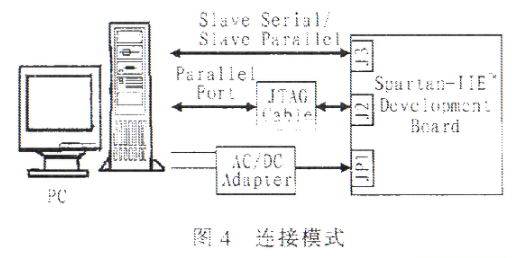

用Spartan-IIE開發板來配置Spartan-IIE FPGA的方法有很多:可以通過其JTAG端口直接配置Spartan-IIE FPGA;通過編程在板XC18V02 ISP PROM進行配置,一旦ISP PROM被編程,通過配置端口就能直接配置Spartan-IIE FPGA;也可以通過在系統板上的從動并行/串行端口來配置FPGA。圖4給出Spartan-IIE開發板支持的Spartan-IIE FPGA配置連接模式。

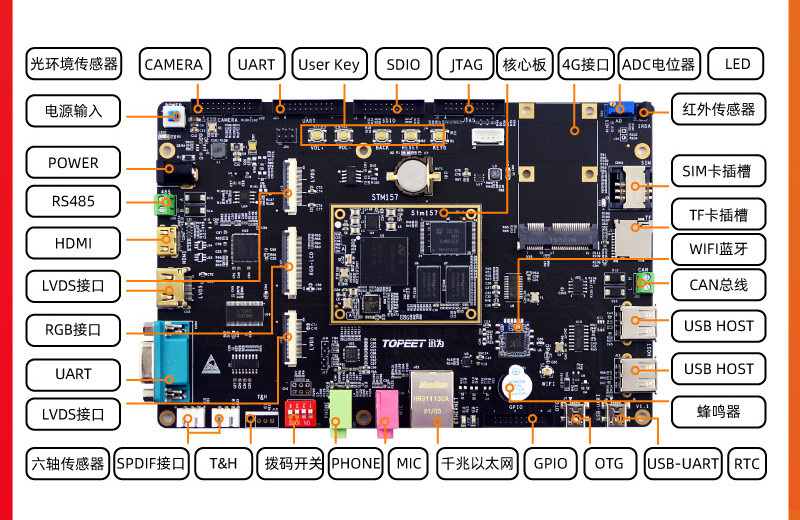

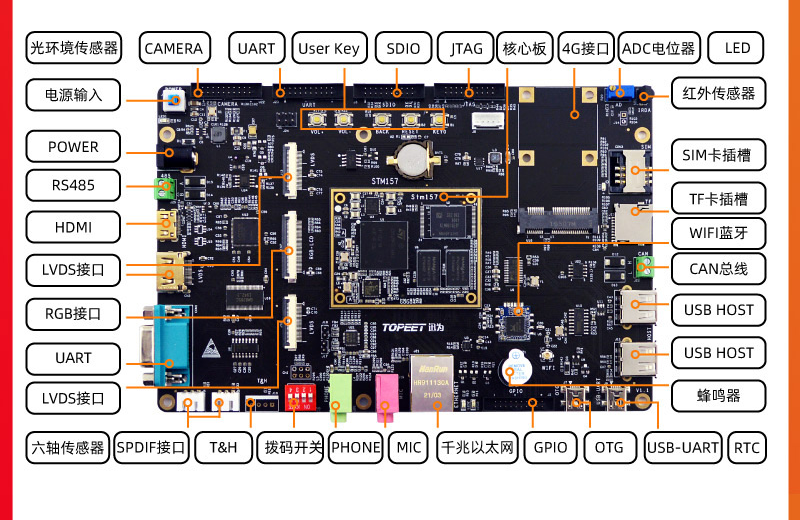

3 驗證系統

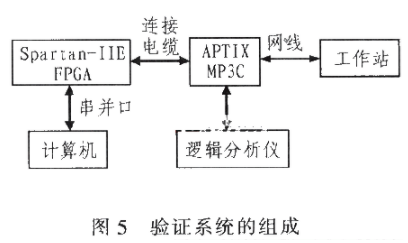

用APTIX MP3C和Spartan-IIE開發板實現對數字系統進行驗證的系統組成如圖5所示。

在這個驗證系統中,把需要驗證的電路放到MP3C FPCB上,Spartan-IIE開發板通過J6或J7通過I/O口連接到FPCB硬件,Spartan-IIE開發板通過串口/并口號計算機相連,工作站通過網線與MP3C通信,也可以把邏輯分析儀連接到MP3C上,實現對系統的在線觀察調試。具體驗證步驟如下:

(1)用51指令對待驗證電路需要的輸入信號和激勵進行編程,程序經編譯后轉換成匯編語言,然后寫入R80515 IP核以便下載到Spartan-IIE FPGA,d Xilinx ISE軟件中對IP核進行仿真和綜合后直接通過并口下載到FPGA中。

(2)用CAD軟件如OrCAD等完成系統頂層原理圖的繪制,需注意其中的接地和電源信號,然后生成網表文件(netlist),把網表文件傳到安裝了EXPLORER軟件的工作站上。

(3)在工作站的EXPLORER軟件上完成整個系統的搭建、MP3C相關參數的設置、輸入網表文件、生成引腳匹配(pinmap)文件和完成MP3C地址設定等,如果在EXPLORER syslib庫中沒有所需要的庫,還要自己建庫,然后就可以進行編譯和調試。

(4)用邏輯分析儀或示波器對某些信號進行觀察,以便進一步查錯和糾錯。這種方法可以很方便地幫助用戶找到出錯的原因。

(5)把驗證電路最后輸出的結果暫存于Spartan-IIE的存儲器中,然后利用串口調試程序在微機上察看結果。目前有很多串口調試程序,如RS-232/RS-485串口通訊程序XP就是一個比較好的程序,如果輸出的結果不正確,就需要檢查錯誤原因,錯誤有可能在硬件方面,也有可能在軟件方面,修改之后回到第一步重新進行驗證。

4 結束語

用這種方法成功實現了對一個復雜FFT電路的驗證。MP3C最具特色的地方就是可編程互連電路板(FPCB)和可編程互連元件(FPIC)的應用,FPIC在FPGA模塊之間提供可編程互連使得在整個設計過程中不用對PCB板進行設計和生產,從而節省了費用;在FPGA上實現了數字系統的設計,允許將FPGA直接安裝到主板上,可以隨著設計FPGA的設計程序重新編制,無需修改其他FPGA,并且可隨時利用最新FPGA技術滿足更大規模的設計,因此大大增加了設計的靈活性和方便性;還可以對系統進行在線實時修改、調試,方便快捷。MP3C的這些特點大大提高了IC驗證的效益。

責任編輯:gt

電子發燒友App

電子發燒友App

評論