在這篇文章里,我們就繼續(xù)來(lái)討論一下 FPGA 的進(jìn)階學(xué)習(xí)路線。和入門(mén)路線不同,我想從入行和職業(yè)發(fā)展的角度,分析一下專業(yè)的 FPGA 開(kāi)發(fā)者需要具備哪些技術(shù)能力,以及如何進(jìn)一步的提升自己這些方面的能力。所以如果你有興趣從事 FPGA 這個(gè)行業(yè)、亦或是正在尋找這方面的工作,或者已經(jīng)入行一段時(shí)間,并且希望明確今后今年的發(fā)展方向,那么這篇文章應(yīng)該會(huì)對(duì)你有所幫助。

和初學(xué)者相比,專業(yè)的 FPGA 工程師需要掌握更多的技能和知識(shí)。對(duì)此我歸納了四個(gè)方面,分別是 FPGA 相關(guān)的高級(jí)技巧、領(lǐng)域相關(guān)的知識(shí)、以及職業(yè)芯片工程師必須具備的硬實(shí)力和軟實(shí)力。我也會(huì)介紹一些書(shū)籍和學(xué)習(xí)資料,希望能對(duì)你的學(xué)習(xí)有所幫助。

RTL 設(shè)計(jì)的高級(jí)開(kāi)發(fā)技巧

掌握基礎(chǔ)知識(shí)之后,就需要繼續(xù)學(xué)習(xí) FPGA 以及數(shù)字電路設(shè)計(jì)相關(guān)的一些高級(jí)技巧。這部分的內(nèi)容有很多,主要包含設(shè)計(jì)、驗(yàn)證、以及一些 FPGA 約束和優(yōu)化的技巧和方法。

這里的設(shè)計(jì)指的是邏輯設(shè)計(jì),也就是使用 RTL 語(yǔ)言實(shí)現(xiàn)一些相對(duì)復(fù)雜一點(diǎn)的模塊或者系統(tǒng),以及在這個(gè)實(shí)現(xiàn)過(guò)程中使用到的一些技巧。在本文也暫時(shí)不討論高層次綜合(HLS)的內(nèi)容,也就是使用 C 語(yǔ)言或者 Python 等高級(jí)語(yǔ)言對(duì) FPGA 進(jìn)行編程。關(guān)于 HLS 的相關(guān)內(nèi)容,可以看我之前的文章《高層次綜合:解鎖 FPGA 廣闊應(yīng)用的最后一塊拼圖》。

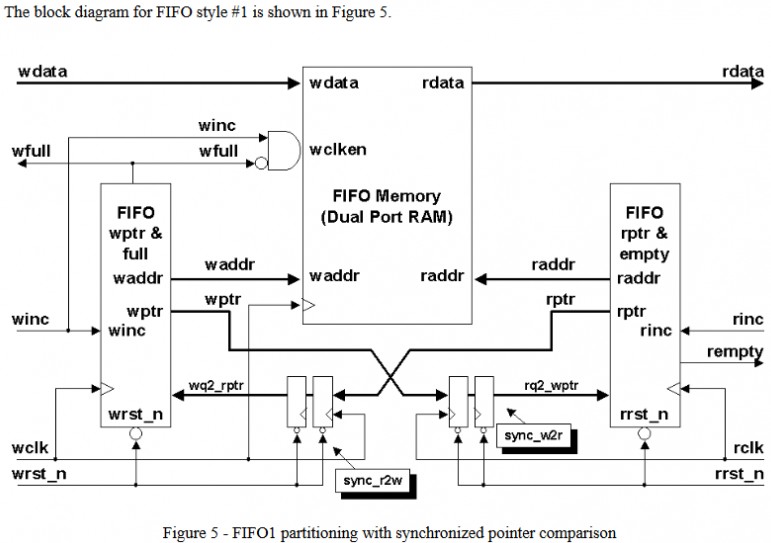

對(duì)于 RTL 設(shè)計(jì),一個(gè)在面試中非常常見(jiàn)的問(wèn)題,就是信號(hào)的跨時(shí)鐘域處理。比如在跨時(shí)鐘域的時(shí)候,怎么處理一位信號(hào)、怎么處理多位不相關(guān)的信號(hào)、怎么處理多位的總線信號(hào)、怎么處理復(fù)位、怎么處理脈沖,從快時(shí)鐘域到慢時(shí)鐘域怎么辦,反過(guò)來(lái)怎么辦等等一大堆。這類問(wèn)題的集大成者就是 FIFO 的設(shè)計(jì),特別是異步 FIFO 的設(shè)計(jì),以及它的一系列變種問(wèn)題。

一種異步 FIFO 的架構(gòu)框圖

關(guān)于跨時(shí)鐘域和 FIFO 的問(wèn)題,推薦讀者朋友們仔細(xì)研究一下 Clifford Cummings 這位大神的幾篇文章,他的文章非常全面的討論了上面說(shuō)的所有問(wèn)題,我也會(huì)把其中的代表作分享到知識(shí)星球里。

?

Clifford Cummings

事實(shí)上,Cummings 作為 Verilog 語(yǔ)言的協(xié)議制定參與者,他還寫(xiě)了很多文章,詳細(xì)探討了各種和數(shù)字電路相關(guān)的問(wèn)題,比如如何寫(xiě)出好的可綜合的 RTL 代碼、狀態(tài)機(jī)怎么寫(xiě)、UVM 和驗(yàn)證相關(guān)的問(wèn)題、還有很多 SystemVerilog 和 Verilog 的細(xì)節(jié)討論。

對(duì)于進(jìn)階的朋友,我覺(jué)得這本書(shū)也有一定借鑒價(jià)值,名叫《FPGA 設(shè)計(jì)實(shí)戰(zhàn)演練 – 高級(jí)技巧篇》。這里面介紹了一些常見(jiàn)的 FPGA 設(shè)計(jì)的技巧和方法,比如前面說(shuō)的時(shí)鐘域處理、還有如何進(jìn)行速度和面積的互換和優(yōu)化等等。

?

值得注意的是,雖然在面試時(shí)常問(wèn)跨時(shí)鐘域處理這類的問(wèn)題,但在實(shí)際的工程項(xiàng)目中是基本不可能讓你從頭寫(xiě)一個(gè)跨時(shí)鐘處理模塊或者 FIFO 的,這些功能早就被封裝成一個(gè)個(gè)現(xiàn)成的模塊了,直接調(diào)用就可以。

但這并不是所謂的“面試造火箭,工作擰螺絲”,前面介紹的這些高級(jí)技巧,更多的是在鍛煉我們的思維方式和設(shè)計(jì)習(xí)慣。只有知道這些,才有可能在面對(duì)一個(gè)實(shí)際問(wèn)題的時(shí)候,知道怎么根據(jù)需求去分析、設(shè)計(jì)和實(shí)現(xiàn),并且得到最優(yōu)化的結(jié)果。

驗(yàn)證的高級(jí)技巧

再來(lái)簡(jiǎn)單說(shuō)一下驗(yàn)證。之前的文章里提到過(guò),驗(yàn)證是一個(gè)非常復(fù)雜的領(lǐng)域。比如在下面的這張 Mentor 的圖片里就顯示,在一個(gè)芯片項(xiàng)目里,平均而言至少會(huì)有超過(guò)一半的時(shí)間花在驗(yàn)證上,有的甚至占 60%~70%。以我自己的經(jīng)驗(yàn)來(lái)說(shuō),這個(gè)比例會(huì)更高。

?

驗(yàn)證之所以復(fù)雜而且耗時(shí),是因?yàn)槲覀儽仨毐M可能多的檢查到所有可能的設(shè)計(jì)功能和狀態(tài)。驗(yàn)證里有一個(gè)“功能覆蓋率”的概念,就是用來(lái)量化這個(gè)過(guò)程的。比如對(duì)于一個(gè)加法電路,a+b=c,我們肯定希望驗(yàn)證到:a 和 b 取所有值的時(shí)候,結(jié)果 c 的值都正確。如果 a 和 b 都是一位十進(jìn)制數(shù),也就是從 0 到 9 之間隨機(jī)選取,那么就有 10x10=100 種可能。但是如果 a 和 b 都是四位十進(jìn)制數(shù),那么就有 10000x10000=1 億種可能,當(dāng)然這還是非常簡(jiǎn)單的情況。

對(duì)于更加復(fù)雜的設(shè)計(jì),比如多個(gè)數(shù)相加、相乘,或者在一些特定領(lǐng)域的邏輯功能、比如 AI 或者網(wǎng)絡(luò)應(yīng)用等等,我們很難通過(guò)仿真驗(yàn)證到所有可能的狀態(tài),甚至不可能覆蓋所有可能的設(shè)計(jì)狀態(tài)。

為了解決這個(gè)問(wèn)題,就需要科學(xué)的制定驗(yàn)證計(jì)劃,同時(shí)使用一些進(jìn)階的驗(yàn)證方法學(xué),比如業(yè)界常用的隨機(jī)約束、UVM 或者形式化方法,來(lái)幫助我們構(gòu)建更加高效的驗(yàn)證環(huán)境。

?

一個(gè)基本的 UVM 驗(yàn)證環(huán)境示意圖

很多芯片公司其實(shí)都有設(shè)計(jì)工程師和驗(yàn)證工程師的分工,但這并不代表做芯片設(shè)計(jì)的人不需要知道驗(yàn)證。事實(shí)上,那些優(yōu)秀的芯片設(shè)計(jì)者同時(shí)也是優(yōu)秀的驗(yàn)證者,他們可能不會(huì)用 UVM 或者形式化驗(yàn)證方法,但肯定會(huì)熟練掌握隨機(jī)約束、參考模型建模、自動(dòng)化測(cè)試、還有斷言等等常用的驗(yàn)證技術(shù),這也應(yīng)該是我們應(yīng)該努力的方向。

FPGA 的約束和優(yōu)化設(shè)計(jì)

除了設(shè)計(jì)和驗(yàn)證之外,F(xiàn)PGA 相關(guān)的優(yōu)化和約束也是進(jìn)階學(xué)習(xí)的重要內(nèi)容。這里主要包括對(duì)時(shí)序、面積、功耗的約束和優(yōu)化。比如,存在多個(gè)時(shí)鐘的時(shí)候怎么寫(xiě)時(shí)序約束,怎么進(jìn)行時(shí)序分析,怎么劃分固定的設(shè)計(jì)區(qū)域,怎么預(yù)估設(shè)計(jì)的功耗等等。這個(gè)過(guò)程可能會(huì)貫穿整個(gè) FPGA 項(xiàng)目的開(kāi)發(fā)周期,而且一些常見(jiàn)的 ASIC 約束方法并不一定會(huì)適用于 FPGA 設(shè)計(jì)。

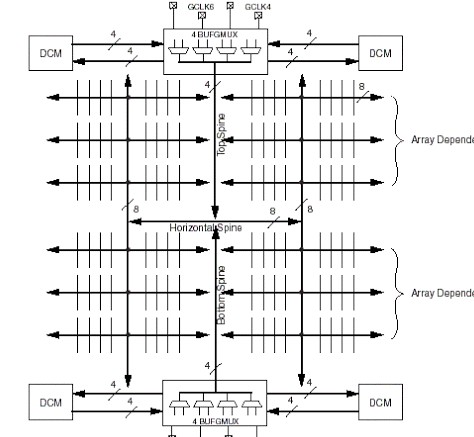

拿 FPGA 低功耗設(shè)計(jì)舉例,門(mén)控時(shí)鐘就不一定適合于 FPGA。這是由于 FPGA 里的時(shí)鐘網(wǎng)絡(luò)是固定的,因此只能關(guān)閉固定的時(shí)鐘樹(shù)或者分支。如果需要做門(mén)控時(shí)鐘,就必須控制某些特定的 clock buffer,且要同時(shí)確定這些 clock buffer 可以被邏輯控制。更重要的是,我們還需要確保這個(gè)時(shí)鐘驅(qū)動(dòng)的邏輯都位于這個(gè)時(shí)鐘樹(shù)的“勢(shì)力范圍”之內(nèi),這就需要在布局布線時(shí)設(shè)置想要的位置約束。由此可見(jiàn),門(mén)控時(shí)鐘這個(gè)在 ASIC 設(shè)計(jì)里常見(jiàn)的低功耗設(shè)計(jì)方法,在 FPGA 設(shè)計(jì)里是困難且繁瑣的。

FPGA 時(shí)鐘樹(shù)示意圖

領(lǐng)域相關(guān)的知識(shí)

進(jìn)階學(xué)習(xí)路線的第二部分內(nèi)容,就是領(lǐng)域?qū)S玫闹R(shí),也就是 Domain Specific Knowledge。我們之所以要學(xué)習(xí)這部分內(nèi)容,是因?yàn)?FPGA 并不是單獨(dú)存在的,它需要被應(yīng)用在某些具體的領(lǐng)域和場(chǎng)景里。

比如,F(xiàn)PGA 目前的一個(gè)很火的應(yīng)用領(lǐng)域就是數(shù)據(jù)中心里的智能網(wǎng)卡。關(guān)于智能網(wǎng)卡的內(nèi)容在之前已經(jīng)說(shuō)過(guò)很多了,包括微軟、阿里、騰訊、京東、字節(jié)等等很多互聯(lián)網(wǎng)公司都在布局這方面的技術(shù)。智能網(wǎng)卡的本質(zhì),就是使用把一些原本在 CPU 里運(yùn)行的應(yīng)用,卸載到 FPGA 里執(zhí)行,這可以是網(wǎng)絡(luò)協(xié)議棧、一些虛擬化的功能、或者是和 AI 相關(guān)的功能等等。

?

這里面就涉及到了很多領(lǐng)域?qū)S玫闹R(shí),比如計(jì)算機(jī)網(wǎng)絡(luò)、網(wǎng)絡(luò)功能虛擬化 NFV、軟件定義網(wǎng)絡(luò) SDN,還有一些其他的虛擬化技術(shù)比如 Virtio、OVS 等。

此外,領(lǐng)域相關(guān)的知識(shí)還包括各種高速接口協(xié)議和總線相關(guān)的內(nèi)容。比如 PCIe、DDR、HBM、以太網(wǎng)、收發(fā)器等,還有各種各樣的總線協(xié)議。這些和 FPGA 也有非常密切的關(guān)系,在實(shí)際的求職應(yīng)聘時(shí)也是重要的加分項(xiàng)。

在學(xué)習(xí)這些內(nèi)容的時(shí)候,我個(gè)人建議還是結(jié)合目標(biāo)職位或者項(xiàng)目的需求來(lái),有目的的去學(xué)習(xí),而不是想著一上來(lái)就一口吃個(gè)胖子。比如我就對(duì)使用 FPGA 進(jìn)行高清視頻處理相關(guān)的內(nèi)容不太了解,因?yàn)槲也⒉蛔鲞@個(gè)方向,但我大概知道怎么構(gòu)建知識(shí)圖譜,并由此去一步步學(xué)習(xí),這樣其實(shí)就可以了。

職業(yè)技能相關(guān)的能力

FPGA 進(jìn)階學(xué)習(xí)路線的第三點(diǎn),就是職業(yè)工程師需要具備的一些硬實(shí)力。比如,企業(yè)里幾乎全部的開(kāi)發(fā)環(huán)境都是在 Linux 系統(tǒng)里完成的,而且大部分時(shí)候沒(méi)有圖形界面。所以除了常用的那些 EDA 工具之外,還特別需要我們熟練掌握 Linux 的一些基本命令。此外還應(yīng)該掌握至少一種腳本語(yǔ)言,比如 Tcl、Perl、Makefile、Python 等等。這能極大的提升我們的工作效率,這也是芯片工程師必備的技能。

此外,作為 FPGA 工程師,硬件調(diào)試的能力也是不可或缺的。一個(gè)在職業(yè)工程師日常工作中非常常見(jiàn)的場(chǎng)景,就是使用和調(diào)試各種各樣的 FPGA 板卡,比如拿來(lái)一個(gè)全新的板卡,從頭開(kāi)始用它進(jìn)行開(kāi)發(fā)。

這就要求我們會(huì)看板卡的原理圖、知道怎么寫(xiě)各種約束,怎么使用板子上的各種資源等等。此外,當(dāng)設(shè)計(jì)出錯(cuò)時(shí),怎么去進(jìn)行硬件調(diào)試,還有怎么設(shè)計(jì)一些有用的邏輯功能來(lái)方便硬件測(cè)試,比如各種狀態(tài)寄存器等等。那么對(duì)于某些專業(yè)領(lǐng)域,比如在網(wǎng)絡(luò)領(lǐng)域,可能還需要知道怎么進(jìn)行流量測(cè)試,比如 DPDK 的使用、配置,還有一些測(cè)試儀器的使用、一些常見(jiàn)的網(wǎng)絡(luò)分析工具(如 wireshark)的使用等等。

總體來(lái)說(shuō),這些職業(yè)工程師需要具備的硬實(shí)力,可能在上學(xué)期間不一定都能接觸到。這就需要我們?cè)诠ぷ髦胁粩鄬?shí)踐和總結(jié),才能把這些技能一點(diǎn)一點(diǎn)積累起來(lái)。

職業(yè)人士的軟實(shí)力

除了硬實(shí)力之外,軟實(shí)力的培養(yǎng)也至關(guān)重要,這包括溝通、時(shí)間管理、團(tuán)隊(duì)協(xié)作、領(lǐng)導(dǎo)力,還有不斷學(xué)習(xí)的能力等等。

不管是芯片還是其他工程領(lǐng)域,絕大部分項(xiàng)目都是由很多團(tuán)隊(duì)一起協(xié)作完成的,因此如何與不同團(tuán)隊(duì)的成員溝通項(xiàng)目?jī)?nèi)容,如何制定項(xiàng)目規(guī)劃、把握項(xiàng)目進(jìn)度,以及遇到難題應(yīng)該如何著手去解決,都是職業(yè)工程師幾乎天天遇到的問(wèn)題。

事實(shí)上,不管你從事或者打算從事什么職業(yè),我們都應(yīng)該從現(xiàn)在開(kāi)始培養(yǎng)自己的各種軟實(shí)力。比如多與人溝通,積極參加各種活動(dòng),或者像我在之前的文章《分享是程序員的必備素質(zhì)》里提到的,不斷分享自己學(xué)習(xí)和工作中的各種心得體會(huì)。這些肯定都會(huì)對(duì)我們今后的職業(yè)生涯大有幫助。

小結(jié)

在今天的文章里,我們梳理了一下作為一個(gè)職業(yè)的 FPGA 工程師需要具備哪些能力,一共有四個(gè)部分,分別是和 FPGA 相關(guān)的高級(jí)開(kāi)發(fā)技巧、各種領(lǐng)域?qū)S玫闹R(shí)、還有芯片工程師必備的硬實(shí)力和軟實(shí)力。針對(duì)每部分內(nèi)容,我們也都深入的了解了如何去學(xué)習(xí)和提升自己的這些能力。

事實(shí)上,這里提到的各種專業(yè)內(nèi)容只是我們?nèi)粘9ぷ髦械囊徊糠郑鼈兛赡軙?huì)隨著技術(shù)的發(fā)展而不斷變化,甚至被各種新技術(shù)所取代。所以最重要的是,培養(yǎng)自己不斷學(xué)習(xí)的能力,不斷嘗試新技術(shù)、新工具,努力跳出自己的舒適圈,只有這樣才能一直保持自己的競(jìng)爭(zhēng)力,從而實(shí)現(xiàn)更好的人生價(jià)值。

? ? ? ?責(zé)任編輯:pj

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論