隨著可編程邏輯器件的發(fā)展,F(xiàn)PGA的應(yīng)用已經(jīng)越來(lái)越廣泛,且用可編程邏輯器件代替?zhèn)鹘y(tǒng)的普通集成電路已成為一種發(fā)展的趨勢(shì)。可編程邏輯器件FPGA以其高集成度、高速度、開(kāi)發(fā)周期短、穩(wěn)定性好而受到了人們

2021-01-04 10:36:00 2066

2066

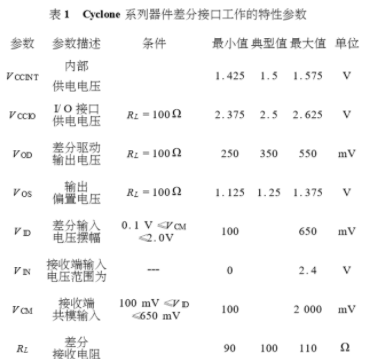

本章節(jié)介紹了 Cyclone? IV 器件所支持的 I/O 與高速 I/O 的性能和特性。Cyclone IV 器件的 I/O 功能是由許多低成本應(yīng)用中的多樣化 I/O 標(biāo)準(zhǔn)所驅(qū)動(dòng)的,大幅度提高了

2017-11-14 10:10:54

電子設(shè)備、通訊、系統(tǒng)控制、醫(yī)療和軍事等領(lǐng)域所使用的關(guān)鍵應(yīng)用中,要求能夠做到以下兩點(diǎn):■ 確認(rèn)存儲(chǔ)在 FPGA 器件中的配置數(shù)據(jù)的準(zhǔn)確性■ 使系統(tǒng)能夠警惕配置錯(cuò)誤的發(fā)生在 Cyclone IV 器件中使用 CRC 錯(cuò)誤檢測(cè)功能不會(huì)對(duì)布線及性能產(chǎn)生影響。

2017-11-14 10:49:16

這個(gè)章節(jié)包含了定義邏輯單元 (LE) 和邏輯陣列模塊 (LAB) 的特性。具體信息體現(xiàn)在 LE如何運(yùn)作,LAB 如何容納 LE 組,以及 LAB 接口如何與 Cyclone? IV 器件中的其他模塊連接。

2017-11-13 11:25:48

本章對(duì) Cyclone IV 器件的外部電源要求、熱插拔規(guī)范、上電復(fù)位 (POR) 要求以及它們的實(shí)現(xiàn)作了相關(guān)的介紹。

2017-11-14 10:51:59

E— 最低的功耗,通過(guò)最低的成本實(shí)現(xiàn)較高的功能性■ Cyclone IV GX— 最低的功耗,集成了 3.125 Gbps 收發(fā)器的最低成本的 FPGA1 Cyclone IV E 器件可以在 1.0

2017-11-13 11:22:50

(AC JTAG) 僅被Cyclone IV GX 器件中的高速串行接口 (HSSI) 收發(fā)器支持。IEEE Std.1149.6 用于使能 AC 耦合的發(fā)送器與接收器之間的板級(jí)連接檢查。

2017-11-14 10:50:26

降低設(shè)備復(fù)雜性、強(qiáng)化易配置性、加快產(chǎn)品上市速度的要求使得可編程邏輯技術(shù)在更多的應(yīng)用領(lǐng)域中得到進(jìn)一步地?cái)U(kuò)展和滲透。最近業(yè)界發(fā)生的兩個(gè)事件可充分地證明這一點(diǎn)。 美國(guó)國(guó)家儀器公司(NI)在其最新推出

2019-07-15 08:15:30

什么是可編程邏輯? 在數(shù)字電子系統(tǒng)領(lǐng)域,存在三種基本的器件類型:存儲(chǔ)器、微處理器和邏輯器件。存儲(chǔ)器用來(lái)存儲(chǔ)隨機(jī)信息,如數(shù)據(jù)表或數(shù)據(jù)庫(kù)的內(nèi)容。微處理器執(zhí)行軟件指令來(lái)完成范圍廣泛的任務(wù),如運(yùn)行字處理

2019-07-10 08:16:49

可編程邏輯芯片 FPGA CYCLONE IV 10K LE 144TQFP 中速度級(jí)數(shù):為8代表什么意思?

2012-09-13 21:18:05

可編程邏輯芯片 FPGA 中的CYCLONE IV系列的芯片·主要指標(biāo)中的速度級(jí)數(shù)代表什么意思?

2012-09-13 21:29:48

可編程邏輯器件到底是干什么用的呢,簡(jiǎn)單的說(shuō),就是通過(guò)重新寫程序,重新注入到這個(gè)器件中達(dá)到實(shí)現(xiàn)其它的功能。最常見(jiàn)的當(dāng)屬電腦了。電腦本身除了加法,減法和簡(jiǎn)單的邏輯運(yùn)算四種。比如要是想實(shí)現(xiàn)一個(gè)功能讓電腦

2014-04-15 10:02:54

可編程邏輯器件FPGA/CPLD結(jié)構(gòu)與應(yīng)用.ppt

2017-01-21 20:34:49

CPLD唱EPLD 改進(jìn)型器件。現(xiàn)在,由于 FPGA 技術(shù)的快速發(fā)展,FPGA 產(chǎn)品在邏輯密度、性能和功能上有了極大的提高,同時(shí)器件成本也大幅下降,可編程邏輯技術(shù)已經(jīng)能與 ASIC(專用集成電路

2019-02-26 10:08:08

FPGA先從讀入編程數(shù)據(jù)進(jìn)行初始化,然后才開(kāi)始正常工作。基于反熔絲技術(shù)的FPGA則只能編程一次,此類FPGA比較適合定型產(chǎn)品和大批量應(yīng)用。可編程邏輯器件是組成數(shù)字邏輯系統(tǒng)的理想器件,設(shè)計(jì)時(shí)只需要通過(guò)

2021-07-13 08:00:00

可編程邏輯器件實(shí)驗(yàn)指導(dǎo)書

2009-09-16 15:11:22

可編程邏輯器件是如何發(fā)展的?

2021-04-29 06:23:22

器件有一個(gè)整體的了解。(特權(quán)同學(xué),版權(quán)所有)Cyclone IIIFPGA系列前所未有的同時(shí)實(shí)現(xiàn)了低功耗、高性能和低成本,大大提高了產(chǎn)品競(jìng)爭(zhēng)力。其特性以及Cyclone III FPGA體系結(jié)構(gòu)為用戶

2015-04-17 12:05:21

部分。現(xiàn)場(chǎng)可編程門陣列(FPGA)是可編程器件,與傳統(tǒng)邏輯電路和門陣列(如PAL,GAL及CPLD器件)相比,F(xiàn)PGA具有不同的結(jié)構(gòu)。FPGA利用小型查找表(16×1RAM)來(lái)實(shí)現(xiàn)組合邏輯,每個(gè)查找表

2023-02-23 15:24:55

PLD可編程邏輯器件 英文全稱為:programmable logic device 即 PLD。PLD是做為一種通用集成電路產(chǎn)生的,他的邏輯功能按照用戶對(duì)器件編程來(lái)確定。一般的PLD的集成度很高

2021-07-22 09:05:48

可編程邏輯器件的電源、接地和去耦網(wǎng)絡(luò)設(shè)計(jì)8.7 LVDS接口設(shè)計(jì)8.8 CPLD器件設(shè)計(jì)中需注意的一些問(wèn)題8.9 本章小結(jié)第9章 Virtex-Ⅱ Pro MGT高速串行I/O設(shè)計(jì)9.1 概述9.2

2012-02-27 14:43:30

` 本帖最后由 eehome 于 2013-1-5 09:47 編輯

XILINX可編程邏輯器件設(shè)計(jì)技術(shù)詳解第1章 可編程邏輯器件設(shè)計(jì)流程導(dǎo)論11.1 設(shè)計(jì)流程概述11.2 設(shè)計(jì)輸入和綜合

2012-04-24 09:18:46

專家都是如何使用超低功耗的復(fù)雜可編程邏輯器件(CPLD)的?從他們的嵌入式設(shè)計(jì)中的I/O子系統(tǒng)中學(xué)到了什么?

2021-04-08 06:31:20

為什么復(fù)雜可編程邏輯器件需要重新上電才能工作?如何去解決AVR單片機(jī)上電復(fù)位不可靠的問(wèn)題?

2021-07-07 06:53:08

可編程邏輯器件市場(chǎng)約為35億美元。固定邏輯器件市場(chǎng)約為120億美元。然而,近年來(lái),PLD銷售額的增長(zhǎng)速度已經(jīng)超過(guò)基于傳統(tǒng)門陣列技術(shù)的固定邏輯器件的銷售增長(zhǎng)速度。而且,高性能FPGA現(xiàn)在已開(kāi)始從采用最先

2009-05-29 11:36:21

了16個(gè)邏輯單元(Logic elements,簡(jiǎn)稱LEs),LEs是能夠實(shí)現(xiàn)用戶邏輯功能的最小單位,后面我們還會(huì)詳細(xì)介紹這個(gè)LEs的內(nèi)部結(jié)構(gòu)。其實(shí)這顆Cyclone IV器件的邏輯結(jié)構(gòu)在Altera

2017-11-21 22:28:24

摘要:介紹了可編程邏輯器件在數(shù)字信號(hào)處理系統(tǒng)中的應(yīng)用。并運(yùn)用VHDL語(yǔ)言對(duì)采用Lattice公司的ispLSI1032E可編程邏輯器件所構(gòu)成的乘法器的結(jié)構(gòu)、原理及各位加法器的VHDL作了詳細(xì)的描述

2019-06-28 06:14:11

傳輸,因而只能做需求數(shù)據(jù)較少的測(cè)向工作,并不能做實(shí)時(shí)波束形成。為了克服這些困難,這里將測(cè)向數(shù)據(jù)和波束形成數(shù)據(jù)分開(kāi)進(jìn)行傳輸,采用LVDS技術(shù)解決多通道高速數(shù)據(jù)傳輸,選擇內(nèi)置高性能DSP內(nèi)核的高密度FPGA并行實(shí)現(xiàn)波束形成中的大量復(fù)乘運(yùn)算。

2020-11-25 06:49:42

復(fù)雜可編程邏輯器件—FPGA技術(shù)在近幾年的電子設(shè)計(jì)中應(yīng)用越來(lái)越廣泛。FPGA具有的硬件邏輯可編程性、大容量、高速、內(nèi)嵌存儲(chǔ)陣列等特點(diǎn)使其特別適合于高速數(shù)據(jù)采集、復(fù)雜控制邏輯、精確時(shí)序邏輯等場(chǎng)合的應(yīng)用。而應(yīng)用FPGA中的存儲(chǔ)功能目前還是一個(gè)較新的技術(shù)。

2019-10-12 07:32:24

所示。 隨著可編程邏輯器件的發(fā)展,Altera公司研發(fā)了可以嵌入軟 CPU核的 Cyclone系列和 Stratix系列的 FPGA芯片。嵌入式軟核與普通硬核的昀大差別在于它的可裁減性,設(shè)計(jì)者可根據(jù)

2019-07-24 06:31:45

介紹了一種基于復(fù)雜可編程邏輯器件(CPLD)的120MHZ高速A/D采集卡的設(shè)計(jì)方法。給出了這種采集卡的硬件原理電路和主要的軟件設(shè)計(jì)思路。采用該設(shè)計(jì)方法設(shè)計(jì)的數(shù)據(jù)采集卡具有包括負(fù)延遲觸發(fā)等多種觸發(fā)方式,具有體積小,工作可靠,控制簡(jiǎn)單等特點(diǎn)。

2011-03-05 12:52:28

介紹了利用現(xiàn)場(chǎng)可編程邏輯門陣列FPGA實(shí)現(xiàn)直接數(shù)字頻率合成(DDS)的原理、電路結(jié)構(gòu)和優(yōu)化方法。重點(diǎn)介紹了DDS技術(shù)在FPGA中的實(shí)現(xiàn)方法,給出了采用ALTERA公司的ACEX系列FPGA芯片EP1K30TC進(jìn)行直接數(shù)字頻率合成的VHDL源程序。

2021-04-30 06:29:00

CLC5958的內(nèi)部結(jié)構(gòu)及基本特性CLC5958應(yīng)用的注意事項(xiàng)有哪些采用可編程邏輯器件和A/D轉(zhuǎn)換器組成的高速數(shù)據(jù)采集卡的設(shè)計(jì)方案

2021-04-15 06:50:05

本文將詳細(xì)論述采用CPLD技術(shù)來(lái)實(shí)現(xiàn)120MHz高速A/D采集卡的設(shè)計(jì)方法,該采集卡具有包括負(fù)延遲觸發(fā)在內(nèi)的多種觸發(fā)方式,采用CPLD復(fù)雜可編程邏輯器件(又稱FPGA)EPM7128SQC100-7和AD公司的高速模數(shù)轉(zhuǎn)換器(A/D)AD9054BST-135來(lái)實(shí)現(xiàn)。

2021-04-30 06:27:01

可編程邏輯器件有哪些種類?可編程邏輯器件在高準(zhǔn)確度A/D轉(zhuǎn)換器中的應(yīng)用

2021-04-22 06:21:25

怎么實(shí)現(xiàn)基于可編程邏輯器件的數(shù)字電路設(shè)計(jì)?

2021-05-06 08:36:18

本文以乘法器的設(shè)計(jì)為例,來(lái)說(shuō)明采用可編程邏輯器件設(shè)計(jì)數(shù)字系統(tǒng)的方法。

2021-04-29 06:22:10

數(shù)字電子技術(shù)-- 可編程邏輯器件[hide][/hide]

2017-03-05 10:51:17

數(shù)字電子技術(shù)--可編程邏輯器件[hide][/hide]

2017-05-01 22:29:19

本文提出一種利用復(fù)雜可編程邏輯器件(Complex Programmable Logic Device,CPLD)設(shè)計(jì)技術(shù)[3]實(shí)現(xiàn)專用鍵盤接口芯片的方案。

2021-04-15 06:55:36

為實(shí)現(xiàn)多點(diǎn)校正法,筆者設(shè)計(jì)了基于復(fù)雜可編程邏輯器件的硬件校正實(shí)現(xiàn)方案,實(shí)驗(yàn)表明,該校正系統(tǒng)可將圖像傳感器CL512J的非均勻度由40%校正到2%. 因此,多點(diǎn)校正法及其實(shí)現(xiàn)系統(tǒng)能在不提高制造工藝和進(jìn)一步研究光敏元結(jié)構(gòu)的基礎(chǔ)上,有效地降低圖像傳感器的非均勻性,獲得較為理想的圖像質(zhì)量。

2021-04-28 06:05:34

隨著智能制造的蓬勃發(fā)展進(jìn)一步推動(dòng)了智能工業(yè)的崛起。制造商及工程師在進(jìn)行智能化系統(tǒng)設(shè)計(jì)時(shí),將面臨著不斷提高性能、突出優(yōu)勢(shì)、降低成本、同時(shí)實(shí)現(xiàn)功能安全等諸多挑戰(zhàn),但同時(shí)也給全球可編程邏輯器件廠商帶來(lái)

2013-04-12 09:57:41

如何選擇PLC可編程邏輯器件?

2021-04-27 06:39:03

可編程邏輯器件設(shè)計(jì)

(264頁(yè),nlc格式)

2006-03-25 16:41:01 66

66 max7000系列器件可編程邏輯的技術(shù)規(guī)范

2007-11-14 12:49:29 17

17 本文介紹了北京A風(fēng)中天科技發(fā)展有限公司開(kāi)發(fā)提供的CYCLONE C64x圖像處理、CYCLONE C6205 PCI-LVDS高速數(shù)據(jù)傳輸和CYCLONE LF2407電機(jī)控制解決方案,以及TI全系歹JDSP仿真開(kāi)發(fā)工具。

2009-05-09 10:56:24 29

29 一種基于可編程邏輯器件的等精度頻率計(jì)的設(shè)計(jì)原理、硬件組成和軟件實(shí)現(xiàn)關(guān)鍵詞:可編程邏輯器等精度 頻率 周期 脈寬 占空比

2009-09-07 16:05:34 31

31 介紹了PLD(可編程邏輯器件) 的技術(shù)特點(diǎn),并針對(duì)當(dāng)前DSP 系統(tǒng)中串并轉(zhuǎn)換器選擇調(diào)試?yán)щy的特點(diǎn),提出利用PLD 開(kāi)發(fā)DSP 系統(tǒng)中高速串行到高速并行的數(shù)據(jù)轉(zhuǎn)換傳輸技術(shù),以簡(jiǎn)化電路及

2009-12-04 11:49:04 17

17 可編程邏輯器件資料:Cyclone Device Handbook, Volume 1Stratix III Device Handbook, Volume 1MAX II Device Handbook

2009-12-08 16:32:17 0

0 基于復(fù)雜可編程邏輯器件(CPLD)的120MHZ高速AD采集卡的設(shè)計(jì):介紹了一種基于復(fù)雜可編程邏輯器件高速AD采集卡的設(shè)計(jì)方法,給出了這種采集卡的硬件原理電路和主要的軟件設(shè)計(jì)思路,采用

2010-01-17 09:37:46 39

39 可編程邏輯器件基礎(chǔ)及應(yīng)用實(shí)驗(yàn)指導(dǎo)書

《可編程邏輯器件基礎(chǔ)及應(yīng)用》是一門側(cè)重掌握可編程邏輯器件的基本結(jié)構(gòu)和原理的課程。重點(diǎn)是使學(xué)生掌握基于可編程

2010-03-24 14:22:46 29

29 本文介紹了Cyclone系列基于查找表(LUT)技術(shù)、SRAM工藝的FPGA配置方式,完成了用USB控制芯片作為微處理器對(duì)FPGA的進(jìn)行被動(dòng)態(tài)配置。

2010-08-06 15:10:16 48

48 本文以高性能可編程邏輯器件,高精度、低抖動(dòng)、低畸變可編程時(shí)鐘芯片為核心器件,采用PCI總線技術(shù),設(shè)計(jì)了高速可編程遙感衛(wèi)星數(shù)據(jù)模擬源,在使用windows2000 的高性能服務(wù)器上

2010-08-09 15:27:03 11

11 為解決目前高速信號(hào)處理中的數(shù)據(jù)傳輸速度瓶頸以及傳輸距離的問(wèn)題,設(shè)計(jì)并實(shí)現(xiàn)了一種基于FPGA 的高速數(shù)據(jù)傳輸系統(tǒng),本系統(tǒng)借助Altera Cyclone III FPGA 的LVDS I/O 通道產(chǎn)生LVDS 信號(hào),穩(wěn)

2010-11-02 15:27:43 42

42 第三十二講 可編程邏輯器件及應(yīng)用第10章 可編程邏輯器件及應(yīng)用10.1 概述10.1.1 PLD器件的基本結(jié)構(gòu)10.1.2 PLD器件的分類10.1.3 PLD器件的優(yōu)點(diǎn)一、

2009-03-30 16:37:51 1333

1333

什么是PLD(可編程邏輯器件)

PLD是可編程邏輯器件(Programable Logic Device)的簡(jiǎn)稱,F(xiàn)PGA是現(xiàn)場(chǎng)可編程門陣列(Field Programable Gate Array)

2009-06-20 10:32:32 14283

14283

基于可編程邏輯器件的數(shù)字電路設(shè)計(jì)

0 引 言

可編程邏輯器件PLD(Programmable Logic De-vice)是一種數(shù)字電路,它可以由用戶來(lái)進(jìn)行編程和進(jìn)行配置,利用它可以

2009-11-16 10:46:41 1473

1473

以Cyclone FPGA 器件為核心,設(shè)計(jì)數(shù)據(jù)交換機(jī). 描述了Cyclone 器件中LVDS 接口、鎖相環(huán)PLL 、片內(nèi)M4KRAM模塊、芯片配置的應(yīng)用方法和技巧,給出了軟件設(shè)計(jì)思路,并研制了數(shù)據(jù)下載線. 經(jīng)實(shí)際測(cè)試和

2011-06-27 15:57:30 44

44 邏輯器件可分類兩大類 - 固定邏輯器件和可編程邏輯器件。一如其名,固定邏輯器件中的電路是永久性的,它們完成一種或一組功能 -- 一旦制造完成,就無(wú)法改變。

2011-12-05 17:39:16 888

888 7.1 可編程邏輯器件的基本原理 7.2 可編程邏輯器件的設(shè)計(jì)技術(shù) 7.3 可編程邏輯器件的編程與配置

2012-05-23 10:46:19 142

142 本章分析幾種邏輯電路的高速特性,包括TTL邏輯電路、CMOS邏輯電路、ECL邏輯電路,和LVDS器件的基本結(jié)構(gòu)、工作原理和特點(diǎn),以及邏輯門電路的使用規(guī)則。 3.1 高速TTL電路 TTL電路,是出現(xiàn)

2012-05-25 16:31:29 1274

1274 可編程邏輯器件PLD(programmable logic device)是作為一種通用集成電路生產(chǎn)的,其邏輯功能按照用戶對(duì)器件編程來(lái)決定。一般的PLD的集成度很高,足以滿足設(shè)計(jì)一般的數(shù)字系統(tǒng)的需要

2012-06-16 22:13:38

FPGA Cyclone器件中PLL的配置方法

2016-02-23 11:04:13 5

5 Altera cyclone iv 器件的動(dòng)態(tài)配置

2016-02-23 17:05:51 2

2 可編程邏輯器件簡(jiǎn)介,相關(guān)詳細(xì)學(xué)習(xí)。

2016-04-26 16:55:36 0

0 電子專業(yè)單片機(jī)相關(guān)知識(shí)學(xué)習(xí)教材資料之Cyclone_IV器件的邏輯單元

2016-09-02 16:54:40 0

0 可編程邏輯器件FPGA/CPLD結(jié)構(gòu)與應(yīng)用

2016-12-11 23:38:39 0

0 數(shù)字電子技術(shù)--可編程邏輯器件

2016-12-12 22:07:22 0

0 數(shù)字電子技術(shù)-- 可編程邏輯器件

2016-12-12 22:07:22 0

0 可編程邏輯器件(書皮)

2022-07-10 14:34:54 0

0 (Xilinx)FPGA中LVDS差分高速傳輸?shù)?b class="flag-6" style="color: red">實(shí)現(xiàn)

2017-03-01 13:12:04 64

64 PLD可以是低邏輯密度器件,采用被稱為復(fù)雜可編程邏輯器件(CPLD)的非易失元件構(gòu)建;也可以是高密度器件,基于現(xiàn)場(chǎng)可編程門陣列(FPGA)的SRAM查找表(LUT)搭建。在可配置邏輯陣列中,除了

2017-09-12 17:08:30 14

14 現(xiàn)場(chǎng)可編程邏輯門陣列器件 FPGA原理及應(yīng)用設(shè)計(jì)

2017-09-19 11:26:26 17

17 可編程邏輯器件原理、開(kāi)發(fā)與應(yīng)用

2017-09-19 16:04:49 19

19 常用的消費(fèi)類視頻接口包括IEEE 1394(火線)、USB 2.0、DVI、HDMI和各種各樣的無(wú)線標(biāo)準(zhǔn)。本文將介紹如何應(yīng)用可編程邏輯器件(PLD)將不同的高速視頻內(nèi)容連接到視頻播放器。

2018-06-10 09:02:00 1340

1340

關(guān)鍵詞:PLD , 可編程邏輯 在數(shù)字電子系統(tǒng)領(lǐng)域,存在三種基本的器件類型:存儲(chǔ)器、微處理器和邏輯器件。存儲(chǔ)器用來(lái)存儲(chǔ)隨機(jī)信息,如數(shù)據(jù)表或數(shù)據(jù)庫(kù)的內(nèi)容。微處理器執(zhí)行軟件指令來(lái)完成范圍廣泛的任務(wù)

2019-02-23 14:42:01 1471

1471 可編程邏輯器件(PLD)是20世紀(jì)70年代發(fā)展起來(lái)的一種新型邏輯器件,是目前數(shù)字系統(tǒng)設(shè)計(jì)的主要硬件基礎(chǔ)。根據(jù)可編程邏輯器件結(jié)構(gòu)、集成度以及編程工藝的不同,它存在以下不同的分類方法。

2020-06-10 17:52:19 26761

26761 Cyclone FPGA 具有鎖相環(huán)(PLL)和全局時(shí)鐘網(wǎng)絡(luò),提供完整的時(shí)鐘管理方案。Cyclone PLL 具有時(shí)鐘倍頻和分頻、相位偏移、可編程 占空比和外部時(shí)鐘輸出,進(jìn)行系統(tǒng)級(jí)的時(shí)鐘管理和偏移

2021-01-15 14:38:00 24

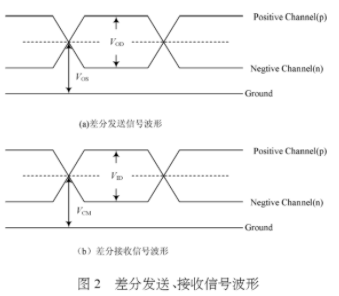

24 LVDS已廣泛應(yīng)用于接口器件和現(xiàn)場(chǎng)可編程門陣列(FPGA)、專用集成電路(ASIC)中,采用LVDS的系統(tǒng)成功實(shí)現(xiàn)了高速互連。然后,并非所有的LVDS I/O接口都有良好的性能。例如,一些ASIC

2021-05-23 17:29:00 2283

2283

可編程邏輯器件PLD課件下載

2021-08-13 10:58:22 31

31 在過(guò)去的十年中,可編程邏輯器件(PLD)市場(chǎng)不斷增長(zhǎng),對(duì)PLD的需求不斷增加。具有可編程特性且可編程的芯片稱為PLD。PLD也稱為現(xiàn)場(chǎng)可編程器件(FPD)。FPD用于實(shí)現(xiàn)數(shù)字邏輯,用戶可以配置集成電路以實(shí)現(xiàn)不同的設(shè)計(jì)。這種集成電路的編程是通過(guò)使用EDA工具進(jìn)行特殊編程來(lái)完成的。

2022-03-22 12:36:24 5304

5304 第一個(gè)商業(yè)化的可編程邏輯器件(Programmable Logic Device,PLD),是由Monolithic內(nèi)存公司推出的可編程陣列邏輯(Programmable Array Logic

2022-08-16 11:36:39 1589

1589 電可編程邏輯器件(Electrically Programmable Logic Device,EPLD)是指采用電信號(hào)的可擦可編程邏輯器件。

2022-08-22 18:12:37 935

935 實(shí)現(xiàn)可編程邏輯電路可以選擇三種主要的技術(shù),它們有兩種主要的特性:是否可重新編程以及是否易失。我們將介紹三種主要的器件,它們是支持可編程電路的技術(shù)基礎(chǔ): 反熔絲、雙柵晶體管和基于SRAM的可編程電路。

2022-09-08 10:47:54 4433

4433 實(shí)現(xiàn)可編程邏輯電路可以選擇三種主要的技術(shù),它們有兩種主要的特性:是否可重新編程以及是否易失。我們將介紹三種主要的器件,它們是支持可編程電路的技術(shù)基礎(chǔ): 反熔絲、雙柵晶體管和基于SRAM的可編程電路。

2022-09-08 10:39:45 1808

1808 常見(jiàn)的可編程邏輯器件分為FPGA、EPLD(CPLD)。下面簡(jiǎn)單介紹兩類器件的結(jié)構(gòu)和區(qū)別。

2023-03-24 14:18:28 798

798

可編程邏輯器件 (Programmable Loeie Device,PLD)是一種用戶編程實(shí)現(xiàn)某種邏輯功能的邏輯器件,主要由可編程的與陣列、或陣列、門陣列等組成,可通過(guò)編程來(lái)實(shí)現(xiàn)一定的邏輯功能

2023-06-06 15:35:59 659

659

可編程邏輯器件 (Programmable Loeie Device,PLD)是一種用戶編程實(shí)現(xiàn)某種邏輯功能的邏輯器件,主要由可編程的與陣列、或陣列、門陣列等組成,可通過(guò)編程來(lái)實(shí)現(xiàn)一定的邏輯功能。

2023-06-06 15:37:45 405

405

可編程邏輯器件(Programmable Logic Device,PLD)是一類集成電路器件,可以根據(jù)用戶的需求進(jìn)行編程和配置,以實(shí)現(xiàn)特定的邏輯功能。它們具有可編程的邏輯門、時(shí)鐘資源和互連結(jié)構(gòu),可以替代傳統(tǒng)的固定功能邏輯芯片,提供更靈活和可定制的解決方案。

2023-09-14 15:25:55 1108

1108 可編程邏輯器件是一種集成電路,具有可編程功能的特性。它們可以根據(jù)用戶的需求進(jìn)行編程,從而實(shí)現(xiàn)不同的邏輯功能。

2024-02-26 18:24:03 576

576

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論