引言:本文我們介紹FPGA SelectIO信號設計。本章提供了選擇I/O標準、拓撲結構和終端的一些策略,并為更詳細的決策和驗證提供了仿真和測量方面的指導。在許多情況下,系統(tǒng)的高級方面(其他設備選擇或標準支持)定義了要使用的I/O接口。在沒有定義這些約束的情況下,由系統(tǒng)設計者選擇I/O接口標準,并根據(jù)設計的目的對其進行優(yōu)化系統(tǒng)。文章包含以下部分:

接口類型

單端信號

1.接口類型

為了更好地處理各種接口類型的細節(jié),有必要首先將接口劃分為多個類別。分為兩個相關部分:

單端接口與差分接口

單數(shù)據(jù)速率(SDR)接口與雙數(shù)據(jù)速率(DDR)接口

1.1 單端信號VS差分接口

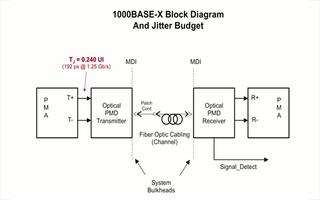

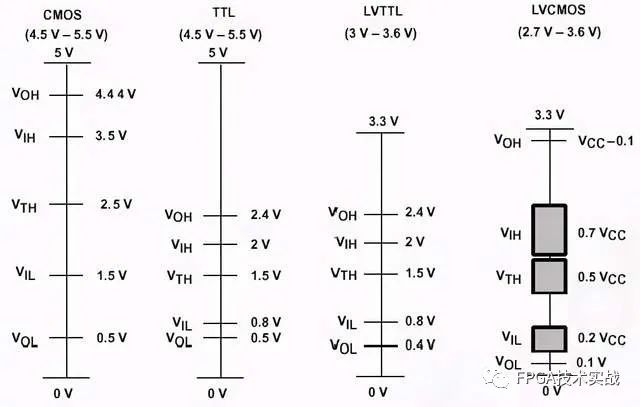

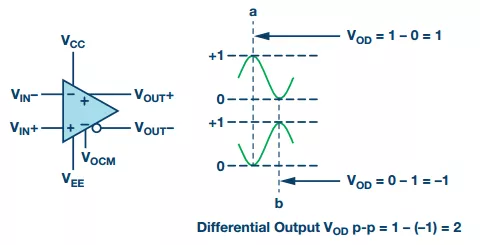

傳統(tǒng)的數(shù)字邏輯使用單端信令——一種傳輸信號并假定驅(qū)動器和接收器共用GND的約定。在單端接口中,信號的斷言(無論是高還是低)是基于其相對于固定電壓閾值的電壓電平,該閾值參考GND。當信號電壓高于VIH閾值時,該狀態(tài)被視為高。當信號的電壓低于VIL閾值時,該狀態(tài)被認為是低的。TTL是單端I/O標準的一個常見示例。 為了達到更高的接口速度和增加噪聲容限,一些單端I/O標準依賴于精確的專用本地參考電壓而不是GND。HSTL和SSTL是依賴VREF來解析邏輯電平的I/O標準的例子。VREF可以看作是一個固定的比較器輸入。 高性能接口通常利用差分信號——一種傳輸兩個相互引用的互補信號的約定。在差分接口中,信號的斷言(無論是高還是低)是基于兩個互補信號的相對電壓電平。當P信號的電壓高于N信號的電壓時,該狀態(tài)被認為是高的。當N信號的電壓高于P信號的電壓時,該狀態(tài)被認為是低的。通常P和N信號具有相似的擺動,并且具有高于GND的共模電壓(盡管情況并非總是如此)。LVDS是差分I/O標準的一個常見示例。

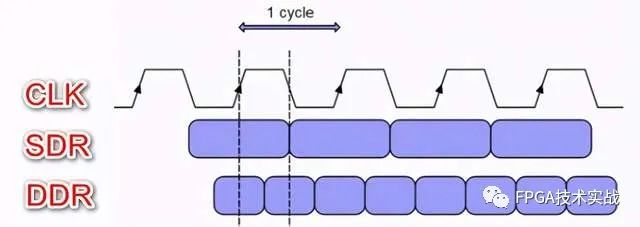

1.2 SDR VS DDR接口

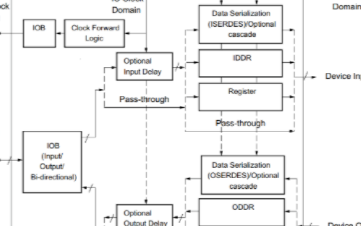

單數(shù)據(jù)速率(SDR)和雙數(shù)據(jù)速率(DDR)接口之間的區(qū)別與總線的數(shù)據(jù)信號與該總線的時鐘信號之間的關系有關。在軟件無線電系統(tǒng)中,數(shù)據(jù)只記錄在接收設備的輸入觸發(fā)器上,在時鐘的上升沿或下降沿。一個完整的時鐘周期相當于一個位時間。在DDR系統(tǒng)中,數(shù)據(jù)在時鐘上升沿和下降沿的接收設備的輸入觸發(fā)器上記錄。一個完整的時鐘周期相當于兩位時間。SDR和DDR的區(qū)別與攜帶信號的I/O標準是單端還是差分無關。單端接口可以是SDR或DDR,差分接口也可以是SDR或DDR。

圖1、SDR VS DDR接口

2.單端信號

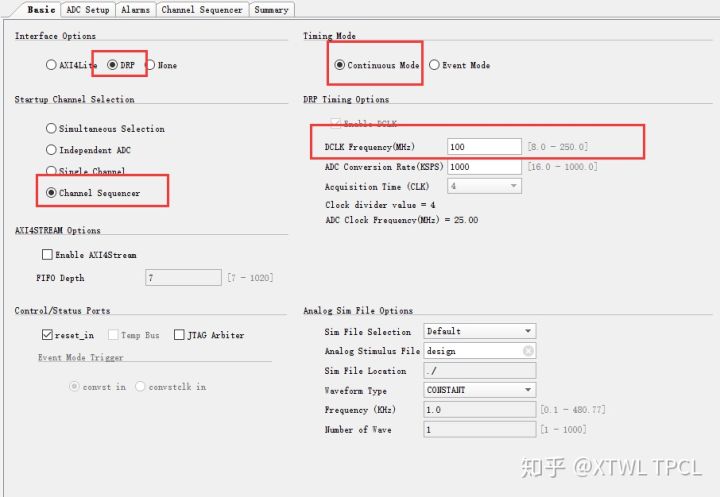

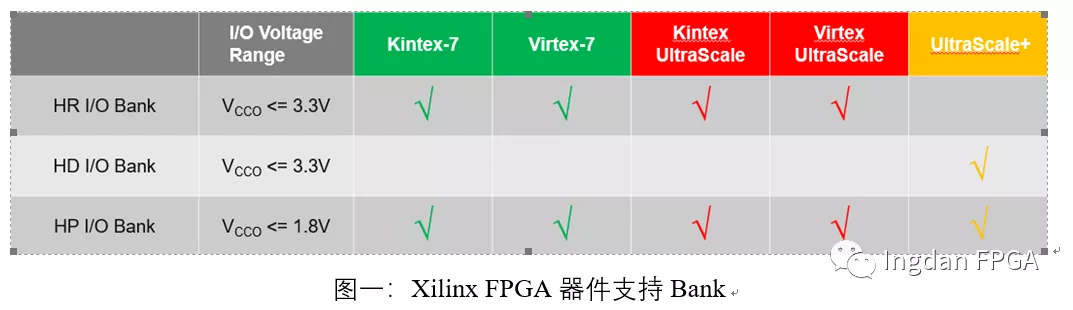

7系列FPGA I/O中提供了多種單端I/O標準。有關支持的I/O標準的完整列表以及每種標準的詳細信息,請參閱UG471:7系列FPGA SelectIO資源用戶指南的“SelectIO資源”一章。該章末尾的表格總結了每個支持的I/O標準,哪些標準支持DRIVE和SLEW屬性、雙向緩沖區(qū)以及DCI選項。它還描述了高性能(HP)和高范圍(HR)I/O組支持哪些I/O標準。

2.1 模式和屬性

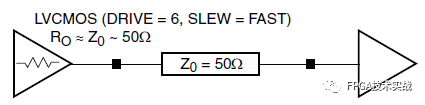

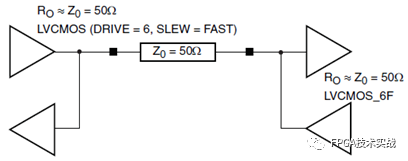

有些I/O標準只能在單向模式下使用,有些則可以在雙向模式或單向模式下使用。 一些I/O標準具有控制驅(qū)動器強度和轉(zhuǎn)換速率的屬性,以及弱上拉或下拉和弱保持電路(不打算用作并行終端)的存在。驅(qū)動強度和轉(zhuǎn)換率可用于調(diào)整接口以獲得足夠的速度,同時不過度驅(qū)動信號。弱上拉、弱下拉和弱保持器可用于確保浮動或3狀態(tài)信號的已知或穩(wěn)定水平。 《UG471,7系列FPGA選擇資源用戶指南》的“選擇資源”一章介紹了哪些標準支持這些屬性。有關詳細信息,請參閱本用戶指南信息。 LVCMOS,當設置為6mA驅(qū)動和快速轉(zhuǎn)換時,具有接近50Ω的近似輸出阻抗,可以用作受控阻抗驅(qū)動器的粗略近似值。弱驅(qū)動器與傳輸線的阻抗匹配是近似的,并且隨電壓和溫度的變化而變化。LVDCI和HSLVDCI,真正的控制阻抗驅(qū)動器,是自適應的,保持更接近的阻抗匹配,并保持恒定的過電壓和溫度。

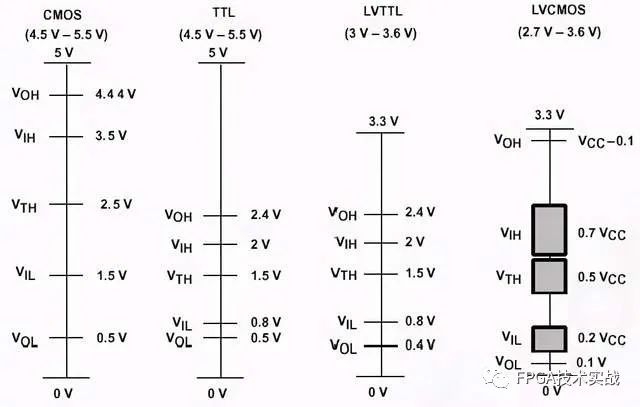

2.2 輸入閾值

單端標準的輸入電路分為兩類:具有固定輸入閾值的電路和具有由VREF電壓設置的輸入閾值的電路。使用VREF有三個優(yōu)點:

允許更嚴格地控制輸入閾值水平

它消除了閾值參考對GND的依賴

它允許輸入閾值更接近,從而減少了輸入接收器處信號電壓大幅度擺動的需要

圖2、常用電平標準閾值 舉例兩個1.8V I/O標準:LVCMOS18和SSTL18 Class 1。1.8V LVCMOS的閾值設置為0.63V和1.17V(需要接收器處的信號至少擺動540mV以進行邏輯轉(zhuǎn)換)。SSTL18等級1的閾值設置為VREF–0.125V和VREF+0.125V,或標稱VREF為0.9V,設置為0.775V和1.025V(要求接收器處的信號至少擺動250 mV,以進行邏輯轉(zhuǎn)換)。所需的較小擺動允許在整個鏈路中進行更高頻率的操作。驅(qū)動器的較小擺幅意味著需要較少的瞬態(tài)電流來降低直流功率。使用VREF的缺陷是,只要在需要VREF電源的Bank中使用I/O標準,Bank的多功能VREF引腳就不能用作I/O。但是,對于7系列器件,可以使用多功能VREF引腳提供參考電壓,也可以選擇使用內(nèi)部VREF功能在內(nèi)部生成參考電壓。有關內(nèi)部VREF的更多詳細信息,請參閱UG471,7系列FPGA選擇用戶指南。有關VREF去耦和所有其他電源去耦的更多信息,請參閱第2部分配電系統(tǒng)。

2.3 拓撲和端接

拓撲通常指接口中驅(qū)動器、接收器、互連和終端的布置。在單向拓撲中使用的技術不同于在雙向拓撲中使用的技術,因此對它們進行分開介紹。選擇符合標準(SSTL、LVCMOS等等)可以根據(jù)標準的字母(由EIA/TIA或JEDEC等標準機構發(fā)布)使用,也可以與來自另一標準或混合I/O的驅(qū)動程序或接收器混合和匹配。I/O標準規(guī)范可以定義接收器的VIL和VIH等限制,也可以定義每個方面包括驅(qū)動器阻抗和轉(zhuǎn)換速率、PCB走線長度和拓撲結構、無源終端的值和位置、接收設備的最大輸入電容,甚至最大輸入電容數(shù)接收器。有許多關于拓撲和終端的設計策略,這些策略影響了接口的信號完整性。通過仿真和測量驗證每個接口的信號完整性是非常重要的。端接通常指用于保持接口中信號完整性的阻抗匹配或阻抗補償裝置。雖然許多類型的元件可用作終端(如電阻器、電容器、二極管),但本討論僅限于電阻終端。一般來說,電容器和二極管端接技術更為復雜。

2.3.1 單端拓撲和端接

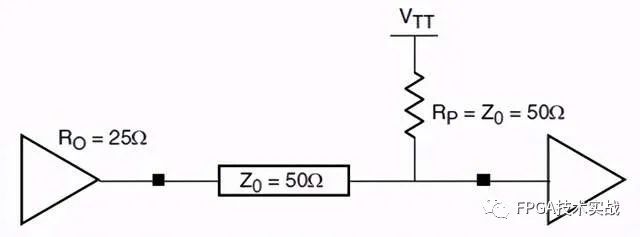

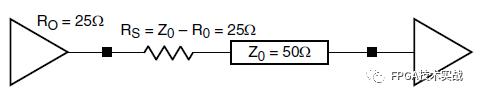

單向拓撲的包括點到點和多點拓撲。點對點拓撲有一個驅(qū)動器和一個接收器,而多點拓撲有一個驅(qū)動器和多個接收器。拓撲是點對點還是多點定義了接口的重要方面,這些方面決定了哪些終止策略是合適的,哪些是不合適的。 1.單端點對點拓撲 最簡單的單向拓撲是點對點形式。也就是說,有一個驅(qū)動器和一個接收器。終端(如有)可包括接收器處的并聯(lián)終端(圖1)、驅(qū)動器處的串聯(lián)終端(圖2)或受控阻抗驅(qū)動器(圖3和圖4)。始終使用IBIS模擬來確定這些終端的最佳電阻值、VTT電壓電平和VRN/VRP參考電阻。

圖3、并行端接單向點對點拓撲

圖4、串聯(lián)端接單向點對點拓撲

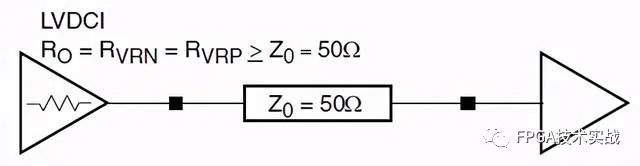

圖5、DCI控制阻抗驅(qū)動器單向點對點拓撲

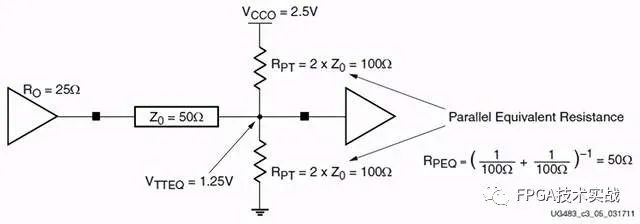

圖6、 弱驅(qū)動,單向點對點拓撲 通常,并聯(lián)電阻終端(RP)的值等于其終端傳輸線的特性阻抗(Z0)。串聯(lián)電阻終端(RS)的值等于傳輸線(Z0)的特性阻抗減去它們所連接的驅(qū)動器(RO)的輸出阻抗。對受控阻抗驅(qū)動器進行調(diào)諧,以使驅(qū)動器輸出阻抗(RO)等于其終端傳輸線的特性阻抗(Z0)。 假設傳輸線的特性阻抗為50Ω,驅(qū)動器輸出阻抗(RO)為25Ω,則25Ω串聯(lián)終端(圖4)或50Ω并聯(lián)終端(圖3)是合適的。受控阻抗驅(qū)動器,無論是用DCI還是用弱LVCMOS驅(qū)動器實現(xiàn),其大小應為50Ω的輸出阻抗(RO,圖5)。對于DCI,這對應于等于50Ω的VRN和VRP電阻器。6 mA至8 mA驅(qū)動強度的弱LVCMOS驅(qū)動器的輸出阻抗約等于50Ω(圖6)。 通常,當VTT(連接到并聯(lián)端接電阻器的電壓源)等于信號電壓的一半時,并聯(lián)端接具有最佳性能。對于2.5V信號(VCCO=2.5V),VTT理想情況下為1.25V。在該電壓不可用的情況下,可以使用戴維南并聯(lián)終端。戴維南并聯(lián)終端由一個分壓器組成,其并聯(lián)等效電阻(RPEQ)等于傳輸線的特性阻抗(大多數(shù)情況下為50Ω)。分壓點設計為VTT。圖7顯示了由2.5V VCCO供電的戴維南并聯(lián)終端,由兩個100Ω電阻器組成,產(chǎn)生1.25V的VTT和50Ω的并聯(lián)等效電阻(RPEQ)。 并聯(lián)端接可能不如串聯(lián)端接或受控阻抗驅(qū)動器理想,因為它會消耗更多的功率。這種權衡必須與其他權衡權衡,以確定接口的最佳終端拓撲。

圖7、戴維南并聯(lián)終端

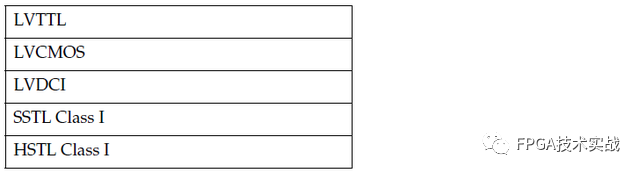

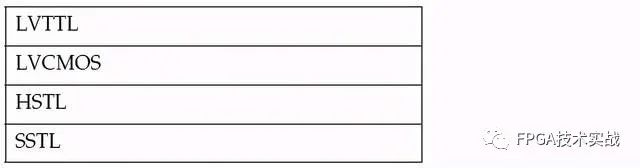

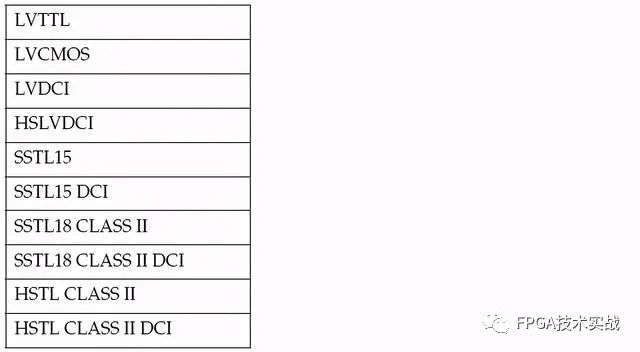

表1列出了可用于單向點到點拓撲的I/O接口類型示例。

表1、可用于單向點到點拓撲的I/O接口類型示例 LVTTL和LVCMOS沒有明確任何規(guī)范的端接方法。驅(qū)動器處的串聯(lián)端接或接收器處的并聯(lián)端接都是合適。

LVDCI隱式使用受控阻抗驅(qū)動器端接,在接收器不需要任何形式的端接。

每I/O標準對終端技術有不同的要求。在某些情況下,I/O標準的規(guī)范可以嚴格定義終端拓撲。具有特定終端要求的標準示例是HSTL。HSTL I類是一種單向I/O標準,建議在接收器處進行并行端接。在HSTL I級的情況下,終端電壓VTT定義為電源電壓VCC的一半。設計人員最終可以選擇完全不使用終端,或者使用不同的終端,例如驅(qū)動程序處的串聯(lián)終端。在給定的系統(tǒng)中,這種選擇可能是有利的,原因有很多。由設計人員通過模擬和測量驗證接收器處的信號完整性是否足夠。 SSTL標準對終端拓撲沒有嚴格的要求。相反,JEDEC規(guī)范提供了通常使用的拓撲圖的示例端接技術。UG471,7系列FPGA SelectIO Resources用戶指南的“SelectIO Resources”一章為每個I/O標準(包括SSTL標準)提供了示例終止技術,目的是為考慮提供一個良好的起點。與HSTL類似,最終由設計者通過模擬和測量來驗證接收器處的信號完整性是否足夠。 2.單向多點拓撲

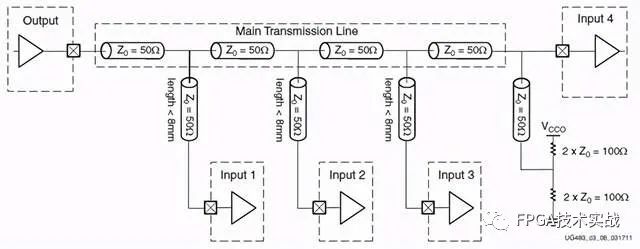

在更復雜的拓撲中,一個驅(qū)動器可以驅(qū)動多個接收器。接收器代表必須由單個傳輸線短接線饋電的負載。從信號完整性的角度來看,在這種情況下使用的最佳拓撲是一條長傳輸線,驅(qū)動器在一端,平行終端在另一端,接收器通過中間的短線連接到主記錄道。這種拓撲通常被稱為飛越多點拓撲(flyby multi-drop)。

這種拓撲有兩個關鍵方面。第一種是在傳輸線的遠端存在一個并聯(lián)終端端接。不得在驅(qū)動器或受控阻抗驅(qū)動器處使用串聯(lián)終端。并行端接是該拓撲唯一適用的端接類型。第二個關鍵方面是每個接收器的連接短截線的長度。這些必須保持短:長度不超過信號上升時間的一小部分。當?shù)湫托盘柹仙龝r間為600 ps時,應使用長度不超過700 ps/4=150 ps或0.9英寸(22.86 mm)的短截線。隨著短截線變長,它們對沿傳輸線傳輸?shù)男盘柍尸F(xiàn)較大的阻抗不連續(xù)性,并且可以支持顯著的反射。這些阻抗的不連續(xù)性破壞了信號。隨著負載數(shù)量的增加和存根長度的增加,信號已損壞到不再可用的程度。 不建議使用星形拓撲圖。設計具有良好信號完整性的星狀拓撲所涉及的限制超出了本文件的范圍。 如單向點對點拓撲圖所述,理想的并聯(lián)電阻終端的值等于其終端傳輸線的特性阻抗。當VTT等于信號電壓的一半時,可獲得最佳性能,當此電壓不可用時,建議使用戴維南并聯(lián)終端,如前一節(jié)所述。 圖8顯示了由VCCO供電的戴維南并聯(lián)終端,由兩個100Ω電阻器組成,產(chǎn)生VCCO/2的VTT和50Ω的并聯(lián)等效電阻。該圖顯示了一個驅(qū)動器(LVCMOS驅(qū)動器)和四個驅(qū)動器的拓撲結構接受者司機在左邊,接收器間隔在50Ω傳輸線的中間點,兩個100Ω電阻器的戴維南并聯(lián)終端位于右側。

圖8、基本多點拓撲 主傳輸線應盡可能短。對于大多數(shù)I/O標準,只要保持精確的跟蹤阻抗并避免串擾源,最長可達20英寸或以上的長度是可行的。主傳輸線路中間段的長度不必相等。它們的相對長度可以是任意的。沿著主傳輸線的不同點的接收器接收具有不同延遲量的信號,但是所有信號上升時間都是相似的。 從主傳輸線延伸到各個接收器的短截線必須盡可能短。這些存根越長,接收到的波形就越損壞。需要仿真和測量來評估各個接收機的信號完整性。

表2列出了可用于單向多點拓撲的I/O接口類型示例。

表2、可用于單向多點拓撲的I/O接口類型示例

LVTTL和LVCMOS沒有指定明確的端接方法。在長T型線末端并聯(lián)端接是一種合適的端接方法。

2.3.2 雙向拓撲和端接

雙向拓撲包括點到點和多點拓撲。點對點拓撲結構有兩個收發(fā)器(驅(qū)動器和接收器共用一個設備管腳),而多點拓撲結構可以有多個收發(fā)器。拓撲是點對點還是多點定義了接口的重要方面,這些方面決定了哪些終止策略是合適的,哪些是不合適的。 1.雙向點對點拓撲

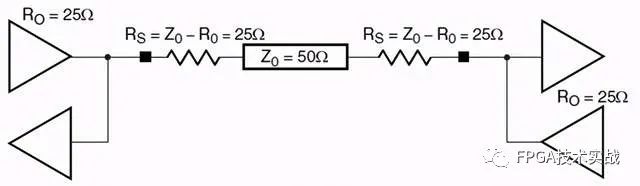

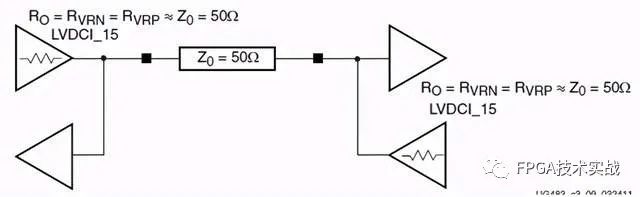

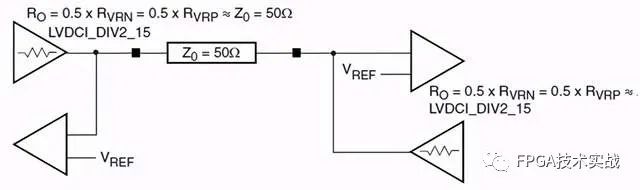

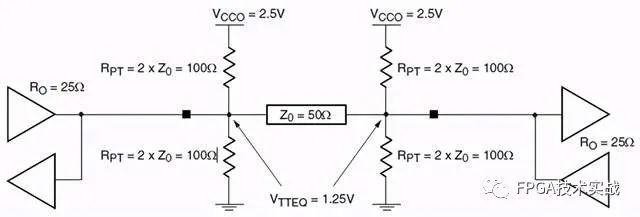

最簡單的雙向拓撲是點對點拓撲。也就是說,有兩個收發(fā)器通過傳輸線連接。因為雙向接口需要在兩個方向上都同樣良好地工作,所以拓撲的對稱性是可取的。雖然非對稱拓撲可以設計為具有相當好的信號完整性,但確保良好信號完整性的最簡單方法是保持拓撲對稱。因此,鏈路一側使用的任何終端也應在鏈路的另一側使用。串聯(lián)終端(圖10)很少適用于雙向接口,因為接收收發(fā)器的串聯(lián)電阻器會衰減輸入信號。并行端接(圖9)幾乎總是在兩種情況下都能獲得更好的信號電平接收器。受控-阻抗驅(qū)動器,無論是以弱LVCMOS驅(qū)動器的形式粗略地控制,還是以LVDCI或HSLVDCI的形式自適應地控制,都可以獲得如圖11、圖12所示的良好效果,以及圖13(使用低驅(qū)動強度LVCMOS驅(qū)動器實現(xiàn))。始終使用IBIS模擬來確定這些終端的最佳終端電阻值、VTT電壓電平和VRN/VRP參考電阻值。

圖9、并行端接雙向點到點拓撲

圖10、串聯(lián)端接雙向點到點T拓撲:不推薦

圖11、DCI控制阻抗雙向點到點拓撲

圖12、HSLVDCI控制阻抗驅(qū)動器雙向點到點拓撲

圖13、“弱驅(qū)動”雙向點對點拓撲 通常,并聯(lián)電阻終端(RP)的值等于其終端傳輸線的特性阻抗Z0。有些接口,如DDR2內(nèi)存接口,使用75Ω終端電阻而不是50Ω,以打開數(shù)據(jù)眼圖。在這種情況下,取舍是眼睛高度與阻抗不連續(xù)的少量信號反射。受控阻抗驅(qū)動器通常進行調(diào)諧,以便驅(qū)動器輸出阻抗(RO)等于其端接傳輸線的特性阻抗(Z0)。 假設傳輸線的特性阻抗為50Ω,驅(qū)動器輸出阻抗為25Ω,50Ω并聯(lián)終端是合適的(圖9)。無論是使用DCI還是使用弱LVCMOS驅(qū)動器實現(xiàn)的可控阻抗驅(qū)動器,其大小應為50Ω的輸出阻抗(RO)。使用受控阻抗驅(qū)動器的一個例子是LVDCI15 I/O標準。通過使用50Ω外部精密電阻器放置在該組的VRN和VRP引腳上,該組的受控輸出阻抗將為50Ω。如果VRN和VRP引腳上已經(jīng)需要100Ω電阻器(用于創(chuàng)建等于50Ω的戴維南等效分裂終端電路),并且同一組中需要50Ω受控阻抗驅(qū)動器,則可以使用“DIV2”版本的驅(qū)動器來實現(xiàn),如LVDCI_15 I/O(圖11和圖3-12)。6 mA至8 mA驅(qū)動強度的弱LVCMOS驅(qū)動器的輸出阻抗約等于50Ω(圖13)。 當VTT(連接到并聯(lián)端接電阻器的電壓源)等于信號電壓的一半時,并聯(lián)端接具有最佳性能,因為這通常是數(shù)據(jù)眼的中心電壓。對于2.5V信號(VCCO=2.5V),VTT理想情況下為1.25V。在該電壓不可用的情況下,建議使用戴維南并聯(lián)終端。戴維南并聯(lián)終端由一個分壓器組成,其并聯(lián)電阻等于傳輸線的特性阻抗(大多數(shù)情況下為50Ω)。分壓點設計為VTT。圖14說明了由2.5V VCCO供電的戴維南并聯(lián)終端,由兩個100Ω電阻器組成,產(chǎn)生1.25V的VTT和50Ω的并聯(lián)等效電阻(RPEQ)。 并聯(lián)端接可能不如串聯(lián)端接或受控阻抗驅(qū)動器理想,因為它會消耗更多的功率。這種權衡必須與其他權衡權衡,以確定接口的最佳終止拓撲。

圖14、戴維南并聯(lián)終端(雙向點對點拓撲)

表3列出了可用于雙向點拓撲的I/O接口類型示例。

表3、雙向點對點I/O拓撲的I/O接口類型示例 LVTTL和LVCMOS沒有指定任何規(guī)范的終止方法。對于雙向接口,不建議使用串聯(lián)端接。然而,并行終止和弱驅(qū)動都是合適的。 LVDCI和HSLVDCI都隱式地使用受控阻抗驅(qū)動端接。 HSTL Class II規(guī)定了兩個收發(fā)器的并行終端。終端電壓VTT定義為電源電壓VCCO的一半。設計者可以選擇完全不使用終端或使用不同的終端。由設計人員通過模擬和測量驗證接收器處的信號完整性是否足夠。 STL的JEDEC規(guī)范提供了串聯(lián)端接和并聯(lián)端接的示例。終端電壓VTT定義為電源電壓VCCO的一半。雖然規(guī)范文件提供了描述驅(qū)動器串聯(lián)端接的示例,但需要注意的是,這樣做的目的是試圖使驅(qū)動器的阻抗與傳輸線的阻抗相匹配。由于7系列FPGA SSTL驅(qū)動器的目標輸出阻抗接近40–50Ω,因此無需任何外部源串聯(lián)終端即可實現(xiàn)更好的信號完整性。在可能的情況下,考慮使用3態(tài)DCI I/O標準(“T_DCI”)是一個更好的起點,該標準提供僅當輸出緩沖器處于3態(tài)時才存在的內(nèi)部并行終端電阻器。設計者應通過仔細的模擬和測量,在接口(通常為DRAM ICs)和終端拓撲中,仔細選擇7系列設備的I/O標準、驅(qū)動器強度和其他設備的模上終端(ODT)選項。有關可用I/O標準和選項的更多詳細信息,請參閱UG471,7系列FPGA SelectIO用戶指南。 2.2 雙向多點拓撲

在更復雜的拓撲中,多點總線中的任何收發(fā)器都可以發(fā)送到所有其他收發(fā)器。通常這些拓撲只能以非常慢的時鐘速率運行,因為它們只支持非常慢的信號上升時間(10 ns到50 ns)。雖然在某些情況下有用,但缺點通常大于好處。設計這些具有良好信號完整性的拓撲所涉及的限制超出了本文件的范圍。

電子發(fā)燒友App

電子發(fā)燒友App

評論