FPGA(Field-Programmable Gate Array),即現(xiàn)場可編程門陣列,它是作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點。對于時序如何用FPGA來分析與設(shè)計,本文將詳細介紹。

2017-06-21 16:05:57 7800

7800

在fpga工程中加入時序約束的目的: 1、給quartusii 提出時序要求; 2、quartusii 在布局布線時會盡量優(yōu)先去滿足給出的時序要求; 3、STA靜態(tài)時序分析工具根據(jù)你提出的約束去判斷

2020-11-25 11:39:35 5320

5320

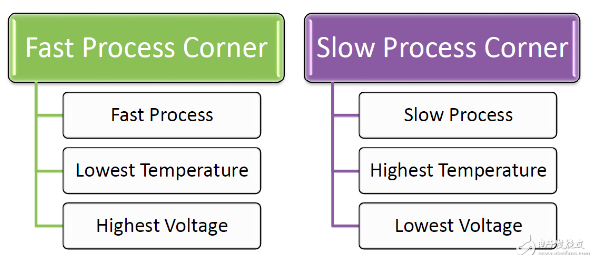

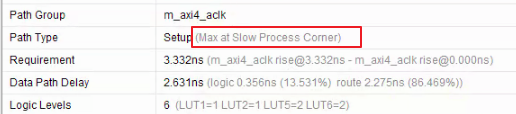

靜態(tài)時序分析用工藝角(Corner)來反映不同的工藝/電壓/溫度等環(huán)境下電路的工作條件。工藝角下的單元庫中定義了單元的時序模型(包括時序延遲值和時序約束值)。理論上時序收斂要保證芯片在各個工作場景(Scenario)下都沒有時序違例,而實際操作中會選取某一個或幾個特殊的工藝角去檢查。

2022-08-30 10:17:49 1709

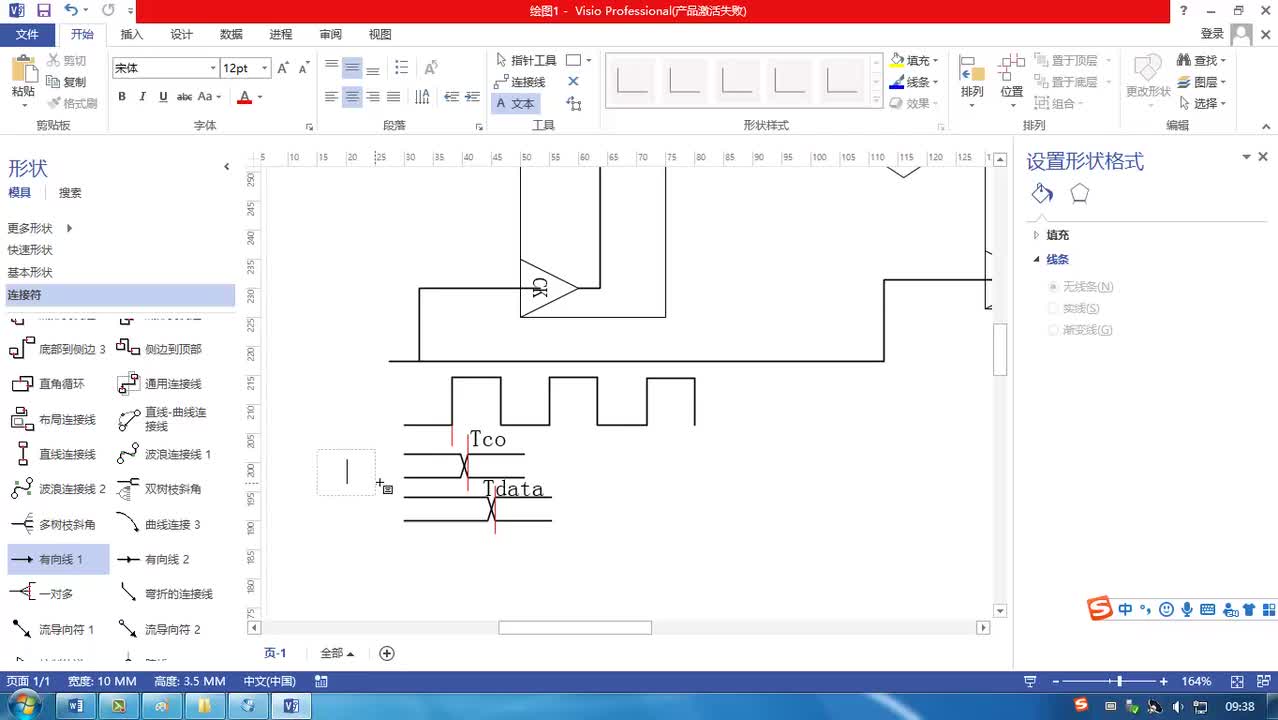

1709 在高速系統(tǒng)中FPGA時序約束不止包括內(nèi)部時鐘約束,還應(yīng)包括完整的IO時序約束和時序例外約束才能實現(xiàn)PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是一個重點。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 1382

1382 時序分析是FPGA設(shè)計中永恒的話題,也是FPGA開發(fā)人員設(shè)計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2022-10-21 09:28:58 1284

1284 今天跟大家分享的內(nèi)容很重要,也是調(diào)試FPGA經(jīng)驗的總結(jié)。隨著FPGA對時序和性能的要求越來越高,高頻率、大位寬的設(shè)計越來越多。在調(diào)試這些FPGA樣機時,需要從寫代碼時就要小心謹(jǐn)慎,否則寫出來的代碼

2023-08-01 09:18:34 1041

1041

前面講解了時序約束的理論知識FPGA時序約束理論篇,本章講解時序約束實際使用。

2023-08-14 18:22:14 842

842

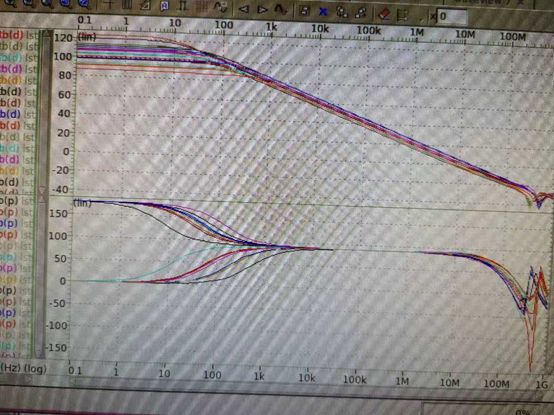

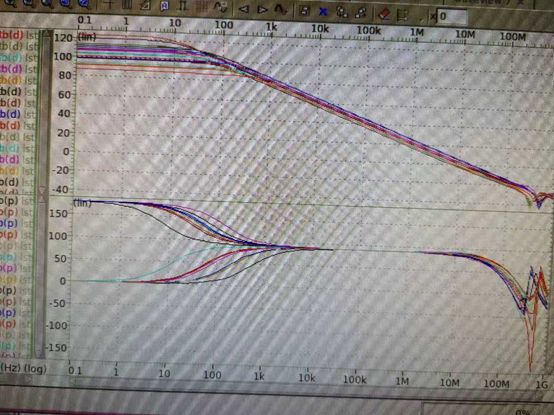

一個運放,使用電阻接成負反饋的形式,閉環(huán)放大倍數(shù)為-1。進行環(huán)路stb仿真,有些corner下相位曲線從0開始,但其他corner正常。這種是什么原因?該怎么解決?

2023-11-07 14:52:35 550

550

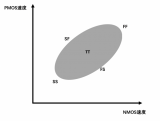

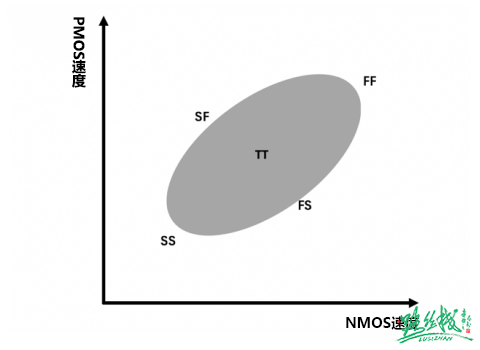

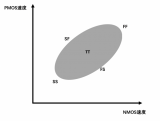

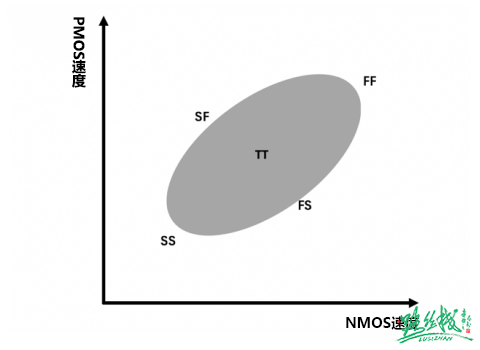

:Typical N Typical P FF:Fast N Fast P SS:Slow N Slow P FS:Fast N Slow P SF:Slow N Fast P

2023-12-01 13:31:22 528

528

電子發(fā)燒友網(wǎng)報道(文/梁浩斌)Corner case在自動駕駛中是指行駛過程中可能出現(xiàn),但發(fā)生頻率極低的小概率事件。盡管平時很少會遇到,但對于自動駕駛系統(tǒng)來說,遇到無法做出決策的corner

2022-10-19 01:21:00 2247

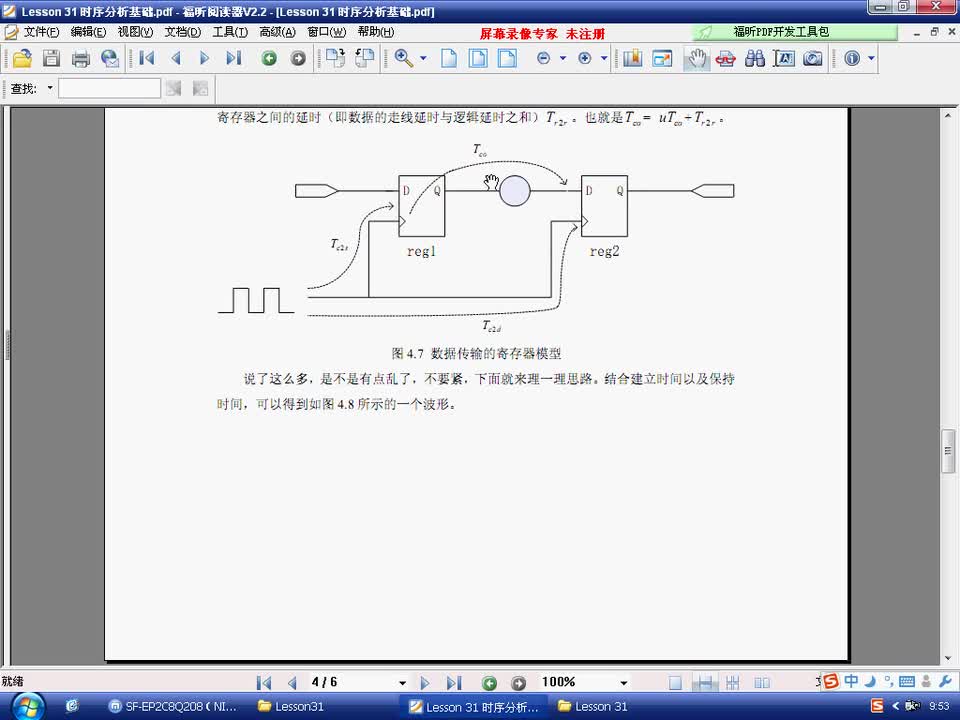

2247 FPGA時序分析系統(tǒng)時序基礎(chǔ)理論對于系統(tǒng)設(shè)計工程師來說,時序問題在設(shè)計中是至關(guān)重要的,尤其是隨著時鐘頻率的提高,留給數(shù)據(jù)傳輸?shù)挠行ёx寫窗口越來越小,要想在很短的時間限制里,讓數(shù)據(jù)信號從驅(qū)動端完整

2012-08-11 17:55:55

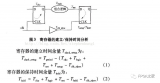

FPGA時序分析與約束(1)本文中時序分析使用的平臺:quartusⅡ13.0芯片廠家:Inter1、什么是時序分析?在FPGA中,數(shù)據(jù)和時鐘傳輸路徑是由相應(yīng)的EDA軟件通過針對特定器件的布局布線

2021-07-26 06:56:44

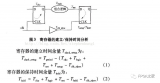

FPGA時序分析與約束(2)——與門電路代碼對應(yīng)電路模型的時序分本文中時序分析使用的平臺:quartusⅡ13.0芯片廠家:InterQuartesⅡ時序分析中常見的時間參數(shù):Tclk1:時鐘從時鐘

2021-07-26 08:00:03

你好: 現(xiàn)在我使用xilinx FPGA進行設(shè)計。遇到問題。我不知道FPGA設(shè)計是否符合時序要求。我在設(shè)計中添加了“時鐘”時序約束。我不知道如何添加其他約束。一句話,我不知道哪條路徑應(yīng)該被禁止。我

2019-03-18 13:37:27

經(jīng)過兩天的惡補,特別是學(xué)習(xí)了《第五章_FPGA時 序收斂》及其相關(guān)的視頻后,我基本上明白了時序分析的概念和用法。之后的幾天,我會根據(jù)一些官方的文件對時序分析進行更系統(tǒng)、深入的學(xué)習(xí)。先總結(jié)一下之前

2011-09-23 10:26:01

FPGA時序相關(guān)的資料。都看完看懂時序就沒問題了。分了三個附件:第一個是通過一些例子教你如何搞定時序分析。第二個附件是網(wǎng)上各種大神們對時序的理解,主要是他們的博客鏈接以及網(wǎng)站鏈接。第三個是其他的一些零散的關(guān)于時序的資料。

2012-11-12 17:45:28

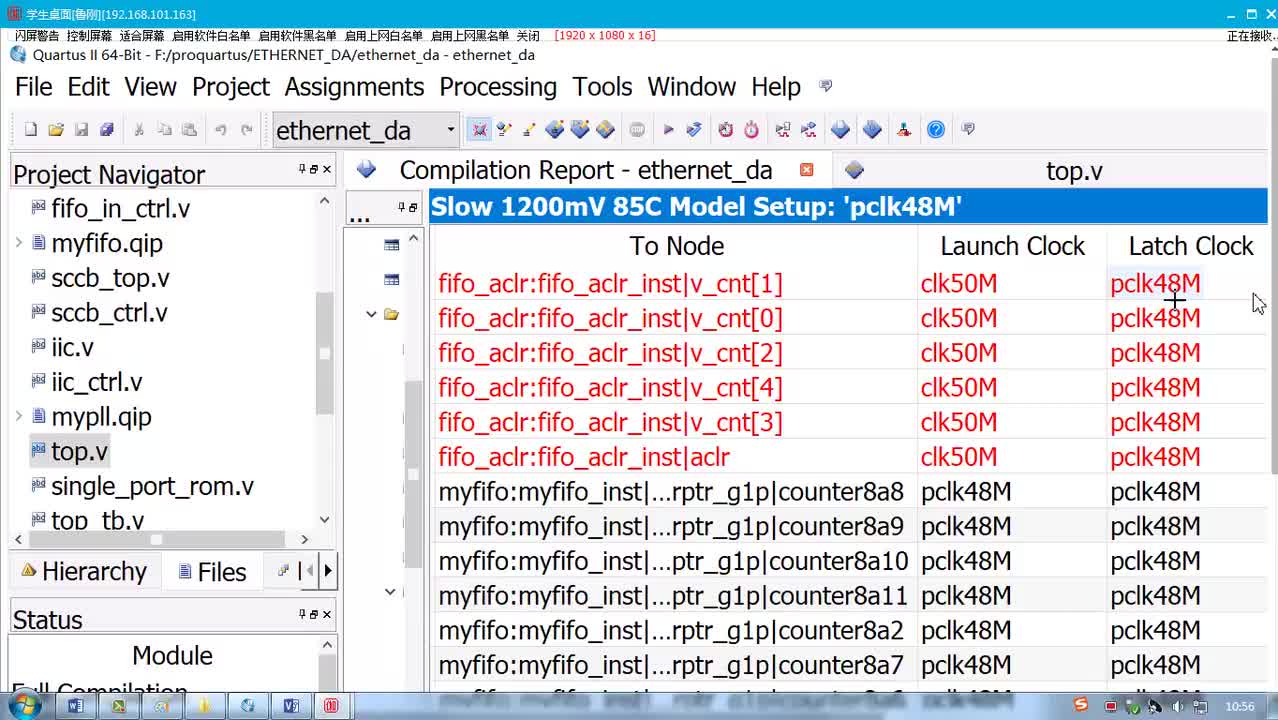

+ 組合邏輯延時Tlogic + FPGA內(nèi)部的網(wǎng)絡(luò)延時Tnet + 寄存器時鐘建立時間Tsu –時鐘偏斜TclkskewFmax = 1 / Tclk在QuartusII時序分析后很容易看到Fmax

2018-07-03 02:11:23

+ 組合邏輯延時Tlogic + FPGA內(nèi)部的網(wǎng)絡(luò)延時Tnet + 寄存器時鐘建立時間Tsu –時鐘偏斜TclkskewFmax = 1 / Tclk在QuartusII時序分析后很容易看到Fmax

2018-07-09 09:16:13

FPGA中幾個基本的重要的時序分析參數(shù)介紹(fmax\tsu\th\tco\tpd)今天無聊,翻開書偶看到介紹時序部分的東西,覺得其中幾個參數(shù)縮寫所代表的含義應(yīng)該記住,故寫如下文章……FPGA中

2012-04-09 09:41:41

基本的時序分析理論1本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計實戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 何謂靜態(tài)時序分析(STA,Static

2015-07-09 21:54:41

基本的時序分析理論2本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計實戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 下面我們再來看一個例子,如圖8.2所示

2015-07-14 11:06:10

FPGA的時序優(yōu)化高級研修班通知通過設(shè)立四大專題,幫助工程師更加深入理解FPGA時序,并掌握時序約束和優(yōu)化的方法。1.FPGA靜態(tài)時序分析2.FPGA異步電路處理方法3.FPGA時序約束方法4.FPGA時序優(yōu)化方法

2013-03-27 15:20:27

FPGA/CPLD的綜合、實現(xiàn)過程中指導(dǎo)邏輯的映射和布局布線。下面主要總結(jié)一下Xilinx FPGA時序約束設(shè)計和分析。

2023-09-21 07:45:57

FPGA靜態(tài)時序分析——IO口時序(Input Delay /output Delay)1.1概述 在高速系統(tǒng)中FPGA時序約束不止包括內(nèi)部時鐘約束,還應(yīng)包括完整的IO時序約束和時序例外約束才能

2012-04-25 15:42:03

如題:fpga時序分析一般都做哪些分析我自己研究時序分析也有一段時間了 ,從理論到altera的timequest,差不多都了解了 ,但就是不知道一個具體的項目都要做哪些約束。求大神知道,或者有沒有這方面的資料(網(wǎng)上資料基本都看過了,沒有說明具體項目的)。

2012-10-22 22:20:32

在學(xué)習(xí)fpga的過程中的疑問:1、在功能仿真和板級驗真后沒問題,還需要進行時序分析嗎2、怎么知道自己寫的代碼有時序問題?

2017-01-08 17:50:35

fpga時序邏輯電路的分析和設(shè)計 時序邏輯電路的結(jié)構(gòu)及特點時序邏輯電路——任何一個時刻的輸出狀態(tài)不僅取決于當(dāng)時的輸入信號,還與電路的原狀態(tài)有關(guān)。[hide][/hide]

2012-06-20 11:18:44

1。時序分析就是分析前級的數(shù)據(jù)是否在后一個時鐘沿的數(shù)據(jù)有效窗口里面,就是說在整個窗口內(nèi)部,數(shù)據(jù)都應(yīng)該保持有效,如果不滿足時間窗的前端,就是setup違例,如果不滿足時間窗的后端,那么就是hold違例

2014-12-29 14:53:00

什么是時序分析?時序約束的作用是什么?FPGA組成的三要素分別是哪些?

2021-09-18 06:05:51

各位好,初次使用pt對fpga進行靜態(tài)時序分析,想請教下需要哪些文件。是不是需要:1、在ise或qutartus生成的網(wǎng)表2、SDC文件3、.db文件.db文件必須且只能從dc生成嗎,要是從.lib轉(zhuǎn)化而來,這個lib文件在fpga設(shè)計時又從哪里得到問題貌似比較多,謝謝回答

2014-12-18 16:15:12

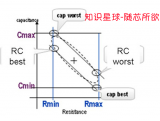

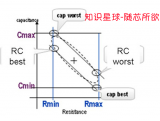

MMMCmulti mode,multi corner :多模式多管腳(適應(yīng)不同情境下芯片的性能等);有些比較悲觀的view可以cover其他的view,以此來節(jié)省實驗的時間。、RC corner

2021-07-23 08:10:12

時序分析是FPGA設(shè)計的必備技能之一,特別是對于高速邏輯設(shè)計更需要時序分析,經(jīng)過基礎(chǔ)的FPGA是基于時序的邏輯器件,每一個時鐘周期對于FPGA內(nèi)部的寄存器都有特殊的意義,不同的時鐘周期執(zhí)行不同的操作

2017-02-26 09:42:48

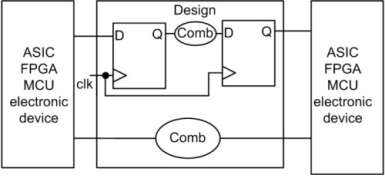

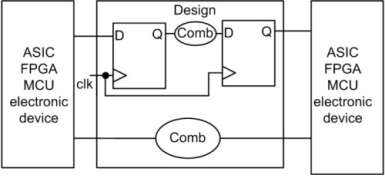

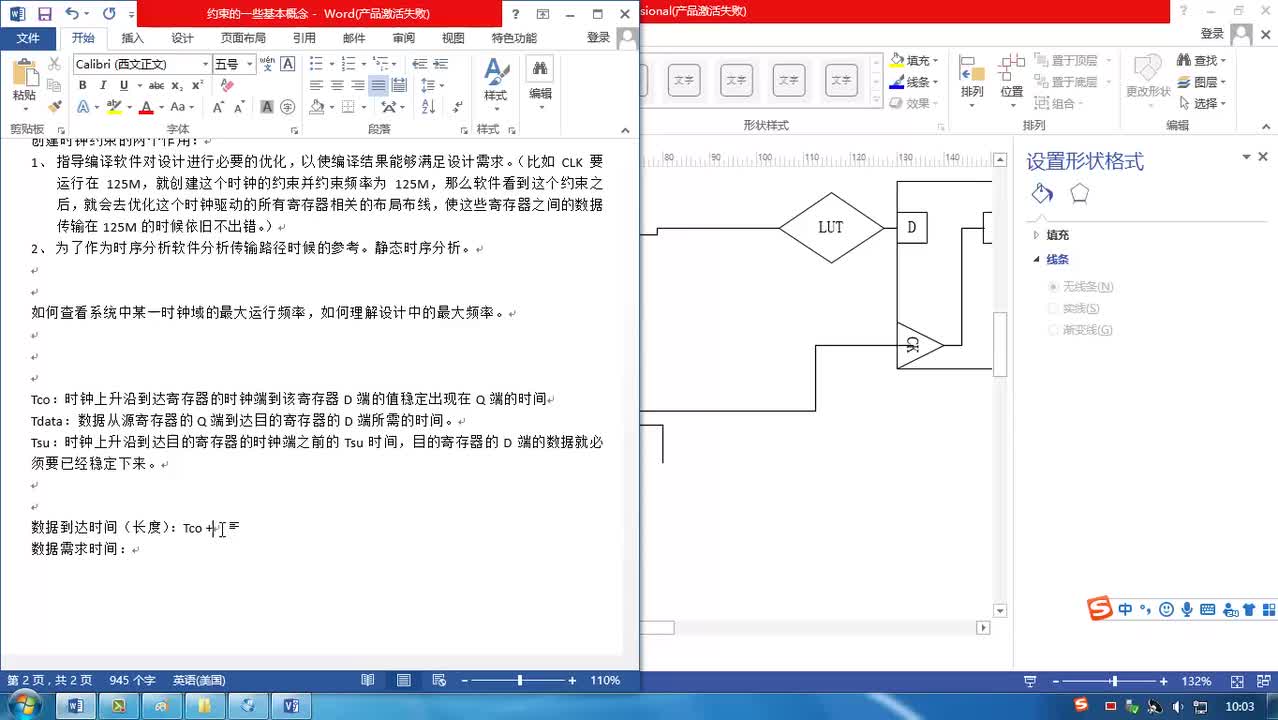

器件門電路數(shù)有限的缺點。對于時序如何用FPGA來分析與設(shè)計,本文將詳細介紹。基本的電子系統(tǒng)如圖 1所示,一般自己的設(shè)計都需要時序分析,如圖 1所示的Design,上部分為時序組合邏輯,下部分只有組合

2018-04-03 11:19:08

:JCDI.0.2010-04-005【正文快照】:1引言90/65nm下芯片的后端設(shè)計變得更加復(fù)雜,隨著模式(mode)和角落(corner)的增多,如何快速取得各種情況下的時序收斂成為設(shè)計的重要

2010-05-28 13:41:58

to dynamically switch between the SLOW and the FAST advertising based on the energy available on the temporary

2018-12-13 14:55:06

在用 ADE XL仿真出現(xiàn)一個error ERRO ID:5010在用 ADE XLall 跑all Corner 的時候,第一個Corner總是會報錯。不知道怎么回事,outputlog里面又沒有顯示有錯,

2021-06-25 06:04:09

1. FPGA時序的基本概念FPGA器件的需求取決于系統(tǒng)和上下游(upstream and downstrem)設(shè)備。我們的設(shè)計需要和其他的devices進行數(shù)據(jù)的交互,其他的devices可能是

2019-07-09 09:14:48

請問如何使用ocean進行corner仿真并用波形查看器查看結(jié)果?

2021-06-24 07:50:23

時序約束與時序分析 ppt教程

本章概要:時序約束與時序分析基礎(chǔ)常用時序概念QuartusII中的時序分析報告

設(shè)置時序約束全局時序約束個別時

2010-05-17 16:08:02 0

0 , FPGAs,and structured ASICs that fi t into nearly every corner ofthe digital electronics market. Combined with Altera’sin

2010-06-30 18:00:09 0

0 介紹了采用STA (靜態(tài)時序分析)對FPGA (現(xiàn)場可編程門陣列)設(shè)計進行時序驗證的基本原理,并介紹了幾種與STA相關(guān)聯(lián)的時序約束。針對時序不滿足的情況,提出了幾種常用的促進 時序收斂的方

2011-05-27 08:58:50 70

70 當(dāng)你的FPGA設(shè)計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現(xiàn)工具來優(yōu)化設(shè)計從而滿足時序要求,也需要設(shè)計者具有明確目標(biāo)和診斷/隔離時序問題的能力。

2014-08-15 14:22:10 1169

1169 FPGA時序約束方法很好地資料,兩大主流的時序約束都講了!

2015-12-14 14:21:25 19

19 基于時序路徑的FPGA時序分析技術(shù)研究_周珊

2017-01-03 17:41:58 2

2 如何有效地管理FPGA設(shè)計中的時序問題

2017-01-14 12:49:02 14

14 當(dāng)你的FPGA設(shè)計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現(xiàn)工具來優(yōu)化設(shè)計從而滿足時序要求,也需要設(shè)計者具有明確目標(biāo)和診斷/隔離時序問題的能力。設(shè)計者現(xiàn)在有一些

2017-02-09 01:59:11 264

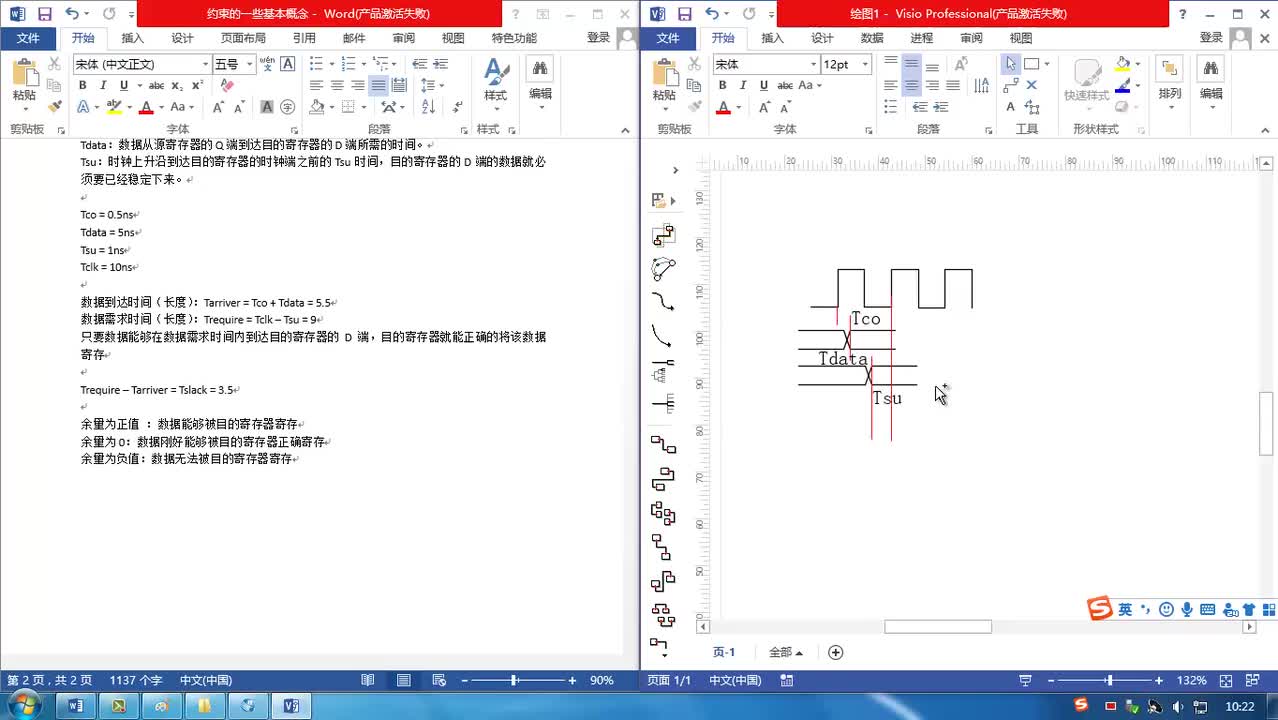

264 時序分析時FPGA設(shè)計中永恒的話題,也是FPGA開發(fā)人員設(shè)計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2017-02-11 19:08:29 3938

3938

fpga時序收斂

2017-03-01 13:13:34 23

23 如今的集成電路(Integrated Circuit,IC)設(shè)計往往要求芯片包含多個工作模式,并且在不同工藝角(corner)下能正常工作。工藝角和工作模式的增加,無疑使時序收斂面臨極大挑戰(zhàn)。本文

2017-10-20 15:21:11 3

3 一個好的FPGA設(shè)計一定是包含兩個層面:良好的代碼風(fēng)格和合理的約束。時序約束作為FPGA設(shè)計中不可或缺的一部分,已發(fā)揮著越來越重要的作用。毋庸置疑,時序約束的最終目的是實現(xiàn)時序收斂。時序收斂作為

2017-11-17 07:54:36 2326

2326

現(xiàn)有的工具和技術(shù)可幫助您有效地實現(xiàn)時序性能目標(biāo)。當(dāng)您的FPGA 設(shè)計無法滿足時序性能目標(biāo)時,其原因可能并不明顯。解決方案不僅取決于FPGA 實現(xiàn)工具為滿足時序要求而優(yōu)化設(shè)計的能力,還取決于設(shè)計人員指定前方目標(biāo),診斷并隔離下游時序問題的能力。

2017-11-18 04:32:34 2951

2951 控制器,在介紹控制器的邏輯結(jié)構(gòu)的基礎(chǔ)上,對FPGA與SDRAM間數(shù)據(jù)通信進行了時序分析,實現(xiàn)SDRAM 帶有自動預(yù)充電突發(fā)讀寫和非自動預(yù)充電整頁讀寫。

2017-11-18 12:42:03 2054

2054

提出了由于FPGA容量的攀升和配置時間的加長,采用常規(guī)設(shè)計會導(dǎo)致系統(tǒng)功能失效的觀點。通過詳細描述Xilinx FPGA各種配置方式及其在電路設(shè)計中的優(yōu)缺點,深入分析了FPGA上電時的配置步驟和工作

2017-11-22 07:18:34 6221

6221

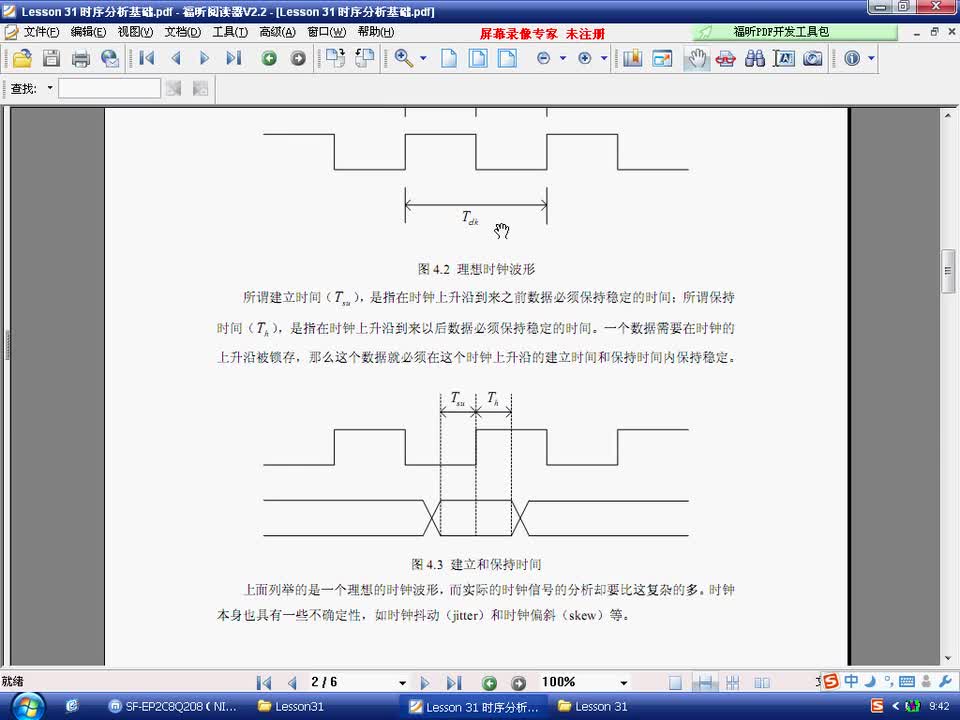

FPGA設(shè)計一個很重要的設(shè)計是時序設(shè)計,而時序設(shè)計的實質(zhì)就是滿足每一個觸發(fā)器的建立(Setup)/保持(Hold)時間的要求。

2018-06-05 01:43:00 4150

4150

“10月是我們在Dark Corner最喜歡的季節(jié),我們很高興能通過這些激動人心的電影來擴展我們的生活,同時繼續(xù)與世界各地的其他虛擬現(xiàn)實媒體和LBE場館建立新的合作關(guān)系,”Dark Corner的CEO蓋伊謝爾默丁在一份官方聲明中說。

2018-10-30 09:15:46 538

538 FPGA中的時序問題是一個比較重要的問題,時序違例,尤其喜歡在資源利用率較高、時鐘頻率較高或者是位寬較寬的情況下出現(xiàn)。建立時間和保持時間是FPGA時序約束中兩個最基本的概念,同樣在芯片電路時序分析中也存在。

2019-12-23 07:01:00 1894

1894

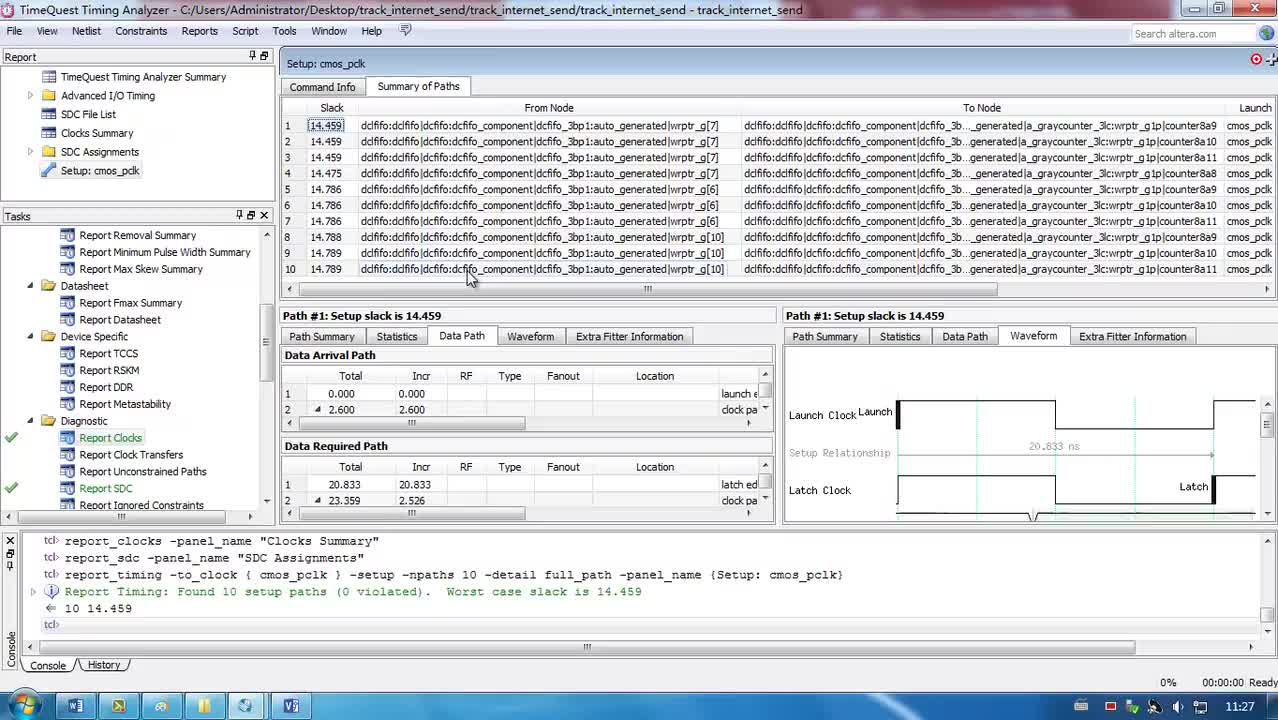

時序分析結(jié)果,并根據(jù)設(shè)計者的修復(fù)使設(shè)計完全滿足時序約束的要求。本章包括以下幾個部分: 1.1 靜態(tài)時序分析簡介 1.2 FPGA 設(shè)計流程 1.3 TimeQuest 的使用 1.4 常用時序約束 1.5 時序分析的基本概念

2020-11-11 08:00:00 58

58 本文檔的主要內(nèi)容詳細介紹的是華為FPGA硬件的靜態(tài)時序分析與邏輯設(shè)計包括了:靜態(tài)時序分析一概念與流程,靜態(tài)時序分析一時序路徑,靜態(tài)時序分析一分析工具

2020-12-21 17:10:54 18

18 時序分析時FPGA設(shè)計中永恒的話題,也是FPGA開發(fā)人員設(shè)計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2021-01-08 16:57:55 28

28 任何學(xué)FPGA的人都跑不掉的一個問題就是進行靜態(tài)時序分析。靜態(tài)時序分析的公式,老實說很晦澀,而且總能看到不同的版本,內(nèi)容又不那么一致,為了徹底解決這個問題,我研究了一天,終于找到了一種很簡單的解讀辦法,可以看透它的本質(zhì),而且不需要再記復(fù)雜的公式了。

2021-01-12 17:48:08 19

19 在高速系統(tǒng)中FPGA時序約束不止包括內(nèi)部時鐘約束,還應(yīng)包括完整的IO時序約束利序例外約束才能實現(xiàn)PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是重點。只有約東正確才能在高速情況下保證FPGA和外部器件通信正確

2021-01-13 17:13:00 11

11 本文檔的主要內(nèi)容詳細介紹的是FPGA的時序分析的優(yōu)化策略詳細說明。

2021-01-14 16:03:59 17

17 本文檔的主要內(nèi)容詳細介紹的是FPGA的時序分析的優(yōu)化策略詳細說明。

2021-01-14 16:03:59 19

19 電子發(fā)燒友網(wǎng)為你提供時序分析是FPGA如何設(shè)計?資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-15 08:51:20 12

12 上一篇《FPGA時序約束分享01_約束四大步驟》一文中,介紹了時序約束的四大步驟。

2022-03-18 10:29:28 1323

1323

時序分析時FPGA設(shè)計中永恒的話題,也是FPGA開發(fā)人員設(shè)計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2022-03-18 11:07:13 2096

2096 靜態(tài)時序分析簡稱STA,它是一種窮盡的分析方法,它按照同步電路設(shè)計的要求,根據(jù)電路網(wǎng)表的拓撲結(jié)構(gòu),計算并檢查電路中每一個DFF(觸發(fā)器)的建立和保持時間以及其他基于路徑的時延要求是否滿足。STA作為

2022-09-27 14:45:13 1809

1809 電子發(fā)燒友網(wǎng)報道(文/梁浩斌)Corner case在自動駕駛中是指行駛過程中可能出現(xiàn),但發(fā)生頻率極低的小概率事件。盡管平時很少會遇到,但對于自動駕駛系統(tǒng)來說,遇到無法做出決策的corner

2022-10-19 07:20:02 711

711 首先使用Harris Corner特征檢測器和sift描述符檢測圖像中的特征,并在其他圖像中找到最佳匹配特征; 然后使用RANSAC 對齊照片(確定它們的重疊和相對位置),最后將生成的圖像拼接到一個無縫的全景圖中。

2023-03-01 11:41:03 699

699

任何學(xué)FPGA的人都跑不掉的一個問題就是進行靜態(tài)時序分析。靜態(tài)時序分析的公式,老實說很晦澀,而且總能看到不同的版本,內(nèi)容又不那么一致,為了徹底解決這個問題,終于找到了一種很簡單的解讀辦法,可以看透

2023-03-14 19:10:03 443

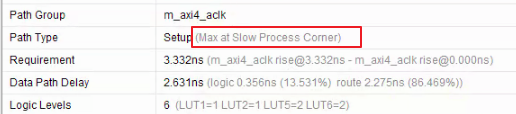

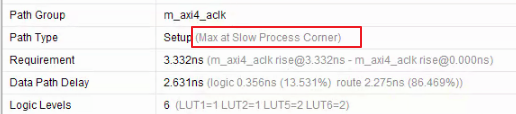

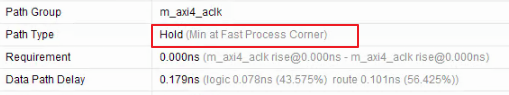

443 在做STA Signoff時,對于Setup來說選擇Slow Corner,也就是慢工藝(SS)、低壓(Low Voltage)、高溫(High Temperature);

2023-04-07 09:37:05 2576

2576 FPGA/CPLD的綜合、實現(xiàn)過程中指導(dǎo)邏輯的映射和布局布線。下面主要總結(jié)一下Xilinx FPGA時序約束設(shè)計和分析。

2023-04-27 10:08:22 768

768 在FPGA的時序分析頁面,我們經(jīng)常會看到`Max at Slow Process Corner`和`Min at Fast Process Corner`,具體是什么含義呢?

2023-05-05 15:50:10 782

782

任何學(xué)FPGA的人都跑不掉的一個問題就是進行靜態(tài)時序分析。靜態(tài)時序分析的公式,老實說很晦澀,而且總能看到不同的版本,內(nèi)容又不那么一致,為了徹底解決這個問題,我研究了一天,終于找到了一種很簡單的解讀辦法,可以看透它的本質(zhì),而且不需要再記復(fù)雜的公式了。

2023-05-29 10:24:29 348

348

90nm后更新的工藝,考慮到互連線coupling的影響,出現(xiàn)了RCworst, RCbest corner.

2023-06-11 15:32:53 3205

3205

UltraEM可以使用Corner Sweep來仿真工藝變化對器件結(jié)構(gòu)造成的影響,具體包含三種仿真模式:MonteCarlo仿真、Perturbation仿真與Corner仿真。

2023-06-19 10:25:53 386

386

STA(Static Timing Analysis,即靜態(tài)時序分析)在實際FPGA設(shè)計過程中的重要性是不言而喻的

2023-06-26 09:01:53 362

362

今天我們要介紹的時序分析基本概念是MMMC分析(MCMM)。全稱是multi-mode, multi-corner, 多模式多端角分析模式。這是在先進工藝下必須要使用的一種時序分析模式。

2023-07-04 15:40:13 1461

1461

FPGA高級時序綜合教程

2023-08-07 16:07:55 3

3 為不同的corner: TT:Typical N Typical P FF:Fast N Fast P SS:Slow N Slow P FS:Fast N Slow P SF:Slow N Fast P 第一個

2023-11-01 15:57:42 1639

1639

今天想聊一聊STA相關(guān)的RC corner的問題。我先簡單介紹一些什么是signoff的corner,然后重點聊一聊RC corner。

2023-12-05 14:11:12 379

379

電子發(fā)燒友App

電子發(fā)燒友App

評論