FPGA設計:為什么要做同步設計?

- FPGA(591969)

- 同步設計(6550)

相關推薦

基于FPGA的通信系統同步提取的仿真與實現

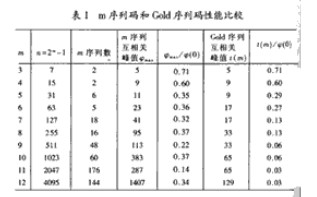

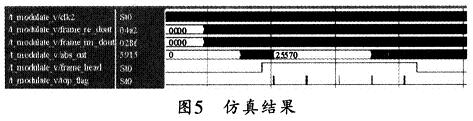

本文介紹一種基于現場可編程門陣列(FPGA)的通信系統同步提取方案的實現。本文只介紹了M序列碼作為同步頭的實現方案,對于m序列碼作為同步頭的實現,只要稍微做一下修改,即加一些相應的延時單元就可以實現。

2013-04-11 10:53:23 3829

3829

3829

3829

基于FPGA的通用位同步器設計方案

摘要本文提出了一種基于FPGA的通用位同步器設計方案。方案中的同步器是采用改進后的Gardner算法結構,其中,內插濾波器采用系數實時計算的Farrow結構,定時誤差檢測采用獨立于載波相位偏差的GA-TED算法,內部控制器和環路濾波器的參數可由外部控制器設置,因而可以適應較寬速率范圍內的基帶碼元。

2013-10-14 13:58:10 5135

5135

5135

5135

基于FPGA的幀同步系統設計方案

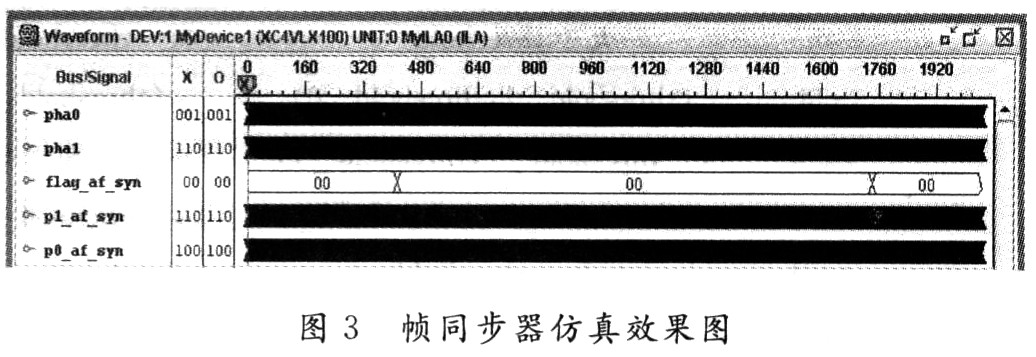

本文介紹了集中式插入法幀同步系統的原理,分析了幀同步系統的工作流程。采用模塊化的設計思想,利用VHDL設計了同步參數可靈活配置的幀同步系統,闡述了關鍵部件的設計方法,提出了一種基于FPGA的幀同步系統設計方案。

2013-11-11 13:36:01 4359

4359

4359

4359

FPGA案例解析:針對源同步的時序約束

約束流程 說到FPGA時序約束的流程,不同的公司可能有些不一樣。反正條條大路通羅馬,找到一種適合自己的就行了。從系統上來看,同步時序約束可以分為系統同步與源同步兩大類。簡單點來說,系統同步

2020-11-20 14:44:52 6859

6859

6859

6859

FPGA/CPLD同步設計若干問題淺析

FPGA CPLD同步設計若干問題淺析摘要:針對FPGA/CPLD同步設計過程中一些容易被忽視的問題進行了研究,分析了問題產生的原因、對可靠性的影響,并給出了解決方案。關鍵詞:FPGA/CPLD

2009-04-21 16:42:01

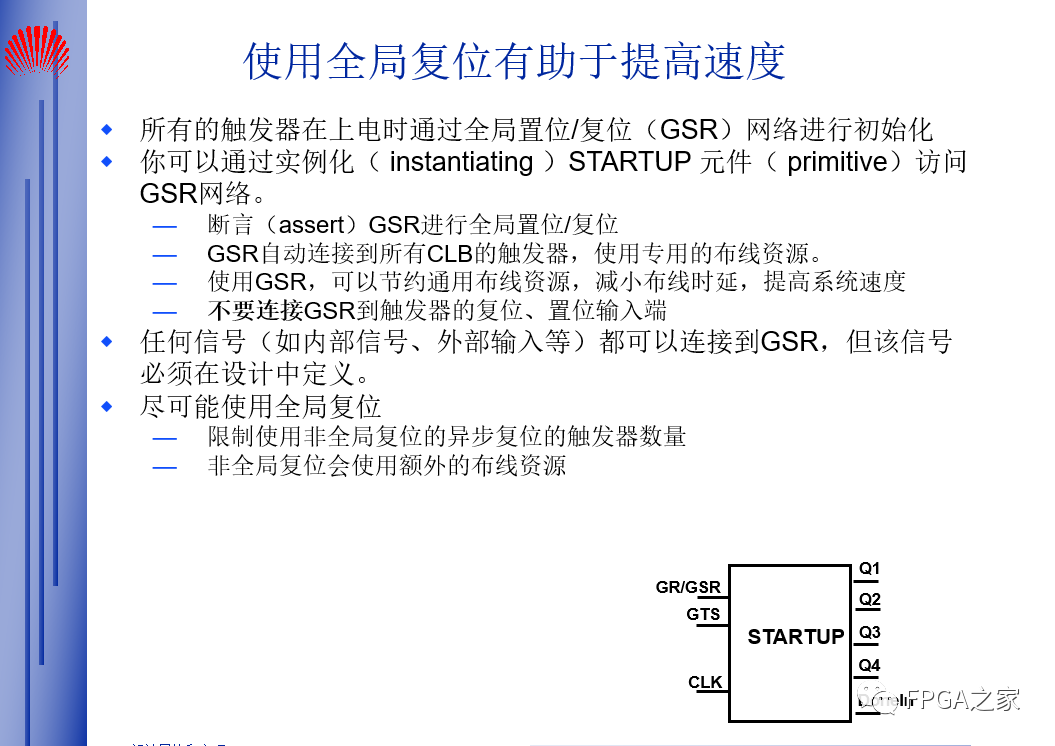

FPGA中的同步與異步復位

和removal時序檢查;異步復位同步撤離(推薦使用) 優點:能避免純異步或純同步復位的潛在問題。它是FPGA設計中最受歡迎的復位,Altera建議使用這種復位方法。這種復位在使用前需要同步到各個使用時

2014-03-20 21:57:25

FPGA異步時鐘設計中的同步策略

摘要:FPGA異步時鐘設計中如何避免亞穩態的產生是一個必須考慮的問題。本文介紹了FPGA異步時鐘設計中容易產生的亞穩態現象及其可能造成的危害,同時根據實踐經驗給出了解決這些問題的幾種同步策略。關鍵詞

2009-04-21 16:52:37

FPGA板卡如何與非FPGA板卡同步

我有一塊IN的FPGA板卡PXI-7854R和非FPGA板卡PXI-6733,請教各位大神,數據輸出和采集時如何將這兩塊板卡同步

2014-12-06 20:47:27

FPGA設計中幀同步系統的實現

FPGA設計中幀同步系統的實現數字通信時,一般以一定數目的碼元組成一個個“字”或“句”,即組成一個個“幀”進行傳輸,因此幀同步信號的頻率很容易由位同步信號經分頻得出,但每個幀的開頭和末尾時刻卻無法由

2012-08-11 16:22:49

FPGA設計中幀同步系統的實現

FPGA設計中幀同步系統的實現數字通信時,一般以一定數目的碼元組成一個個“字”或“句”,即組成一個個“幀”進行傳輸,因此幀同步信號的頻率很容易由位同步信號經分頻得出,但每個幀的開頭和末尾時刻卻無法由

2012-08-11 17:44:43

fpga和ad9789是如何同步的?

我們的設計用到了FPGA和AD9789進行CMOS電平的數字通信。fpga的時鐘跟AD9789的時鐘是異步的,不知道這樣的設計會不會導致fpga和ad9789的通信不穩定,如何避免。fpga和ad9789是如何同步的?通信速率fs=18.284MHz,fdac=2.395204GHz。謝謝!

2023-12-21 08:29:25

fpga和外圍芯片的接口同步問題

fpga和外圍芯片進行通訊是不是需要把所有外圍芯片傳進來的信號進行同步,就是用寄存器打一拍(就是把所有wire類型的輸入變量變為reg),輸出也應該用寄存器打一拍(就是說不能以wire類型的數據輸出)。這樣做是不是能一定程度保存信號同步?

2012-10-28 22:31:25

OFDM系統中頻域同步技術及FPGA實現方法是什么

本文主要介紹各部分的算法方案及電路實現時所用的FPGA元件的基本結構、設計思路。最后通過對電路的仿真波形可以看出,這些頻域同步算法和FPGA電路能夠滿足多載波傳輸系統的同步要求。

2021-05-07 06:52:34

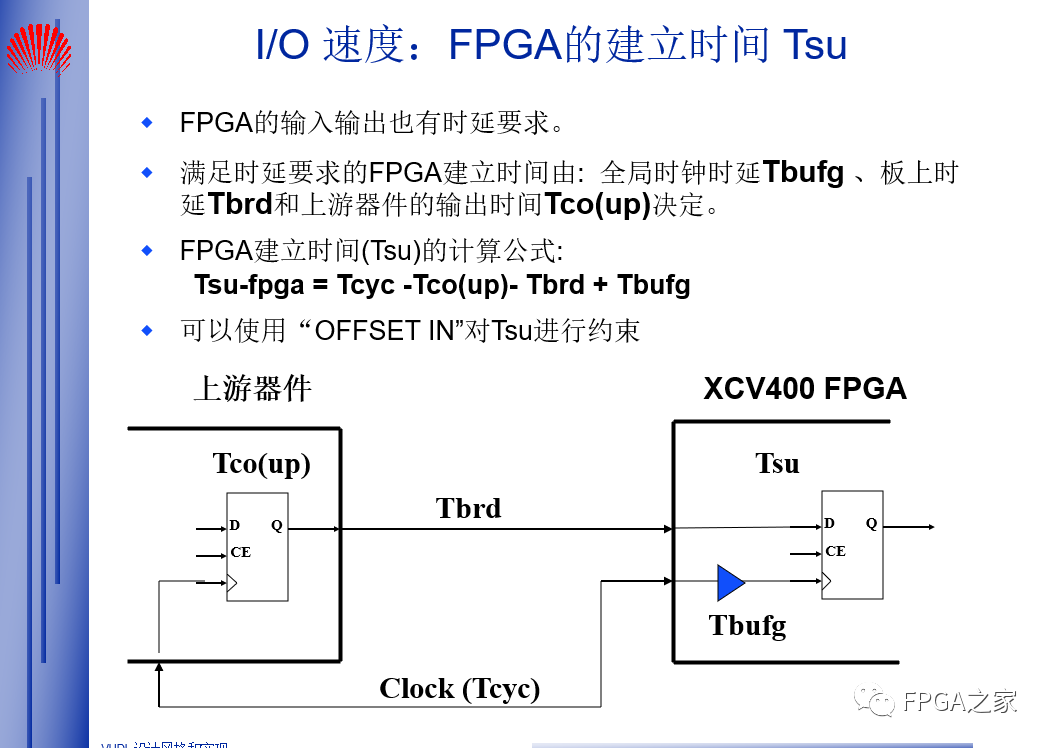

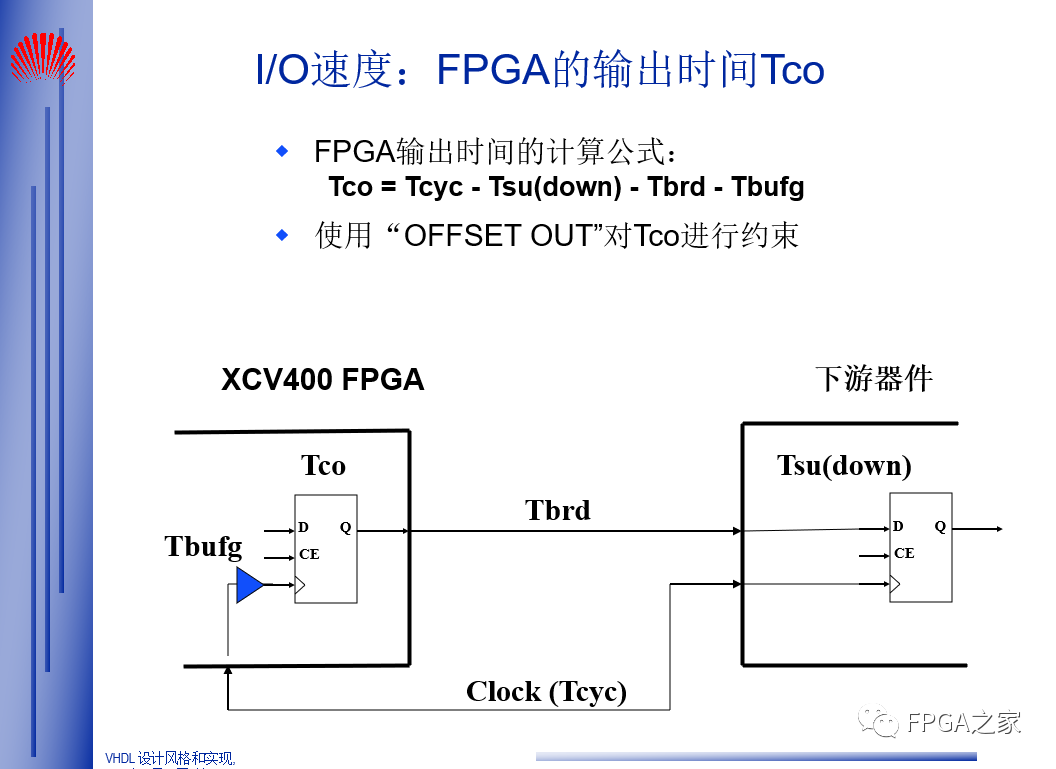

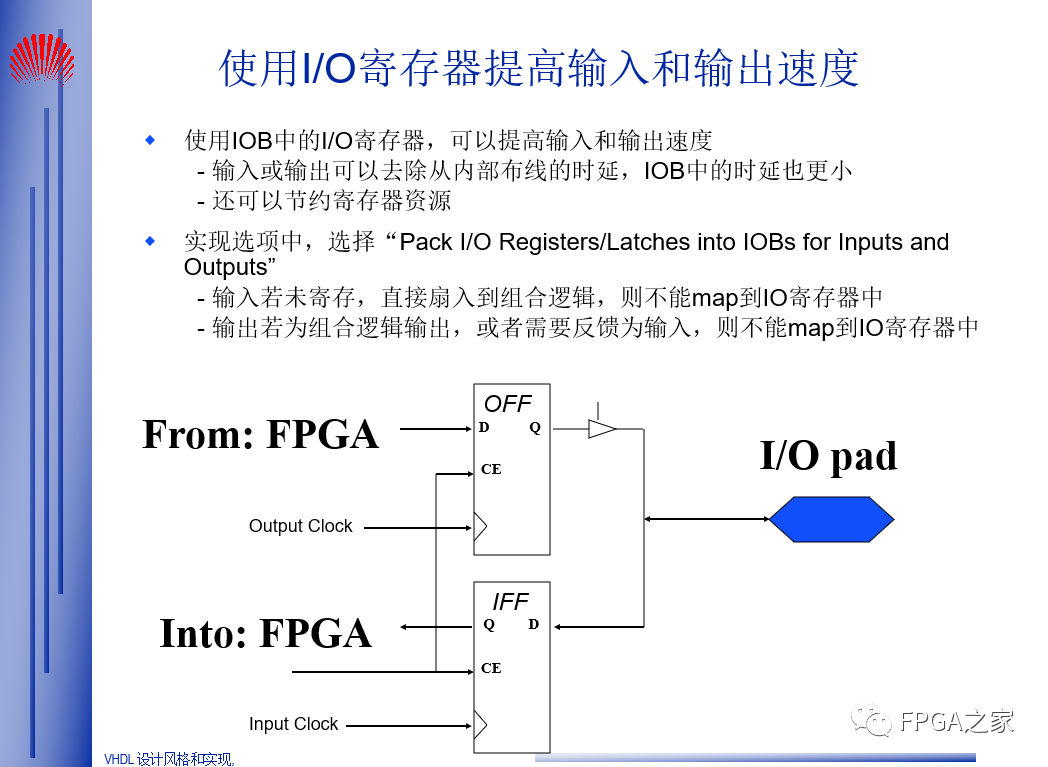

xilinx教程:基于FPGA的時序及同步設計

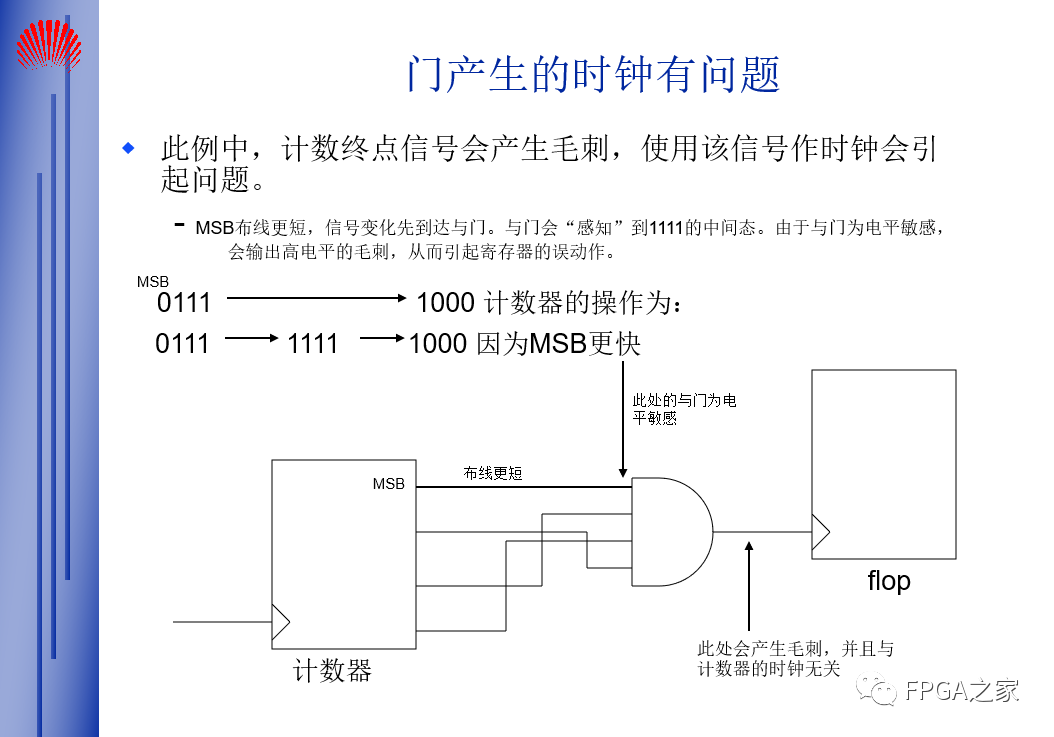

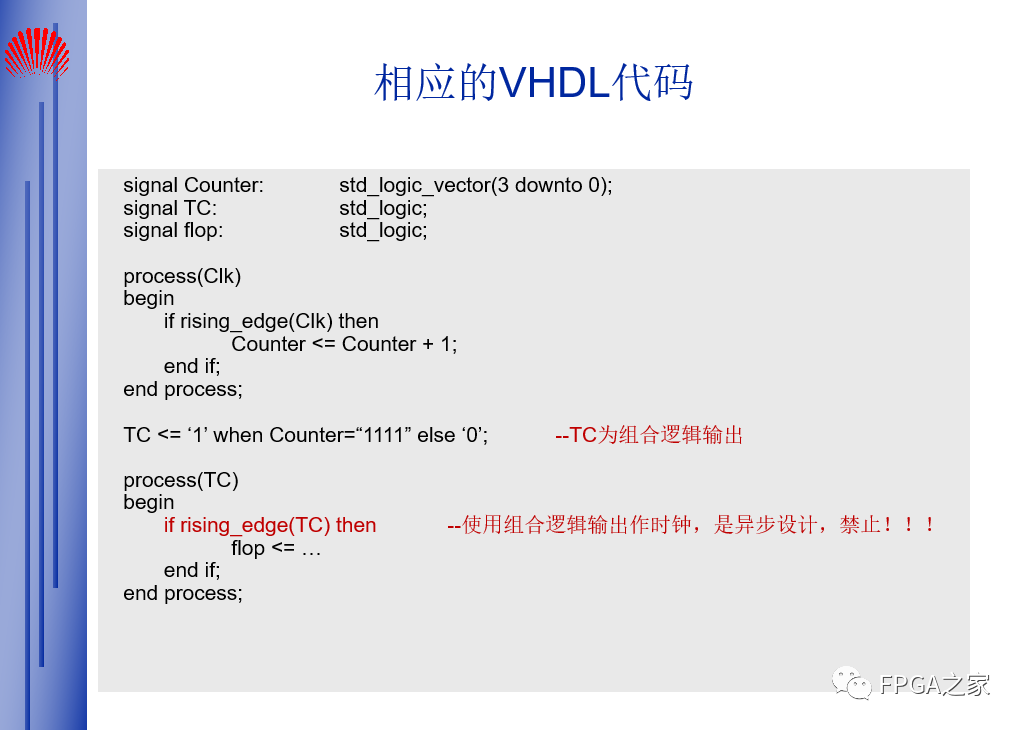

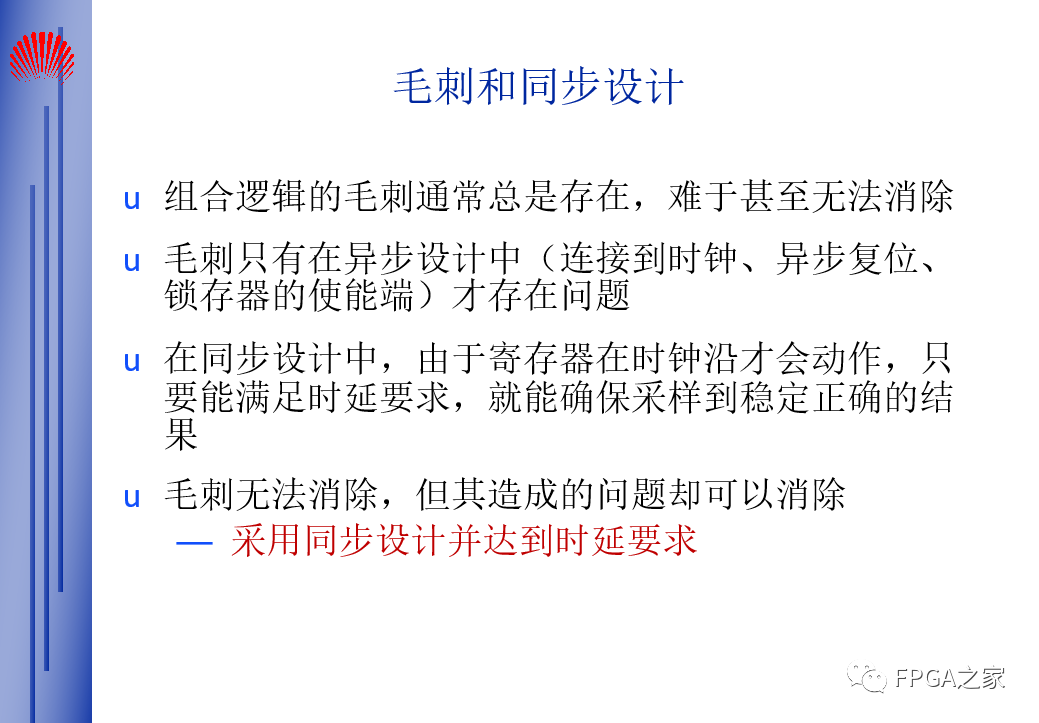

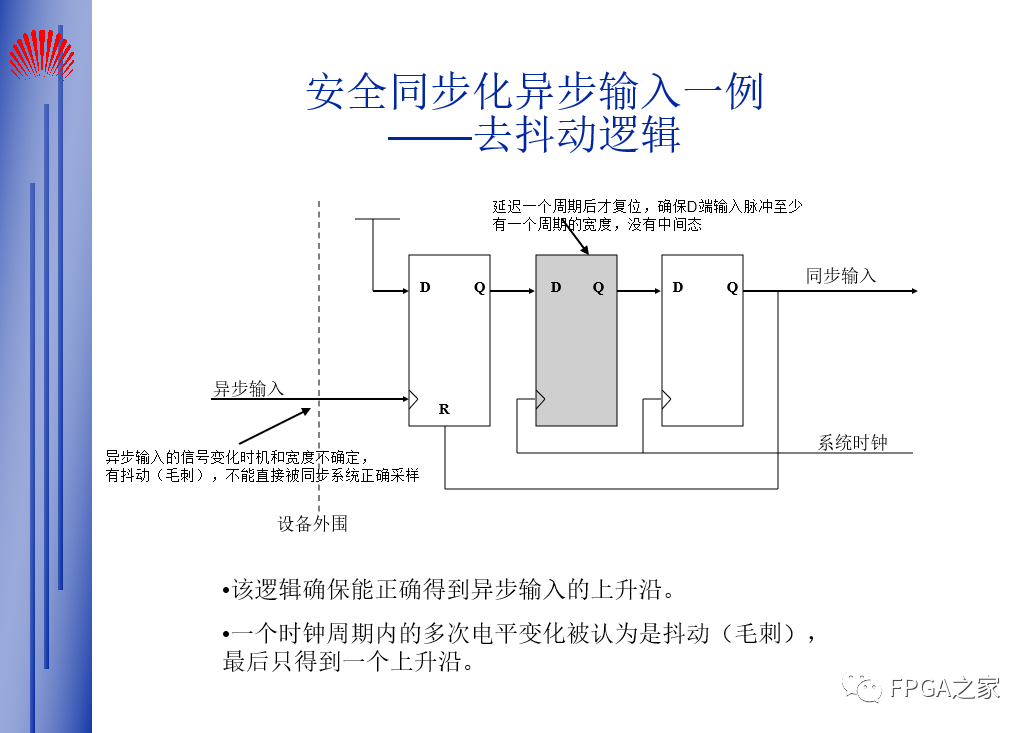

。 對于一個設計項目來說,全局時鐘(或同步時鐘)是最簡單和最可預測的時鐘。在CPLD/FPGA設計中最好的時鐘方案是:由專用的全局時鐘輸入引腳驅動的單個主時鐘去控制設計項目中的每一個觸發器。 只要

2012-03-05 14:29:00

使用FPGA進行CAN通信,需不需要進行位同步

CAN里有一個位同步的概念,我以前用STM32時,還有專門用于做位同步的結構體請問我現在用FPGA作CAN,需不需要設計位同步?還是外接的獨立CAN控制器自己本身就有位同步

2018-10-10 09:35:45

做多通道數據同步采集用哪個系列的fpga功耗低?

項目里用到fpga和單片機,采樣率24bit100kHz。使用fpga一個是用來GPS PPS時鐘同步,一個是多通道A/D數據同步采集(起始沿和clk時鐘同步),采集后存到RAM里,采滿后通知單

2018-11-06 09:35:33

關于FPGA設計的同步信號和亞穩態的分析

同一個時鐘域中,或者來自不同的源(即使它們具有相同的時鐘頻率)在將信號同步到 FPGA 或不同的時鐘域時,有多種設計可供選擇。在xilinx fpga中,最好的方法是使用xilinx參數化宏,創建這些

2022-10-18 14:29:13

基于FPGA的時序及同步設計

數字電路中,時鐘是整個電路最重要、最特殊的信號:因此, 在FPGA設計中最好的時鐘方案是:由專用的全局時鐘輸入引腳驅動單個主時鐘去控制設計項目中的每一個觸發器。同步設計時,全局時鐘輸入一般都接在器件的時鐘端, 否則會使其性能受到影響。

2012-05-23 19:51:48

基于FPGA的時鐘恢復以及系統同步方案設計

摘要:隨著石油勘探的發展,在地震勘探儀器中越來越需要高精度的同步技術來支持高效采集。基于這種目的,采用FPGA技術設計了一種時鐘恢復以及系統同步方案,并完成了系統的固件和嵌入式軟件設計。通過室內測試

2019-06-18 08:15:35

基于FPGA的源同步LVDS接收正確字對齊實現方法

的協議會定義特殊的碼型(常見的碼型如8B/10B編碼中的K28.5)用于字對齊處理。另一些帶源同步時鐘的LVDS接口,通常會利用低頻的源同步時鐘來攜帶字對齊信息,用于接收端的正確恢復。FPGA對上述兩種

2019-07-29 07:03:50

多個FPGA小系統板的同步問題。

我想做多個FPGA的時鐘同步,目前的想法是用一個FPGA的內部時鐘,復制到外接IO口,接到另一個FPGA的外部時鐘引腳,波形有較小的相移但是可以保證同步。想問一下可以復制多次,驅動多個FPGA的同步嗎。對驅動能力有什么要求?其中每一個FPGA都用的是一個EP4CE的最小系統板。

2019-01-21 15:07:41

如何利用FPGA設計提取位同步時鐘DPLL?

信息。自同步法又可以分為兩種,即開環同步法和閉環同步法。開環法采用對輸入碼元做某種變換的方法提取位同步信息。閉環法則用比較本地時鐘和輸入信號的方法,將本地時鐘鎖定在輸入信號上。閉環法更為準確,但是也更為復雜。那么,我們該怎么利用FPGA設計提取位同步時鐘DPLL?

2019-08-05 06:43:01

如何避免FPGA內部操作和ADC數據之間的同步問題?

我們建議的設置如下:希望ADC工作在200 MHz,采樣速率為200 MSPS。最初,為了避免FPGA內部操作和ADC數據之間的同步問題,我們計劃從FPGA驅動ADC輸入時鐘。現在我們擔心高采樣率

2020-08-25 09:23:10

求教FPGA準確采集同步信號

請教各位大大:我最近做FPGA采集100MHz的信號,另一路同步觸發。但觸發信號上升沿在40ns左右,最后導致信號波形左右晃動。請問在FPGA中如何處理可以準確采集到觸發信號,排除左右晃動的情況?

2013-03-06 00:22:42

求解,現在是一個FPGA新手,主要做的是高速接口設計,模塊里有些RS422等

求解,現在是一個FPGA新手,主要做的是高速接口設計,模塊里有些RS422等,想問問各位大神應該怎么學習 或者看些哪些高速接口的書籍嗎?

2017-03-30 20:38:43

用FPGA要做pc與以太網數據的通信的話,是不是可以用lwip+ftp協議,將FPGA做成那種ftp服務器?

我現在用FPGA要做pc與以太網數據的通信的話,是不是可以用lwip+ftp協議,將FPGA做成那種ftp服務器,通過ftp協議進行文件傳輸?如果要做成這種效果,我應該從哪方面入手啊?感覺看了一堆協議,例程,還是沒有思路。

2017-01-16 21:38:44

請問AD轉換芯片數字輸出A0-A11這12根數據線與FPGA連接時要做等長嗎?

AD轉換芯片數字輸出A0-A11這12根數據線與FPGA連接時要做等長嗎?

AD轉換芯片時鐘為70MHz,如果不需要,那么時鐘速率達到多少需要做等長,就是畫蛇形線!

2023-12-12 08:15:53

請問AD轉換芯片數字輸出A0-A11這12根數據線與FPGA連接時要做等長嗎?

AD轉換芯片數字輸出A0-A11這12根數據線與FPGA連接時要做等長嗎?AD轉換芯片時鐘為70MHz,如果不需要,那么時鐘速率達到多少需要做等長,就是畫蛇形線!

2019-01-21 15:55:14

請問DSP與FPGA之間EMIF通訊需要做數據校驗嗎?

請教,一般DSP與FPGA之間EMIF通訊需要做數據校驗嗎?如果需要的話采用什么校驗方式呢?如果DSP采用的是DMA讀寫,那傳錯一個數據就得把那一堆數據重新傳了,這樣會不會影響實時性呢?

2020-07-30 06:24:46

請問我需要將FPGA外部引腳的頻率與內部FPGA時鐘同步嗎?

計算FPGA外部引腳的頻率。我需要將其與內部FPGA時鐘同步嗎?內部參考時鐘以60Mhz運行,外部頻率在10khz到15khz之間變化,不同步的外部頻率是否會導致錯誤或問題?以上來自于谷歌翻譯以下

2019-06-18 09:37:29

EasyGo FPGA Solver

概述EasyGo FPGA Solver是EasyGo開發的專門部署在FPGA 硬件上的解算器軟件。根據不同的應用需求,會有不同的FPGA Solver 選擇

2022-05-19 09:21:43

基于FPGA 的OFDM 寬帶數據通信同步系統設計與實現

基于FPGA 的OFDM 寬帶數據通信同步系統設計與實現:正交頻分復用(OFDM)是第四代移動通信的核心技術,本文介紹了一種基于FPGA的OFDM 寬帶數據通信同步系統的設計方案,該方案為OFDM

2009-06-25 08:18:06 44

44

44

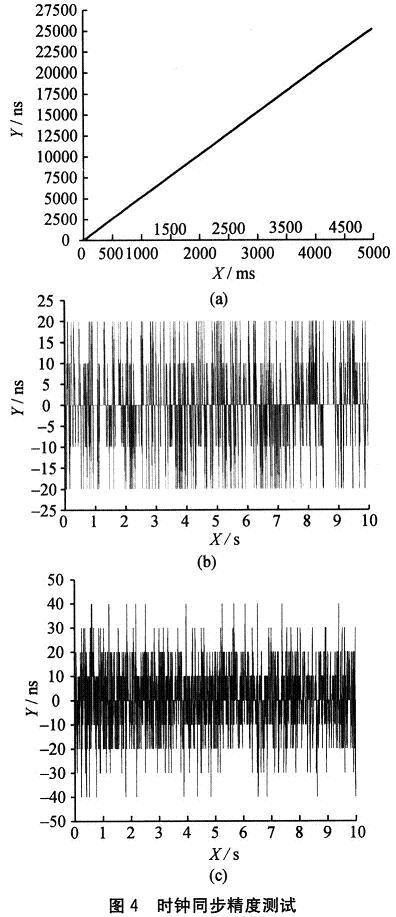

44基于FPGA的GPS同步時鐘裝置的設計

在介紹了GPS 同步時鐘基本原理和FPGA 特點的基礎上,提出了一種基于FPGA 的GPS同步時鐘裝置的設計方案,實現了高精度同步時間信號和同步脈沖的輸出,以及GPS 失步后秒脈沖的平

2009-07-30 11:51:45 40

40

40

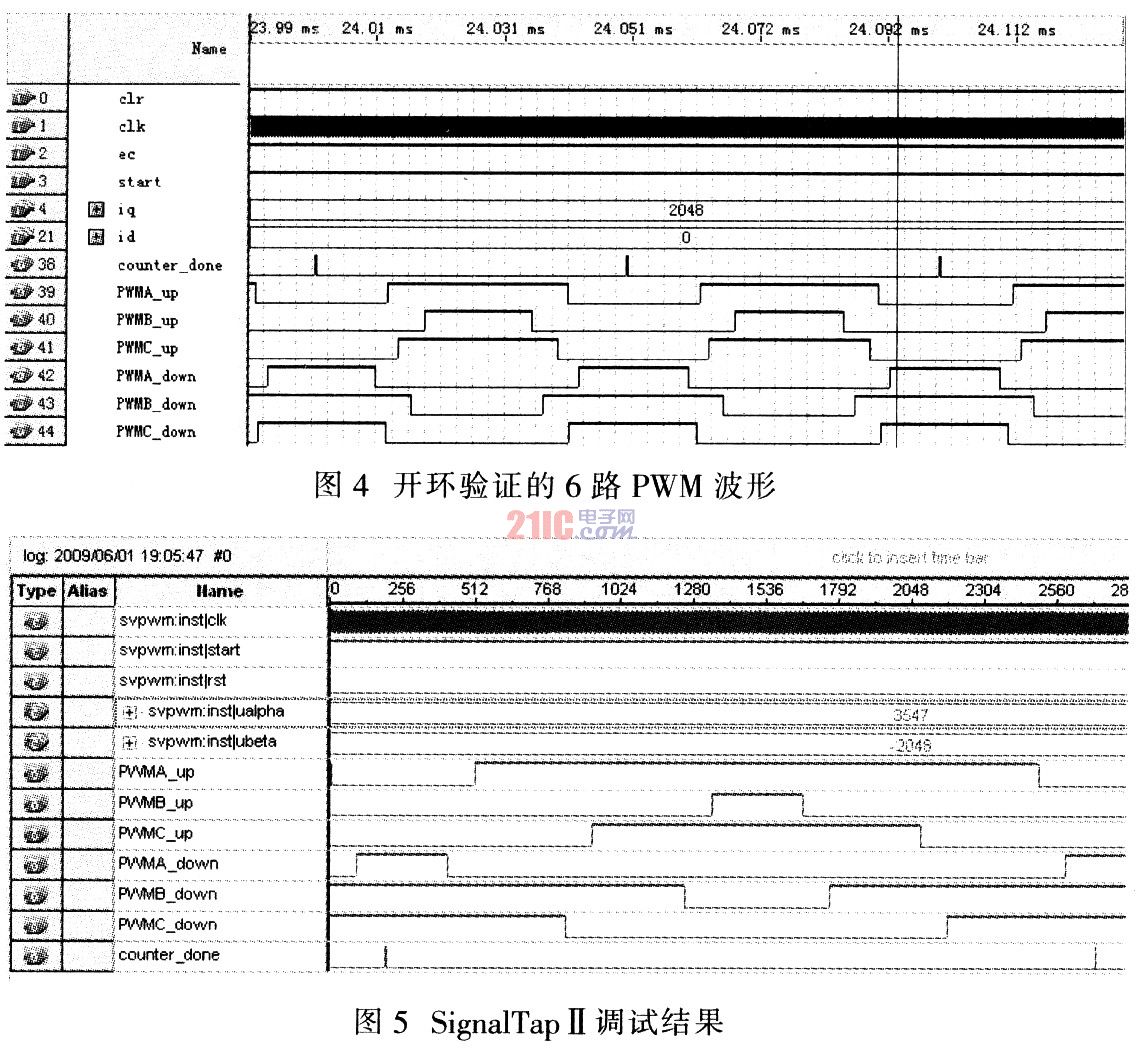

40基于FPGA 的永磁同步電動機矢量控制IP 核的研究

基于FPGA 的永磁同步電動機矢量控制IP 核的研究

摘 要論文首先分析了永磁同步電動機的數學模型及矢量控制的原理。研究了使用現代EDA 工程設計方法,在FPGA

2009-11-11 15:45:18 28

28

28

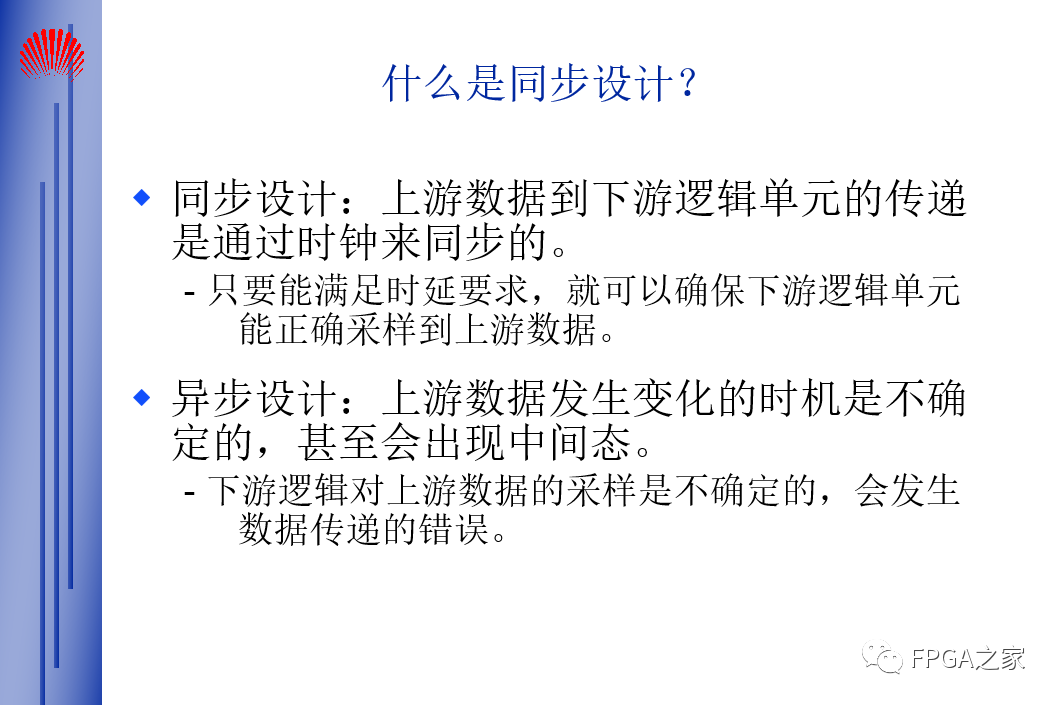

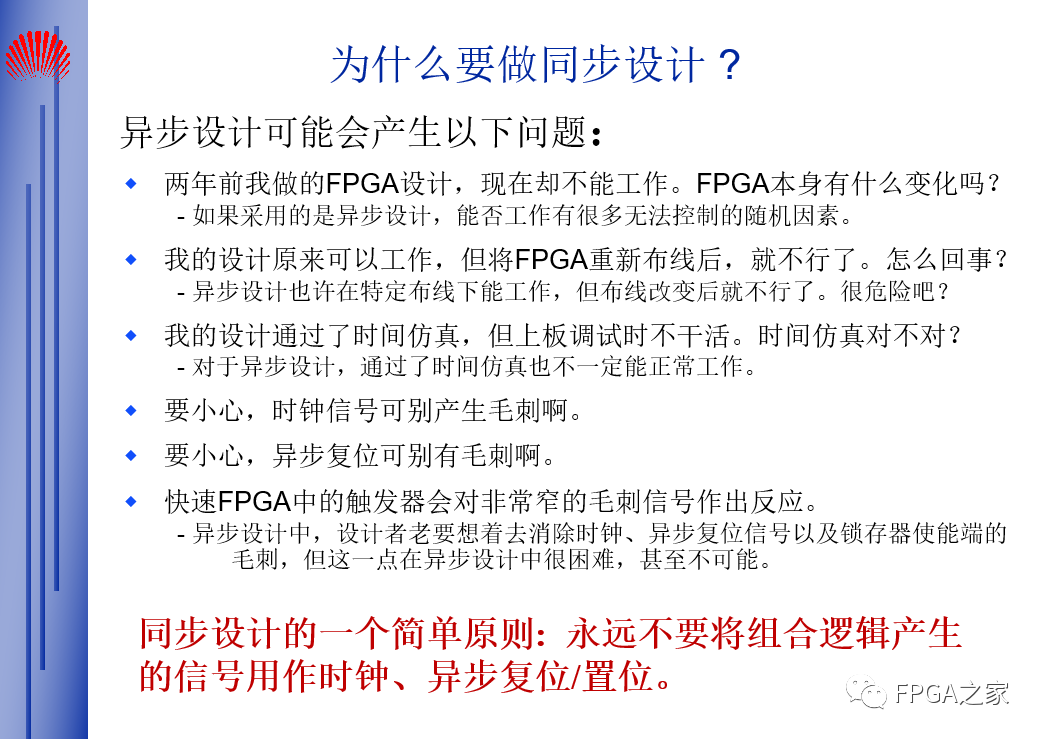

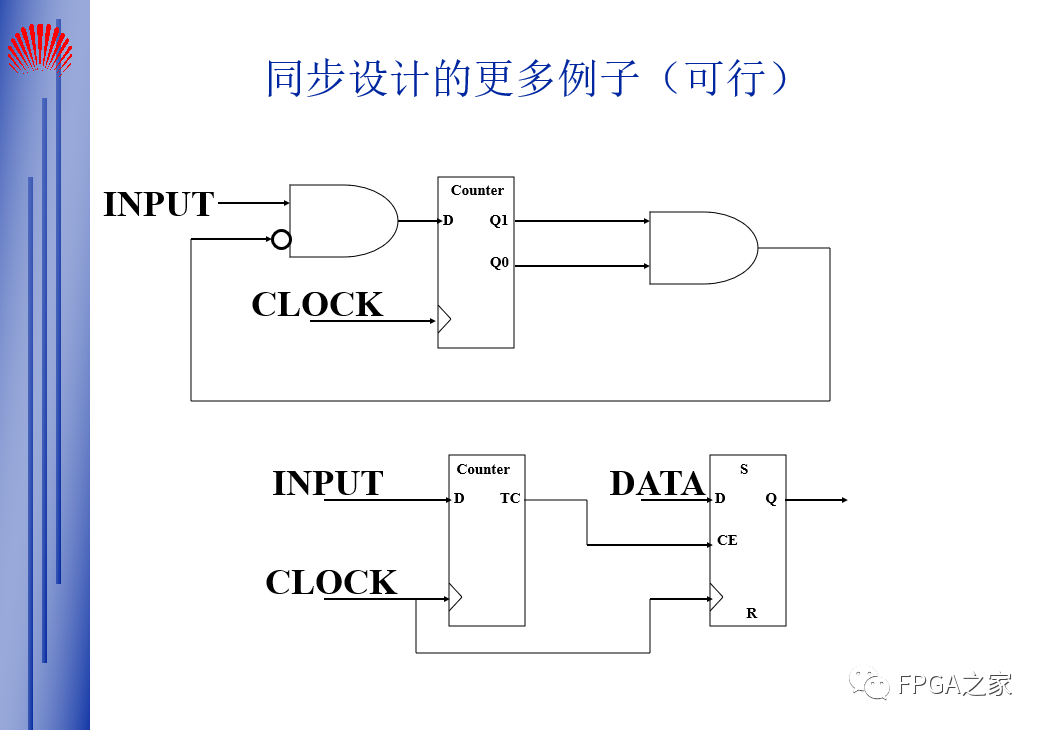

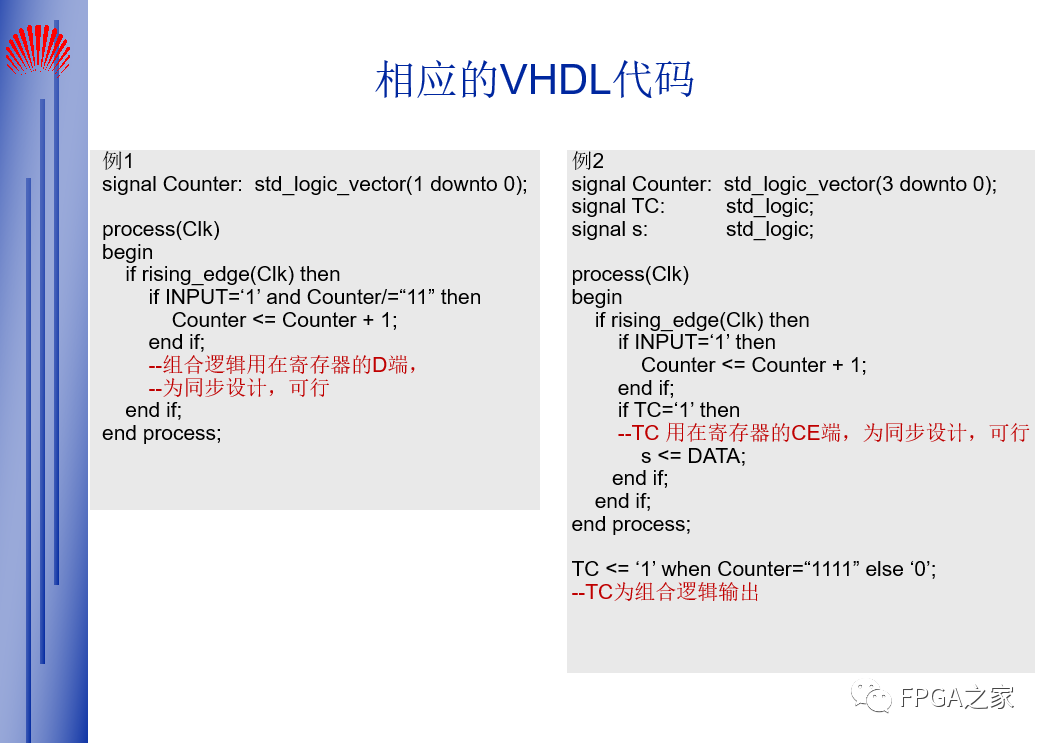

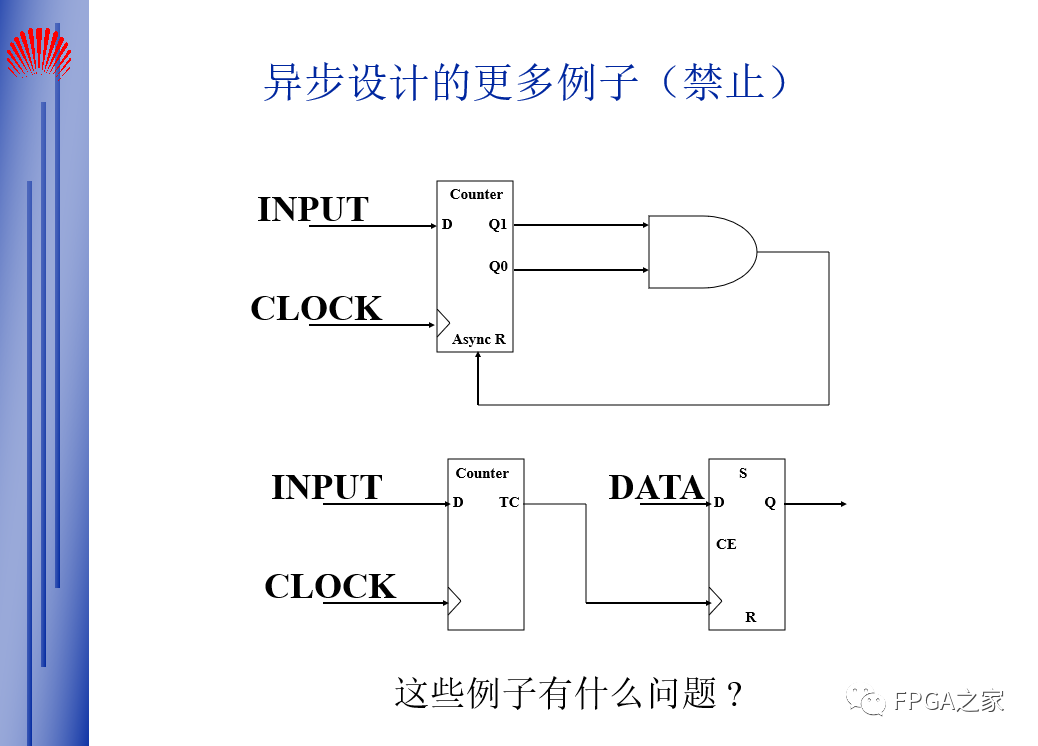

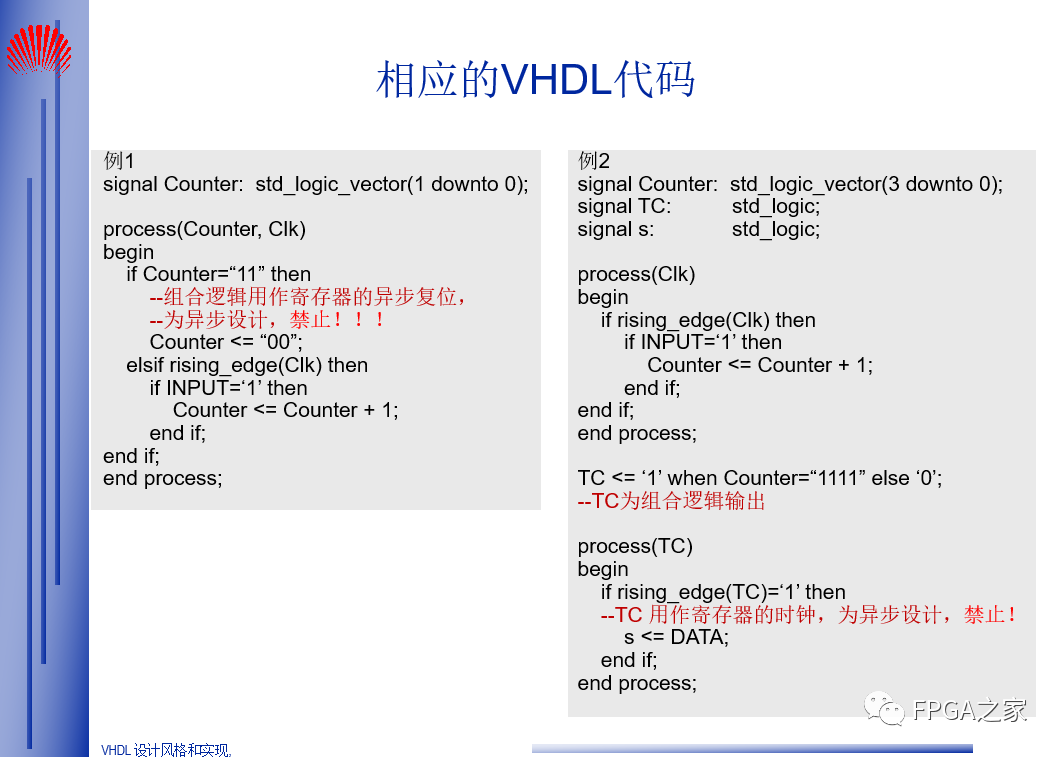

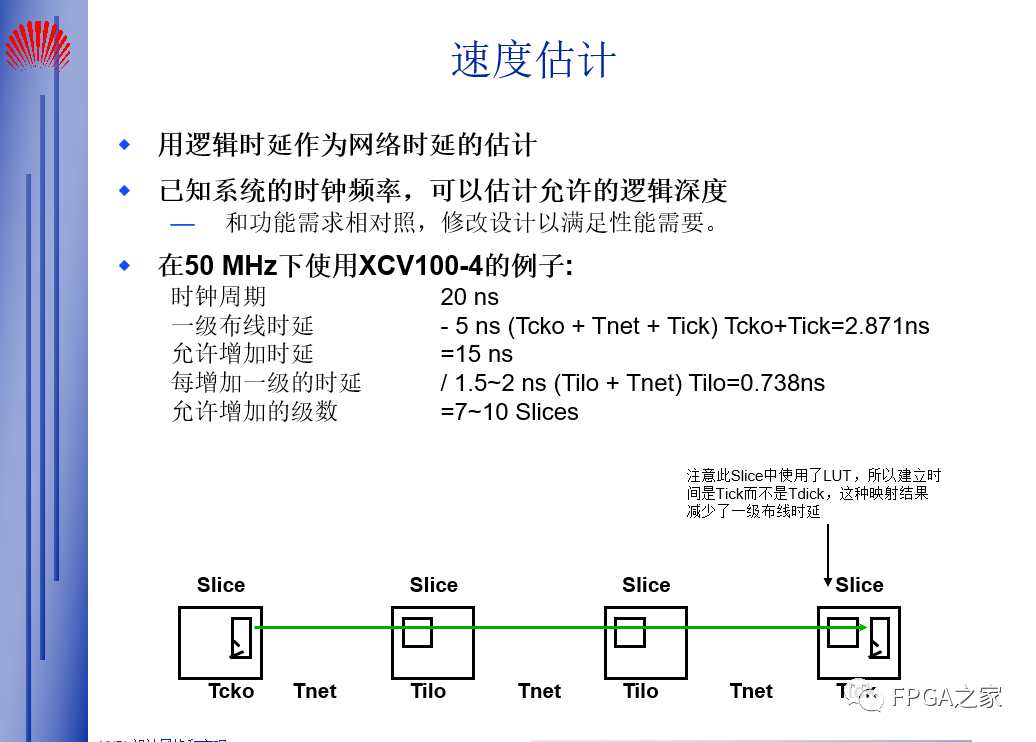

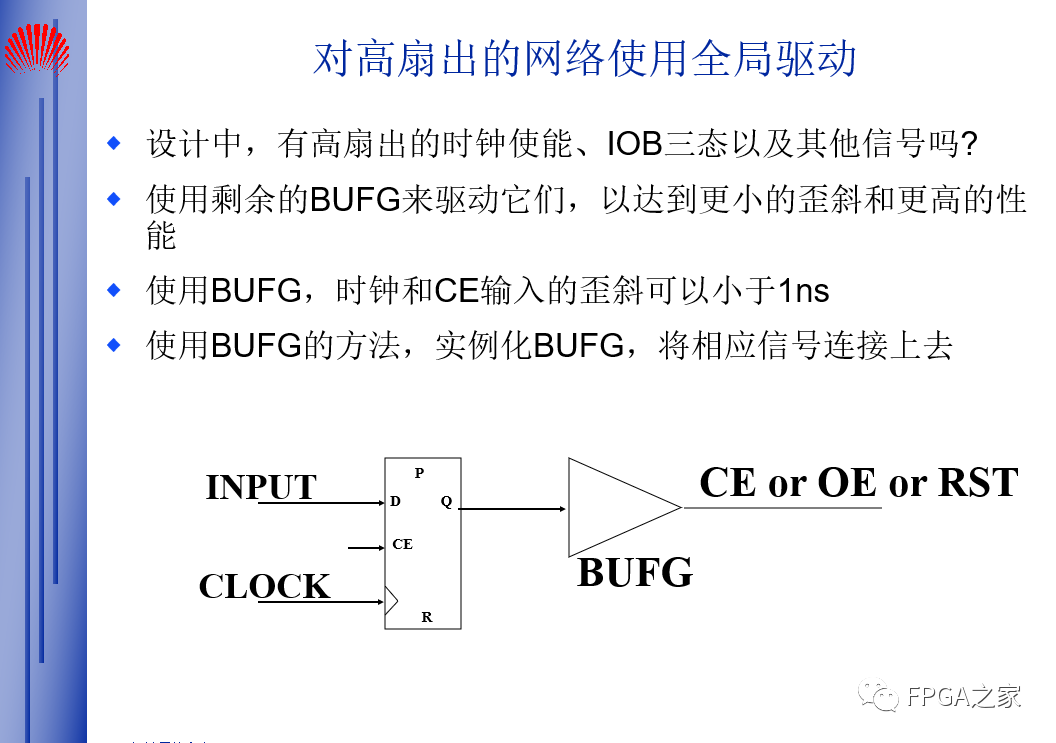

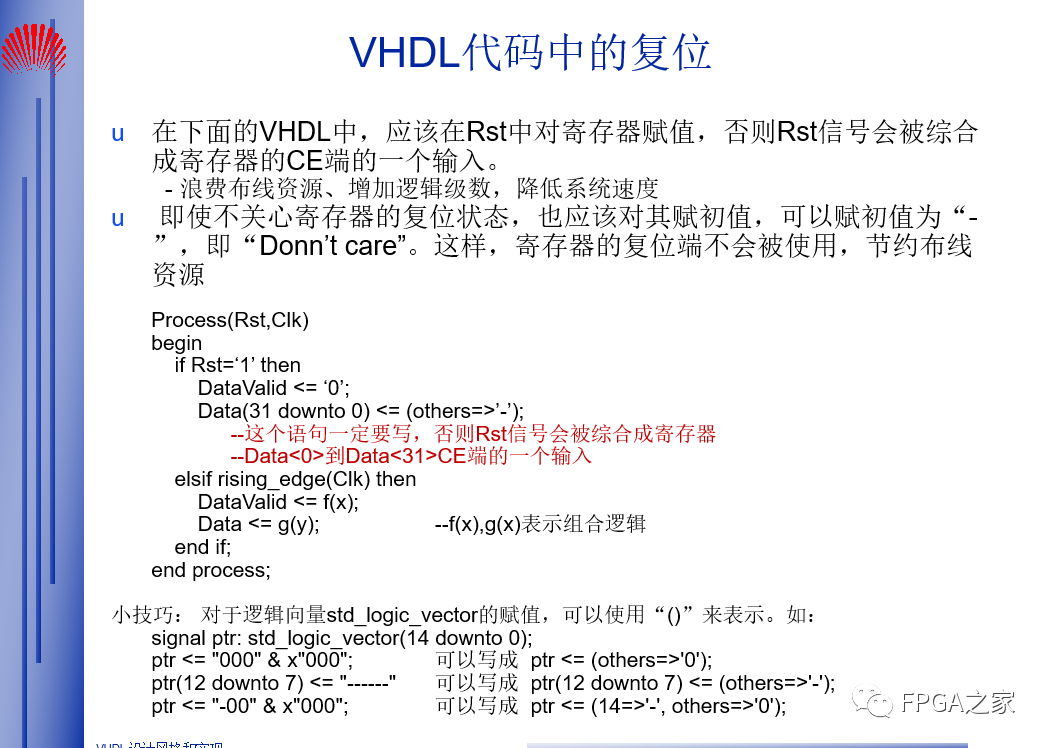

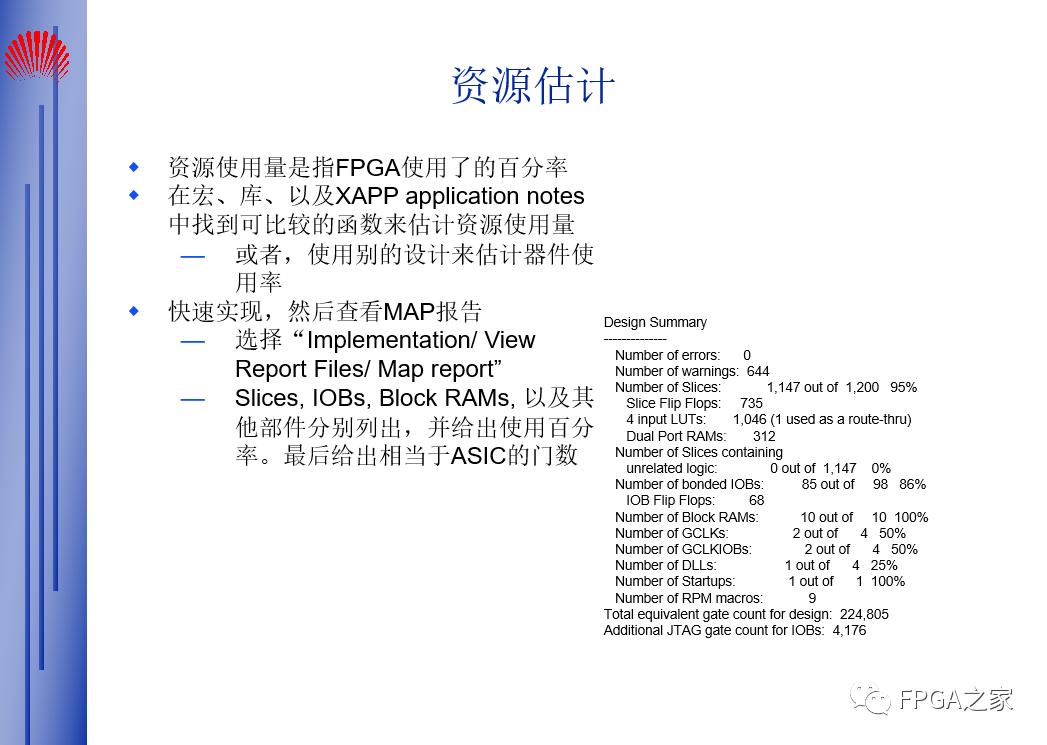

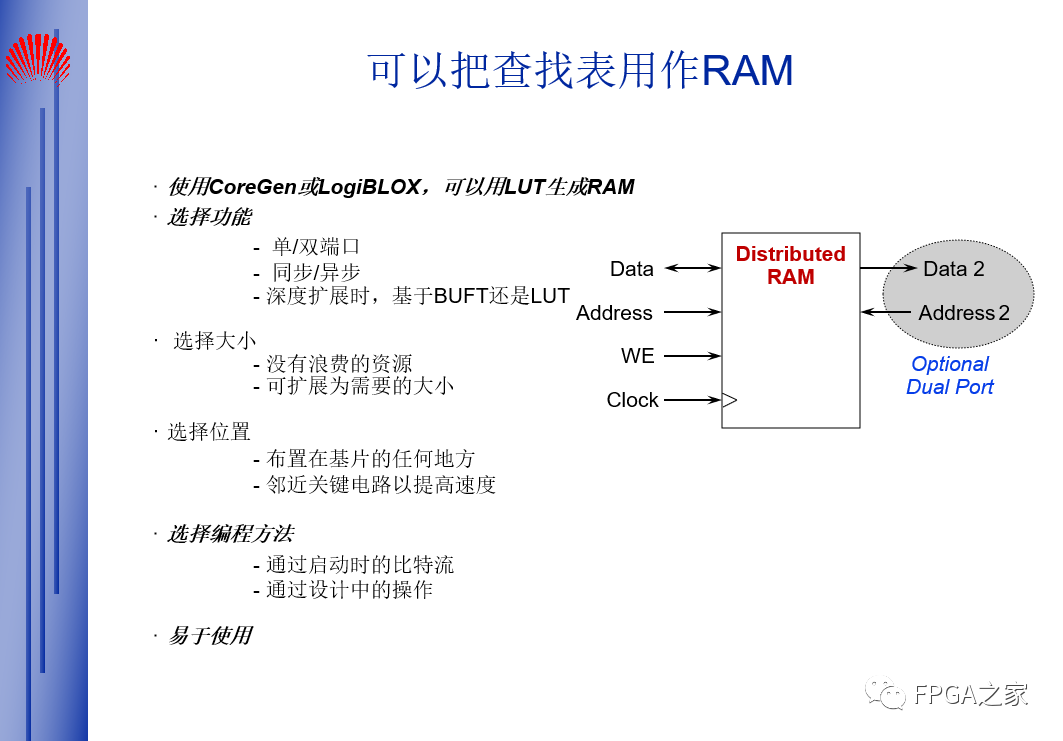

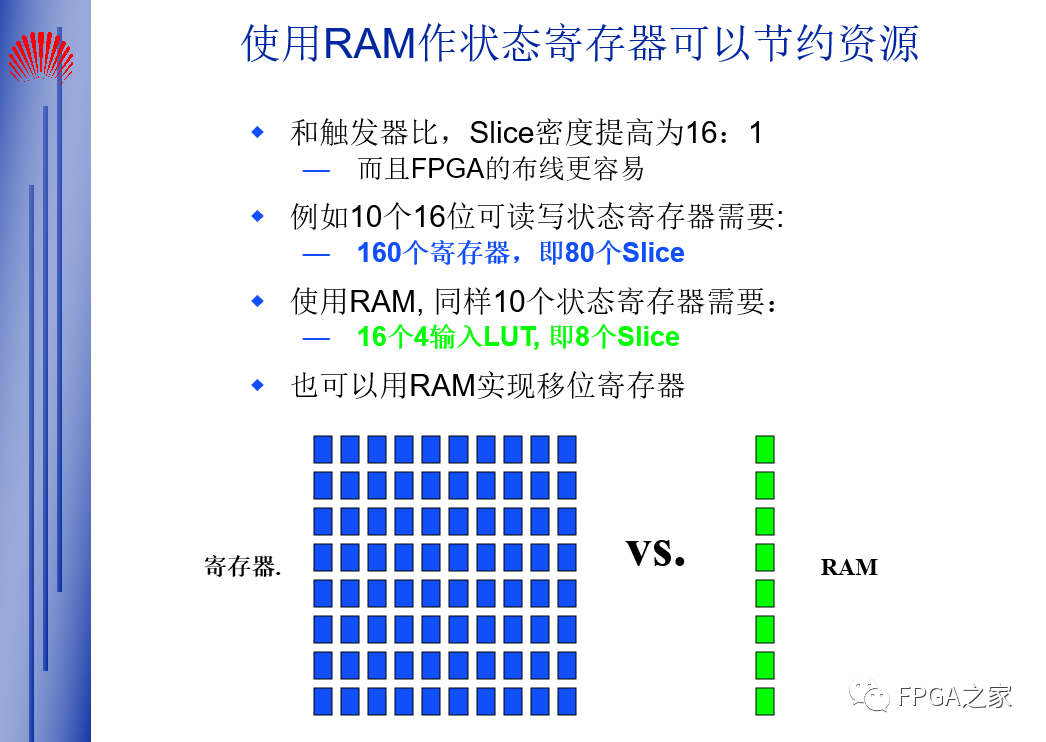

28FPGA的同步設計

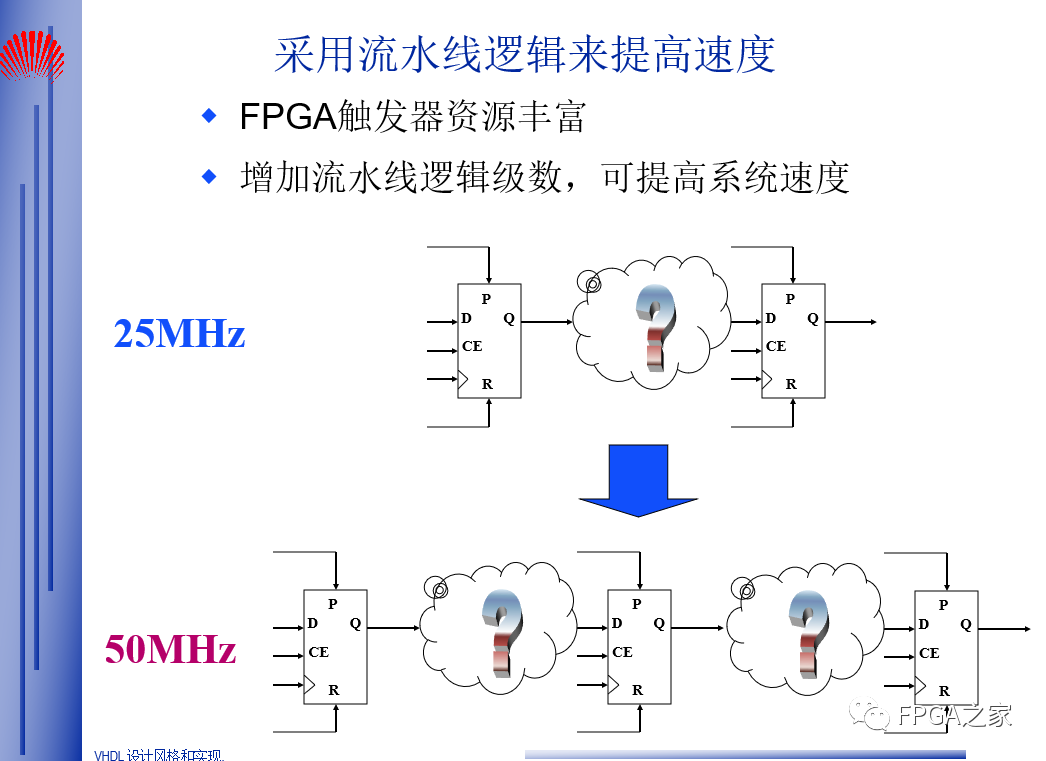

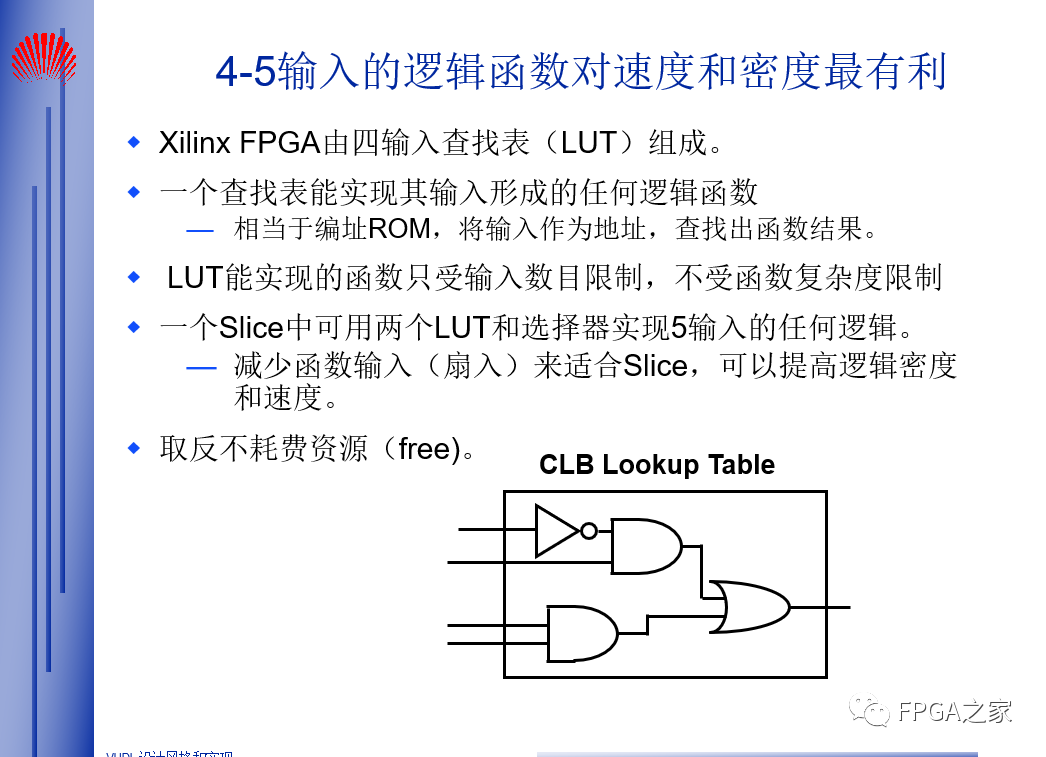

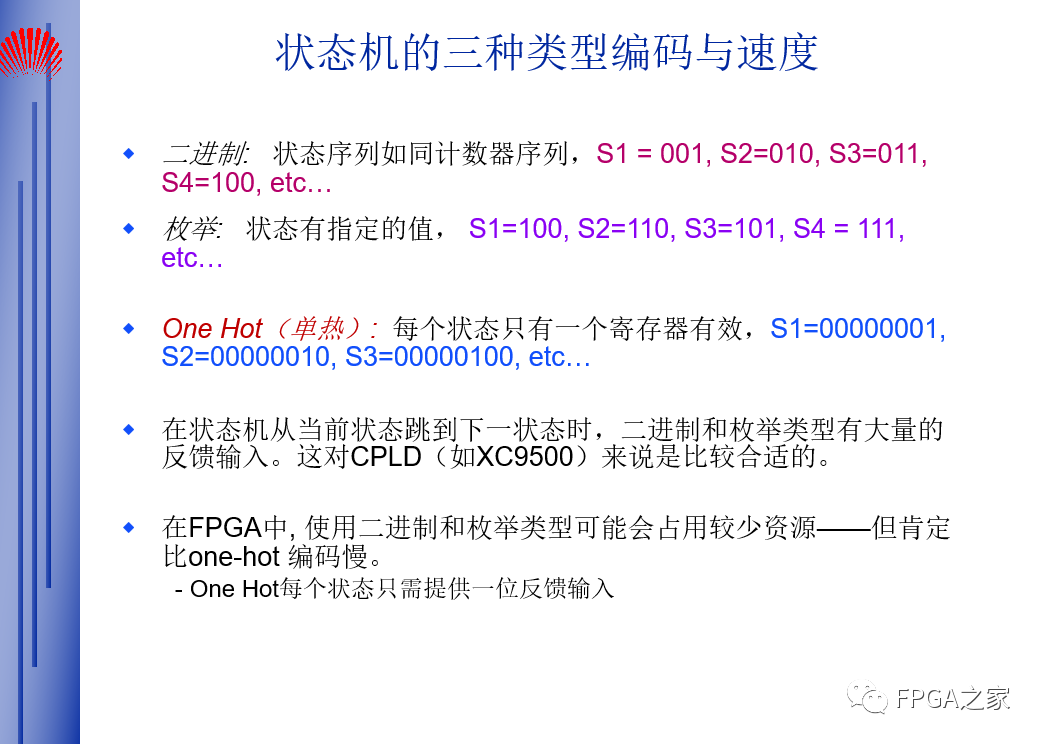

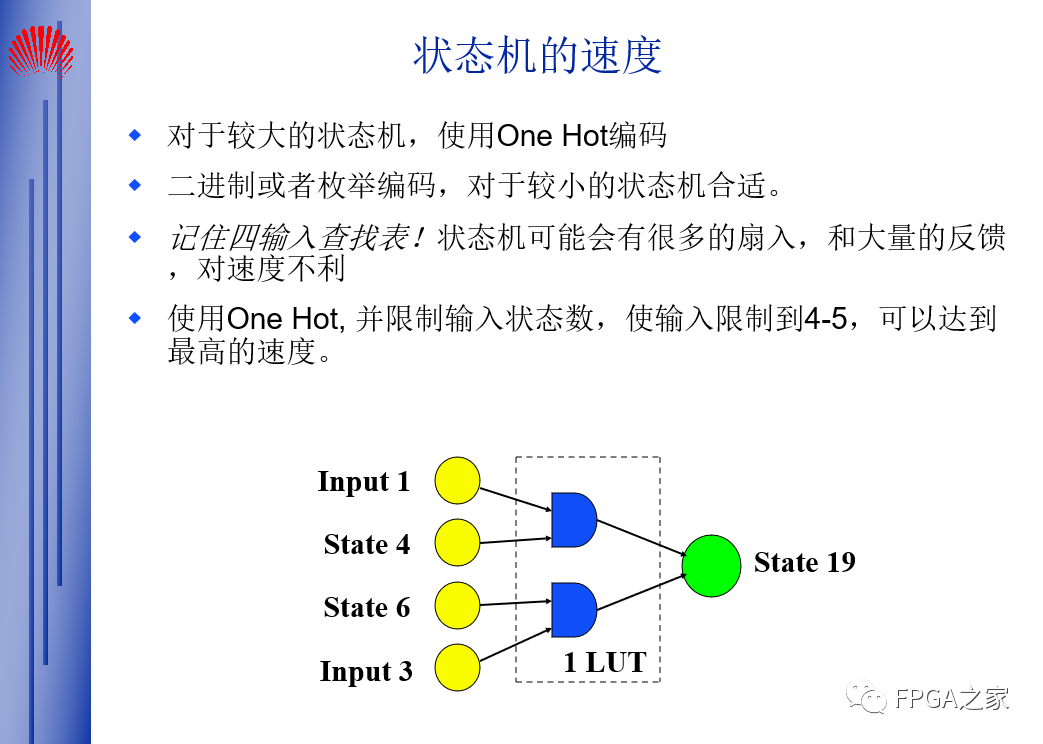

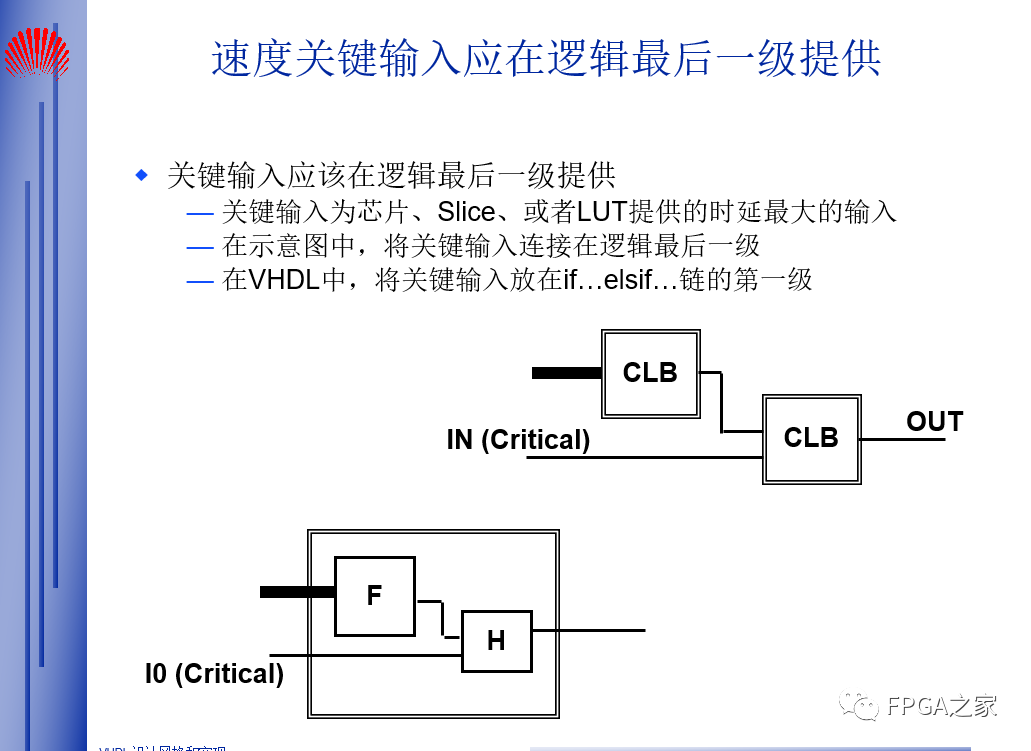

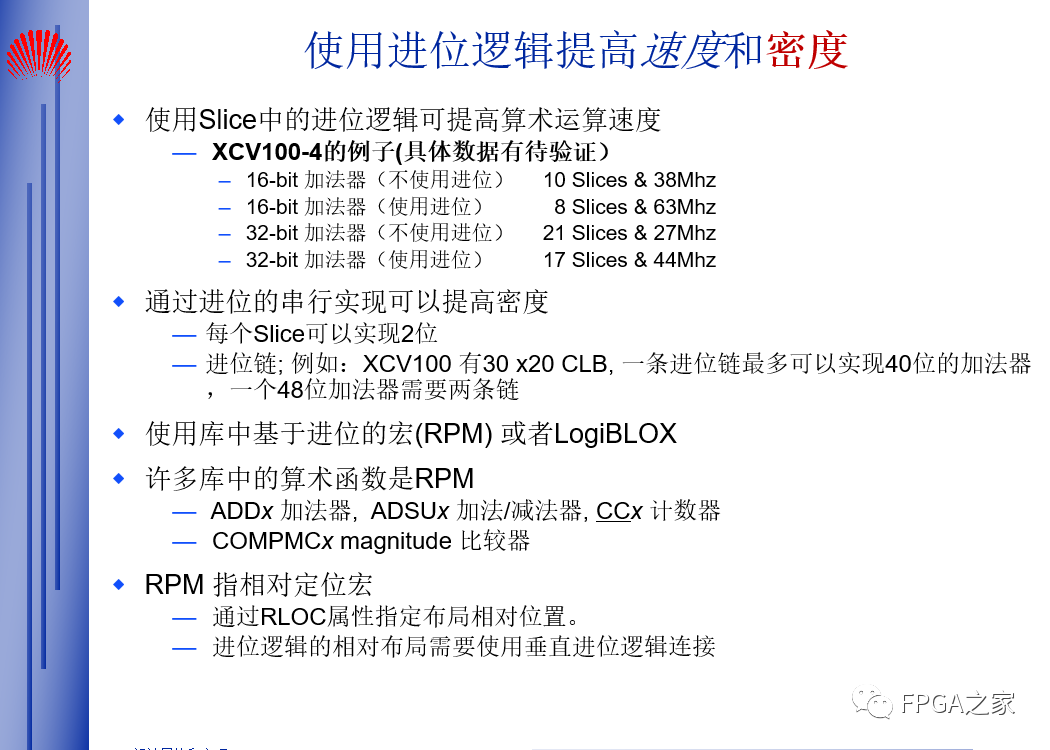

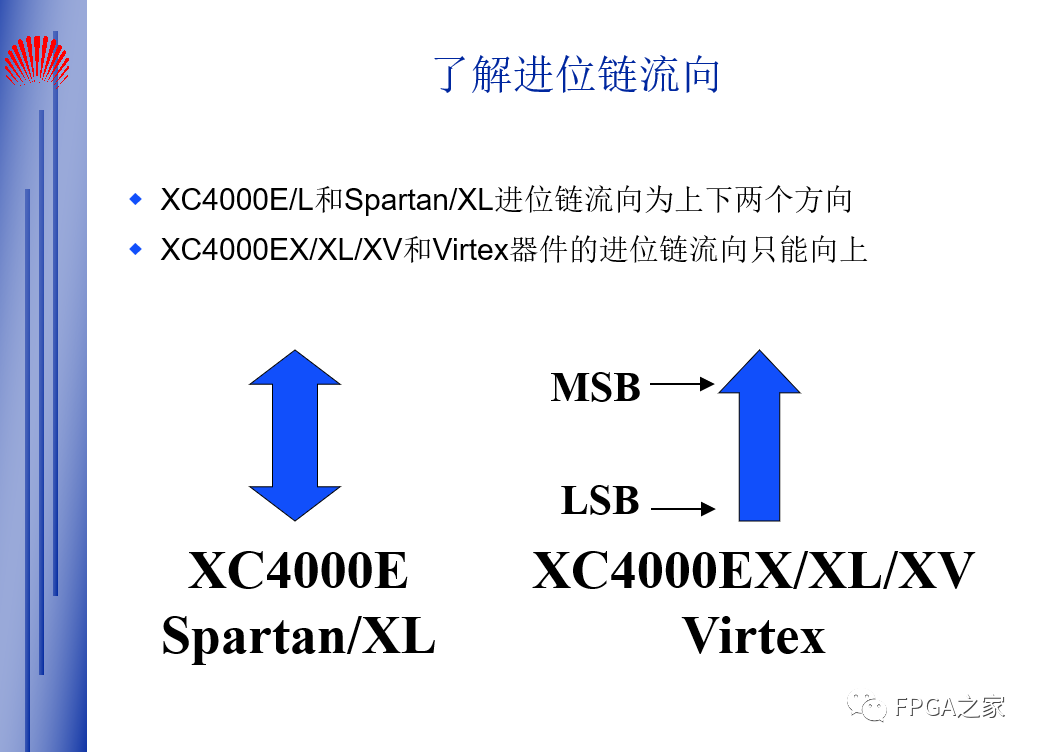

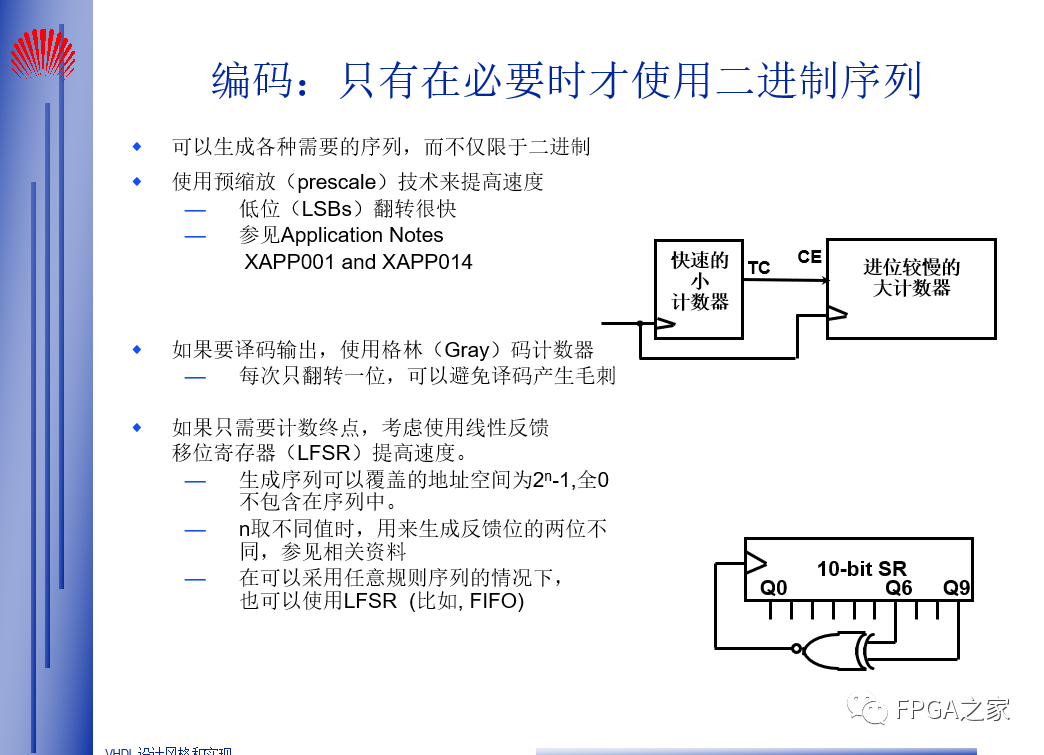

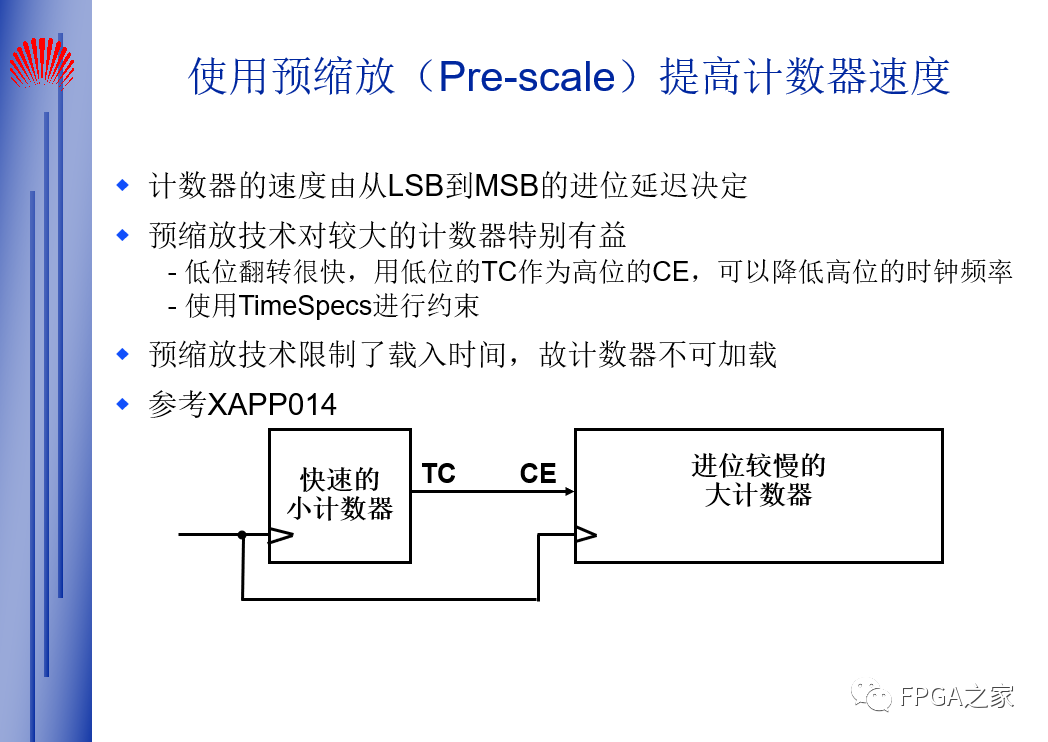

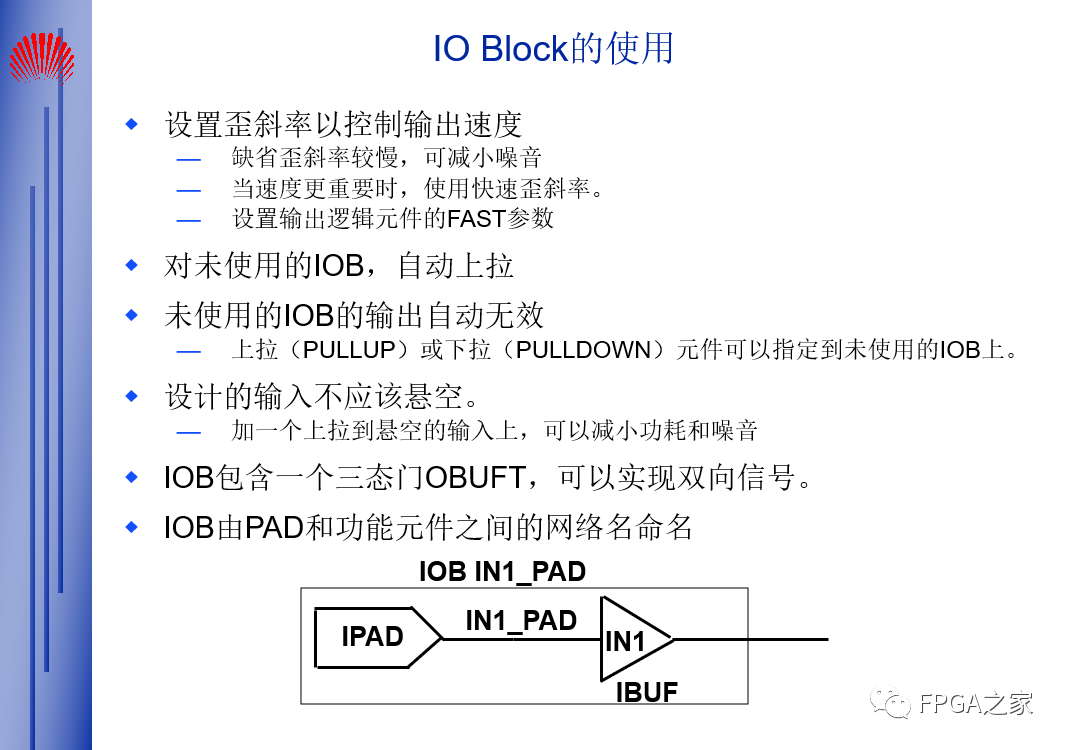

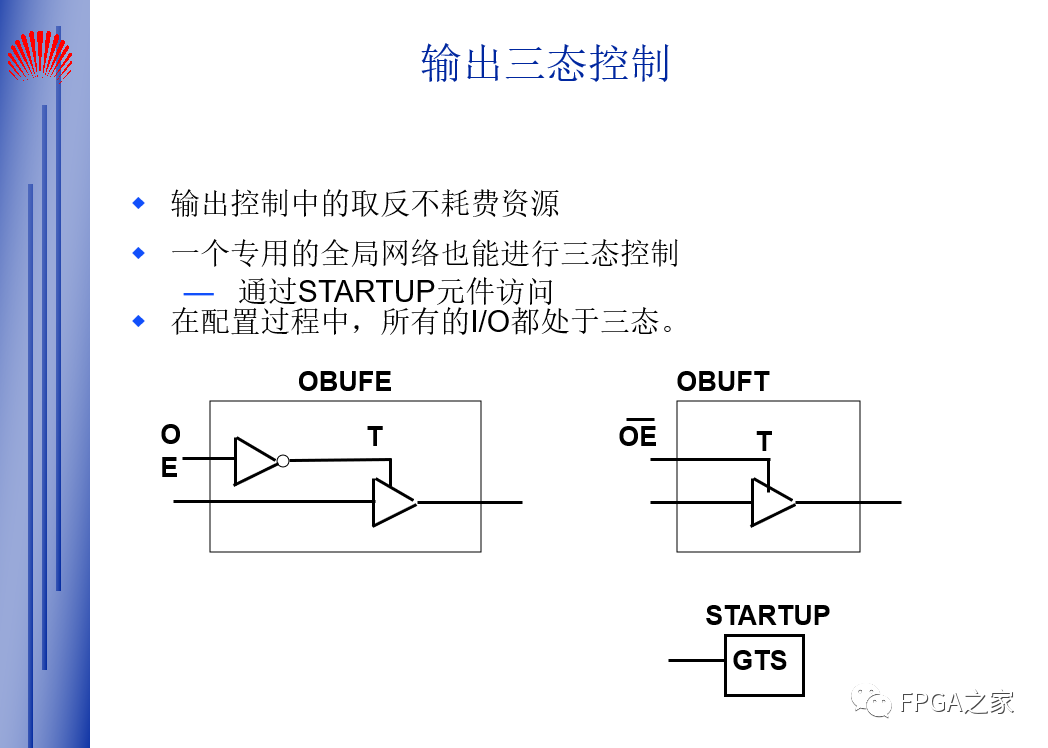

目標完成本單元的學習后你將會:•有效地利用層次•通過采用同步設計技術提高電路可靠性及性能

概覽•層次化設計•Xilinx FPGA的同步設計•總

2010-01-25 08:20:16 33

33

33

33基于FPGA的快速位同步系統設計

從時分復接系統對位同步系統的性能要求出發,提出了一種基于FPGA的快速位同步系統的設計方案,給出了位同步系統的實驗仿真,結果表明該系統有較快的位同步建立時間,節省了F

2010-07-28 18:13:40 20

20

20

20幀同步系統的FPGA設計

從時分復接系統對幀同步系統的性能要求出發,提出了一種采用FPGA實現幀同步系統的設計方案,重點介紹了同步保護電路的設計,并給出了FPGA設計的實驗仿真,實驗結果表明該電路

2010-08-06 16:46:59 24

24

24

24基于FPGA的新型高性能永磁同步電機驅動系統設計

為了研制高性能的全數字永磁同步電機驅動系統,本文提出了一種基于FPGA的單芯片驅動控制方案。它采用硬件模塊化的現代EDA設計方法,使用VHDL硬件描述語言,實現了永磁同步電機

2010-10-15 09:43:46 35

35

35

35基于FPGA的光纖通信系統中幀同步頭檢測設計

為實現設備中存在的低速數據光纖通信的同步復接/ 分接,提出一種基于FPGA 的幀同步頭信號提取檢測方案,其中幀頭由7 位巴克碼1110010 組成,在數據的接收端首先從復接數據中

2010-10-26 16:56:54 46

46

46

46基于FPGA的多通道同步數據采集存儲系統

設計一種基于FPGA的多通道同步數據采集存儲系統,分為多通道同步數據采集模塊和數據存儲模塊。系統設計采用多通道數據的同步實時采集以及壞塊檢測技術。多通道同步數據采集

2010-12-27 15:31:33 70

70

70

70基于FPGA的提取位同步時鐘DPLL設計

基于FPGA的提取位同步時鐘DPLL設計

在數字通信系統中,同步技術是非常重要的,而位同步是最基本的同步。位同步時鐘信號不僅用于監測輸入碼元信號,確保收發

2010-01-25 09:36:18 2890

2890

2890

2890

一種高速幀同步和相位模糊估計的方法及其FPGA實現

一種高速幀同步和相位模糊估計的方法及其FPGA實現

摘要:提出僅依靠接收符號和本地同步碼快速確定MPSK調制符號的幀同步,并同時估計其相位模糊值的計算方法,給

2010-01-27 09:38:17 1278

1278

1278

1278

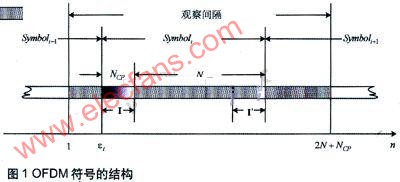

基于802.16d的定時同步算法改進及FPGA實現

基于802.16d的定時同步算法改進及FPGA實現

0 引言

WiMAX ( Wordwide Interoperability for Mi-crowave Access)是代表空中接口滿足IEEE 802.16標準的寬帶無線通信系統。其

2010-02-22 09:38:31 844

844

844

844

利用FPGA的永磁同步電機控制器原理及設計

利用FPGA的永磁同步電機控制器原理及設計

概述:提出一種基于FPGA的永磁同步電機控制器的設計方案,該設計可應用于具有高動態性能要求的永磁同

2010-03-17 11:43:08 2951

2951

2951

2951

基于循環前綴的同步算法及FPGA實現

基于循環前綴的同步算法及FPGA實現

正交頻分復用(OrthogonalFrequency Division Multiplexing,OFDM)技術已經成為第四代移動通信研究的熱點,同時,OFDM同步又是OFDM的關鍵技

2010-03-23 09:27:48 1530

1530

1530

1530

FPGA上同步開關噪聲的分析

FPGA上同步開關噪聲的分析

概述

隨著半導體技術的快速發展,近年來FPGA 的器件容量和輸入輸出的管腳數量都極大的增加了,例如StratixIV 器件,最大的

2010-04-12 15:09:35 2999

2999

2999

2999

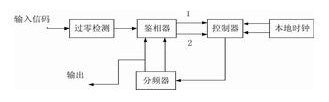

FPGA的時鐘頻率同步設計

FPGA的時鐘頻率同步設計

網絡化運動控制是未來運動控制的發展趨勢,隨著高速加工技術的發展,對網絡節點間的時間同步精度提出了更高的要求。如造紙機械,運行速

2010-01-04 09:54:32 2762

2762

2762

2762

基于VHDL和FPGA的非對稱同步FIFO設計實現

本文采用VHDL描述語言,充分利用Xilinx公司Spartan II FPGA的系統資源,設計實現了一種非對稱同步FIFO,它不僅提供數據緩沖,而且能進行數據總線寬度的轉換。

2011-01-13 11:33:43 1744

1744

1744

1744光纖縱差保護同步接口的FPGA實現

摘要:同步接口是光纖縱差保護裝置的重要組成部分,本文介紹了Cyclone II FPGA 在光纖縱差保護同步接口中的應 用,詳細地闡述了FPGA 實現光纖縱差保護同步通信接口的原理。大規模可編

2011-04-06 16:42:11 40

40

40

40WCDMA主同步的FPGA實現

本文闡述了主同步搜索的改進型算法,并且針對這種算法提出了基于片上RAM 的實現方式,最大程度地節省了FPGA 的硬件資源,為WCDMA 同步的FPGA 實現提供了很好的解決方案。這種技術可

2011-05-14 16:45:53 30

30

30

30導頻疊加OFDM同步方法的FPGA實現

導頻疊加OFDM同步方法的FPGA實現,目前正交頻分復用(OFDM)技術已經成為第四代移動通信研究的熱點,同時OFDM同步又是OFDM的關鍵技術

2012-02-20 15:15:39 1765

1765

1765

1765

基于ARM和FPGA的時間同步儀控制單元設計

本文以時間同步儀的功能為出發點,設計了基于ARM和FPGA的控制系統,該系統以ARM芯片S3C2440A為控制核心,在FPGA芯片XCS30的輔助控制下,完成了時間同步儀的人機交互、參數設定、電文處

2012-05-25 14:33:54 41

41

41

41高階QAM定時同步算法的MATLAB仿真及FPGA實現

本文針對128 QAM調制信號,設計了定時同步算法結構,并且用MATLAB做了仿真驗證,最后在FPGA平臺上實現了該算法。

2012-11-23 11:15:17 5895

5895

5895

5895基于ARM/FPGA的高速多通道同步數據采集解決方案(恒頤)

恒頤基于ARM+FPGA的高速同步數據采集方案,解決了數據采集的同步性問題,與以往的數據采集方案相比,具有高精度、高速率、多參數同步測量、實時處理、網絡傳輸不受區域限制等特點

2012-11-27 10:51:24 1198

1198

1198

1198基于FPGA的跳頻系統快速同步算法設計與實現

同步技術是跳頻系統的核心。本文針對FPGA的跳頻系統,設計了一種基于獨立信道法,同步字頭法和精準時鐘相結合的快速同步方法,同時設計了基于雙圖案的改進型獨立信道法,同步算

2013-05-06 14:09:20 22

22

22

22Altera全球同步推出10代FPGA和SoC

Altera于6月11日在北京宣布,全球同步推出10代FPGA和SoC。先行發布的包括高端Stratix10和中端Arria10系列。目標是替代傳統的ASSP和ASIC。

2013-06-13 14:26:14 2150

2150

2150

2150基于FPGA的同步器信號采集技術研究

針對航空測試中常用的同步器信號,提出一種基于嵌入式系統的雙通道同步器信號采集系統。系統以同步器專用芯片對信號進行預處理,解析出數字量的角度和角速率,以FPGA為控制器進行數據處理,實現兩路角度和角速率測量功能。經過仿真實驗和系統調試,結果表明此系統能夠穩定高效的采集和處理同步器信號。

2015-12-04 15:03:44 0

0

0

0采用FPGA實現同步、幀同步系統的設計

為了能在GPS接收端獲取正確導航電文,研究了CJPS接收機位同步、幀同步的基本原理和實現方式。提出一種采用FPGA來實現位同步、幀同步系統的設計方案。使用Xilinx開發軟件,通過Verilog代碼

2017-11-07 17:13:39 10

10

10

10基于FPGA的高精度同步時鐘系統設計

介紹了精密時鐘同步協議(PTP)的原理。本文精簡了該協議,設計并實現了一種低成本、高精度的時鐘同步系統方案。該方案中,本地時鐘單元、時鐘協議模塊、發送緩沖、接收緩沖以及系統打時標等功能都在FPGA

2017-11-17 15:57:18 6196

6196

6196

6196

FPGA設計中的異步復位同步釋放問題

異步復位同步釋放 首先要說一下同步復位與異步復位的區別。 同步復位是指復位信號在時鐘的上升沿或者下降沿才能起作用,而異步復位則是即時生效,與時鐘無關。異步復位的好處是速度快。 再來談一下為什么FPGA設計中要用異步復位同步釋放。

2018-06-07 02:46:00 1989

1989

1989

1989Xilinx FPGA的同步復位和異步復位

對于xilinx 7系列的FPGA而言,flip-flop支持高有效的異步復/置位和同步復位/置位。對普通邏輯設計,同步復位和異步復位沒有區別,當然由于器件內部信號均為高有效,因此推薦使用高有效的控制信號,最好使用高有效的同步復位。輸入復位信號的低有效在頂層放置反相器可以被吸收到IOB中。

2018-07-13 09:31:00 6091

6091

6091

6091如何利用FPGA設計一個跨時鐘域的同步策略?

基于FPGA的數字系統設計中大都推薦采用同步時序的設計,也就是單時鐘系統。但是實際的工程中,純粹單時鐘系統設計的情況很少,特別是設計模塊與外圍芯片的通信中,跨時鐘域的情況經常不可避免。如果對跨時鐘

2018-09-01 08:29:21 5302

5302

5302

5302

基于FPGA實現電路的同步提取性能設計

一般的位同步電路大多采用標準邏輯器件按傳統數字系統設計方法構成,具有功耗大,可靠性低的缺點。用FPGA設計電路具有很高的靈活性和可靠性,可以提高集成度和設計速度,增強系統的整體性能。本文給出了一種基于fpga的數字鎖相環位同步提取電路。

2019-04-19 08:24:00 3113

3113

3113

3113

如何使用FPGA進行兩路視頻同步播放系統的設計

為了實現基于嵌入式系統的兩路視頻的同步播放控制,本文提出了根據圖像內容檢測達到兩路視頻同步播放控制的設計思想。根據該思想設計了基于FPGA 的實驗電路,構建了完整的系統實驗硬件平臺。該系統平臺的建立,證明了基于嵌入式電路的以圖像內容檢測為手段的兩路圖像同步播放控制的可行性。

2018-11-06 19:35:28 7

7

7

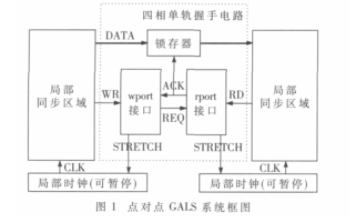

7關于FPGA的全局異步局部同步四相單軌握手協議實現

在常規FPGA中設計了基于LUT的異步狀態保持單元,實現了全局異步局部同步系統的接口電路、時鐘暫停電路,進一步完

2021-05-26 18:12:38 3436

3436

3436

3436

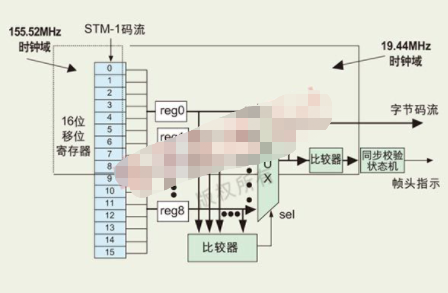

基于EP1C6T144C8 FPGA實現STM-1同步系統的應用方案

,首先要從同步數據流中提取幀同步信息,幀同步提取性能的優劣直接影響整個數據的處理質量與整個系統的性能。使用FPGA技術可以實現同步系統的模塊化、小型化和芯片化,得到穩定可靠的幀同步器。

2021-06-23 15:44:00 2451

2451

2451

2451

ARM+FPGA的高速同步數據采集

著較高的要求,并且大多情況下要求多參數同步測量。飛旭公司在基于實際的工程項目成功的基礎上,推出了基于ARM+FPGA的低功耗、高速率、高精度、多通道同步數據采集方案,可以通過監測者的要求完成多通道數據的同步采集并實現實時的網絡傳輸。 ?

2023-02-10 17:50:01 1091

1091

1091

1091fpga與dsp通訊怎樣同步時鐘頻率?dsp和fpga通信如何測試?

fpga與dsp通訊怎樣同步時鐘頻率?dsp和fpga通信如何測試? 在FPGA與DSP通訊時,同步時鐘頻率非常重要,因為不同的設備有不同的時鐘頻率,如果兩者的時鐘頻率不同步,會導致通訊數據的錯誤

2023-10-18 15:28:13 1060

1060

1060

1060 電子發燒友App

電子發燒友App

評論