算法的原理,然后帶大家使用FPGA來(lái)實(shí)現(xiàn)(C語(yǔ)言實(shí)現(xiàn)過(guò)程特別簡(jiǎn)單)。 二. PID算法 PID取自比例、積分、微分三個(gè)英文字母的首字母。意味著算法由這三部分組成。 1. P 比例 ????運(yùn)算過(guò)程為 期望值 減去 當(dāng)前值 ,然后再乘上一個(gè)p系數(shù),就得到了一個(gè)反

2023-07-20 09:23:12 1220

1220

PID算法資料,供大家學(xué)習(xí)!

2014-07-26 22:14:40

解決的最基本問(wèn)題,既系統(tǒng)的穩(wěn)定性、快速性和準(zhǔn)確性。調(diào)節(jié)PID的參數(shù),可實(shí)現(xiàn)在系統(tǒng)穩(wěn)定的前提下,兼顧系統(tǒng)的帶載能力和抗擾能力,同時(shí),在PID調(diào)節(jié)器中引入積分項(xiàng),系統(tǒng)增加了一個(gè)零積點(diǎn),使之成為一階或一階以上

2016-03-23 10:10:07

在自動(dòng)控制中,PID及其衍生出來(lái)的算法是應(yīng)用最廣的算法之一。各個(gè)做自動(dòng)控制的廠家基本都有會(huì)實(shí)現(xiàn)這一經(jīng)典算法。我們?cè)谧鲰?xiàng)目的過(guò)程中,也時(shí)常會(huì)遇到類似的需求,所以就想實(shí)現(xiàn)這一算法以適用于更多的應(yīng)用場(chǎng)

2021-12-21 08:22:06

目錄一. 緒論二. 角度環(huán)串級(jí)PID原理1. PID基本算法2. 姿態(tài)角串級(jí)PID原理三. 如何用STM32實(shí)現(xiàn)角度-角速度的串級(jí)PID控制1. PID算法的代碼實(shí)現(xiàn)2. 串級(jí)PID算法的代碼實(shí)現(xiàn)四

2021-08-17 06:44:18

一 PID 算法原理在工業(yè)應(yīng)用中 PID 及其衍生算法是應(yīng)用最廣泛的算法之一,是當(dāng)之無(wú)愧的萬(wàn)能算法,如果能夠熟練掌握 PID 算法的設(shè)計(jì)與實(shí)現(xiàn)過(guò)程,對(duì)于一般的研發(fā)人員來(lái)講,應(yīng)該是足夠應(yīng)對(duì)一般研發(fā)

2022-02-09 07:56:11

一個(gè)PID控制的詳解資料,完整的在下面鏈接下載PID控制簡(jiǎn)介PID( Proportional Integral Derivative)控制是最早發(fā)展起來(lái)的控制策略之一,由于其算法簡(jiǎn)單、魯棒性好

2016-01-20 15:17:28

本帖最后由 張飛電子學(xué)院郭嘉 于 2021-3-11 17:37 編輯

PID控制詳解PID控制簡(jiǎn)介PID( Proportional Integral Derivative)控制是最早

2021-01-25 17:19:51

`在自動(dòng)控制中,PID及其衍生出來(lái)的算法是應(yīng)用最廣的算法之一。各個(gè)做自動(dòng)控制的廠家基本都有會(huì)實(shí)現(xiàn)這一經(jīng)典算法。我們?cè)谧鲰?xiàng)目的過(guò)程中,也時(shí)常會(huì)遇到類似的需求,所以就想實(shí)現(xiàn)這一算法以適用于更多的應(yīng)用場(chǎng)

2018-04-21 16:58:59

、ourdevBasic PID的經(jīng)典文章、PID測(cè)速、由入門到精通-吃透PID2.0版、容易理解的PID等相關(guān)PID電機(jī)控制內(nèi)容,從PID控制原理延伸到位置式和增量式的PID算法,以及控制器參數(shù)整定的三大方

2019-03-18 14:18:02

:System Generator for DSP(SysGen)的許可證簽出失敗。無(wú)法聯(lián)系Xilinx許可證管理器。請(qǐng)檢查以下內(nèi)容:(1

2019-01-28 07:16:36

錯(cuò)誤:System Generator for DSP(SysGen)的許可證簽出失敗。無(wú)法聯(lián)系Xilinx許可證管理器。請(qǐng)檢查以下內(nèi)容:(1)XILINX環(huán)境變量指向有效的ISE安裝(2

2018-12-29 10:35:12

FPGA中的數(shù)字控制器是什么?System Generator中的PID控制器是如何設(shè)計(jì)的?

2021-04-08 06:51:46

大家好,這是我第一次使用System Generator工具,如果有人能夠解決一個(gè)不讓我繼續(xù)參與我的硬件協(xié)同仿真項(xiàng)目的問(wèn)題,我想。我正在使用Matlab R2013b,Xilinx ISE 14.7

2020-03-23 06:53:11

根據(jù)我的理解,System Generator是MatLab到RTL的轉(zhuǎn)換,因此不包括Vivado的優(yōu)化過(guò)程。問(wèn)題1--是真的。確實(shí),Vivado中的優(yōu)化將大大改變系統(tǒng)描述,而系統(tǒng)描述不會(huì)向后兼容

2019-04-25 12:47:45

快速浮_定點(diǎn)PID控制器FPGA的研究與實(shí)現(xiàn)提出了基于 的快速 控制器技術(shù),采用流水線運(yùn)算方法,具有高速 穩(wěn)定精確的實(shí)時(shí)控制性能,實(shí)現(xiàn)了速度和資源的優(yōu)化匹配研究并分析了位置式 不同算式的特點(diǎn),完成

2012-08-11 15:58:43

算法篇(PID詳解)

2020-05-19 10:30:59

本帖最后由 richthoffen 于 2019-7-19 16:41 編輯

詳解快速傅里葉變換FFT算法

2019-07-18 08:07:33

詳解快速傅里葉變換FFT算法

2020-03-28 11:48:16

詳解快速傅里葉變換FFT算法

2020-05-25 09:31:30

詳解快速傅里葉變換FFT算法

2021-03-05 11:07:32

/sysgen.htmhttp://www.sogou.com/sogou?query=+Xilinx+System+Generator+for+DSP&pid=AWTo5-0000System

2013-10-05 11:59:34

翻譯成verilog,在FPGA里面實(shí)現(xiàn),即system generator。altera有沒(méi)有類似的接口,與matlab可以互連,直接在matlab里設(shè)計(jì)我所需要的算法,在翻譯成verilog?

2015-01-14 14:20:50

協(xié)仿真8.4.1 硬件協(xié)仿真平臺(tái)的介紹與平臺(tái)安裝8.4.2 硬件協(xié)仿真的基本操作8.4.3 共享存儲(chǔ)器的操作8.5 System Generator的高級(jí)應(yīng)用8.5.1 導(dǎo)入外部的HDL程序模塊

2012-04-24 09:23:33

針對(duì)實(shí)現(xiàn)DSP的設(shè)計(jì)軟件—System Generator。在使用FPGA為原型平臺(tái)運(yùn)行算法時(shí),它不僅能夠?qū)?b class="flag-6" style="color: red">硬件的真實(shí)情況進(jìn)行仿真,還能夠自動(dòng)生成硬件實(shí)現(xiàn)所需要的硬件描述語(yǔ)言代碼。與語(yǔ) 言設(shè)計(jì)相比

2019-06-21 06:25:23

什么是PID控制算法?PID控制算法C語(yǔ)言是如何實(shí)現(xiàn)的?特殊情況下的控制算法該如何去調(diào)整?比例、積分、微分三個(gè)環(huán)節(jié)的控制作用分別是什么?

2021-06-29 09:24:32

什么是AES算法?如何對(duì)AES算法進(jìn)行優(yōu)化?怎樣快速實(shí)現(xiàn)AES算法?

2021-04-28 06:51:19

使用system generator導(dǎo)入xilinx模塊時(shí),只要連線兩個(gè)模塊,matlab就崩潰,有知道原因的大佬嗎?

2018-01-19 17:54:57

前文對(duì)PID算法離散化和增量式PID算法原理進(jìn)行來(lái)探索,之后又使用Matlab進(jìn)行了仿真實(shí)驗(yàn),對(duì)PID三個(gè)參數(shù)又有了更深入的認(rèn)識(shí),接下來(lái)我們來(lái)使用C語(yǔ)言進(jìn)行PID算法實(shí)現(xiàn),并且結(jié)合控制電機(jī)的項(xiàng)目來(lái)

2021-09-15 09:20:04

前文對(duì)PID算法離散化和增量式PID算法原理進(jìn)行來(lái)探索,之后又使用Matlab進(jìn)行了仿真實(shí)驗(yàn),對(duì)PID三個(gè)參數(shù)又有了更深入的認(rèn)識(shí),接下來(lái)我們來(lái)使用C語(yǔ)言進(jìn)行PID算法實(shí)現(xiàn),并且結(jié)合控制電機(jī)的項(xiàng)目來(lái)深入學(xué)習(xí)。

2021-09-16 09:11:08

.Vivado 2016.4與Spartan-6不兼容。據(jù)Xilinx稱,Vivado不支持任何早于7系列的設(shè)備系列。)根據(jù)以下說(shuō)明,Xilinx System Generator可以嵌套在ISE Design

2018-12-27 10:55:34

在自動(dòng)控制中,PID及其衍生出來(lái)的算法是應(yīng)用最廣的算法之一。各個(gè)做自動(dòng)控制的廠家基本都有會(huì)實(shí)現(xiàn)這一經(jīng)典算法。我們?cè)谧鲰?xiàng)目的過(guò)程中,也時(shí)常會(huì)遇到類似的需求,所以就想實(shí)現(xiàn)這一算法以適用于更多的應(yīng)用場(chǎng)

2019-06-11 06:00:00

在system generator中,我把(-128~127),變?yōu)椋?1~1),但是下載到硬件中,使用chipscope抓取到的數(shù)據(jù)確實(shí)(-128~127),請(qǐng)問(wèn)是怎么回事

2016-08-10 15:32:38

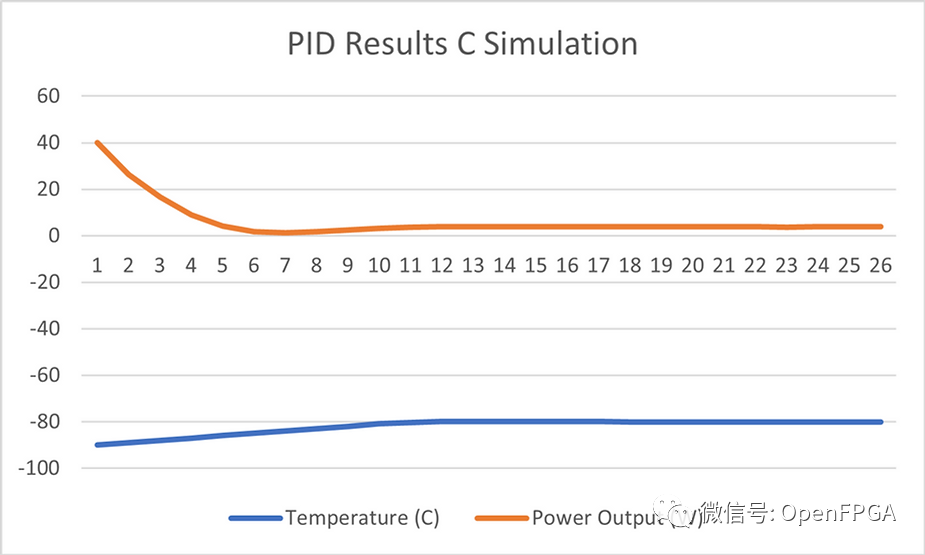

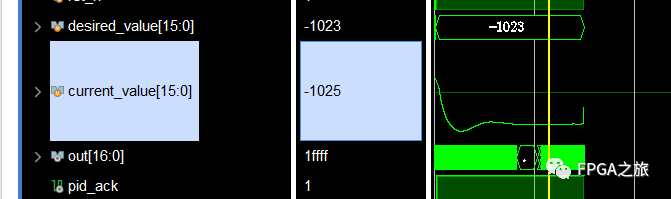

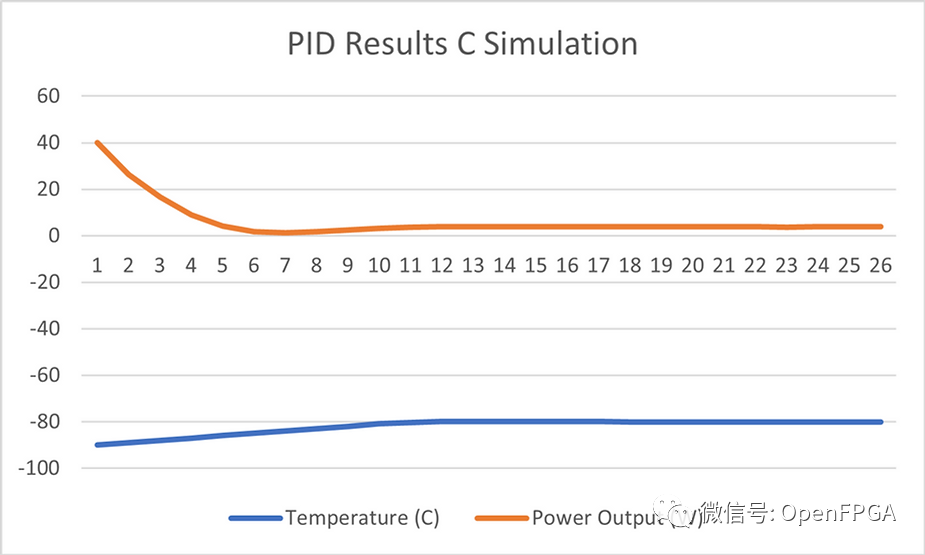

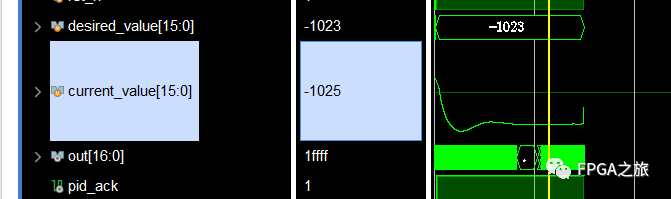

的實(shí)例是使用HLS構(gòu)建我們的PID算法。使用HLS能夠使用浮點(diǎn)或任意精度的定點(diǎn)數(shù)。HLS還能通過(guò)#pragma 快速的為IP添加通用控制接口(AXI)。在純 FPGA 實(shí)現(xiàn)類似系統(tǒng)時(shí)候,我們需要添加軟

2022-10-31 15:53:33

盡快進(jìn)入狀態(tài)。特地分享一些自己如何實(shí)現(xiàn)的過(guò)程。首先說(shuō)說(shuō)增量式PID的公式,這個(gè)關(guān)系到MCU算法公式的書寫,實(shí)際上兩個(gè)公式的寫法是同一個(gè)公式變換來(lái)得,不同的是系數(shù)的差異。資料上比較多的是:還有一種的算法是:這里主要介紹第二種,具體會(huì)分析比例、積分、微分三個(gè)環(huán)節(jié)...

2021-09-13 06:54:20

有做System Generator處理圖像的嗎?遇到一些問(wèn)題,一起商量下

2020-09-28 19:04:58

源:增量式PID的stm32實(shí)現(xiàn),整定過(guò)程 首先說(shuō)說(shuō)增量式PID的公式,這個(gè)關(guān)系到MCU算法公式的書寫,實(shí)際上兩個(gè)公式的寫法是同一個(gè)公式變換來(lái)得,不同的是系數(shù)的差異。 資料上比較多的是: 還有一種

2021-09-13 07:35:35

各位大佬,我在安裝System Generator時(shí),跟著教程走,發(fā)現(xiàn)在vivado中沒(méi)有出現(xiàn)System Generator for DSP這個(gè)選項(xiàng),請(qǐng)問(wèn)是我哪里安裝得不對(duì)嗎?

2023-09-26 21:54:58

當(dāng)我完成SDx 2017.2的安裝時(shí),沒(méi)有安裝System Generator的選項(xiàng)。我正在運(yùn)行從Xilinx下載的安裝程序:https://www.xilinx.com/member/forms

2019-01-07 10:59:00

你好,我叫Joaquín。有人知道,我可以在Matlab / Simulink中使用System Generator創(chuàng)建一個(gè)雙向(inout)端口。我正在嘗試為Xilinx的外部存儲(chǔ)器創(chuàng)建一個(gè)接口

2019-05-09 14:36:24

如何去設(shè)計(jì)一款合理的電子硬件解決方案,從而實(shí)現(xiàn)經(jīng)濟(jì)有效的大規(guī)模生產(chǎn)與部署?怎樣去驗(yàn)證可部署目標(biāo)硬件與軟件算法模型之間的算法性能一致性?System Generator是什么?有什么功能?

2021-04-08 06:25:48

硬件服務(wù)器應(yīng)用程序管理”。所以我認(rèn)為硬件目標(biāo)只是我在當(dāng)前設(shè)計(jì)中使用的Xilinx平臺(tái)電纜。謝謝最好的祝福以上來(lái)自于谷歌翻譯以下為原文Hi, I use KC705 in my design. When

2018-10-30 11:12:37

,是當(dāng)之無(wú)愧的萬(wàn)能算法,如果能夠熟練掌握PID算法的設(shè)計(jì)與實(shí)現(xiàn)過(guò)程,對(duì)于一般的研發(fā)人員來(lái)講,應(yīng)該是足夠應(yīng)對(duì)一般研發(fā)問(wèn)題了,而難能可貴的是,在我所接觸的控制算法當(dāng)中,PID控制算法又是最簡(jiǎn)單,最能體現(xiàn)反饋思想

2020-06-22 11:37:44

有用Xilinx的system generator做圖像處理的嘛?求交流 。我正在用這個(gè)做圖像處理,已經(jīng)用了3個(gè)月了,在做一些算法,遇到一些困難,求一起交流學(xué)習(xí)。發(fā)現(xiàn)用這個(gè)開發(fā)的人真不多啊。

2014-05-09 14:57:21

,誤差較小時(shí)采用模糊PID控制,實(shí)現(xiàn)了2種控制方法的優(yōu)勢(shì)互補(bǔ)。 同時(shí)在此基礎(chǔ)上,給出了Fuzzy PID控制器設(shè)計(jì)、硬件結(jié)構(gòu)和軟件設(shè)計(jì),實(shí)驗(yàn)曲線表明該控制算法可以獲得滿意的控制效果,采用模糊PID控制的效果明顯優(yōu)于常規(guī)PID控制。

2019-05-30 10:38:57

的增量,而不是對(duì)應(yīng)執(zhí)行機(jī)構(gòu)的實(shí)際位置,因此要求執(zhí)行機(jī)構(gòu)必須具有對(duì)控制量增量的累積功能,才能完成對(duì)被控對(duì)象的控制操作。執(zhí)行機(jī)構(gòu)的累積功能可以采用硬件的方法實(shí)現(xiàn);也可以采用軟件來(lái)實(shí)現(xiàn),如利用算式 u(k)=u

2016-01-15 18:35:33

針對(duì)之前以CompactDAQ平臺(tái)上實(shí)現(xiàn)溫度PID控制中存在的溫度曲線不收斂現(xiàn)象,更新程序算法,并更換為CompactRIO平臺(tái),提高PID輸出數(shù)據(jù)實(shí)時(shí)性;且進(jìn)一步明確溫度控制算法,以PID輸出時(shí)間

2016-01-08 14:54:42

xilinx公司的網(wǎng)絡(luò)教程“利用 System Generator 進(jìn)行 DSP 設(shè)計(jì)”誰(shuí)有?上傳一份給小弟吧

2013-03-14 12:17:03

關(guān)注+星標(biāo)公眾號(hào),不錯(cuò)過(guò)精彩內(nèi)容來(lái)源 |技成培訓(xùn)PID的數(shù)學(xué)模型在工業(yè)應(yīng)用中PID及其衍生算法是應(yīng)用最廣泛的算法之一,是當(dāng)之無(wú)愧的萬(wàn)能算法,如果能夠熟練掌握PID算法的設(shè)計(jì)與實(shí)現(xiàn)過(guò)程,...

2021-07-19 06:38:27

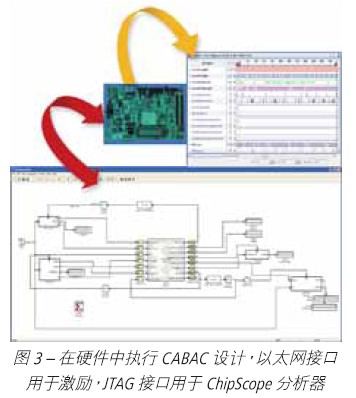

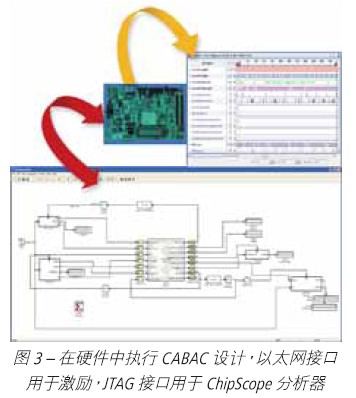

采用以太網(wǎng)硬件在環(huán)路實(shí)現(xiàn)高帶寬DSP仿真設(shè)計(jì)

System Generator v8.1提供全新的千兆位級(jí)以太網(wǎng)硬件在環(huán)接口,支持使用Xilinx ML402 FPGA平臺(tái)進(jìn)行高帶寬協(xié)仿真

通

2010-03-05 09:13:10 27

27 System Generator for DSP 是一款具有高抽象層的設(shè)計(jì)工具,為算法開發(fā)人員和系統(tǒng)架構(gòu)師從 Simulink 算法參考模型過(guò)渡到FPGA 硬件實(shí)施技術(shù)提供了一種高效的途徑,且無(wú)需任何 HDL 編碼工作

2010-06-10 08:21:19 29

29

采用Gardner算法,對(duì)QPSK調(diào)制解調(diào)系統(tǒng)中的位同步系統(tǒng)進(jìn)行設(shè)計(jì)與實(shí)現(xiàn),大大提高了系統(tǒng)性能和資源利用率。重點(diǎn)闡述采用FPGA開發(fā)環(huán)境System Generator系統(tǒng)設(shè)計(jì)工具進(jìn)行位同

2010-07-21 16:12:40 26

26 深入了解賽靈思System Generator中的時(shí)間參數(shù)

基于模型的設(shè)計(jì)(MBD)因其在縮小實(shí)時(shí)系統(tǒng)抽象的數(shù)學(xué)建模和物理實(shí)現(xiàn)之間差距方面的光明前景而備受關(guān)注。通過(guò)使用相同的

2009-12-29 11:40:30 1300

1300

HDL設(shè)計(jì)和驗(yàn)證與System Generator相結(jié)合

Xilinx®SystemGeneratoRForDSP是用來(lái)協(xié)助系統(tǒng)設(shè)計(jì)的MATLABSimulink模塊集。SystemGeneratorforDSP在熟悉的MATLAB環(huán)境中引入XilinxFPGA對(duì)象,讓您能夠

2010-01-06 14:39:30 1181

1181

System Generator 工具由 MathWorks 與 Xilinx 合作開發(fā)而成,DSP 設(shè)計(jì)人員可使用 MATLAB 和Simulink 工具在 FPGA 內(nèi)進(jìn)行開發(fā)和仿真來(lái)完善 DSP 設(shè)計(jì)。 該工具為系統(tǒng)級(jí) DSP 設(shè)計(jì)與 FPGA 硬件實(shí)現(xiàn)的融合起

2011-05-11 18:36:23 224

224 該設(shè)計(jì)是基于System Generator設(shè)計(jì)平臺(tái),在Matlab/Simulink環(huán)境下搭建系統(tǒng)模型,再進(jìn)行功能仿真和驗(yàn)證,完成QPSK調(diào)制器的設(shè)計(jì)。仿真結(jié)果表明,所設(shè)計(jì)的調(diào)制器能產(chǎn)生正確QPSK波形,達(dá)到了預(yù)期效果

2011-10-17 16:10:51 65

65 PID控制器是一種最優(yōu)控制。本文講述了增量式PID算法原理與數(shù)字PID算法原理與數(shù)字PID算法程序,詳細(xì)講解了什么是pid算法。

2012-01-01 11:58:21 10606

10606

Xilinx公司推出的DSP設(shè)計(jì)開發(fā)工具System Generator是在Matlab環(huán)境中進(jìn)行建模,是DSP高層系統(tǒng)設(shè)計(jì)與Xilinx FPGA之間實(shí)現(xiàn)的橋梁。在分析了FPGA傳統(tǒng)級(jí)設(shè)計(jì)方法的基礎(chǔ)上,提出了基于System Generator的

2013-01-10 16:51:24 58

58 pid算法原理和C語(yǔ)言的簡(jiǎn)單實(shí)現(xiàn),有興趣的可以看看

2015-12-07 18:34:39 9

9 Xilinx FPGA工程例子源碼:System Generator的設(shè)計(jì)實(shí)例

2016-06-07 14:41:57 22

22 PID算法的實(shí)現(xiàn)

2016-12-20 22:54:26 3

3 PID算法實(shí)現(xiàn)C語(yǔ)言(位置式PID)STCunio數(shù)字電源帶PID數(shù)字閉環(huán)結(jié)合51單片機(jī)arduino完成步進(jìn)電機(jī)增量式PID-STM32實(shí)現(xiàn)

2016-12-17 11:58:56 20

20 PID算法詳解

2016-12-17 20:48:18 12

12 最新版System Generator支持快速開發(fā)和實(shí)現(xiàn)基于All Programmable FPGA、SoC和MPSoC的無(wú)線電設(shè)計(jì) 賽靈思日前宣布推出高級(jí)設(shè)計(jì)工具System Generator

2017-02-09 01:23:41 279

279 一直都在System Generator下做圖像處理相關(guān)的算法,感覺SysGen挺強(qiáng)大的,前幾天突發(fā)奇想,能否直接用SysGen實(shí)現(xiàn)數(shù)據(jù)的通信呢,畢竟一句HDL代碼都不寫對(duì)于做FPGA的人來(lái)說(shuō)卻是很有吸引力的。

2017-02-10 19:51:11 2618

2618

前一陣一直在忙,所以沒(méi)有來(lái)得及寫博文。弄完雜七雜八的事情,又繼續(xù)FPGA的研究。使用Verilog HDL語(yǔ)言和原理圖輸入來(lái)完成FPGA設(shè)計(jì)的方法都試驗(yàn)過(guò)了,更高級(jí)的還有基于System Generator和基于EDK/Microblaze的方法。

2017-02-11 03:10:11 8192

8192

System Generator是Xilinx公司進(jìn)行數(shù)字信號(hào)處理開發(fā)的一種設(shè)計(jì)工具,它通過(guò)將Xilinx開發(fā)的一些模塊嵌入到Simulink的庫(kù)中,可以在Simulink中進(jìn)行定點(diǎn)仿真,可是設(shè)置

2017-02-11 11:53:11 3778

3778

system generator是xilinx公司的系統(tǒng)級(jí)建模工具,它是擴(kuò)展mathworks公司的MATLAB下面的simulink平臺(tái),添加了XILINX FPGA專用的一些模塊。加速簡(jiǎn)化了FPGA的DSP系統(tǒng)級(jí)硬件設(shè)計(jì)。

2017-02-11 19:21:33 7386

7386

四軸飛行器的PID控制算法介紹

2017-08-29 14:57:26 50

50 利用System Generator軟件平臺(tái),實(shí)現(xiàn)基于模塊化建模方法的變換器建模,并簡(jiǎn)化語(yǔ)言編寫控制系統(tǒng)的復(fù)雜過(guò)程。研究了從MATLAB-Xilinx環(huán)境中導(dǎo)出使用模塊化建模方法搭建的控制算法。通過(guò)

2017-11-15 14:31:34 4985

4985

現(xiàn)在的FPGA算法的實(shí)現(xiàn)有下面幾種方法: 1. Verilog/VHDL 語(yǔ)言的開發(fā) ; 2. system Generator; 3. ImpulsC 編譯器實(shí)現(xiàn)從 C代碼到 HDL 語(yǔ)言; 4.

2017-11-17 14:29:06 7298

7298 在FPGA平臺(tái)上應(yīng)用System Generator工具實(shí)現(xiàn)了高精度頻率估計(jì)Rife算法。不同于傳統(tǒng)的基于HDL代碼和IP核的設(shè)計(jì)方法,采用System Generator工具可以使復(fù)雜算法

2017-11-18 09:01:51 2208

2208

在工業(yè)應(yīng)用中PID及其衍生算法是應(yīng)用最廣泛的算法之一,是當(dāng)之無(wú)愧的萬(wàn)能算法,如果能夠熟練掌握PID算法的設(shè)計(jì)與實(shí)現(xiàn)過(guò)程,對(duì)于一般的研發(fā)人員來(lái)講,應(yīng)該是足夠應(yīng)對(duì)一般研發(fā)問(wèn)題了,而難能可貴的是,在我所接觸的控制算法當(dāng)中,PID控制算法又是最簡(jiǎn)單,最能體現(xiàn)反饋思想的控制算法

2017-11-24 14:47:39 10760

10760

在工業(yè)應(yīng)用中PID及其衍生算法是應(yīng)用最廣泛的算法之一,是當(dāng)之無(wú)愧的萬(wàn)能算法,如果能夠熟練掌握PID算法的設(shè)計(jì)與實(shí)現(xiàn)過(guò)程,對(duì)于一般的研發(fā)人員來(lái)講,應(yīng)該是足夠應(yīng)對(duì)一般研發(fā)問(wèn)題了,而難能可貴

2018-03-16 16:13:15 9

9 基于傳統(tǒng)組態(tài)軟件在實(shí)現(xiàn)復(fù)雜的PID控制算法方面存在不足,以力控組態(tài)軟件為平臺(tái),通過(guò)研究PID控制算法原理以及力控組態(tài)軟件的運(yùn)行機(jī)制,在力控組態(tài)軟件平臺(tái)上編程實(shí)現(xiàn)PID控制算法,并基于力控組態(tài)軟件平臺(tái)

2018-04-10 14:51:23 2

2 本視頻產(chǎn)品演示介紹了 Xilinx 系統(tǒng)生成器(System Generator)和 Xilinx ISE? 項(xiàng)目瀏覽器(Project Navigator)設(shè)計(jì)環(huán)境之間的新整合。

2018-06-06 13:46:00 3024

3024

上一節(jié)中已經(jīng)抽象出了位置性 PID 和增量型 PID 的數(shù)學(xué)表達(dá)式,這一節(jié),重 點(diǎn)講解 C 語(yǔ)言代碼的實(shí)現(xiàn)過(guò)程,算法的 C 語(yǔ)言實(shí)現(xiàn)過(guò)程具有一般性,通過(guò) PID 算法的 C 語(yǔ)言實(shí)現(xiàn),可以以此類推,設(shè)計(jì)其它算法的 C 語(yǔ)言實(shí)現(xiàn)。

2018-07-16 08:00:00 8

8 應(yīng)用中PID及其衍生算法是應(yīng)用最廣泛的算法之一,是當(dāng)之無(wú)愧的萬(wàn)能算法,如果能夠熟練掌握PID算法的設(shè)計(jì)與實(shí)現(xiàn)過(guò)程,對(duì)于一般的研發(fā)人員來(lái)講,應(yīng)該是足夠應(yīng)對(duì)一般研發(fā)問(wèn)題了,而難能可貴的是,在我所接觸的控制算法當(dāng)中

2018-08-13 15:03:45 1103

1103 了解如何在System Generator中使用多個(gè)時(shí)鐘域,從而可以實(shí)現(xiàn)復(fù)雜的DSP系統(tǒng)。

2018-11-27 06:42:00 3450

3450 了解如何使用Vivado System Generator for DSP進(jìn)行點(diǎn)對(duì)點(diǎn)以太網(wǎng)硬件協(xié)同仿真。

System Generator提供硬件協(xié)同仿真,可以將FPGA中運(yùn)行的設(shè)計(jì)直接整合到Simulink仿真中。

2018-11-23 06:02:00 4262

4262 PID算法原理_調(diào)試經(jīng)驗(yàn)以及代碼總結(jié)分享。

2021-05-25 15:59:46 16

16 面向硬件實(shí)現(xiàn)的HEVC幀內(nèi)編碼快速算法

2021-06-21 16:30:15 10

10 PID算法原理、調(diào)試經(jīng)驗(yàn)以及代碼資料

2021-11-21 10:25:33 15

15 本篇博文是面向希望學(xué)習(xí) Xilinx System Generator for DSP 入門知識(shí)的新手的系列博文第一講。其中提供了有關(guān)執(zhí)行下列操作的分步操作方法指南。

2022-02-16 16:21:36 1578

1578

簡(jiǎn) 介: 利用FFT算法實(shí)現(xiàn)快速傅里葉變換, 在理論、工程中具有非常廣泛的應(yīng)用。除了能夠在合適的計(jì)算平臺(tái)完成FFT算法,同時(shí)還需要注意到它在頻譜分析中可能帶來(lái)的頻率混疊以及頻率泄露等問(wèn)題。

2022-07-10 09:07:00 2632

2632 一種非常常用的算法是比例積分微分控制器(proportional-integral-derivative control)或 PID 控制器。PID 算法用于控制各種應(yīng)用中溫度、壓力、電機(jī)位置和流量

2023-05-11 15:36:30 714

714

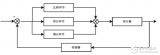

相信大家對(duì)于PID控制算法,都不感到陌生了,平衡車就是靠它平衡起來(lái)的,還有飛控的平衡算法也是它,以及FOC中的閉環(huán)控制中也是用的它,它不僅簡(jiǎn)單,而且易于理解。那么本篇文章將簡(jiǎn)要介紹一下算法的原理,然后帶大家使用FPGA來(lái)實(shí)現(xiàn)(C語(yǔ)言實(shí)現(xiàn)過(guò)程特別簡(jiǎn)單)。

2023-05-19 16:40:23 1014

1014

PID算法詳解及實(shí)例分析#include using namespace std;struct _pid{? ?float SetSpeed; //定義設(shè)定值? ?float ActualSpeed

2023-11-09 16:33:15 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論