隨著處理器被添加到傳統FPGA中,可編程性被添加到ASIC中,FPGA和ASIC的分界線日益模糊。

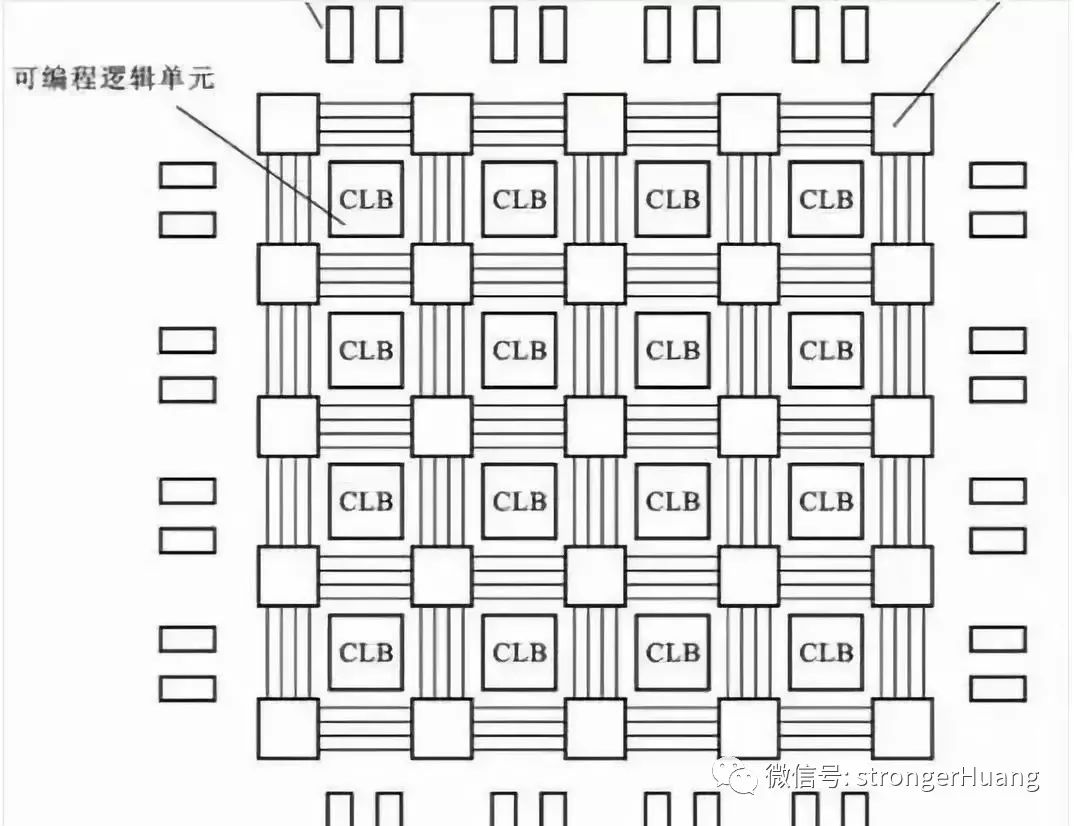

FPGA變得比之前更加流行了。現在的FPGA不再只是查找表(LUT)和寄存器的簡單組合了,它已經成為系統探索的架構,以及驗證未來ASIC設計架構的橋梁。

從基本的可編程邏輯器件到復雜的SoC器件,當今的FPGA家族陣營極其龐大。在包括汽車和其它應用的AI、企業網絡、航空航天、國防和工業自動化等各種應用領域,FPGA使得芯片制造商可以在必要時以更新的方式部署實施系統。在這種標準、協議和最佳實現仍然在探索中,而且要求具備成本競爭力的新興市場中,FPGA的靈活性至關重要。

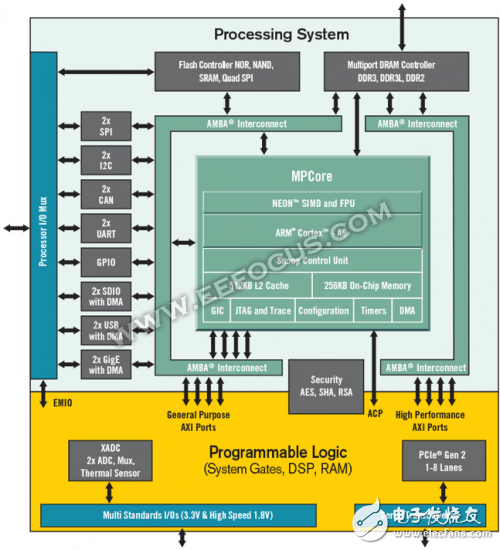

這就是賽靈思決定在其Zynq FPGA中添加ARM內核以創建FPGA SoC的原因所在,Aldec市場總監Louie de Luna表示。“最重要的是,供應商已經改進了工具流程嗎,這使得人們對Zynq產生了很大的興趣。他們的SDSoC開發環境看起來很像C語言,對開發人員很友好,因為應用程序通常是用C語言編寫的。他們將軟件功能放到開發環境中,允許用戶將這些功能分配到具體的硬件上。”

其中有些FPGA不只是像SoC,他們本身就是SoC。

“他們可能包含多個嵌入式處理器、專用計算引擎、復雜接口以及大容量存儲器等,”OneSpin Solutions綜合驗證產品專家Muhammad Khan說。 “系統架構師規劃并使用FPGA的可用資源,就像他們在ASIC上所做的那樣。設計團隊使用綜合工具將他們的System Verilog、VHDL或System C RTL代碼映射到基礎邏輯元素中。對于大部分設計過程來說,專門針對FPGA或ASIC或全定制芯片的設計差異正在減少。”

ArterisIP首席技術官Ty Garibay非常熟悉這一演變。“賽靈思2010年開始在Zynq上實踐這種路線,他們定義了一款產品,把ARM SoC的硬宏納入到了當時現有的FPGA中,”他說。 “然后,Altera招募了我做基本上同樣的事情。它的價值主張在于許多客戶都想要SoC子系統,但是SoC的特性尤其是處理器那部分并不適合綜合到FPGA中。將這種級別的功能嵌入到實際的可編程邏輯中令人望而卻步,因為它幾乎用盡了整個FPGA的資源。但是它可以作為整個FPGA芯片的一小部分或一小部分,作為一個硬性的功能而存在。雖然你沒有為SoC提供真正可重構邏輯的能力,但是它們可以通過軟件編程,以這種方式改變功能。”

“這意味著,這種結構可以同時具備軟件可編程功能、硬宏和硬件可編程功能,他們可以一起工作,”他說。 “這類期間有一些相當理想的目標市場,尤其是在低成本的汽車控制領域,在這種系統中一般都會以中等性能的微控制器搭配FPGA,現在客戶會說,‘我現在可以將整個功能放到FPGA芯片的硬宏上,以減少電路板空間,減少BOM并降低功耗。’”

這也符合過去30年FPGA的發展趨勢。最初的FPGA只是可編程結構和一組I/O。隨著時間的推移,內存控制器、SerDes、RAM、DSP和HBM控制器都慢慢地被硬化了。

Garibay說:“FPGA供應商一直在繼續增加芯片面積,同時也在繼續增加越來越多的硬邏輯,這些邏輯被相當大比例的客戶群普遍使用。現在,這些硬邏輯轉變成軟件可編程器件。在ARM SoC之前添加的大多數東西都是不同形式的硬件,主要與I/O有關,但也包括DSP,DSP有足夠的應用計劃,因此,通過將DSP硬化,可以節省可編程邏輯門。”

市場可能性

這種方式基本上已經把FPGA變成了具有多種可能性的瑞士軍刀。

“如果你往回看,FPGA只是一堆LUT和寄存器,而不是門,”NetSpeed Systems市場和業務開發副總裁AnushMohandass說。 “這里有一個典型問題。如果您將任何通用器件和專用器件進行比較就會發現,通用計算可以提供更大的靈活性,而專用計算可以提供性能或效率優勢。賽靈思和Altera一直試圖越來越多地融合通用計算和專用計算,他們注意到,幾乎每個FPGA客戶都擁有DSP和某種形式的計算。所以他們在FPGA里面加入了ARM內核、DSP內核,還加入了所有不同的PHY和常用模塊,他們把這些東西硬化了,使得效率更高,并且性能曲線變得更好。”

這些新功能為FPGA在各種新興市場和現有市場中發揮重要作用打開了大門。

“從市場角度來看,您可以看到FPGA肯定會進入SoC市場,”Synopsys的高級營銷總監Piyush Sancheti表示。 “是做一個FPGA還是做一款成熟的ASIC牽扯到經濟問題。它們的界限開始變得模糊不清,我們看到越來越多的公司 - 特別是在某些市場上 - 正在在量產階段使用成本更低的FPGA。”

從歷史上看,FPGA主要用于原型階段,在生產用途而言,它僅限于航空航天、國防和通信基礎設施等市場,Sancheti說。 “現在市場正在擴展到汽車、工業自動化和醫療設備。”

AI:一個蓬勃發展的FPGA市場

一些系統供應商/OEM采用FPGA,希望優化其IP或AI/ML算法性能。

NetSpeed的Mohandass表示:”他們想要打造自己的芯片,對其中很多人來說,做ASIC可能有點嚇人。他們也可能不想花費3000萬美元的晶圓成本來獲得芯片。對他們來說,FPGA是一個有效的切入點,他們擁有獨特的算法、自己的神經網絡,他們想要工程化,看看它是否能夠提供他們所期望的性能。”

西門子子公司Mentor的Catapult HLS綜合與驗證高級產品營銷經理Stuart Clubb表示,目前AI應用面臨的挑戰是量化。 “需要什么樣的網絡? 我如何建立這個網絡? 什么樣的內存架構? 即便你只有幾層神經網絡,當你獲得很多采用若干系數的數據之后,很快就會轉化成為數百萬個系數,存儲帶寬也會變得非常恐怖。沒有人真正知道正確的架構是什么。如果你不知道答案,你肯定不會直接上來就設計一個ASIC。”

在企業網絡領域,最常見的問題是密碼標準似乎一直在變化。Mohandass表示:“與其嘗試構建一顆ASIC,不如將密碼引擎放在FPGA中設計。“或者,如果您在全球網絡中進行任何類型的數據包處理,FPGA仍然能夠為您提供更多的靈活性和更多的可編程性。這就是靈活性的用武之地,他們也已經利用了這種靈活性。你可以稱之為異構計算,它看起來仍然像一個SoC。”

新規則

隨著新一代FPGA SoC的投入使用,舊規則不再適用了。“具體來說,如果你還在電路板上進行調試,那就太落伍了,”Clubb指出。 “雖然在開發板上進行調試被認為是一種成本較低的解決方案,但這是在早期階段使用的手段:‘它是可編程的,您可以在它上面放置一個示波器,觀察一下現象,看看發生了什么。如果發現了一個錯誤,我可以修復它,在一天內修改代碼,然后將它重新燒錄到電路板上,然后再定位下一個bug,‘這太瘋狂了。在員工的時間不被視為成本的很多公司,管理層不會購買模擬器或系統級工具或調試器,因為’我付了錢讓這個人完成工作,我會一直訓他,直到他努力工作。‘”

這種行為仍然很常見,Clubb說,因為有很多公司實行10%的末位淘汰,以鞭策每個員工好好干活。

但是,FPGA SoC是真正的SoC,需要嚴格的設計和驗證方法。 “器件可編程不會真正影響設計和驗證,”Clubb說。 “如果你要設計一顆SoC,你可以按照我聽很多客戶說起過的‘樂高’工程,采用框圖式的方法。我需要一顆處理器、一塊內存、一顆GPU、一些其他零件、一個DMA內存控制器、WiFi、USB和PCI,這些都是您組裝用的’樂高‘積木。麻煩之處在于必須驗證它們能夠工作,并且能夠一起工作。”

不過,FPGA SoC系統開發人員正在迅速掌握SoC從業者們關注的驗證方法。

“因為[使用FPGA]的成本更低,所以FPGA SoC系統開發人員的思考方式和傳統的芯片SoC開發人員不同,傳統SoC開發人員的處理思路是’這將花費我200萬美元,所以我最好做好萬全的準備‘,“Clubb說。 “但是如果你花費200萬美元開發FPGA,沒搞對,現在你將需要花費三個月的時間修復這些bug,這也是需要考慮的成本。開發團隊有多大?要花多少錢?沒有及時上市的懲罰是什么?這些都是非常難以清晰量化的成本。如果您處于消費領域,需要在圣誕節期間及時上市的產品上幾乎不可能使用FPGA,所以這有一個不同的優先級。在定制芯片中做一款SoC需要面臨巨大的整體成本和風險,因此越來越少見了。眾所周知,這個行業正在整合,大玩家越來越少。每個選手都必須找出一種方式實現自己的設計,這些FPGA SoC可以幫助實現這一目標。”

新的折衷選擇

Sancheti說,很多工程團隊不介意更換目標器件。“我們看到許多公司創建RTL并對其進行驗證,但幾乎不知道他們最終會選擇FPGA還是ASIC,因為這個決定可能會變很多次。你可以從FPGA開始,當達到一定數量后,如果ASIC成本更低,就轉到ASIC上。”

這種局面對于今天的AI應用領域尤其普遍。

eSilicon營銷副總裁Mike Gianfagna表示:“加速AI算法速度的技術還在發展中。人工智能算法其實已經存在了很長一段時間,但是現在,我們在使用AI方面突然間變得更加復雜,并且可以非常神奇地以接近實時的速度運行它們。最初的AI算法運行在CPU上,然后轉移到了GPU上。GPU也可以認為是一種可編程器件,盡管它具有一定的通用性。GPU架構擅長并行處理,因為圖形加速運算就是并行計算,所以在GPU上跑AI算法很方便,因為AI基本上就是并行處理。在很大程度上來說,GPU確實很好,但是它仍然是一種通用的方法,你可以在一定的功耗下獲得一定程度的性能。現在,有些人接下來要轉向FPGA運行AI算法,因為FPGA可以提供比GPU更好的專用電路,而且性能和功效上都能得到提升。ASIC在功耗和性能方面最為出色,因為您擁有可以完全滿足您的需求的自定義架構,不多不少,顯然最好。”

人工智能算法很難映射到芯片上,因為它們幾乎總是在變化。就這一點可以看出,做一款全定制的ASIC完全不合時宜,因為芯片出廠時老的算法就已經過時了。“FPGA顯然可以很好地應對這種情況,因為你可以對它們進行重新編程,這樣對芯片的昂貴投資就不會打水漂了。”Gianfagna說。

這里有一些自定義的內存配置,以及某些像卷積和轉置存儲等可以再次使用的子系統功能,因此,雖然算法可能會更改,但某些塊不會更改,可以一次又一次地使用。考慮到這一點,eSilicon正在開發一款具有軟件分析功能、可以查驗AI算法的機箱,目標是能夠更快速地為特定應用選擇最佳架構。

“使用FPGA,可以靈活地更換機器或者引擎,因為您可能會遇到一種新的神經網絡,選擇ASIC則要承擔風險,因為你可能無法獲得靈活性,”eSilicon知識產權工程副總裁Deepak Sabharwal說。 “然而,FPGA在容量和性能方面總是受到限制,所以用FPGA無法真正達到產品級規格。 你可以用它做實驗,對事物分組,但最終你將不得不選用一顆ASIC。”

嵌入式LUT

過去幾年,還有一種器件類型取得了一定進步,即嵌入式FPGA,它將可編程性集成到ASIC中,同時將ASIC的性能和功耗優勢添加到FPGA中。

Flex Logix公司首席執行官Geoff Tate表示:“在FPGA SoC中,處理單元的芯片面積相對較小,在方框圖中看起來,比例有大有小,但是在實際的光刻圖中,仍然主要是FPGA。不過,有一類應用和客戶,FPGA邏輯單元和SoC其余部分的正確比例應該是FPGA更小,使得它們既具有RTL可編程性,同時芯片尺寸更具成本效益。”

這種方法在航空航天、無線基站、電信、網絡、汽車和視覺處理等領域,特別是在人工智能應用上獲得了相當的關注。 “算法變化非常快,以至于芯片從晶圓廠流片回來時就幾乎已經過時了,”Tate說。 “有了嵌入式FPGA,可以讓設計人員更快地迭代他們的算法。”

在汽車從司機駕車模式向自主駕駛汽車的演變中,這種意義尤其明顯。Achronix系統工程副總裁Raymond Nijssen表示,雖然失效和老化問題引起了很多關注,但主要的挑戰在于保持“優雅的降級”。 “隨著時間的推移,性能和質量會發生變化,標準也會發生變化。比如一個相對較新的需求是汽車需要識別小孩過馬路,沒有人知道這些法規會如何改變,或者你如何進行測試,如何測試那些尚未知曉的標準。”

Nijssen說,在這種情況下,可編程性對于避免重新制作整個芯片或模塊變得至關重要。

調試你的設計

和所有SoC一樣,理解怎么調試這些系統,如何構建測量手段,可以幫助人們在出現大麻煩之前找出問題。

“隨著系統FPGA變得越來越像SoC,他們需要一套類似于SoC的開發和調試方法,”UltraSoC首席執行官Rupert Baines說。 “有一種天真的想法認為,你可以在FPGA中看到任何東西,所以很容易調試。波形查看器可以查看到bit級別,但是并不能提供任何系統級別的信息。現在新的大型FPGA顯然是系統級的。在系統級別上,你通過位探測器獲得的波形級視圖沒有太大作用,你需要的是邏輯分析儀、協議分析儀,以及處理器內核本身的良好調試和跟蹤功能。”

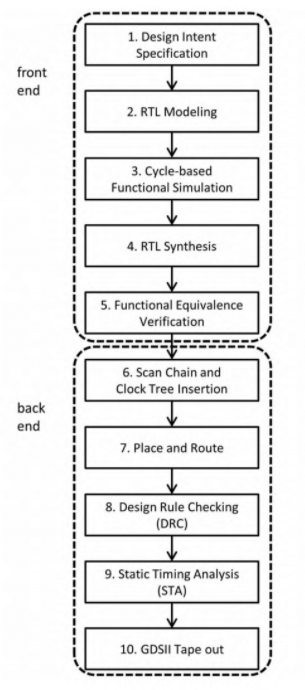

FPGA的大小和復雜性要求其驗證過程類似于ASIC。先進的基于UVM的測試平臺支持模擬,通常也支持仿真。從自動設計檢查到基于斷言的驗證,以及一系列強大的求解器,形式工具在這里起著關鍵的作用。盡管FPGA確實可以比ASIC更快更便宜地修改,但在大型SoC中檢測和診斷bug的難度意味著必須在進入bring-up階段之前進行徹底的驗證,OneSpin的Khan說。

事實上,在RTL輸入和綜合后網表之間進行等效性檢查方面,對FPGA SoC的驗證要求可能比ASIC更高。與傳統的ASIC邏輯綜合流程相比,FPGA的精細化、綜合和優化階段通常需要對設計進行更多的修改。這些更改可能包括跨越周期邊界移動邏輯,以及在內存結構中實現寄存器。 Khan補充道,徹底的順序等價檢查對于確保最終的FPGA設計仍然符合RTL中最初的設計者意圖至關重要。

在工具方面還有優化性能的空間。““很多嵌入式視覺應用程序都是在Zynq上編寫的,性能可能是每秒5幀。但如果你在硬件上加速它,可能會提高到每秒25到30幀,這種改進空間為新型器件鋪平了道路。問題在于,這些器件的模擬和驗證并不簡單。您需要整合軟件和硬件,這很困難。 如果你把所有運算都放在SoC中運行,那就太慢了。每次模擬可能需要五到七個小時,如果你把多個模擬合并起來,就可以節省時間,”Aldec的de Luna說。

簡而言之,復雜ASIC中使用的同類方法現在正用于復雜的FPGA。隨著這些器件被用于功能安全類型的應用,這變得越來越重要。

“這就是形式分析的用武之地,通過形式分析,可以得出錯誤的傳播路徑,然后驗證這些路徑,”Cadence市場營銷總監Adam Sherer說。 “這些東西非常適合進行形式分析。傳統的FPGA驗證方法幾乎不可能進行這些類型的驗證。有一種非常流行的觀點認為,FPGA設計非常快,而且能夠容易地以系統速度運行硬件測試,并且只需進行簡單的仿真即可進行完整性檢查。 把編程燒錄到器件中,在實驗室中實際運行,這是一條相對較快的驗證路徑,但實驗室中的可觀察性和可控性極其有限,因為它只能根據FPGA引腳的數據進行探測,以便您可以在測試儀上看到它們。”

Breker Verification Systems首席營銷官Dave Kelf對此表示贊同。 “這使得這些器件得到驗證的方式發生了有趣的轉變。 過去,在小型器件上,通過將設計加載到FPGA中并在測試卡上實時運行,盡可能多地運行來驗證它。隨著SoC和軟件驅動設計的出現,可以預期這種“自行設計原型”的驗證方式可能適用于軟件驅動技術,并且可能適用于該過程的某些階段。 但是,在原型上識別問題并對其進行調試非常復雜,這個早期驗證階段需要模擬,因此SoC型FPGA看起來越來越像ASIC。SoC和FPGA之間的通用性使得驗證過程更高效,調試和測試平臺也會通用。Portable Stimulus(便攜式激勵)等新進展將提供這種通用性,實際上將使得SoC FPGA更易于管理。”

結論

展望未來,Sherer表示,用戶正在尋求將現在用在ASIC領域里的更嚴格的流程應用到FPGA流程中。

“有很多學習和分析應用希望FPGA中有更多系統級調試技術,”他說。“FPGA社區一向落后于最新的技術,傾向于使用非常傳統的方法,因此他們需要培訓和了解最新的技術和方法、規劃、管理和需求的可追溯性。FPGA絕對需要那些來自SoC流程的元素,其驅動力來自終端應用中的那些行業標準,而不是FPGA自身。傳統的FPGA工程師需要重新接受再教育。”

在需要靈活性的應用、不斷將可編程邏輯和硬線邏輯結合在一起的系統架構以及適用于兩者的工具的推動下,ASIC和FPGA之間的界限正在變得日益模糊。這種趨勢短期內不會發生扭轉,因為需要這些組合的許多新應用領域目前仍處于起步階段。

電子發燒友App

電子發燒友App

評論