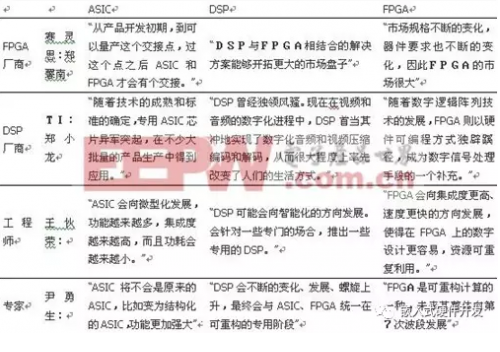

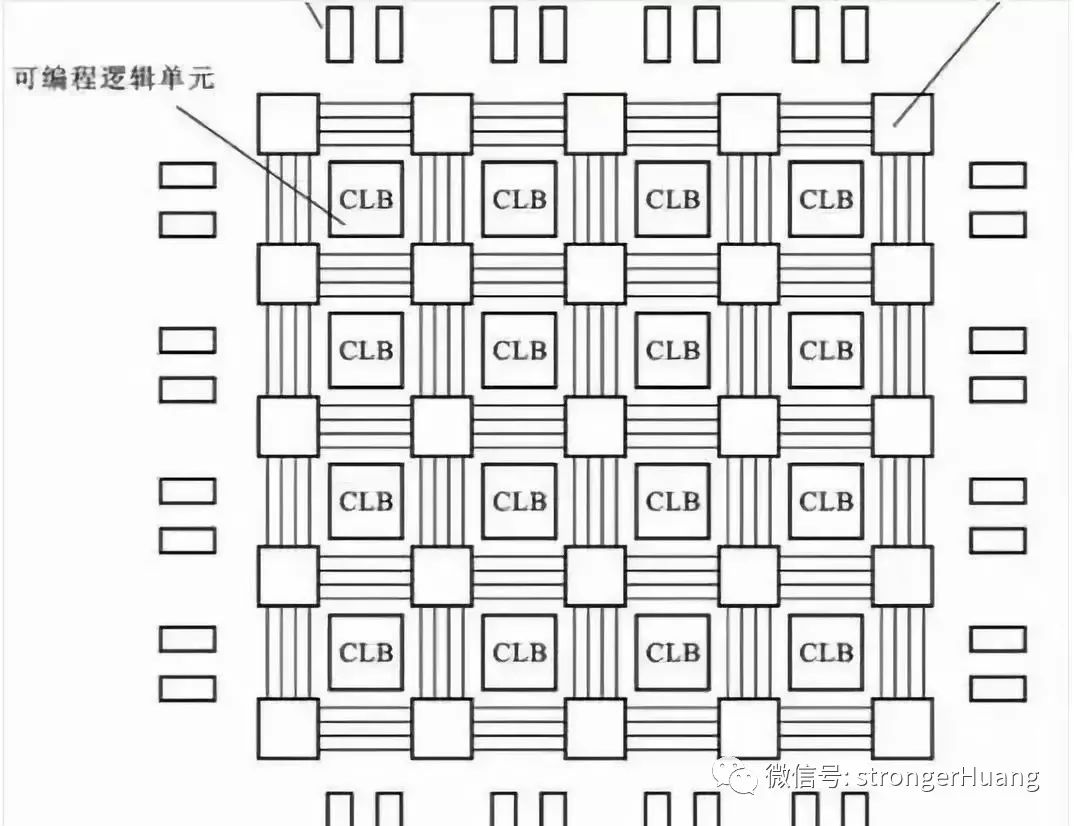

由于在傳統(tǒng)的FPGA中增加了處理器,在ASIC中增加了可編程性,使得這些產品的界限越來越模糊了。

FPGA與以前的自己相比,現在都是搖滾明星了。不再只是一個查找表(LUT)和寄存器的集合,FPGA已經遠遠超出了現在的系統(tǒng)體系結構和原來只是用于證明未來ASIC設計架構的工具。

FPGA器件系列現在包括了從基本的可編程邏輯到復雜的SoC器件。在各種應用領域,汽車和其他應用領域的人工智能、企業(yè)網絡、航空航天、國防和工業(yè)自動化等等,FPGA使芯片制造商能夠在需要時隨時更新系統(tǒng)。在新的市場中,這種靈活性至關重要,協(xié)議、標準和最佳案例仍在不斷發(fā)展,ECOs需要保持競爭力。

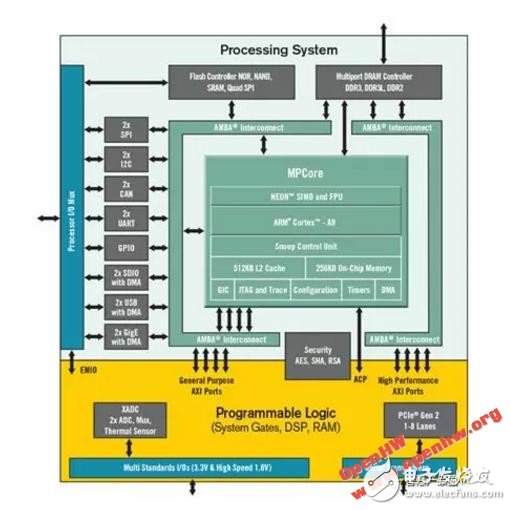

這就是賽靈思(Xilinx)公司的決策理由,Xilinx在它的Zynq FPGA里增加了一個ARM核處理器,以打造一個SoC FPGA芯片。Aldec公司的營銷總監(jiān)Louie de Luna說,“最重要的是,供應商已經改善了他們的工具流程。這使得他們對Zynq更感興趣。他們的SDSoC開發(fā)環(huán)境看起來像C,這對開發(fā)人員很有好處,因為應用程序通常是用C編寫的。因此,他們輸入軟件功能,并允許用戶將這些功能分配給硬件。”

圖:賽靈思的Zynq-7000 SoC(來源:Xilinx)

這些不僅僅是SoC FPGA,這也是他們有自主專利的SoC。

“它們可能包含若干個嵌入式處理器、專用計算引擎、復雜接口、大的內存等等,” OneSpin Solutions的產品綜合驗證專家Muhammad Khan說。“系統(tǒng)架構師計劃和使用FPGA的可用資源,就像他們做一個ASIC那樣。設計團隊使用綜合工具將他們的SystemVerilog、VHDL或SystemC RTL代碼映射到基本邏輯元件中。對于設計過程的大部分,在有效針對FPGA和針對ASIC或全定制芯片之間的差異正在減小。”

ArterisIP的首席技術官Ty Garibay非常熟悉這種演變。“從歷史上看,Xilinx從2010開始形成Zynq路徑。他們定義了一種產品,它基本上是把一個ARM SoC的硬宏嵌入到現有FPGA里,”他說。“后來Altera雇我基本上做同樣的事情。價值命題是SoC子系統(tǒng)是許多客戶想要的東西,但由于SoC的性質,特別是處理器,他們不適合綜合到一個FPGA。嵌入到實際可編程邏輯的功能級是令人望而卻步的,因為它幾乎使用了整個FPGA的資源。但它可以作為一個硬件功能只占FPGA很小的資源。你放棄了為SoC提供真正可重構邏輯的能力,但它是可編程的軟件,因此它是以這樣的方式來改變功能。”

這意味著可以實現一個軟件可編程,一個硬宏,然后在構架中實現硬件可編程功能,他們可以一起工作,他說。“有一些很好的市場,尤其是在低成本汽車控制的地方,過去傳統(tǒng)做法是在FPGA旁邊放一個中等性能的微控制器。客戶只會說,‘我只要把整個功能放到FPGA芯片的硬宏上,以減少電路板空間,減少BOM,降低功率。’”

這符合FPGA在過去30年中的演變,原來的FPGA只是一組I/O的可編程架構。隨著時間的推移,內存控制器被固化,以及SerDes、RAM、DSP和HBM控制器等等。

“FPGA供應商一直不斷在培育芯片,但也增加了越來越多的硬件邏輯,因為有一個很大比例的客戶群需求,”Garibay說。“今天發(fā)生的事情是把它擴展到軟件可編程那一面,在ARM SoC之前我們添加的大部分東西都是不同形式的硬件,主要與I/O有關,但我們也有必要嘗試通過加強可編程邏輯門來加固像DSP這樣的東西,因為市場有足夠的應用需求。”

01

市場視角

這樣做實質上已經把FPGA變成了像設計瑞士軍刀一樣的多可能性。

“如果倒轉時間,它只是一堆LUTs和寄存器,而不是門,”NetSpeed Systems的市場營銷和業(yè)務發(fā)展副總裁Anush Mohandass說。“這里有一個經典的問題,如果你使用通用版本,并將其與特定于專用程序的版本進行比較,通用計算將給出更多的靈活性,而專用的版本會比通用版本在性能或效率上更優(yōu)。Xilinx和Altera正試圖越來越多將這兩塊結合,他們注意到每個FPGA客戶都有諸如DSP或某種形式的計算需求。因此,他們嵌入ARM核,嵌入DSP核,他們嵌入所有不同的PHYs(物理結構)和常用的東西。并固化它,使它更有效,同時性能指標也變得更好。”

這些新的能力為FPGA在各種新的和現有市場中扮演重要角色打開了大門。

“從市場的角度看,FPGA肯定會進入SoC的市場,”新思科技高級營銷總監(jiān)Piyush Sancheti說。“不管你做FPGA還是做十分成熟的ASIC,都有一個經濟學問題。現在這些路線開始變得模糊,我們看到越來越多的公司,特別是在某些市場上,反而做FPGA產品的生產會取得較好的經濟效益。”

從歷史上看,FPGA曾被用于原型設計,但是對于生產使用來說,它僅限于像航空航天、國防和通信基礎設施這樣的市場,Sancheti說。“現在這個市場正在擴展到汽車、工業(yè)自動化和醫(yī)療電子。”

02

AI:FPGA的一個新興市場

那些信奉FPGA的公司一般都是系統(tǒng)供應商/ OEM,他們總是希望優(yōu)化自己的IP或AI/ML算法的性能。

“他們想建立自己的芯片,對于很多人來說,開始做ASIC可能會有點嚇人,” NetSpeed的Mohandass說。“對于不想花3000萬美元的晶圓成本來制造芯片的他們來說,FPGA是一個有效的切入點,在那里他們有計劃中的獨特算法,獨特的神經網絡,用FPGA設計看看是否可以得到他們正在尋找的功能。”

目前人工智能應用面臨的挑戰(zhàn)是量化,西門子業(yè)務Mentor的Catapult HLS綜合驗證高級產品營銷經理Stuart Clubb說。“我們需要什么樣的網絡,該如何建設那個網絡,內存結構是什么?你從網絡開始設計,即使只有幾層,有很多數據在若干個系數中,它很快地旋轉到幾百萬個系數,內存帶寬變得非常可怕。沒有人知道什么架構可行,如果答案是未知的,你就不會跳進去貿然建立一個ASIC。”

在企業(yè)網絡領域,最常見的問題是加密標準似乎一直在變化。“把加密設計到FPGA里代替設計一個ASIC,對加密引擎更好,”Mohandass說。“或者,如果你在全球網絡方面做任何類型的數據包處理,FPGA仍然給會你更多的靈活性和可編程性。這就是靈活性發(fā)揮作用的地方,他們也利用了這一點。你仍然可以稱之為異構計算,它看起來更像一個SoC。”

03

新規(guī)則

隨著新一代的FPGA SoC,舊的規(guī)則不再適用。具體來說,如果你在板子上調試,那你就錯了,”Clubb指出。“雖然在板上調試被認為是一種低成本的解決方案,這可以追溯到能夠說“可編程”的早期階段。但如果現在說,‘我發(fā)現一個bug,我可以修復它,在一天之內編程一個新的比特流,然后把它放回板子上,再找到下一個bug,’那就是瘋了。這是一種被視為不關心成本的心態(tài),就像你在做普通員工那樣,管理層不會購買模擬器、系統(tǒng)級工具或調試器,因為‘我只是付錢給那個家伙完成任務,我會對他大喊大叫,直到他更努力工作。’”

這種行為仍然很普遍,因為有足夠多的公司,他們每年都會把底部10%的員工砍掉以讓每個人都保持警覺的態(tài)度,他說。

然而,FPGA SoC是真正的SoC,需要相同的嚴格設計和驗證方法。“事實上,可編程的構造并不真正影響設計和驗證,”Clubb說。“如果你做一個SoC,例如,你可以做我聽到的一些客戶稱之為“樂高”工程,這是一個框圖法。我需要一個處理器,一個內存,一個GPU,一些其他的小模塊,一個DMA內存控制器,WiFi,USB和PCI。這些都是你組裝的‘樂高’塊。麻煩的是,你必須確認他們能工作,并且能在一起工作。”

盡管如此,FPGA SoC系統(tǒng)開發(fā)人員還是很快趕上了他們的SoC兄弟們,在那里,驗證方法是值得關注的。

“它們不是像原先的傳統(tǒng)硅SoC開發(fā)商那樣的心態(tài):‘這將花費我200萬美元,所以我最好把它弄對。’因為FPGA的失敗成本很低,”Clubb說。“但是如果你花了200萬美元開發(fā)FPGA,你弄錯了,現在你要花三個月來修復bug,還有一些其他問題需要解決。需要組建多大的團隊,要花多少錢,產品上市時間的處罰成本,市場在哪里等等?這些都是很難明確量化的成本。如果你是在一個消費領域,幾乎不太可能去考慮用FPGA,你真正關心的是它能不能趕上圣誕節(jié)前上市,所以有一點不同的優(yōu)先級。考慮定制硅中做SoC的總成本和風險,當你扣動扳機說:‘這是我的系統(tǒng),我已經完成了,’其實你看不到那么多。我們知道,這個行業(yè)正在整合,很少有大玩家做大籌碼。每個人都想辦法來做,而這些正是FPGA可以提供的。”

04

新的折衷方案

工程團隊設計目標器件時常常會有意留出一些選項,這并不少見。Sancheti說,“我們看到很多公司創(chuàng)建RTL并驗證它,幾乎不知道是去做FPGA還是做ASIC,因為很多因素可以讓這個決定改變。你可以從FPGA開始,如果達到了某個量,從經濟學角度考慮可能你會去做一個ASIC。”

這尤其適用于今天的人工智能應用領域。

“已經有一系列技術被用于人工智能算法加速,”eSilicon市場營銷副總裁Mike Gianfagna說。“顯然,AI算法已經存在很長時間了,但是現在我們突然碰到更加復雜的情況是如何使用它們,頗堪稱奇的是在近乎實時的速度下運行它們的能力。它從CPU開始,然后轉移到GPU。即使GPU是一個可編程的通用器件,一個就可以適合所有。雖然架構擅長并行處理,因為這就是圖形加速的全部內容,這很方便,這就是AI的全部內容。在很大程度上它是好用的,但它仍然是一種通用的方法。這樣你就可以得到一定程度的性能和功率的覆蓋。一些人接下來要轉移到FPGA,因為這比你用GPU可以更好地設計電路,并在性能和功率效率方面取得進步。ASIC對功率和性能來說是終極的,因為在那里你有一個完全定制的架構,它能滿足你所需要的,不多也不少。這顯然是最好的。”

人工智能算法很難映射到硅中,因為硅處于幾乎不變的狀態(tài)。所以在這一點上做一個全定制的ASIC不是一個好的選擇,因為相對硅的時代它已經過時了。“FPGA是很好的選擇,因為你可以重新編程它們,所以在昂貴芯片上的投資也不會損失。” Gianfagna說。

這里,有一些自定義內存配置,以及某些子系統(tǒng)功能,如卷積和轉置存儲器,它們被再次使用。因此,當算法可能改變時,有一些模塊不會被改變/或被反復使用。他補充說。考慮到這一點,ESILICON正在開發(fā)一個帶有軟件分析的平臺來研究人工智能算法,目標是能夠更快地為特定的應用選擇最佳的體系結構。

“FPGA為你提供了更換機器或發(fā)動機的靈活性,因為你可能會遇到一種新的網絡,提交ASIC是有風險的,因為你沒有最好的支持,以及這樣的靈活性,”,eSilicon IP工程副總裁Deepak Sabharwal說。“然而,FPGA總是會在容量和性能上受到限制,所以你將無法真正達到FPGA的生產水平規(guī)格。你可以玩它和歸類東西,但最終你可能不得不建立一個ASIC。”

05

嵌入式LUTs

另一個在過去幾年取得了立足點的選擇是嵌入式FPGA,它將可編程性構建為ASIC,而不是將ASIC的性能和功率優(yōu)勢添加到FPGA中。

“FPGA SoC仍然主要是FPGA,具有相對少量的芯片面積用于加工,”Flex Logix首席執(zhí)行官Geoff Tate說。“從框圖看不出規(guī)模,要看實際芯片的照片,主要面積還是FPGA。但是有一類應用程序和客戶,FPGA邏輯和SoC的部分之間的正確比率是更小的FPGA,他們的RTL編程在一個更具成本效益的芯片尺寸上。”

這種方法在航空航天、無線基站、電信、網絡、汽車和視覺處理領域,尤其是人工智能領域找到了牽引力。“算法變化如此之快,以至于芯片在返回時幾乎就過時了”Tate說。“使用一些嵌入式FPGA,可以讓他們更快地進行算法迭代。”

從人駕駛汽車轉向自動駕駛汽車,這一點尤其明顯。雖然失效和老化的問題得到了很多關注,但挑戰(zhàn)是如何保持“優(yōu)雅的退化”。根據Achronix系統(tǒng)工程副總裁Raymond Nijssen的說法,“性能和質量隨著時間的推移而變化,標準也是如此。對汽車識別一個孩子過街的要求是相對較新的。沒有人知道規(guī)章會如何改變,或者你如何測試。但你如何測試還不知道的標準呢?”

在這種情況下,可編程性對于避免重做整個芯片或模塊就變得至關重要,Nijssen說。

06

設計調試

盡管這只是一部分原因,與所有的SoC一樣,了解如何調試這些系統(tǒng),并在儀器中構建,可以幫助它們在成為主要問題之前識別它們。

“隨著系統(tǒng)FPGA變得更像SoC,他們需要適用于在SoC中的開發(fā)和調試方法,”UltraSoC的首席執(zhí)行官Rupert Baines說。“有一個(也許是天真的)信念,因為在FPGA上你可以看到所有東西,調試起來一定很容易。這在比特級別上是正確的,帶有波形觀察器,但是當到達系統(tǒng)級時它不成立。最新的大型FPGA顯然是系統(tǒng)級的。在這一點上,你從一個探針排列得到的波形圖并不是非常有用。你需要一個邏輯分析器,一個協(xié)議分析器,以及處理器內核本身的良好的調試和跟蹤能力。”

FPGA的大小和復雜性要求與ASIC類似的驗證過程。基于測試臺的復雜的UVM支持模擬,通常也支持仿真。正規(guī)的工具都在這里扮演著重要的角色,從自動設計檢查,到權威驗證以及一系列強大的解決方案。雖然FPGA可以比ASIC更快速、更便宜地改變,這是事實,在大型SoC中檢測和診斷BUG的困難意味著在進入實驗室之前必須對它們進行徹底的驗證,OneSpin的Khan說。

事實上,在一個領域中,對FPGA SoC的驗證要求比在RTL輸入和后綜合網表之間的ASIC等價性檢查更高。FPGA的闡述、綜合和優(yōu)化階段常常比傳統(tǒng)的ASIC邏輯綜合流程對設計有更多的修改。這些變化可以包括跨越循環(huán)邊界的移動邏輯,以及在存儲器結構中實現寄存器。徹底的時序電路等價性檢查對于確保最終的FPGA設計仍然符合RTL中的原始設計者意圖是必不可少的,Khan補充說。

在工具方面,也有優(yōu)化性能的空間。“使用嵌入式視覺應用程序,其中很多都是為Zynq編寫的,每秒鐘可以獲得5幀圖像。但如果你用硬件加速,就可以得到每秒25-30幀,這為新型器件鋪平了道路。問題是,這些器件的仿真和驗證并不簡單。你需要在軟件和硬件之間進行集成,這是困難的。如果你在SoC運行所有的東西,那太慢了。它可以模擬5到7個小時,如果你用協(xié)同仿真,就可以大大節(jié)省模擬時間,” Aldec’s de Luna說。

簡單地說,在復雜的ASIC中使用的相同類型的方法現在正在用于復雜的FPGA中。隨著這些器件在功能安全性應用中的使用,這一點變得越來越重要。

“這就是為了確保有故障傳播路徑,然后驗證這些路徑的形式化分析,” Cadence的集團營銷總監(jiān)Adam Sherer說。“這些東西都是非常適合形式化分析。FPGA驗證的傳統(tǒng)方法是無法完成這類驗證任務的。它在FPGA設計中仍然很普遍,假設它非常快,很容易達到以系統(tǒng)速度運行的硬件測試。即使它運行在系統(tǒng)速度,一個非常簡單的模擬就能完成一個全面的檢查。然后你編程這些器件,在實驗室開始啟動運行。除了實驗室中的可觀測性和可控性是極其有限的,這是一個相對快速的路徑。因為只有在從FPGA的內部拉動數據到引腳才能進行探測,這樣才能在測試儀上看到它們。”

Breker驗證系統(tǒng)公司的首席營銷官Dave Kelf同意這一點,“這使得器件驗證的方式發(fā)生了有趣的轉變。在過去,通過將設計加載到FPGA本身并在測試卡上實時運行的方法使較小的器件盡可能多地驗證。隨著SoC和軟件驅動設計的出現,可以預期這種自我“原型”的驗證方式可能與軟件驅動的技術結合得很好,對于這個過程的某些階段,它確實如此。然而,在原型開發(fā)過程中識別問題并調試它們是很復雜的。這種較早的驗證階段需要進行仿真,因此SoC風格的FPGA看起來越來越像一個ASIC。考慮到這兩個過程,它們之間的協(xié)同使得過程更加高效,包括常見的調試和測試平臺。新的進展,如便攜式激勵(Portable Stimulus)會提供這種協(xié)同性,事實上,使得SoC FPGA更易于管理了。”

07

結論

Sherer說,展望未來,用戶正在尋求把那種在ASIC世界更嚴格的工藝整合到FPGA。

“有大量的培訓和分析,他們希望在FPGA中有更多的技術用于調試,以獲得這樣的支持。”他說。“FPGA社區(qū)傾向于落后于現有技術,傾向于使用非常傳統(tǒng)的方法。因此,他們需要在空間、規(guī)劃和管理、需求追溯等方面進行培訓和培養(yǎng)意識。來自SoC流程的那些元素在FPGA中是絕對必要的,而FPGA本身并沒有推動這個那么多,而是那些最終應用的工業(yè)標準在推動它。需要對在FPGA環(huán)境下工作的工程師進行再培訓和再教育。”

在大量需要靈活性的應用驅動下,ASIC和FPGA之間的界限正變得模糊,系統(tǒng)架構越來越多地結合可編程性與硬件邏輯,以及工具,這些現在都適用于兩者。這種趨勢不太可能很快改變,因為許多新應用領域要求的這些組合仍然還處于萌芽階段。

電子發(fā)燒友App

電子發(fā)燒友App

評論