講解xilinx FPGA 使用mig IP對DDR3的讀寫控制,旨在讓大家更快的學習和應用DDR3。 本實驗和工程基于Digilent的Arty Artix-35T FPGA開發板完成。 軟件

2020-12-16 15:47:59 1692

1692

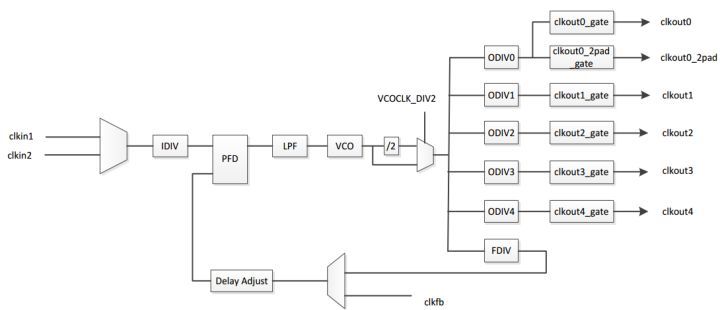

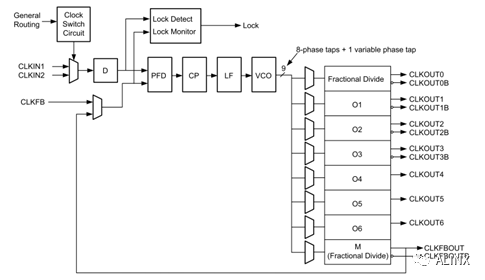

也有類似的功能模塊,通過PLL可以倍頻分頻,產生其他很多時鐘。本實驗通過調用PLL ip core來學習PLL的使用方法。

2021-02-04 13:22:00 6661

6661

上文XILINX FPGA IP之Clocking Wizard詳解說到時鐘IP的支持動態重配的,本節介紹通過DRP進行MMCM PLL的重新配置。

2023-06-12 18:24:03 5528

5528

在我們設計工程中我們會用到100M,500M等時鐘,如果我們的晶振達不到我們就需要倍頻,再上一個文檔中我們了解到了分頻,可是倍頻我們改怎么做了,這里我們就用了altera的IP核鎖相環。今天我們將去學習

2019-06-17 08:30:00

FPGA硬核與軟核處理器有什么區別和聯系?

2023-05-30 20:36:48

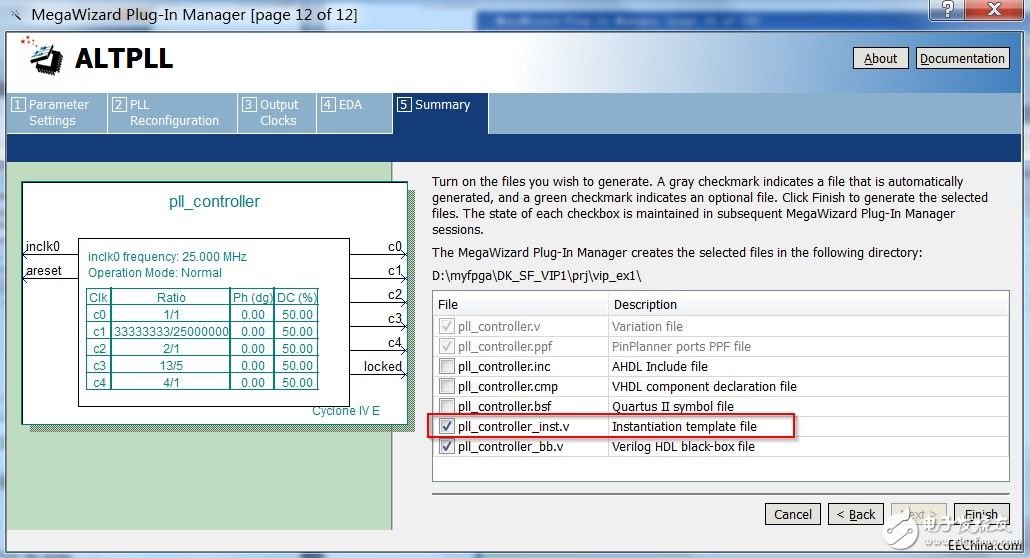

在配置PLL過程中,打開了megawizard plug-in manager后,下拉菜單中沒有IO這個選項,更別說選ATLPLL了,求問這是什么情況!PLL配置教程原帖http

2017-03-22 09:58:41

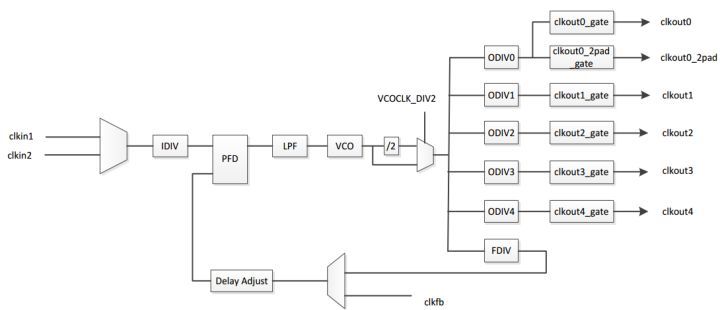

,Lattice公司的新型芯片上同時集成了PLL和DLL。PLL 和DLL可以通過IP核生成的工具方便地進行管理和配置。DLL的結構如圖1-5所示。7. 內嵌專用硬核 內嵌專用硬核是相對底層嵌入的軟核

2017-05-09 15:10:02

如果要學習關于FPGA的pll搭建和讓工程在有源碼的情況下一步一步變為例程中那樣有序的工程,該做那些準備呢?

2016-12-28 00:46:41

,Lattice公司的新型芯片上同時集成了PLL和DLL。PLL 和DLL可以通過IP核生成的工具方便地進行管理和配置。DLL的結構如圖1-5所示。圖1-5 典型的DLL模塊示意圖7. 內嵌專用硬核內嵌專用硬核

2023-05-30 20:53:24

的情況時,總會遇到一些以前未曾接觸過的新內容,這些新內容會讓我們感到陌生和恐懼,不知道該如何下手。

那么今天以xilinx vivado 為例分享學習FPGA 新IP核的正確打開方式。

一、常規

2023-11-17 11:09:22

文檔創建既然是ROM,那么我們就必須實現給它準備好數據,然后在FPGA實際運行時,我們直接使用這些預存儲好的數據就行。Xilinx FPGA的片內ROM支持初始化數據配置。如圖所示,我們可以創建一個名為

2019-04-08 09:34:43

寄存器和查找表的組合模式也不同。 學習底層配置單元的LUT和Register比率的一個重要意義在于器件選型和規模估算。由于FPGA內部除了基本可編程邏輯單元外,還有嵌入式的RAM、PLL或者是DLL

2019-09-24 11:54:53

寄存器和查找表的組合模式也不同。 學習底層配置單元的LUT和Register比率的一個重要意義在于器件選型和規模估算。由于FPGA內部除了基本可編程邏輯單元外,還有嵌入式的RAM、PLL或者是DLL

2016-07-16 15:32:39

寄存器和查找表的組合模式也不同。 學習底層配置單元的LUT和Register比率的一個重要意義在于器件選型和規模估算。由于FPGA內部除了基本可編程邏輯單元外,還有嵌入式的RAM、PLL或者是DLL

2016-08-23 10:33:54

寄存器和查找表的組合模式也不同。 學習底層配置單元的LUT和Register比率的一個重要意義在于器件選型和規模估算。由于FPGA內部除了基本可編程邏輯單元外,還有嵌入式的RAM、PLL或者是DLL

2016-09-18 11:15:11

寄存器和查找表的組合模式也不同。 學習底層配置單元的LUT和Register比率的一個重要意義在于器件選型和規模估算。由于FPGA內部除了基本可編程邏輯單元外,還有嵌入式的RAM、PLL或者是DLL

2016-10-08 14:43:50

的主流形式之一。 硬核 (Hard IP Core) :硬核在EDA 設計領域指經過驗證的設計版圖;具體在FPGA 設計中指布局和工藝固定、經過前端和后端驗證的設計,設計人員不能對其修改。不能修改的原因

2018-09-03 11:03:27

如何根據成本、功耗和性能來選擇微處理器?FPGA結構中硬核和軟核的特點是什么?處理器IP有什么重要性?

2021-04-08 06:16:37

不多說,上貨。IP CORE 之 PLL- ISE 操作工具本篇實現基于叁芯智能科技的SANXIN -B02 FPGA開發板,如有入手開發板,可以登錄官方淘寶店購買,還有配套的學習視頻。Xilinx

2023-04-06 16:04:21

在我的一個FPGA類中,我被要求使用coregen創建一個blcok ram(8dx16w),單端口ram IP。我在Windows XP,Service Pack 3上使用Xilinx ISE

2019-06-05 13:39:14

。圖像識別是一項相當復雜的機器學習任務,通常

需要比關鍵字識別更高的性能。

該指南也適用于想要為高端智能設備創建SoC的系統設計人員設備,比如智能手機。

具體來說,該指南解釋道:

?為什么要為這個

2023-08-02 11:02:42

。通過寫寄存器將AD9364狀態置為FDD狀態時(reg[0x017]=0x1A),發現FPGA內部PLL不能保持鎖定狀態了。 請教大家哪個寄存器的配置有問題會造成上述現象?附件1.png17.2 KB

2018-08-20 07:20:29

zynq是xilinx的新一代的嵌入ARM硬核的SOC,請問1、這種FPGA器件相對以往傳統FPGA有哪些優勢和劣勢?2、針對圖像和視頻處理的,這兩類哪一種器件更適合?3、相同價格的情況下,ARM硬核的引入相比傳統FPGA是否會降低zynq的性價比和靈活度?

2022-07-25 14:35:16

)放置flash 偏移地址0x50000處,關閉看門狗,重新配置后,發現fpga只更新了硬核,軟核沒有運行。通過測試,發現更新完硬核后,軟核還是找到的第一個程序軟核入口。沒有找到要更新程序軟核入口地址。不知道如何設置,使重新配置后,能夠找到更新程序軟核地址?希望大神幫助。。感激

2017-07-30 10:21:09

Altera可重配置PLL使用手冊在實際應用中,FPGA的工作時鐘頻率可能在幾個時間段內變動,對于與之相關的鎖相環(PLL),若PLL的輸入時鐘在初始設定的時鐘頻率的基礎上變化不太大時,PLL一般

2009-12-22 11:27:13

擁有成本,從而帶來可持續的長期盈利能力。美高森美公司(Microsemi)提供具有硬核ARM Cortex-M3微控制器和IP集成的SmartFusion2 SoC FPGA器件,它采用成本優化的封裝

2019-06-24 07:29:33

EG_PHY_PLL 是 FPGA 內部的時鐘鎖相環硬核 IP 模塊,Eagle 系列 FPGA 內嵌 4 個多功能鎖相環(PLL0~PLL3),分布在器件四角,可實現高性能時鐘管理功能。每個

2022-10-27 07:45:54

嗨! Ultrascale + 100G以太網硬核IP是否支持RS_FEC?如果是,我們如何訪問RS_FEC?

2020-05-22 15:18:57

Xilinx FPGA入門連載24:PLL實例之基本配置 1 工程移植可以復制上一個實例sp6ex7的整個工程文件夾,更名為sp6ex8。然后在ISE中打開這個新的工程。 2 新建IP核文件

2019-01-21 21:33:40

`Xilinx FPGA入門連載24:PLL實例之基本配置特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 工程移植可以復制上一個實例

2015-11-16 12:09:56

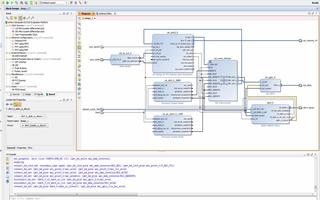

本實驗通過調用PLL IP core來學習PLL的使用、vivado的IP core使用方法。

2021-03-02 07:22:13

我用xilinx spartan-6fpga 它硬核的管腳是固定的還是可配置的我在xilinx提供的文檔里找不到關于硬核管腳的分配求指導

2012-08-11 09:28:44

`PLL鎖相環介紹與簡單應用實驗目的:1.學會配置Altera提供的PLL IP核并進行仿真了解其接口時序2.利用參數化設計一個簡易的系統進行驗證已配置好的PLL實驗平臺:芯航線FPGA學習套件主板

2017-01-05 00:00:52

,Altera 公司的芯片集成了PLL。7. 內嵌專用硬核內嵌專用硬核是相對底層嵌入的軟核而言的,指FPGA 處理能力強大的硬核(Hard Core),等效于ASIC 電路。為了提高FPGA 性能,芯片生產商在芯片內

2012-03-08 11:03:49

本帖最后由 蛙蛙蛙 于 2021-4-12 17:51 編輯

本視頻是Runber FPGA開發板的配套視頻課程,主要通過PLL的工程實例講解高云IP core的使用,課程主要介紹什么是IP

2021-04-12 16:45:11

基于Lattice MXO2 LPC的小腳丫FPGA核心板 - Type C接口

開發板的硬件規格如下:

核心器件:Lattice LCMXO2-4000HC-4MG132

132腳BGA封裝

2024-01-31 21:01:32

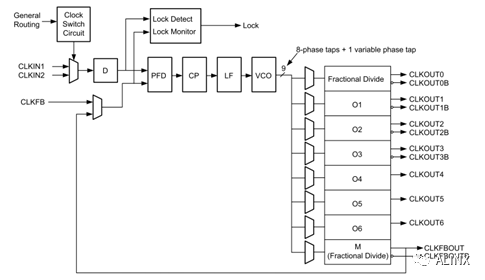

/PLL IP核的使用方法是我們學習FPGA的一個重要內容。本章我們將通過一個簡單的例程來向大家介紹一下MMCM/PLL IP核的使用方法。本章包括以下幾個部分:1111.1MMCM/PLL IP核簡介

2020-09-22 16:48:59

,以PLL為例。 過程創建工程創建空的工程pll IP核配置Tools->IP Compiler 看到又如下IP 選擇PLL下的PLL(1.5),設置實例名Instance Name,點擊

2023-02-09 23:21:59

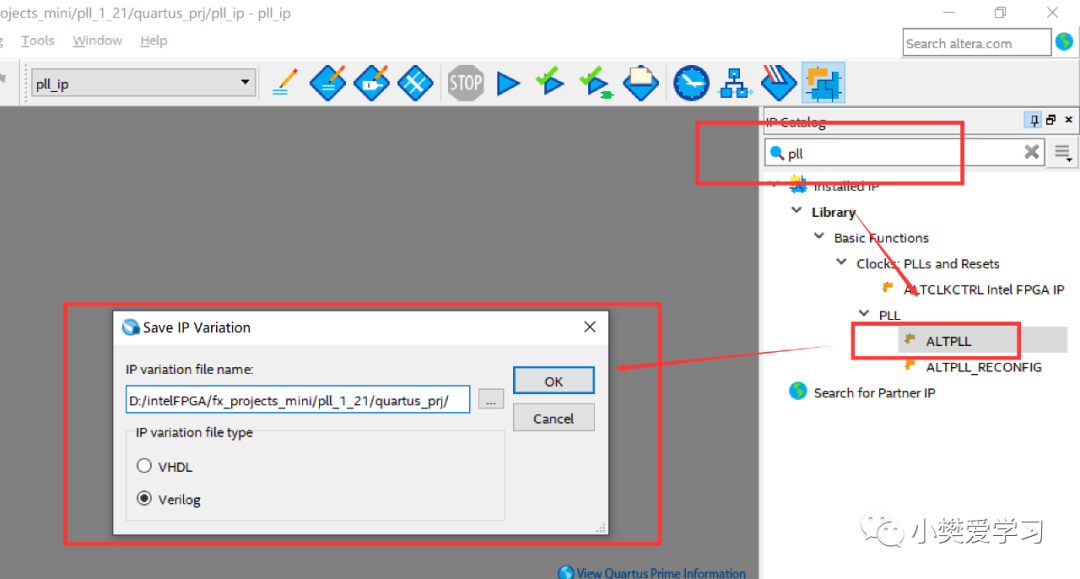

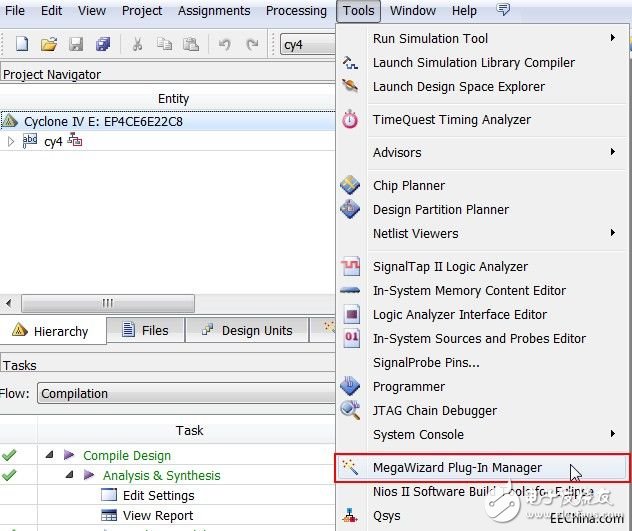

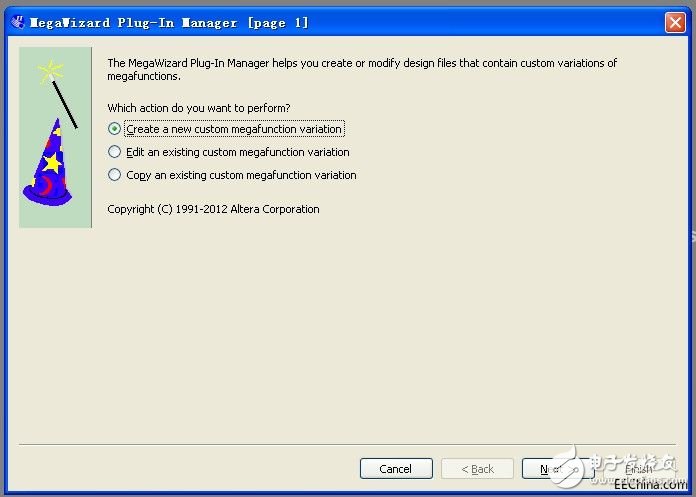

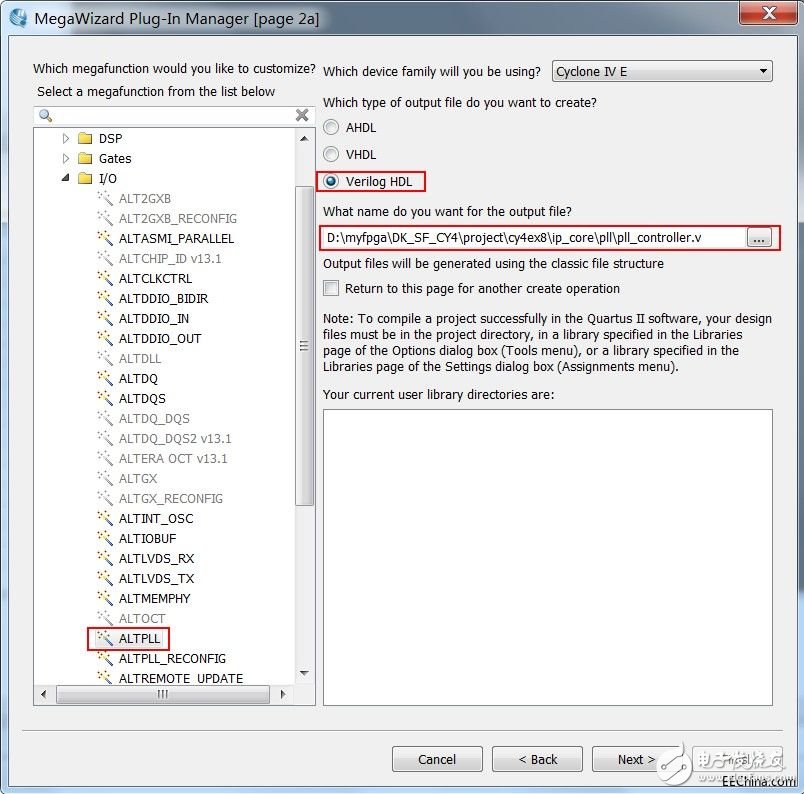

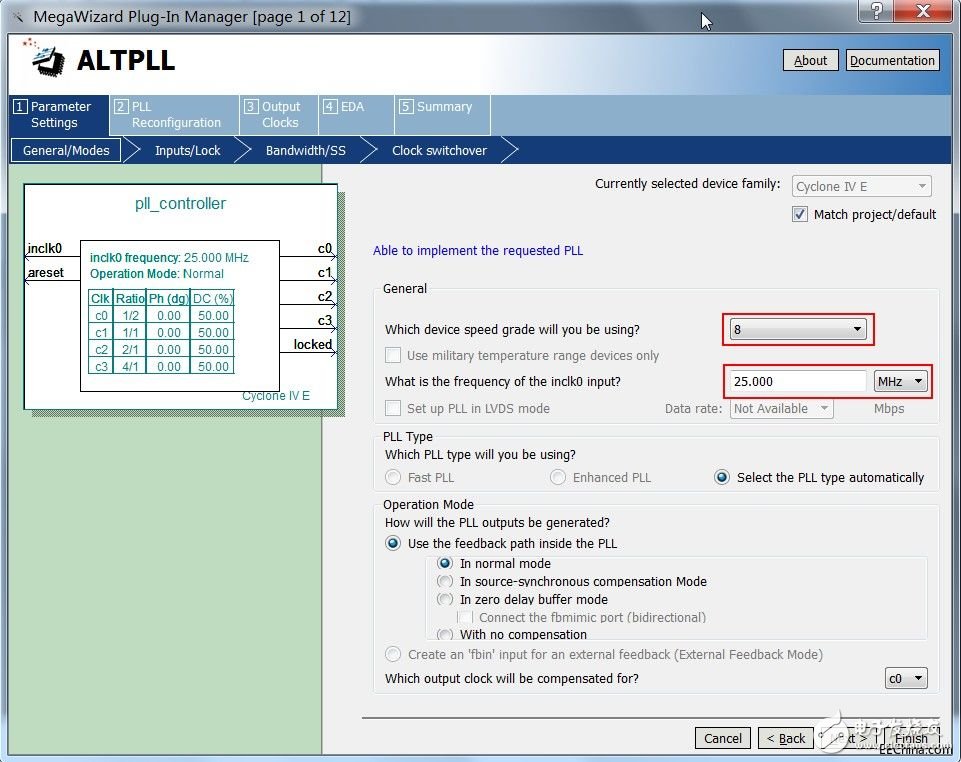

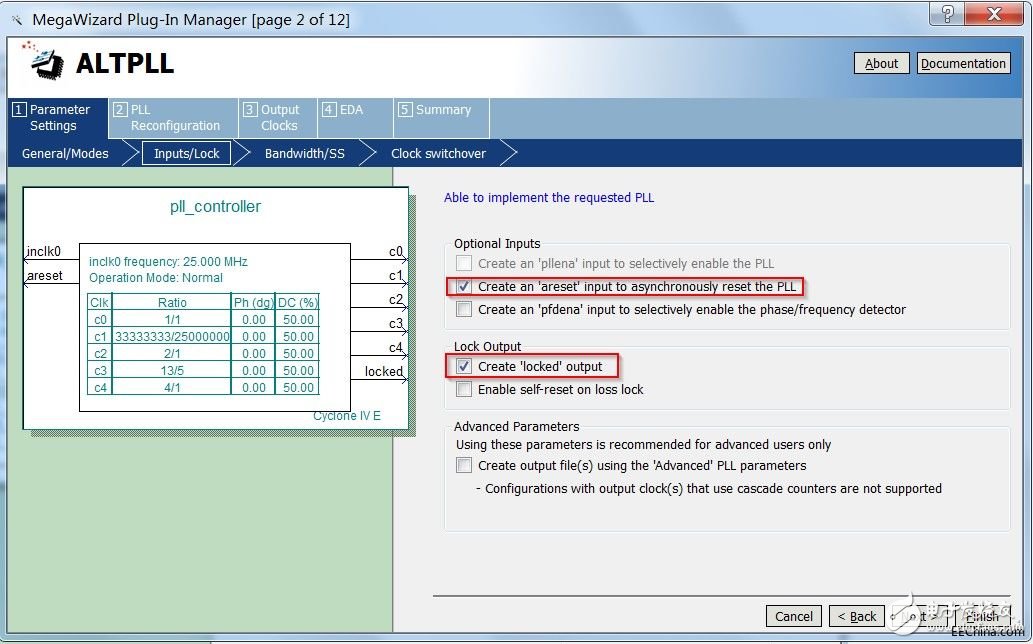

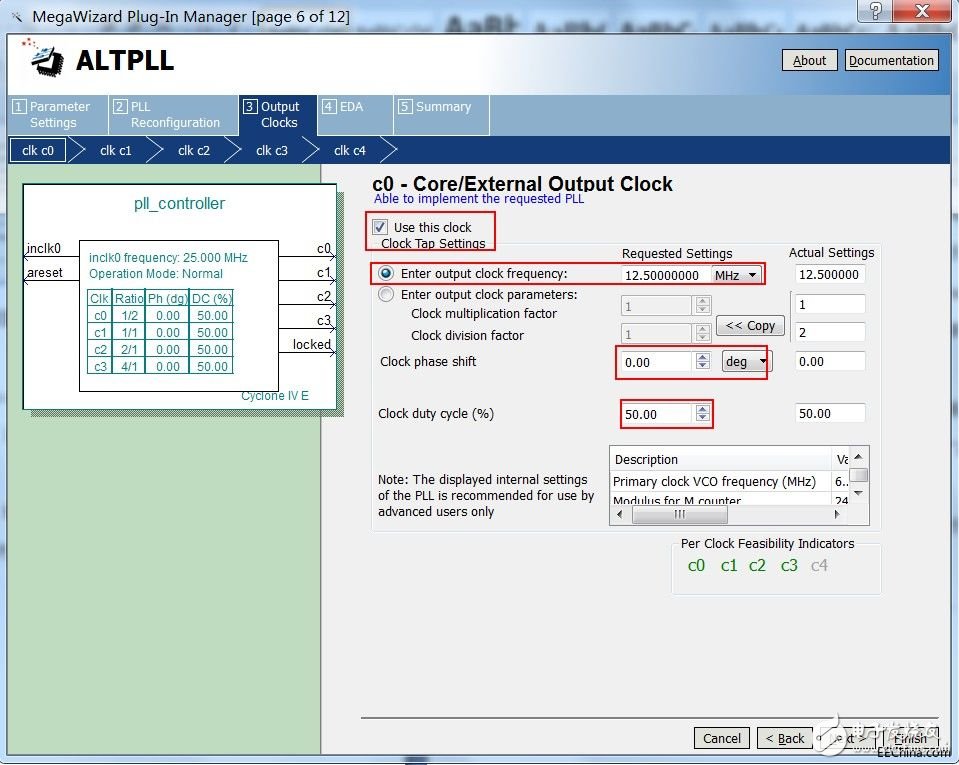

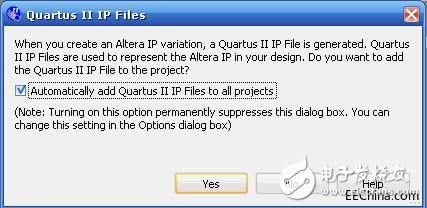

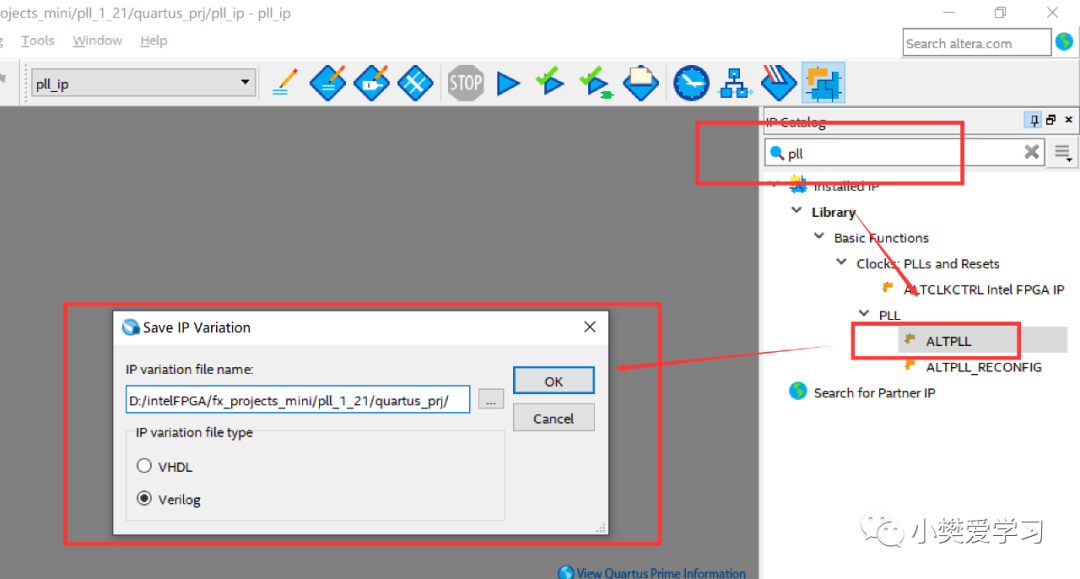

通過Quartus II 軟件創建PLL IP核。首先,要新建一個工程,這個方法在之前的帖子中已經發過,不會的可以查看前面的相關帖子。創建好自己的工程:打開如下的菜單

2016-09-23 21:44:10

的時鐘。首先建立一個文件在ip核目錄里搜索ALTPLL然后在工程文件的par文件里建立一個文件夾ipcore將剛剛的變化保存到文件里命名為pll_clk然后點擊ok就會出現配置過程界面FPGA系統晶振為

2020-01-13 18:13:48

`例說FPGA連載30:PLL例化配置與LED之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 本實例使用Quartus II

2016-09-09 18:29:24

`例說FPGA連載31:PLL例化配置與LED之PLL的IP核配置特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 本實例使用了一個

2016-09-12 17:31:43

。比如:怎么創建工程,怎么添加文件,怎么跑一系列編譯的流程,怎么加入時序約束,怎么分配管腳,然后怎么把生成的FPGA映像加載到開發板上運行。

第二,就是熟悉一些常用的IP的用法

。在FPGA項目中,我們

2024-01-02 23:03:31

FPGA的硬核和軟核有什么區別呢,有沒有使用硬核的開發板,想學習關于FPGA硬核的知識,各位大神有什么建議呢?真心求教

2013-03-05 11:51:54

本人想問下,FPGA的介紹中有些事說帶有PCIe硬核的,那么這個FPGA直接購買后就可以使用這個硬核完成PCIE功能了嗎?不再需要購買其他什么許可文件之類的東西了嗎? 這點不是很清楚,順便問一下帶有這中硬核的FPGA大概要多少錢呢?

2012-12-12 17:52:08

`勇敢的芯伴你玩轉Altera FPGA連載63:PLL IP核創建于配置特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD 可以復制上一個

2018-04-20 21:45:06

如何使用部分PLL創建調制波形

2021-04-06 06:19:42

和硬核都必需的一些可交付使用的提供物。1.文檔創建清晰和簡練的文檔是大多數技術產品的先決條件。然而,需要參考IP核文檔的人差異非常大,這使IP核技術文檔創建面臨非常大的挑戰。在圖1中,每一個開發活動都有

2021-07-03 08:30:00

[]()使用SF1的硬核使用IP Generator生成RISC-V硬核和PLL核創建工程并選擇器件為SF160CG121I。點擊Tools->IP Generator,選擇

2023-04-16 17:34:01

大家好我正在使用Zynq ZC702板。如何創建自己的PLL時鐘?例如,我的IP需要25MHz時鐘我嘗試了以下方法1. XPS中的時鐘向導2.AXI時鐘發生器但我仍然無法獲得25MHz的時鐘。誰能幫我?謝謝

2019-09-03 10:43:07

在線求助是否有帶DA或者AD硬核的fpga 還是只能由外置的da ad

2012-06-01 14:49:26

往往需要使用多個時鐘和時鐘相位的偏移,且通過編寫代碼輸出的時鐘無法實現時鐘的倍頻,因此學習Altera PLL IP核的使用方法是我們學習FPGA的一個重要內容。本章我們將通過一個簡單的例程來向大家

2020-07-30 14:58:52

LED,而是IP核的應用,當然,僅以PLL IP核為例。2 模塊化設計參考文檔《玩轉Zynq-基礎篇:基于FPGA的模塊化設計.pdf》。3 PLL IP核添加配置 3.1Vivado標準IP核概述我們

2019-09-06 08:13:18

本文檔主要是以Altera公司的Stratix II系列的FPGA器件為例,介紹了其內嵌的增強型可重配置PLL在不同的輸入時鐘頻率之間的動態適應,其目的是通過提供PLL的重配置功能,使得不需要對

2010-11-02 15:17:24 27

27 在開始查找PLL的最佳配置之前,需要考慮的是如何才能為PLL找到配置。具體而言,我們應找到PLL針對給定參考振蕩器和所需輸出頻率所使用的所有可行配置。只有在確保獲得能夠滿足需

2012-11-22 10:34:32 3472

3472 FPGA Cyclone器件中PLL的配置方法

2016-02-23 11:04:13 5

5 JAVA教程之創建和配置數據源,很好的JAVA的資料,快來學習吧。

2016-04-12 17:41:43 6

6 單片機是基于FLASH結構的,所以單片機上電直接從本地FLASH中運行。但SRAM 架構的FPGA是基于SRAM結構的,掉電數據就沒了,所以需要借助外部電路來配置運行的數據,其實我們可以借助Vivado來學習FPGA的各種配置模式。

2018-11-05 15:12:57 7298

7298 了解如何在IP Integrator中創建簡單的MicroBlaze設計,并創建一個在KC705目標板上運行的簡單軟件應用程序。

2018-11-20 06:13:00 2836

2836

本視頻介紹了使用IP Integrator(IPI)創建簡單硬件設計的過程。

使用IPI可以無縫,快速地實現DDR4和PCIe等塊

連接在一起,在幾分鐘內創建硬件設計。

2018-11-22 06:13:00 4157

4157

該篇不僅講解了如何使用Quartus II軟件、ModelSim和SignalTap II軟件,還講解了PLL、ROM、RAM和FIFO IP核的使用。從第一個新工程建立,管腳分配,程序下載及工程

2019-12-06 07:03:00 2931

2931 先用FPGA的外部輸入時鐘clk將FPGA的輸入復位信號rst_n做異步復位、同步釋放處理,然后這個復位信號輸入PLL,同時將clk也輸入PLL。設計的初衷是在PLL輸出有效時鐘之前,系統的其他部分都保持復位狀態。

2020-03-29 17:19:00 2456

2456

,但是也有類似的功能模塊,通過PLL可以倍頻分頻,產生其他很多時鐘。本實驗通過調用PLL IP core來學習PLL的使用、vivado的IP core使用方法。

2022-02-08 15:13:17 3306

3306

,但是也有類似的功能模塊,通過PLL可以倍頻分頻,產生其他很多時鐘。本實驗通過調用PLL IP core來學習PLL的使用、vivado的IP core使用方法。

2021-01-29 09:30:52 7

7 本文檔的主要內容詳細介紹的是在FPGA上編寫通過SPI總線配置外部PLL芯片AD9518和ADC9268的程序免費下載。

2021-03-10 15:50:00 50

50 在FPGA中配置PLL的步驟及使用方法

2021-05-28 10:01:17 20

20 設計的帶嵌入式收發器的Gen1×1硬核IP的 PCI Express IP編譯器(基于嵌入式開發游戲項目)-在Cyclone IV GX收發器入門套件上,設計帶嵌入式收發器的Gen1×1硬核IP的 PCI Express IP編譯器。.rar

2021-07-30 16:48:41 9

9 在FPGA上編寫的通過SPI總線配置外部PLL芯片AD9518和ADC9268的程序(開關電源技術與設計潘永雄.pdf)-在FPGA上編寫的通過SPI總線配置外部PLL芯片AD9518和ADC9268的程序,適合感興趣的人學習參考

2021-09-16 11:37:05 61

61 內嵌處理器硬核的FPGA,即SoC FPGA,是在芯片設計之初,就在內部的硬件電路上添加了硬核處理器,是純硬件實現的,不會消耗FPGA的邏輯資...

2022-01-26 19:23:29 2

2 在FPGA實際的開發中,官方提供的IP并不是適用于所有的情況,需要根據實際修改,或者是在自己設計的IP時,需要再次調用時,我們可以將之前的設計封裝成自定義IP,然后在之后的設計中繼續使用此IP。因此本次詳細介紹使用VIvado來封裝自己的IP,并使用IP創建工程。

2022-04-21 08:58:05 4579

4579 電子發燒友網站提供《EF3 PLL動態配置.pdf》資料免費下載

2022-09-27 10:26:04 0

0 電子發燒友網站提供《ELF2 FPGA PLL動態配置.pdf》資料免費下載

2022-09-26 15:13:06 0

0 定時決定一切:如何使用部分 PLL 創建調制波形

2022-11-04 09:52:13 0

0 IP_數據表(A-3):Analog-PLL For Frequency Multiplying

2023-03-16 19:27:15 0

0 IP_數據表(A-6):Analog-PLL For Skew adjust

2023-03-16 19:27:43 0

0 IP_數據表(A-9):Analog-PLL For Skew adjust

2023-03-16 19:28:21 0

0 IP_數據表(A-1):Analog-PLL For Frequency Multiplying

2023-03-16 19:30:25 0

0 IP_數據表(A-4):Analog-PLL For Frequency Multiplying

2023-03-16 19:30:43 0

0 IP_數據表(A-7): 用于小數乘法的模擬 PLL

2023-03-16 19:30:54 3

3 LiteX 框架為創建 FPGA 內核/SoC、探索各種數字設計架構和創建完整的基于 FPGA 的系統提供了方便高效的基礎架構。

2023-06-28 09:08:05 425

425

IP_數據表(A-3):Analog-PLL For Frequency Multiplying

2023-07-06 20:13:27 0

0 IP_數據表(A-6):Analog-PLL For Skew adjust

2023-07-06 20:14:06 0

0 IP_數據表(A-9):Analog-PLL For Skew adjust

2023-07-06 20:14:39 0

0 IP_數據表(A-1):Analog-PLL For Frequency Multiplying

2023-07-06 20:16:34 0

0 IP_數據表(A-4):Analog-PLL For Frequency Multiplying

2023-07-06 20:16:44 0

0 IP_數據表(A-7): 用于小數乘法的模擬 PLL

2023-07-06 20:17:04 1

1 在ip目錄里搜索pll,選擇ALTPLL,點擊打開后設置名稱并自動保存在目錄中。

2023-07-19 16:37:34 665

665

IP(Intellectual Property)是知識產權的意思,半導體行業的IP是“用于ASIC或FPGA中的預先設計好的電路功能模塊”。一些常用的復雜的功能模塊(如FIFO、RAM、FIR

2023-08-22 15:04:43 1523

1523

pll鎖相環的作用 pll鎖相環的三種配置模式? PLL鎖相環是現代電子技術中廣泛應用的一種電路,它的作用是將一個特定頻率的輸入信號轉換為固定頻率的輸出信號。PLL鎖相環的三種配置模式分別為

2023-10-13 17:39:48 1102

1102

電子發燒友App

電子發燒友App

評論