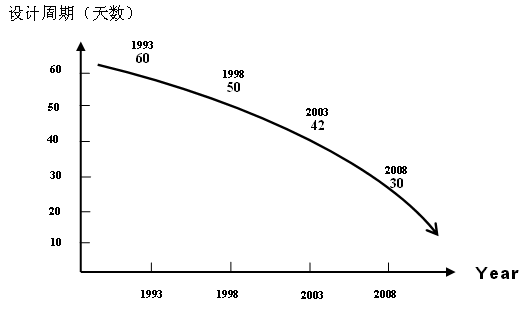

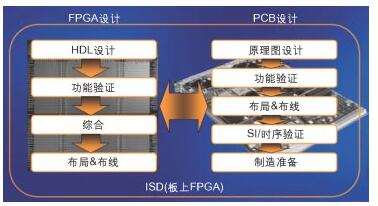

復(fù)雜度日益增加的系統(tǒng)設(shè)計(jì)要求高性能FPGA的設(shè)計(jì)與PCB設(shè)計(jì)并行進(jìn)行。通過整合FPGA和PCB設(shè)計(jì)工具以及采用高密度互連(HDI)等先進(jìn)的制造工藝,這種設(shè)計(jì)方法可以降低系統(tǒng)成本、優(yōu)化系統(tǒng)性能并縮短設(shè)計(jì)周期。

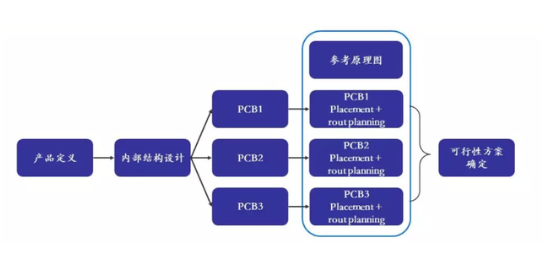

圖1 FPGA和PCB

設(shè)計(jì)團(tuán)隊(duì)必須并行工作,不斷地交換數(shù)據(jù)和信息以確保系統(tǒng)設(shè)計(jì)成功

電子工業(yè)背后的推動(dòng)力是對更快、更便宜的產(chǎn)品的需求以及在競爭廠商之前將產(chǎn)品推向市場。IC技術(shù)的進(jìn)步一直以來就是促使功能增加和性能提高的主要因素之一,而FPGA技術(shù)也一直以非常快的速度在發(fā)展。與過去FPGA僅僅用作膠合邏輯不同的是,現(xiàn)在FPGA已經(jīng)被用來實(shí)現(xiàn)主要系統(tǒng)功能。FPGA的邏輯門數(shù)已達(dá)1千萬,內(nèi)核速度達(dá)到400MHz,能提供高達(dá)11Gbps的下一代芯片間通信速度。而與此同時(shí),它仍然保持著非常合理的成本,因此,與ASIC和定制IC相比,F(xiàn)PGA是一種更具有吸引力的選擇。

IC和FPGA技術(shù)的進(jìn)步對下游產(chǎn)業(yè)產(chǎn)生的效應(yīng)影響到了PCB行業(yè),這些高管腳數(shù)和高性能封裝推動(dòng)新的PCB生產(chǎn)及設(shè)計(jì)技術(shù)具有諸如嵌入無源器件、數(shù)千兆位信號和EMI分析等功能,并對專用的高密度和高性能布線提出了需求。基本的系統(tǒng)設(shè)計(jì)方法也在發(fā)生變化,對FPGA和PCB的設(shè)計(jì)可以并行進(jìn)行以降低系統(tǒng)成本、優(yōu)化系統(tǒng)性能并縮短設(shè)計(jì)周期。

PCB和FPGA一般是在不同的設(shè)計(jì)環(huán)境下創(chuàng)建,過去這些設(shè)計(jì)方案很少相互溝通。然而,隨著高性能、高密度FPGA器件的日益流行,為滿足緊張的上市時(shí)間表,如今PCB和FPGA設(shè)計(jì)團(tuán)隊(duì)必須并行工作(見圖1),不斷地交換數(shù)據(jù)和信息以確保整個(gè)系統(tǒng)設(shè)計(jì)獲得成功。

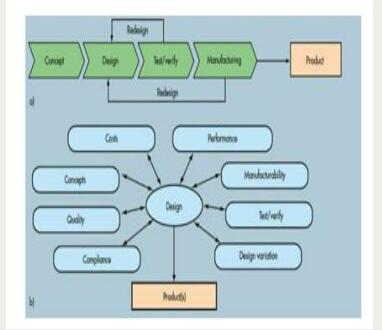

當(dāng)在PCB上實(shí)現(xiàn)高端FPGA時(shí),設(shè)計(jì)工程師面臨性能優(yōu)化和系統(tǒng)設(shè)計(jì)生產(chǎn)率的雙重挑戰(zhàn)。設(shè)計(jì)工程師必須問自己:是什么問題使得過程慢了下來?需要做什么來獲得最佳性能?這些問題的答案可幫助他們鑒別可實(shí)現(xiàn)更小、更便宜和更快系統(tǒng)的解決方案。

設(shè)計(jì)效率的挑戰(zhàn)

設(shè)計(jì)工程師需要并行設(shè)計(jì)PCB和FPGA時(shí),F(xiàn)PGA設(shè)計(jì)工程師再也不能像以前那樣獨(dú)立地設(shè)計(jì),然后將完成的FPGA設(shè)計(jì)交給PCB設(shè)計(jì)工程師就可了事。一個(gè)有競爭力的設(shè)計(jì)要求FPGA和PCB設(shè)計(jì)工程師從上至下的協(xié)作,各自做些折衷以保證最后得到一個(gè)最優(yōu)系統(tǒng)。并行設(shè)計(jì)的好處是它能減少設(shè)計(jì)周期、優(yōu)化系統(tǒng)性能并降低制造成本。

并行設(shè)計(jì)的挑戰(zhàn)在于FPGA布局和布線工具得到的結(jié)果需要準(zhǔn)確、迅速地映射到原理圖和PCB布局中,同時(shí)PCB設(shè)計(jì)的任何改變也必須在FPGA上更新。傳統(tǒng)的設(shè)計(jì)過程是先設(shè)計(jì)FPGA,然后再將它們交給PCB設(shè)計(jì)工程師進(jìn)行電路板實(shí)現(xiàn),如今這種做法不再可行。

如果FPGA設(shè)計(jì)/綜合、布局/布線以及PCB設(shè)計(jì)環(huán)境沒有被整合,F(xiàn)PGA和PCB方案之間的溝通必須用人工的方法來實(shí)現(xiàn)。對于有幾百個(gè)管腳的小型FPGA,這可能還可以接受,但是,如今很多設(shè)計(jì)擁有多個(gè)高度復(fù)雜的FPGA,使用這種方法進(jìn)行信息溝通將非常浪費(fèi)時(shí)間,并容易出錯(cuò)。僅僅是高管腳數(shù)FPGA的PCB原理圖符號的創(chuàng)建和更新,就可以凸顯這個(gè)問題。

另外一個(gè)問題涉及到PCB上的大型FPGA。與小型FPGA的符號不同,大型FPGA的單個(gè)符號在一張?jiān)韴D放不下。這些符號必須通過功能分組被分成幾個(gè)符號,并在FPGA的設(shè)計(jì)反復(fù)過程中保持不變。

FPGA設(shè)計(jì)工程師花費(fèi)大量時(shí)間調(diào)整性能、選擇正確的I/O管腳驅(qū)動(dòng)器/接收器,然而FPGA的設(shè)計(jì)并非僅受FPGA設(shè)計(jì)工程師的控制。當(dāng)在PCB上進(jìn)行FPGA的布局和布線時(shí),設(shè)計(jì)環(huán)境可能要求改變FPGA的管腳分配,如果PCB工具中沒有FPGA設(shè)計(jì)規(guī)則,這可能成為一個(gè)重復(fù)而費(fèi)時(shí)的過程。

此外,F(xiàn)PGA 的I/O分配也成了一個(gè)系統(tǒng)問題。設(shè)計(jì)工具需要能夠管理管腳分配,但它們必須能被PCB和FPGA設(shè)計(jì)工程師用來溝通管腳約束。PCB設(shè)計(jì)工程師無法創(chuàng)建一個(gè)阻止FPGA時(shí)序收斂的條件,而FPGA設(shè)計(jì)工程師也不能創(chuàng)建一個(gè)阻止系統(tǒng)時(shí)序收斂的條件。

圖3、圖4給出的例子體現(xiàn)了裝配在PCB上的FPGA的性能優(yōu)化前后的布線情況。FPGA的32位總線必須直接與左邊連接器進(jìn)行通訊,這是一個(gè)高速總線,其上所有網(wǎng)絡(luò)必須匹配以獲得適當(dāng)?shù)钠笨刂啤?/p>

在圖3中,為使所有的走線長度與最長網(wǎng)絡(luò)相匹配,布線器增加了很多蛇形走線。從PCB布線的角度來看,其結(jié)果是一團(tuán)糟:有很多額外的擁塞、太多額外的走線以及一個(gè)工作性能并非最優(yōu)的總線。

圖3 FPGA性能優(yōu)化前的布線圖

在圖4中,布線器也對所有的走線長度與最長走線進(jìn)行了匹配。即使這樣,每條走線的長度也只有1.8英寸,而此前為3.2英寸,更短的匹配長度使總線延時(shí)減少到320皮秒。這種性能優(yōu)化是整合FPGA和PCB設(shè)計(jì)過程的結(jié)果,它可獲得理想的FPGA管腳圖。

圖4 FPGA性能優(yōu)化后的布線圖

這個(gè)例子說明了在PCB上裝配FPGA可能存在的挑戰(zhàn),包括:額外的擁塞需要更長的PCB設(shè)計(jì)時(shí)間完成布線;并非最優(yōu)的系統(tǒng)性能;額外的布線要求額外的PCB層,從而增加制造成本。

功能方面的性能障礙

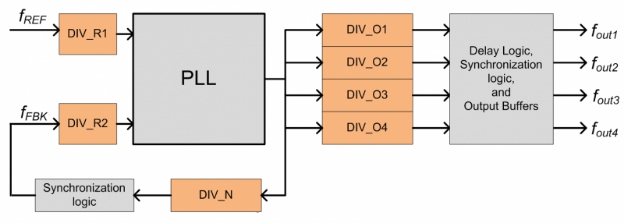

IC和FPGA器件已經(jīng)過優(yōu)化以便得到更高性能,例如,它們現(xiàn)在能夠?qū)崿F(xiàn)每秒數(shù)Gb的串行通訊性能。從時(shí)序收斂、信號完整性以及全面降低PCB布線密度的角度來看,這種方法有以下幾個(gè)優(yōu)點(diǎn):

(1) 時(shí)序校準(zhǔn)沒那么嚴(yán)格:時(shí)鐘包含在串行信號內(nèi),因此設(shè)計(jì)工程師不需要管理時(shí)鐘和數(shù)據(jù)之間的時(shí)序;

(2) 改善信號完整性:所有信號都使用差分線對,可提高信號質(zhì)量;

(3) 布線簡化:串行信號沿一條路徑(實(shí)際上是差分線對)傳輸,而不是在具有多條走線的總線上并行傳輸,這意味著互連需要較少的走線和層數(shù);

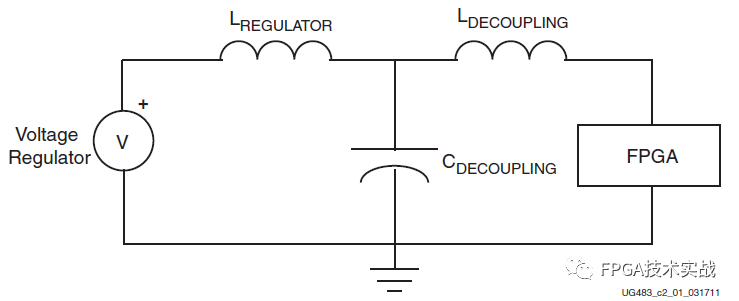

(4) 片上端接:通過在FPGA內(nèi)集成可變電阻端接器,板上需要的表面貼器件更少,可以節(jié)省空間并提高性能。在更新的器件里還包含了片上電容,可節(jié)省更多的空間。

在系統(tǒng)中使用這些高端FPGA則使PCB設(shè)計(jì)成為整個(gè)系統(tǒng)設(shè)計(jì)取得成功的關(guān)鍵途徑,其中系統(tǒng)必須能高速運(yùn)行,并具有生產(chǎn)成本效益,還能按時(shí)設(shè)計(jì)出來。

每秒數(shù)Gb的通訊速度要求一套能夠進(jìn)行信號走線并驗(yàn)證的全新工具。這時(shí)PCB上的走線、連接器和過孔也需要消耗功率,必須小心地對它們建模,用經(jīng)典的信號完整性分析方法計(jì)算延時(shí)、過沖/下沖和串?dāng)_。另外還必須用理解位模式、預(yù)加重、均衡和眼圖,對工作在GHz頻率范圍的串行連接進(jìn)行建模。EDA和FPGA供應(yīng)商也正在協(xié)作,以“設(shè)計(jì)套件”的形式提供準(zhǔn)確的器件模型、設(shè)計(jì)約束和參考設(shè)計(jì),這都將提高設(shè)計(jì)質(zhì)量并縮短設(shè)計(jì)周期。

串行I/O還需要由公共系統(tǒng)約束驅(qū)動(dòng)的改進(jìn)的PCB布局和布線技術(shù),另外還須根據(jù)最大的匹配延時(shí)以及用到的過孔數(shù)量嚴(yán)格控制差分線對的走線。

先進(jìn)的PCB制造技術(shù)

高端FPGA的高管腳數(shù)和高管腳密度產(chǎn)生的另一個(gè)挑戰(zhàn)是需要將FPGA裝配到PCB上,然后再將它們連接到板上的其它IC。在很小的面積上有如此多管腳,以致采用普通PCB制造工藝幾乎不可能進(jìn)行內(nèi)部連線。其結(jié)果是,這些器件促進(jìn)了先進(jìn)PCB制造技術(shù)的采用,例如高密度互連(HDI)以及嵌入無源器件等。

HDI在PCB上使用IC制造技術(shù)。HDI層沉積在傳統(tǒng)PCB壓合層上(例如FR4),可以制造出很窄的走線和很小的過孔(微過孔),并很容易使扇出遠(yuǎn)離高密度封裝,通常是球柵陣列(BGA)或芯片級封裝(CSP)。另外,使用這些HDI技術(shù)還需要能夠理解這種PCB和IC混合生產(chǎn)技術(shù)的專用PCB布局軟件。

HDI/微過孔的好處包括:

減少產(chǎn)品尺寸:PCB基板的高度和厚度降低,體積也減小了;

增加走線密度:每個(gè)器件的連線更多,而器件布置得更緊密;

降低成本:HDI能減少電路板的層數(shù)和面積,使每塊大的裸板能產(chǎn)出更多電路板,削減生產(chǎn)成本;

改善電氣性能:HDI的寄生效應(yīng)只有通孔的十分之一,其引線更短,噪聲裕量更大;

降低無線電干擾(RFI)/EMI:因?yàn)榈仄矫娓咏蛘呔驮诒韺樱衫玫仄矫娴姆植茧娙荩蟠鬁p少RFI/EMI;

提高散熱效率:HDI層的絕緣介質(zhì)很薄,溫度梯度很高,可提高散熱性能;

提高設(shè)計(jì)效率:微過孔使雙面布局變得容易,還改善了器件管腳的走線(在焊盤上打過孔),因而留出更多的內(nèi)層布線空間;

提高良品率(DFM):由于間隙很小,HDI板幾乎不需要壓合;

減少層數(shù):通常需要10到12層板的表面貼技術(shù)(SMT),采用HDI制造工藝只需6層就可以實(shí)現(xiàn);

縮短設(shè)計(jì)周期:由于采用埋孔,布線空間更充足,可顯著減少設(shè)計(jì)時(shí)間。

此外,這些高管腳數(shù)器件需要很多去耦電容和端接電阻以保證工作性能,傳統(tǒng)的SMD無源器件會(huì)占用表面層的寶貴面積。通過將這些無源器件嵌入到PCB內(nèi)層,PCB的尺寸可大大減少,同時(shí)性能也能得到提高。

嵌入無源器件具有很多優(yōu)點(diǎn),包括:

增加設(shè)計(jì)密度:將無源SMD移入到內(nèi)層能讓其它器件布置得更緊密;

降低系統(tǒng)成本:雖然額外的步驟將增加生產(chǎn)成本,但是通過減少SMD并使電路板面積最小化,可降低整體系統(tǒng)成本;

減輕系統(tǒng)重量和電路板面積:去除SMD能減少電路板尺寸和重量;

提高性能:無源器件可以非常靠近有源器件,這可減少電感,提高性能;

提高可靠性和質(zhì)量:需要裝配的SMD越少意味著潛在的焊接故障越少;

增加功能:為增加功能創(chuàng)造了機(jī)會(huì),而不用擔(dān)心減少設(shè)計(jì)面積。

就像其它任何新興技術(shù)一樣,隨著支持它們的基礎(chǔ)技術(shù)的發(fā)展,其成本將下降。嵌入無源器件技術(shù)便是如此,它曾經(jīng)僅用于非常前沿的設(shè)計(jì),但現(xiàn)在它甚至用在那些要求小尺寸、高功能的消費(fèi)類產(chǎn)品中。

嵌入無源器件的設(shè)計(jì)關(guān)鍵是要有便于高效設(shè)計(jì)的自動(dòng)化工具。如果由人工來定義庫器件,那么要設(shè)計(jì)具有不同參數(shù)值和公差的數(shù)百個(gè)無源器件是不可能的,它需要由電阻和電容特性參數(shù)(來自元器件供應(yīng)商)驅(qū)動(dòng)的自動(dòng)綜合算法。這些綜合算法驅(qū)動(dòng)那些分析所有無源器件所需的權(quán)衡工具,并幫助確定最佳材料組合和外形尺寸。這些權(quán)衡工具有助于減少電路板上的器件數(shù)量,減少生產(chǎn)步驟和最終成本。

本文小結(jié)

從事電子產(chǎn)品設(shè)計(jì)的公司需要FPGA工具和PCB設(shè)計(jì)工具進(jìn)行緊湊、雙向地整合,還需要EDA和FPGA供貨商緊密合作。有了這種整合與合作,他們才能達(dá)到上市時(shí)間和性能的目標(biāo),

電子發(fā)燒友App

電子發(fā)燒友App

評論