英商康橋半導(dǎo)體宣布全新的一次側(cè)感應(yīng) (PSS) 返馳式控制晶片系列,可以大幅度降低高功率應(yīng)用設(shè)計(jì)的系統(tǒng)成本及零組件數(shù)量,同時(shí)也提供絕佳的輕載及待機(jī)效率性能。

2012-09-11 09:26:16 1862

1862 在FPGA上使用OpenCL標(biāo)準(zhǔn),與目前的硬件體系結(jié)構(gòu)(CPU、GPU,等)相比,能夠大幅度提高性能,同時(shí)降低了功耗。此外,與使用Verilog或者VHDL等底層硬件描述語(yǔ)言(HDL)的傳統(tǒng)FPGA

2014-05-26 09:10:18 3967

3967 降低至少一半;性能與容量翻番;采用的目標(biāo)設(shè)計(jì)平臺(tái)則大幅度提高了生產(chǎn)率;并且越來(lái)越少的設(shè)計(jì)人員選擇使用ASSP;ASIC同樣也難逃厄運(yùn)。總之,其前景可謂是一片“光明”。 當(dāng)然,想要一直保持“光明”狀態(tài)

2012-09-21 13:46:16

可編程邏輯的靈活性。可以有效降低系統(tǒng)功耗和成本,減小電路板面積,同時(shí)滿足性能要求。而且采用內(nèi)置糾錯(cuò)碼(ECC)和存儲(chǔ)器保護(hù)功能,保護(hù)用戶的系統(tǒng)不受硬件或者軟件錯(cuò)誤的影響,從而提高了系統(tǒng)可靠性

2014-08-01 14:12:39

電源引腳布局減小了22%,功耗降低了35%。圖1 2.有效應(yīng)對(duì)噪聲敏感輸入 因?yàn)?b class="flag-6" style="color: red">FPGA中許多模塊對(duì)供電電源噪聲非常敏感,而噪聲會(huì)導(dǎo)致產(chǎn)生抖動(dòng),隨之帶來(lái)很高的誤碼率(BER),降低了電路性能,而

2018-10-23 16:33:09

,采用低K值電介質(zhì)工藝,不僅提高了性能還降低了寄生電容。結(jié)構(gòu)的改變,如增強(qiáng)的邏輯單元內(nèi)部互連,可實(shí)現(xiàn)更強(qiáng)大的功能,而無(wú)需更多的功耗。StraTIx II更大的改變是采用了六輸入查找表(LUT)架構(gòu),能夠

2015-02-09 14:58:01

μs減小到5μs。這意味著顯著提高了功效,對(duì)應(yīng)驅(qū)動(dòng)90%的總體運(yùn)行成本。在這個(gè)例子中,SoC的功耗大約比三芯片方案低37%。圖4a圖4bSoCFPGA增強(qiáng)了系統(tǒng)功能,通過(guò)集成降低了系統(tǒng)總成本。通過(guò)在一

2021-07-14 08:00:00

30多年,但是由于 HDL 是一種用形式化的語(yǔ)言描述極其復(fù)雜的數(shù)字系統(tǒng)的,抽象級(jí)別較低,因而大大提高了編程難度,限制了FPGA 的推廣和普及。其次隨著系統(tǒng)級(jí) FPGA 和片上系統(tǒng)(SoC)的出現(xiàn)

2018-08-10 09:16:48

多年,但是由于 HDL 是一種用形式化的語(yǔ)言描述極其復(fù)雜的數(shù)字系統(tǒng)的,抽象級(jí)別較低,因而大大提高了編程難度,限制了FPGA 的推廣和普及。其次隨著系統(tǒng)級(jí) FPGA 和片上系統(tǒng)(SoC)的出現(xiàn)和迅速發(fā)展

2018-08-13 09:31:45

復(fù)雜度日益增加的系統(tǒng)設(shè)計(jì)要求高性能FPGA的設(shè)計(jì)與PCB設(shè)計(jì)并行進(jìn)行。通過(guò)整合FPGA和PCB設(shè)計(jì)工具以及采用高密度互連(HDI)等先進(jìn)的制造工藝,這種設(shè)計(jì)方法可以降低系統(tǒng)成本、優(yōu)化系統(tǒng)性能并縮短

2018-09-21 11:55:09

集成度、高性能、低功耗FPGA器件的需求。設(shè)計(jì)人員更喜歡網(wǎng)絡(luò)通信而不是點(diǎn)對(duì)點(diǎn)通信,這意味著可能需要額外的控制器用于通信,進(jìn)而間接增加了BOM成本、電路板尺寸和相關(guān)NRE(一次性工程費(fèi)用)成本。總體擁有成本

2019-06-24 07:29:33

期中看不到明顯的數(shù)據(jù)變化。這類方法能夠顯著降低功耗,不需要來(lái)自系統(tǒng)其它部分的任何輸入,對(duì)性能也不會(huì)有任何影響。其它方法則需要來(lái)自系統(tǒng)管理硬件或者軟件的大量幫助。一個(gè)例子是動(dòng)態(tài)電壓頻率調(diào)整(DVFS

2014-09-02 14:51:19

變系統(tǒng)邏輯的情況下接地或接電源。(4)對(duì)單片機(jī)使用電源監(jiān)控及看門狗電路,如:IMP809,IMP706,IMP813, X25043,X25045等,可大幅度提高整個(gè)電路的抗干擾性能。(5)在速度能

2015-05-07 14:26:19

應(yīng)用系統(tǒng)使用了更多的功率元件,以及封裝密度的不斷提高,先進(jìn)的冷卻技術(shù)變得更加重要。我們用獨(dú)特的方法把熱界面材料和電路板的屏蔽產(chǎn)品結(jié)合起來(lái),用于制造更加可靠的電子產(chǎn)品,例如PDA、 移動(dòng)電話和便攜式DVD

2018-08-31 11:53:58

夠集成整個(gè)芯片系統(tǒng)(SoC),與分立的MCU、DSP、ASSP以及ASIC解決方案相比,大幅度降低了成本。不論是用作協(xié)處理器還是SoC皆具備不可取代的獨(dú)特優(yōu)勢(shì)。那么,這些器件之間差異性在哪里呢?一位資深

2014-07-24 11:18:05

SoCFPGA器件在一個(gè)器件中同時(shí)集成了處理器和FPGA體系結(jié)構(gòu)。將兩種技術(shù)合并起來(lái)具有很多優(yōu)點(diǎn),包括更高的集成度、更低的功耗、更小的電路板面積,以及處理器和FPGA之間帶寬更大的通信等等。這一同類最佳的器件發(fā)揮了處理器與FPGA系統(tǒng)融合的優(yōu)勢(shì),同時(shí)還保留了獨(dú)立處理器和FPGA方法的優(yōu)點(diǎn)。

2019-09-26 07:59:27

通過(guò)最大化可用的電壓和降低功耗(請(qǐng)參閱下面的溫度計(jì)比較),理想二極管橋簡(jiǎn)化了電源設(shè)計(jì)和降低供電成本,尤其是在低電壓應(yīng)用。一個(gè)理想二極管橋也消除了熱設(shè)計(jì)問(wèn)題,昂貴的散熱片,并大大降低了印刷電路板面積。

2019-10-23 09:10:25

本文以MP3解碼器為例,介紹了一種在嵌入式Linux系統(tǒng)下配置使用處理器片內(nèi)SRAM的應(yīng)用方案,有效提高了代碼的解碼效率,降低了執(zhí)行功耗。該方案不論在性能還是成本上都得到了很大改善。

2020-03-05 07:01:34

本文以MP3解碼器為例,介紹了一種在嵌入式Linux系統(tǒng)下配置使用處理器片內(nèi)SRAM的應(yīng)用方案,有效提高了代碼的解碼效率,降低了執(zhí)行功耗。該方案不論在性能還是成本上都得到了很大改善。

2019-09-24 07:09:13

寬壓供電設(shè)計(jì)。MM32F系列是靈動(dòng)微新一代MM32系列中率先升級(jí)推出的通用高性能MCU平臺(tái)。全新MM32F系列和經(jīng)典MM32F引腳兼容,并在系統(tǒng)性能、功能擴(kuò)展、可靠性、穩(wěn)定性上獲得了大幅度提升,ESD

2021-09-02 08:16:20

。Quartus II軟件v13.1大幅度優(yōu)化了算法,增強(qiáng)了并行算法,提高了您的多處理器計(jì)算機(jī)上多個(gè)內(nèi)核的性能。 圖1顯示了自從2011年以來(lái),高端器件在Quartus II軟件上的基準(zhǔn)測(cè)試結(jié)果。 圖

2013-11-13 15:34:26

This paper discusses how Vivace Networks uses ScanWorks at the benchtop and at in-circuit test to reduce test costs and accelerate time to market in a competitive environment.

2019-08-08 07:07:06

進(jìn)行遠(yuǎn)程監(jiān)測(cè)、遠(yuǎn)程控制、遠(yuǎn)程維護(hù)和管理。內(nèi)嵌于設(shè)備的Web服務(wù)器可以提供統(tǒng)一的基于瀏覽器方式的操作和控制界面,界面直觀易操作,大大降低了軟件系統(tǒng)和通信系統(tǒng)的設(shè)計(jì)、維護(hù)工作量,節(jié)省了人員培訓(xùn)費(fèi)用,提高了現(xiàn)場(chǎng)監(jiān)測(cè)和控制設(shè)備的管理水平。

2019-08-02 08:19:18

從Xilinx公司推出FPGA二十多年來(lái),研發(fā)工作大大提高了FPGA的速度和面積效率,縮小了FPGA與ASIC之間的差距,使FPGA成為實(shí)現(xiàn)數(shù)字電路的優(yōu)選平臺(tái)。今天,功耗日益成為FPGA供應(yīng)商及其

2019-09-20 06:33:32

MPCoreTM處理器,以及豐富的硬件外設(shè),從而降低了系統(tǒng)功耗和成本,減小了電路板面積。基本描述如下: (1)28nm FPGA實(shí)現(xiàn)了業(yè)界最低系統(tǒng)成本和功耗 (2)三種型號(hào):僅邏輯、3G收發(fā)器和5G收發(fā)器

2012-09-21 13:49:05

的功耗。對(duì)于第二種挑戰(zhàn),通常通過(guò)降低產(chǎn)品原材料 (BOM)中元器件的成本來(lái)降低現(xiàn)有成功產(chǎn)品的成本。設(shè)計(jì)團(tuán)隊(duì)的另一選擇是重新設(shè)計(jì)產(chǎn)品,不是針對(duì)新功能,而是要大幅度的降低成本。

2019-08-09 07:41:27

TriQuint是一個(gè)高性能射頻解決方案的領(lǐng)導(dǎo)者,其產(chǎn)品涉及復(fù)雜移動(dòng)設(shè)備、國(guó)防與航天應(yīng)用以及網(wǎng)絡(luò)基礎(chǔ)設(shè)施等方面。現(xiàn)在,TriQuint通過(guò)使用GaAs、GaN、SAW和BAW技術(shù)為世界各地的組織提供創(chuàng)新的解決方案。工程師和科學(xué)家借助TriQuint的創(chuàng)新提高了產(chǎn)品的性能,并降低了其應(yīng)用的總成本。

2019-08-16 08:14:37

本文介紹雙通道數(shù)字式磁隔離器ADUM1201在CAN總線通信系統(tǒng)中的應(yīng)用,由于ADUM1201的優(yōu)良特性,用ADUM1201代替?zhèn)鹘y(tǒng)的光電隔離器件,降低了系統(tǒng)功耗,簡(jiǎn)化系統(tǒng)結(jié)構(gòu),增加了系統(tǒng)穩(wěn)定性,提高了系統(tǒng)的性能。

2021-05-31 06:52:41

反對(duì)法多福多壽發(fā)的發(fā)大幅度反對(duì)法大幅度

2013-09-13 23:18:54

μs減小到5μs。這意味著顯著提高了功效,對(duì)應(yīng)驅(qū)動(dòng)90%的總體運(yùn)行成本。在這個(gè)例子中,SoC的功耗大約比三芯片方案低37%。圖4a圖4bSoCFPGA增強(qiáng)了系統(tǒng)功能,通過(guò)集成降低了系統(tǒng)總成本。通過(guò)在一

2021-07-12 08:00:00

CPU內(nèi)核。如何大幅度減少實(shí)施時(shí)間?我有什么選擇可以改變以加快它嗎?以上來(lái)自于谷歌翻譯以下為原文The implementation process is a time-consuming

2018-10-17 11:59:47

本文基于Viitex-5 LX110驗(yàn)證平臺(tái)的設(shè)計(jì),探索了高性能FPGA硬件系統(tǒng)設(shè)計(jì)的一般性方法及流程,以提高FPGA的系統(tǒng)性能。

2021-04-26 06:43:55

FPGA的功耗高度依賴于用戶的設(shè)計(jì),沒(méi)有哪種單一的方法能夠?qū)崿F(xiàn)這種功耗的降低,如同其它多數(shù)事物一樣,降低功耗的設(shè)計(jì)就是一種協(xié)調(diào)和平衡藝術(shù),在進(jìn)行低功耗器件的設(shè)計(jì)時(shí),人們必須仔細(xì)權(quán)衡性能、易用性、成本、密度以及功率等諸多指標(biāo)。

2019-08-15 08:28:42

的TCO 直接提高了毛利潤(rùn),從而減緩了當(dāng)今大部分設(shè)計(jì)團(tuán)隊(duì)所面臨的壓力。圖1. 有利于降低TCO 的一些構(gòu)建模塊FPGA 降低了TCO為闡述Altera Cyclone 系列FPGA 是怎樣降低TCO

2013-11-13 11:17:35

復(fù)雜器件專業(yè)技術(shù)相結(jié)合,將為系統(tǒng)供應(yīng)商提供低功耗的芯片方案,供他們?cè)诖嘶A(chǔ)上持續(xù)提高帶寬容量,并完成更智能的處理。此外,TPACK提供的芯片解決方案可以導(dǎo)入到最新的FPGA中,進(jìn)一步降低功耗。最終實(shí)現(xiàn)

2019-07-31 07:13:26

有什么方法可以提高片上系統(tǒng)級(jí)集成嗎?有什么方法可以降低物料成本嗎?

2021-05-14 06:20:23

對(duì)于各種不同的數(shù)據(jù)中心工作負(fù)載,FPGA 可以顯著提高性能,最大程度減少附加功耗并降低總體擁有成本 (TCO)。

2019-10-10 07:46:05

能保持靜止,然后過(guò)一會(huì)兒突然一下就大幅度的來(lái)回走動(dòng),然后重新啟動(dòng)后就直接大幅度來(lái)回走動(dòng)了。設(shè)定的movement=0;if(Turn_Off(Angle_Balance,Voltage)==1

2019-05-19 21:36:39

自己做了一個(gè)電路板,因?yàn)?b class="flag-6" style="color: red">功耗除了點(diǎn)問(wèn)題,怎么降低電路板功耗呢

2019-08-07 22:21:34

從當(dāng)前嵌入式消費(fèi)電子產(chǎn)品來(lái)看,媒體處理與無(wú)線通信、3D游戲逐漸融合,其強(qiáng)大的功能帶來(lái)了芯片處理能力的增加,在復(fù)雜的移動(dòng)應(yīng)用環(huán)境中,功耗正在大幅度增加。比如手機(jī),用戶往往希望待機(jī)時(shí)間、聽音樂(lè)時(shí)間,以及看MPEG4時(shí)間能更長(zhǎng)。在這樣的背景下,如何降低入式芯片的功耗已迫在眉睫。

2019-08-28 08:27:58

從當(dāng)前嵌入式消費(fèi)電子產(chǎn)品來(lái)看,媒體處理與無(wú)線通信、3D游戲逐漸融合,其強(qiáng)大的功能帶來(lái)了芯片處理能力的增加,在復(fù)雜的移動(dòng)應(yīng)用環(huán)境中,功耗正在大幅度增加。比如手機(jī),用戶往往希望待機(jī)時(shí)間、聽音樂(lè)時(shí)間,以及看MPEG4時(shí)間能更長(zhǎng)。在這樣的背景下,如何降低嵌入式芯片的功耗已迫在眉睫。

2019-09-18 06:22:27

本文運(yùn)用目前基于FPGA(Field Programmable Gate Array)的SoPC (System on Programmable Chip)技術(shù)構(gòu)建軟件無(wú)線電平臺(tái)。大大提高了數(shù)字信號(hào)處理的能力和速度,并且降低了系統(tǒng)功耗,縮小了系統(tǒng)體積,為更高層次的3G無(wú)線通信要求提供了解決方案。

2021-05-06 06:21:24

據(jù)的擦除、修改,只需更改代碼,無(wú)需改變電路結(jié)構(gòu),降低了系統(tǒng)成本,同時(shí)簡(jiǎn)化了系統(tǒng)的復(fù)雜性,提高了系統(tǒng)工作的穩(wěn)定性。

2021-05-20 07:00:52

蒸汽輪機(jī)或水輪機(jī)的發(fā)電原理是什么?有什么方法可以大幅度提升發(fā)電機(jī)的發(fā)電量呢?

2021-06-30 06:49:48

性以及高可靠性,它是一個(gè)被廣泛使用的針對(duì)于FPGA上的單粒子翻轉(zhuǎn)(Single-EventUpset,SEU)的容錯(cuò)技術(shù)。文獻(xiàn)中表明TMR大幅度提高了FP-GA在SEU影響下的可靠性。盡管TMR能有效提高

2019-08-27 07:28:32

本文以MP3解碼器為例,介紹了一種在嵌入式Linux系統(tǒng)下配置使用處理器片內(nèi)SRAM的應(yīng)用方案,有效提高了代碼的解碼效率,降低了執(zhí)行功耗。該方案不論在性能還是成本上都得到了很大改善。

2021-04-26 07:01:55

nm SoC封裝到一個(gè)20 nm管芯中,結(jié)果是減小了芯片間延時(shí),降低了I/O功耗,以及電路板級(jí)成本,這說(shuō)明單位晶體管成本的提高是有好處的。而不明顯的是,規(guī)劃人員通過(guò)使用晶體管來(lái)提高性能或者能效。一個(gè)

2014-09-01 17:26:49

發(fā)發(fā)大幅度發(fā)大廈

2015-11-28 11:22:20

,會(huì)使系統(tǒng)的穩(wěn)定性大幅度提高。一般應(yīng)在電源進(jìn)入印刷電路板的位置和靠近各器件的電源引腳處加上幾十到幾百IlF的電容,以濾除電源噪聲。還要注意在器件的電源和地之間加上0.1μF左右的電容,用來(lái)濾除元器件工作

2018-09-05 16:38:26

Altera20nmArria10FPGA和SoC中,以及14nmStratix10FPGA和SoC中。該新功能支持設(shè)計(jì)人員以相同的定點(diǎn)性能和效率在浮點(diǎn)中實(shí)現(xiàn)其算法,且不會(huì)對(duì)功耗、面積或者密度產(chǎn)生任何影響,也不會(huì)損失定點(diǎn)特性或

2019-07-03 07:56:05

被動(dòng)門禁 (Passive Entry, PE)系統(tǒng)在汽車舒適度和安全性方面正在引領(lǐng)一個(gè)新的發(fā)展趨勢(shì)。盡管這種技術(shù)幾年前就已經(jīng)問(wèn)世了,但直到最近才開始快速流行,主要是因?yàn)?b class="flag-6" style="color: red">系統(tǒng)集成度不斷提高,使系統(tǒng)成本得以大幅度降低。

2019-08-23 06:03:43

。面向 Arria 10 等高端 FPGA 的電源管理解決方案應(yīng)該謹(jǐn)慎選擇。 一個(gè)經(jīng)過(guò)精心計(jì)劃的電源管理設(shè)計(jì)可以減小 PCB 尺寸、減輕重量并降低復(fù)雜性,同時(shí)降低功耗和冷卻成本。這對(duì)優(yōu)化系統(tǒng)性能而言

2018-10-15 10:30:31

端 FPGA 的電源管理解決方案應(yīng)該謹(jǐn)慎選擇。 一個(gè)經(jīng)過(guò)精心計(jì)劃的電源管理設(shè)計(jì)可以減小 PCB 尺寸、減輕重量并降低復(fù)雜性,同時(shí)降低功耗和冷卻成本。這對(duì)優(yōu)化系統(tǒng)性能而言是必不可少的。 例如,為圖

2018-11-20 10:46:52

,大幅度降低了成本。不論是用作協(xié)處理器還是SoC,Altera FPGA在您的工業(yè)應(yīng)用中都具有以下優(yōu)點(diǎn): 1. 設(shè)計(jì)集成——使用FPGA作為協(xié)處理器或者SoC,在一個(gè)器件平臺(tái)上集成 IP和軟件堆棧

2014-11-05 14:03:37

是,硬核IP模塊功耗降低了65%,而性能提高了50%,表1列出了Cyclone V FPGA中的硬核IP功能,以及通過(guò)硬核實(shí)現(xiàn)所節(jié)省的資源量。表1 Cyclone V FPGA中的硬核IP功能 硬核IP

2015-02-09 15:02:06

工業(yè)電子產(chǎn)品的發(fā)展趨勢(shì)是更小的電路板尺寸、更時(shí)尚的外形和更具成本效益。由于這些趨勢(shì),電子系統(tǒng)設(shè)計(jì)人員必須降低印刷電路板(PCB)的尺寸和成本。使用現(xiàn)場(chǎng)可編程門陣列(FPGA)和片上系統(tǒng)(SoC

2019-03-08 06:45:06

在高速電路中推薦使用多層電路板。首先,多層電路板分配內(nèi)層專門給電源和地,因此 具有如下優(yōu)點(diǎn): · 電源非常穩(wěn)定; · 電路阻抗大幅降低; · 配線長(zhǎng)度大幅縮短。 此外,從成本角度考慮

2018-11-23 16:04:04

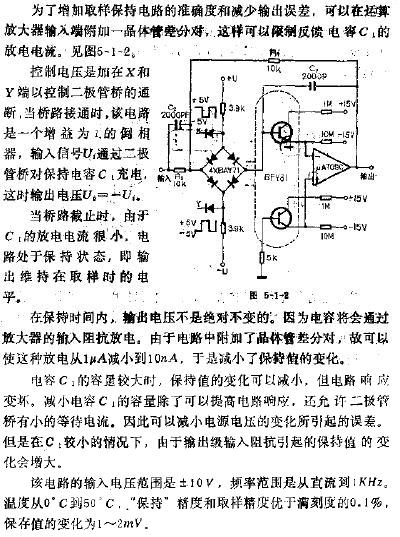

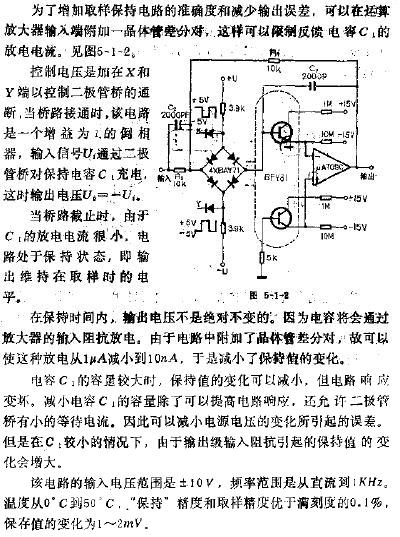

提高了準(zhǔn)確度的取樣保持電路

2009-04-11 10:51:58 668

668

光纖接入組網(wǎng)方案讓網(wǎng)速大幅度提高

隨著網(wǎng)吧行業(yè)的發(fā)展,競(jìng)爭(zhēng)也越來(lái)越激烈,要在激烈的競(jìng)爭(zhēng)中立于不敗之地,設(shè)計(jì)和組建一個(gè)穩(wěn)

2010-04-14 13:51:56 1886

1886 MAX6581 精度、8通道溫度傳感器,有效降低電路板面積

2010-09-17 13:23:04 973

973 自從Xilinx推出FPGA二十多年來(lái),研發(fā)工作大大提高了FPGA的速度和面積效率,縮小了FPGA與ASIC之間的差距,使FPGA成為實(shí)現(xiàn)數(shù)字電路的優(yōu)選平臺(tái)。今天,功耗日益成為FPGA供應(yīng)商及其客戶關(guān)注的問(wèn)題。降低FPGA功耗是縮減封裝和散熱成本、提高器件可靠性以及打開移

2011-03-15 14:58:34 31

31 2012年4月11號(hào),北京——Altera公司(Nasdaq: ALTR)今天宣布,goHDR作為FPGA OpenCL計(jì)劃的早期試用客戶,通過(guò)Altera的FPGA OpenCL計(jì)劃,大幅度縮短了開發(fā)時(shí)間,顯著提高了性能。與Altera密切

2012-04-12 08:58:10 705

705 Cadence公司宣布Renesas微系統(tǒng)有限公司已采用Cadence Encounter RTL Compiler用于綜合實(shí)現(xiàn)。其優(yōu)勢(shì)在于將復(fù)雜ASIC設(shè)計(jì)的芯片利用率提高了15%,面積減少了8.4%,加速了實(shí)現(xiàn)周期并降低了成本。

2012-12-14 10:59:15 1008

1008 接通功能,集成了閃存,適用于遠(yuǎn)程更新和系統(tǒng)管理功能。

模數(shù)轉(zhuǎn)換器(ADC),降低了系統(tǒng)成本,減小了電路板面積。

小外形封裝,集成器件,減小了引腳布局。

可定制處理器外設(shè)組,提高了功效。

2016-01-06 10:22:08 39

39 楔式制動(dòng)器設(shè)計(jì)提高了線控剎車的性能

2017-01-24 15:44:12 12

12 那么這項(xiàng)很嚇人的技術(shù)到底是什么,現(xiàn)在似乎也有了些眉目。根據(jù)內(nèi)部人士的爆料,這項(xiàng)“很嚇人的技術(shù)”就是借助黑科技使得圖形圖像的性能,以及玩游戲的性能得到極大幅度的提升,據(jù)說(shuō)速度快到不可思議。當(dāng)然,這里所說(shuō)的黑科技借助對(duì)系統(tǒng)底層的優(yōu)化,輔以芯片上的支持,從而逆轉(zhuǎn)過(guò)去麒麟處理器在GPU性能方面的不足。

2018-05-28 12:32:00 4503

4503 如何讓汽車上的LED適應(yīng)越來(lái)越嚴(yán)苛的環(huán)境?近日全球知名半導(dǎo)體制造商ROHM發(fā)布了業(yè)界首款完全無(wú)銀的高亮度紅色LED“SML-Y18U2T”,大幅度的提高了汽車燈具尤其是剎車燈在嚴(yán)酷環(huán)境下使用的可靠性

2018-05-30 11:35:00 2119

2119 Vivado HLS有助于降低整體系統(tǒng)功耗,降低材料成本,提高系統(tǒng)性能并加快設(shè)計(jì)生產(chǎn)率。

我們將向您展示如何使用C,C ++或SystemC創(chuàng)建更高效??的規(guī)范。

2018-11-27 06:43:00 3392

3392 特斯拉大幅度降價(jià) 為何

2019-03-04 14:48:02 687

687 Altera公司今天宣布,NEC將使用Altera的 28nm FPGA,進(jìn)一步提高了其長(zhǎng)期發(fā)展(LTE)基站的性能,支持無(wú)線服務(wù)供應(yīng)商高效的管理他們的網(wǎng)絡(luò)。

2019-05-14 15:34:45 774

774 對(duì)于電動(dòng)汽車而言,電池占據(jù)了車輛30%到40%左右的用車成本,如果電池成本大幅度下降,電動(dòng)車會(huì)逆襲燃油車嗎?

2019-12-26 10:07:58 780

780 2月28日,美國(guó)泛林公司宣布與ASML阿斯麥、IMEC比利時(shí)微電子中心合作開發(fā)了新的EUV光刻技術(shù),不僅提高了EUV光刻的良率、分辨率及產(chǎn)能,還將光刻膠的用量最多降至原來(lái)的1/10,大幅降低了成本。

2020-02-29 11:20:58 3228

3228 的筆記本電腦和臺(tái)式機(jī)提供最高的BOM集成度,在縮小電路板面積的同時(shí),還能降低OEM廠商的成本。此外,新的EZ-PD控制器還支持最新的USB4?標(biāo)準(zhǔn)和Intel Thunderbolt?平臺(tái)。

2020-03-04 14:16:15 2594

2594 在PCB電路的開發(fā)階段,通常要經(jīng)歷幾次電路設(shè)計(jì)送代,包括測(cè)試、再設(shè)計(jì)、重新加工電路等。這些多次的更改可能導(dǎo)致成本上升項(xiàng)日從開始開發(fā)到推出市場(chǎng)經(jīng)歷4次到8次的更改并不少見。比較慣用的方式是使用電路仿真軟件做好精確的仿真從而可以大幅度減少變更次數(shù)和相關(guān)成本。

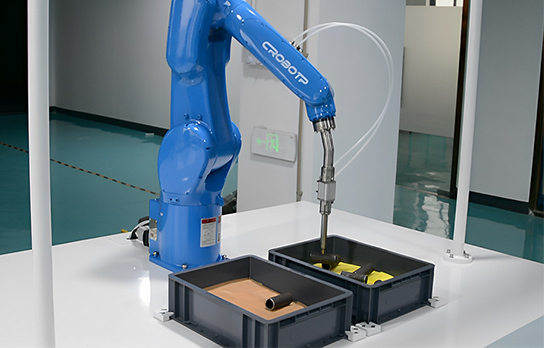

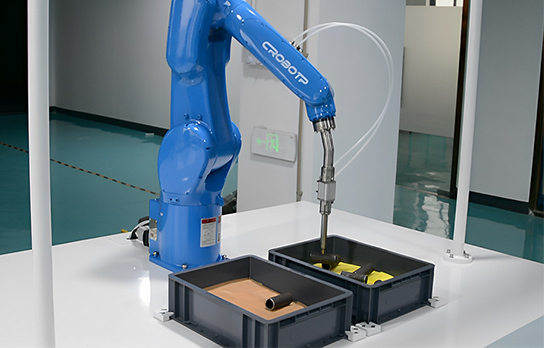

2020-07-17 10:25:00 3

3 視覺(jué)系統(tǒng)和機(jī)器人移動(dòng)機(jī)構(gòu),實(shí)現(xiàn)了抓取不同尺寸、形狀和重量的零件,并且可以在保證生產(chǎn)節(jié)拍的同時(shí)實(shí)現(xiàn)無(wú)損拾取,大大提高了生產(chǎn)企業(yè)的效率,降低了成本。 danikor的研發(fā)團(tuán)隊(duì)在材料的選型和制備上進(jìn)行了系統(tǒng)化的探索,通過(guò)對(duì)各種高分子材料的配比

2020-12-11 08:46:04 810

810 高線性度下變頻混頻器使 3G 和 4G 無(wú)線基站的性能提高并降低了功耗

2021-03-21 10:18:10 3

3 高精度(±1°C)溫度傳感器提高了系統(tǒng)性能和可靠性

2021-05-27 09:56:09 2

2 集電容式觸控和主機(jī)控制器功能,節(jié)約時(shí)間、成本以及電路板空間

2022-11-01 08:25:27 0

0 帶抽頭電感的離線降壓轉(zhuǎn)換器提高了性能

2022-11-14 21:08:21 1

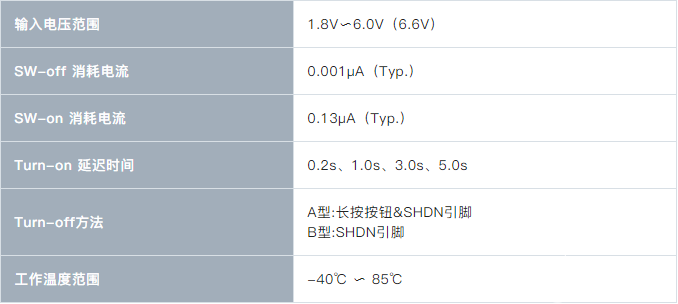

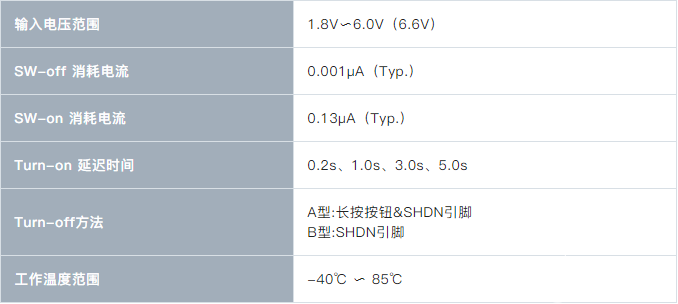

1 XC6193/XC6194系列產(chǎn)品是能大幅度降低出廠后待機(jī)時(shí)及電源OFF時(shí)消耗的電力、并且在系統(tǒng)死機(jī)時(shí)能關(guān)閉電源的智能負(fù)載開關(guān)。有利于機(jī)器節(jié)電、延長(zhǎng)工作時(shí)間。

2022-11-19 19:04:21 315

315

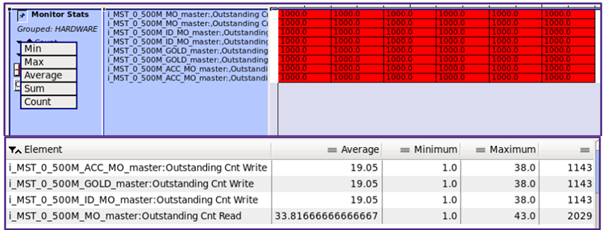

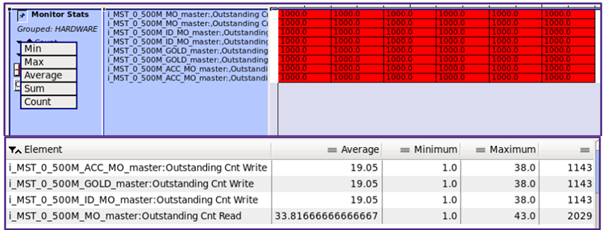

在使用 AXI 總線移動(dòng)大量數(shù)據(jù)的 SoC 中,AXI 總線的性能可能會(huì)成為整體系統(tǒng)性能的瓶頸。SoC 中日益增加的復(fù)雜性和軟件內(nèi)容,因此需要使用實(shí)際數(shù)據(jù)有效載荷在硅前進(jìn)行左移性能驗(yàn)證。硬件輔助驗(yàn)證

2023-05-25 15:37:52 544

544

3D視覺(jué)引導(dǎo)金屬圓管無(wú)序抓取,不僅提高了生產(chǎn)效率,降低了成本,還大幅度提升了作業(yè)的精確性和安全性。

2023-07-11 15:54:44 206

206

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論