,也被專注于特定應用但全定制化、成本低的ASIC壓得有些抬不起頭來。FPGA廠商們也沒法維系那么多的應用,去和不斷涌現的ASIC初創公司在各個領域去一一硬碰硬。 與此同時,FPGA大廠在被收購后,也開始順應他們的技術路線,可以看到他們的產品方向開始往數據中

2022-08-22 08:22:00 3543

3543 1.引言

本文針對紅外圖像處理系統的實時性要求,提出了基于DSP+FPGA+ASIC的圖像處理架構。

隨著紅外焦

2010-07-22 15:18:50 796

796 ASIC和FPGA具有不同的價值主張,在作出選擇前必須仔細評估。兩種種技術對比。這里介紹了ASIC和FPGA 的優勢與劣勢。

2011-03-31 17:30:09 5382

5382

不久前,據國外媒體報道,華為公司正在首次使用ASIC來替代其設備中的FPGA芯片,而這些芯片原本采購于FPGA主要廠商之一的Altera【 電子發燒友網關于此事報道:華為ASIC設計案,FPGA雙雄

2012-11-14 08:47:56 1970

1970 DS18B20數字溫度傳感器接線方便,封裝成后可應用于多種場合,如管道式,螺紋式,磁鐵吸附式,不銹鋼封裝式,型號多種多樣,有LTM8877,LTM8874等等。主要根據應用場合的不同而改變其外

2013-07-26 13:54:39

的區別是什么?以及高端FPGA應該歸類為SoC嗎? 這里有幾個難題,至少技術和術語隨著時間而演變。牢記這一點,對于這些術語的起源以及它們現在的意義是什么,我對此做了高度簡化的解釋。ASIC——特定

2014-07-24 11:18:05

1、概念區別: ASIC(專用集成電路)是一種在設計時就考慮了設計用途的IC。 FPGA(現場可編程門陣列)也是一種IC。顧名思義,只要有合適的工具和適當的專業基礎,工程師就可以對FPGA

2020-12-01 17:41:49

ASIC技術過時的報道是不成熟的。新的ASIC產品的數目可能有大幅度下降,但其銷售額仍然相當高,尤其是在亞太區。此外,采用混合式方法,如結構化ASIC,也為該技術注入了新的活力。同時,FPGA(和其他可編程邏輯器件)也在發揮作用,贏得了重要的大眾市場,并從低端應用不斷向上發展。

2019-07-19 06:24:30

硬件DSP:是ASIC,如同CPU/GPU一樣,適合量產,降低成本,缺點是(硬件)設計一旦確定,便不易于修改。FPGA :通過HDL 快速設計,但成本較高,用于ASIC的prototype設計。與DSP比較軟件-編程語言DSP:DSP寫...

2021-07-28 09:06:55

和配置實現自己想要的功能。實現 ASIC,就如從一張白紙開始,你得有代碼,之后綜合,之后布局,布線,得到 GDSII 后去流片。五、比速度相同的工藝和設計,在 FPGA 上的速度應該比 ASIC

2020-09-25 11:34:41

本帖最后由 24不可說 于 2017-9-10 15:07 編輯

FPGA要取代ASIC了,這是FPGA廠商喊了十多年的口號。可是,FPGA地盤占了不少,ASIC也依舊玩得愉快。這兩位仁兄

2017-09-02 22:24:53

,稱為半定制專用集成電路,相對來說更接近FPGA,甚至在某些地方,ASIC就是個大概 念,FPGA屬于ASIC之下的一部分。FPGA基本就是高端的CPLD,兩者非常接近。我現在用的是ALTERA...

2021-11-24 07:09:18

都能做;而FPGA可以做的,ARM不一定行,DSP也不一定行。這就是很多原型產品設計過程中,時不時的有人會提出給于FPGA的方案了。在一些靈活性要求高、定制化程度高、性能要求也特別高的場合,FPGA再

2021-11-02 06:30:00

ASIC是專用集成電路設計,FPGA是可編程邏輯陣列,DSP和單片機(MCU?)是不是有點像?這四個我只接觸過FPGA,就是自己布置邏輯單元,可以使用IP核,最后下到開發板驗證。現在我想問:如果我要實現一個電子系統,這四個方案有什么區別?鑒于天朝的本科其實沒講什么東西,所以到現在沒搞清。。。

2015-09-21 11:34:58

),一旦設計制造完成后電路就固定了,無法再改變。 用于深度學習加速器的FPGA(Xilinx Kintex 7 Ultrascle,左)和ASIC(Movidius Myriad 2,右)比較

2016-12-15 19:21:50

FPGA是一種可編程的硅芯片,DSP是數字信號處理,當系統設計人員在項目的架構設計階段就面臨到底采用FPGA還是DSP的重要問題。本文將首先分別介紹FPGA和DSP的特點,然后再從內部資源、編程語言

2019-05-07 01:28:40

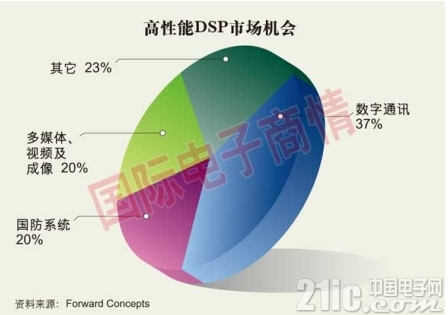

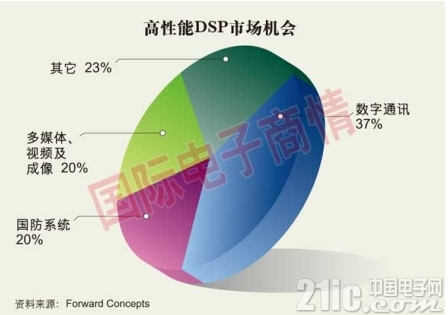

,新一代基站設施成為二者競爭的焦點,同時Femtocell的發展潛力也吸引了FPGA和DSP廠商。 飛思卡爾是第一個向市場推出商用四核心DSP的廠商。飛思卡爾現在在市場上主推的產品是第二代四核DSP

2019-07-19 06:10:44

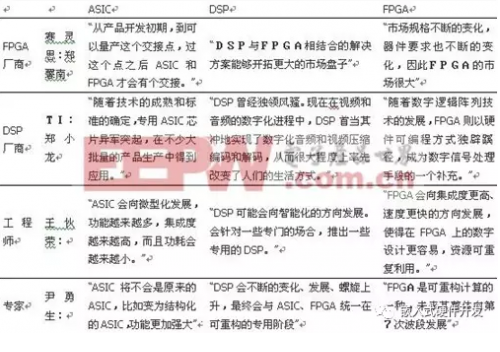

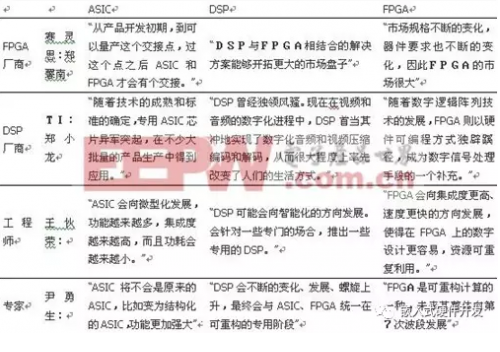

Altera和Xilinx主導的PLD廠商在各領域攻城拔寨勢如破竹,喜訊頻傳。“FPGA將取代DSP”之聲日盛。這無疑撩動著傳統DSP大廠的敏感神經,德州儀器(TI)、CEVA、飛思卡爾

2014-01-09 17:52:31

可以像軟件一樣通過編程來修改。作為專用集成電路(ASIC)領域中的一種半定制電路,FPGA既解決了 定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。可以毫不夸張的講,FPGA能完成任何數字器件

2014-06-26 14:23:43

,以實現用戶的邏輯。它還具有靜態可 重復編程和動態在系統重構的特性,使得硬件的功能可以像軟件一樣通過編程來修改。作為專用集成電路(ASIC)領域中的一種半定制電路,FPGA既解決了 定制電路的不足,又

2013-05-06 15:56:02

都可以用FPGA的邏輯門搭出來的。MCU編程和應用相對簡單,不過只能用于地端產品,高端的話只能用ARM了。不過成本相對較低。DSP其實就是一種高端的MCU,它是在單片機的基礎上增加了很多個硬件乘加器

2018-08-30 09:13:25

。與其形成對照的是,FPGA曾經在微細化方面雖曾落后于ASIC,但在2005年轉向90nm工藝后趕超了ASIC,其后一直在拉大雙方的差距。2008年FPGA轉向40nm工藝時,已比ASIC領先3個節點

2012-11-20 20:09:57

工藝。與其形成對照的是,FPGA曾經在微細化方面雖曾落后于ASIC,但在2005年轉向90nm工藝后趕超了ASIC,其后一直在拉大雙方的差距。2008年FPGA轉向40nm工藝時,已比ASIC領先3個

2012-11-07 20:25:53

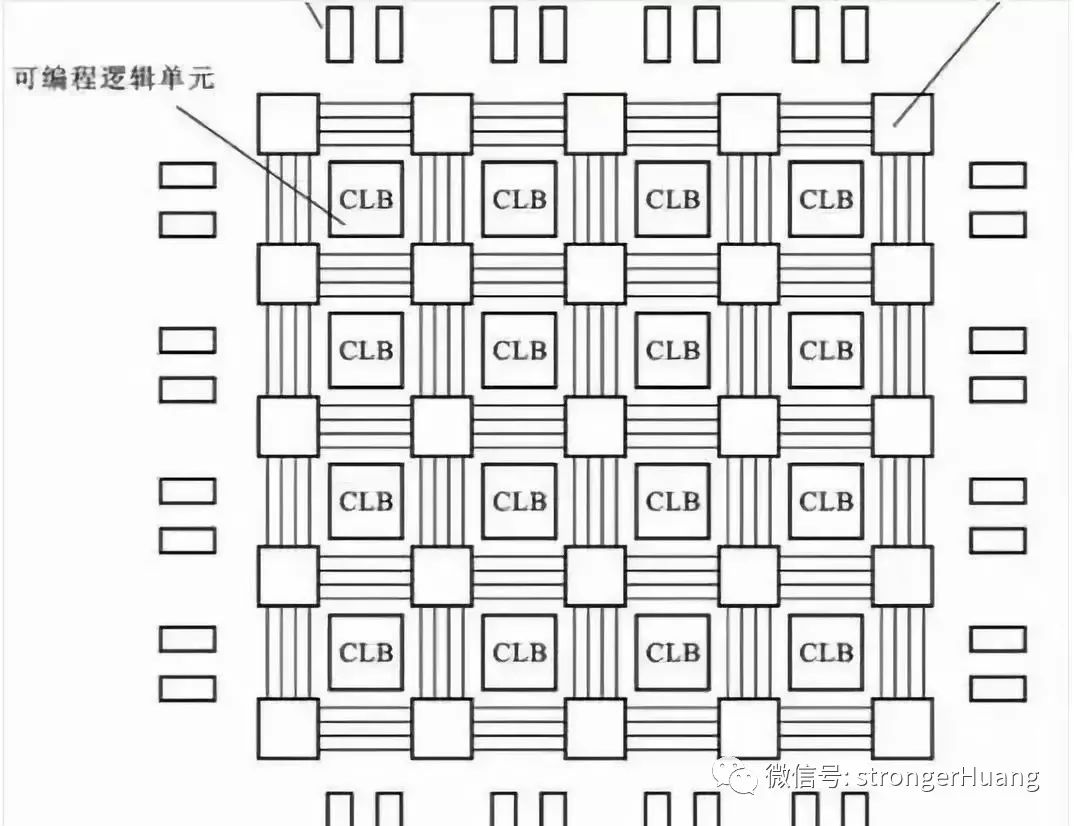

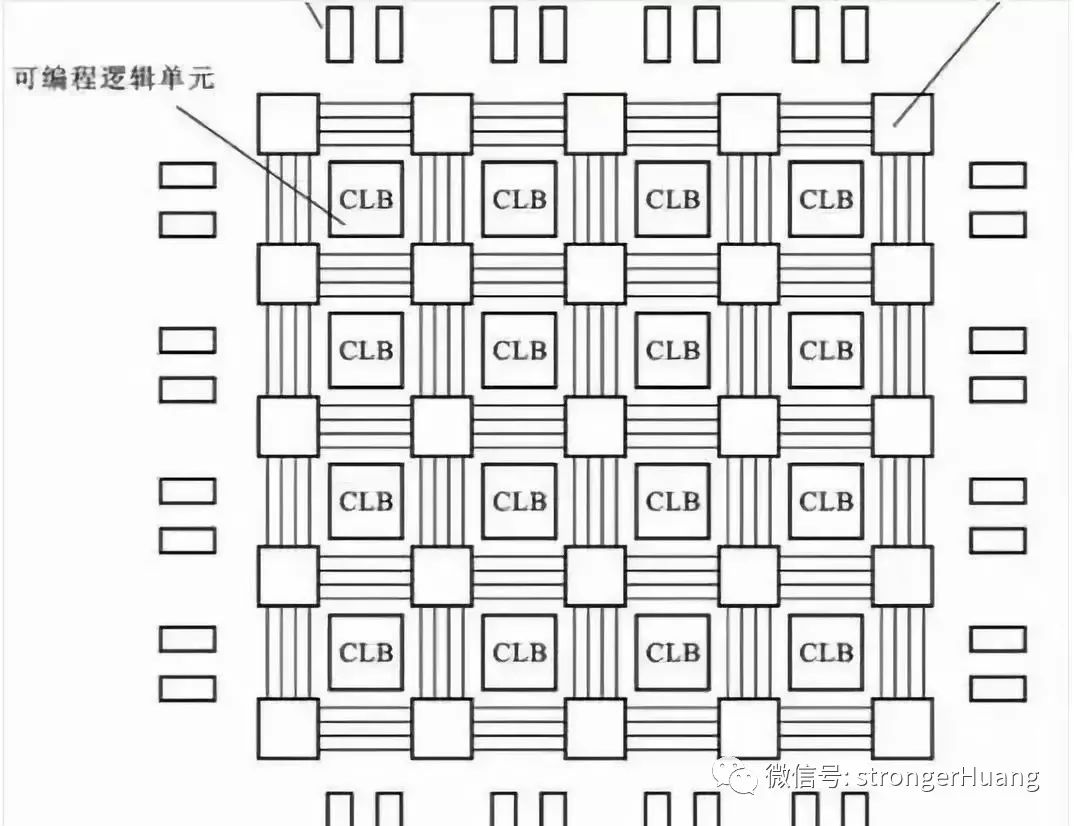

ASIC領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。設計師可以根據需要通過可編輯的連接把FPGA內部的邏輯塊連接起來,就好像一個電路試驗板被放在了

2017-06-12 15:56:59

可以自由發揮的白紙一張。(特權同學版權所有)圖1.2 ASIC和FPGA就如同印刷品和白紙使用了FPGA器件的電子產品,在產品發布后仍然可以對產品設計作出修改,大大方便了產品的更新以及針對新的協議

2015-03-10 11:34:28

的并行架構,使其在某些特殊應用場合如魚得水。而FPGA目前雖然還受制于較高的學習門檻以及器件本身昂貴的價格,應用的普及率上來看和ARM、DSP還是有一定的差距,但是在非常多的應用場合,工程師們還是要

2015-03-24 11:09:11

也有很多的優點比如可以快速成品,可以被修改來改正程序中的錯誤和更便宜的造價。廠商也可能會提供便宜的但是編輯能力差的FPGA。因為這些芯片有比較差的可編輯能力,所以這些設計的開發是在普通的FPGA上完成的,然后將設計轉移到一個類似于ASIC的芯片上。

2013-07-31 17:37:32

FPGA的方案選擇 幸運的是,需要高性能DSP功能的便攜式設備設計者還有其它選擇。最近FPGA開始達到了應用所要求的成本競爭力。優選的FPGA方案可用來處理計算量繁重的高端DSP算法,同時還可

2011-02-17 11:21:37

目錄文章目錄目錄FPGAFPGA 的應用場景FPGA 的技術難點FPGA 的工作原理FPGA 的體系結構FPGA 的開發FPGA 的使用FPGA 的優缺點參考文檔FPGAFPGA(Field

2021-07-28 08:43:58

有限的場合2.FPGA相比其他MCU,他的競爭力在于并行處理和可定制性,這也是為什么FPGA的主要應用場合在通信和驗證領域,SOC功能對于FPGA來說能提升開發速度,降低在算法實現上的復雜度,填補一定的市場

2015-01-06 17:22:57

用戶的邏輯。它還具有靜態可重復編程和動態在系統重構的特性,使得硬件的功能可以像軟件一樣通過編程來修改。作為專用集成電路(ASIC)領域中的一種半定制電路,FPGA既解決了定制電路的不足,又克服了原有

2021-09-08 17:49:20

修改。作為專用集成電路(ASIC)領域中的一種 半定制電路,FPGA既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。可以毫不夸張的講,FPGA能完成任何數字器件的功能,上至高 性能

2013-03-14 16:12:07

用戶的邏輯。它還具有靜態可重復編程和動態在系統重構的特性,使得硬件的功能可以像軟件一樣通過編程來修改。作為專用集成電路(ASIC)領域中的一種半定制電路,FPGA既解決了定制電路的不足,又克服了原有可編程

2018-11-19 11:07:49

軟件一樣通過編程來修改。作為專用集成電路(ASIC)領域中的一種 半定制電路,FPGA既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。可以毫不夸張的講,FPGA能完成任何數字器件

2017-11-16 10:57:02

(ASIC)領域中的一種半定制電路,FPGA既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。可以毫不夸張的講,FPGA能完成任何數字器件的功能,上至高性能CPU,下至簡單的74電路

2019-04-01 06:20:23

(Field-ProgrammableGateArray),即現場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有

2017-04-13 08:55:14

反復編程使用。DSP、FPGA芯片雖成本略微高于ASIC芯片,但具有貨源暢通、可多次編程使用等優點。在中小批量通信產品的設計生產中,用FPGA和DSP實現HDLC功能是一種值得采用的方法。HDLC的幀

2011-03-17 10:23:56

中,尤其是支持物聯網的核心技術——通信基站。Xilinx是全球最大的FPGA廠商,其產品在通信市場占據近50%的市場份額,是無線市場半導體器件和有線市場里的霸主。收購Auviz Systems后

2016-09-08 13:54:13

arm,asic,dsp,fpga,mcu,soc各自的特點人工智能受到越來越多的關注,許多公司正在積極開發能實現移動端人工智能的硬件,尤其是能夠結合未來的物聯網應用,對于移動端人工智能硬件的實現

2021-11-11 07:35:31

、GAL、EPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。 FPGA采用

2012-02-27 17:46:03

申請理由:(1)TMS320C6748是高性能DSP內核,用來做信號處理目測會很棒,開發板又載了這么多資源,一句話好東西!(2)我導師就是教數字信號處理的,哈。前面走的matlab+vc的圖像處理

2015-11-06 09:53:02

FPGA是一種可編程的,DSP是,當系統設計人員在項目的架構設計階段就面臨到底采用FPGA還是DSP的重要問題。本文將首先分別介紹FPGA和DSP的特點,然后再從內部資源、編程語言、功能多個角度解析

2023-06-01 11:03:14

這一挑戰。盡管eFPGA在2016年特斯拉開發全自動駕駛芯片時還不是主流技術,但現在已經成為主流技術了。Achronix eFPGA IP現在已在多個大批量應用中投入生產,證明Achronix擁有可實現

2020-09-10 11:02:38

傳統型FPGA基本具備高性能、傳輸速度快的特點,因此這些產品都具有DSP(數字信號處理)和高速傳輸I/O接口,那為什么說FPGA正部分取代ASIC在便攜消費市場的地位呢?

2019-08-05 06:39:43

`FPGA是一種可編程的硅芯片,DSP是數字信號處理,當系統設計人員在項目的架構設計階段就面臨到底采用FPGA還是DSP的重要問題。本文將首先分別介紹FPGA和DSP的特點,然后再從內部資源、編程

2016-12-23 16:56:04

代碼就可以用 FPGA 廠商提供的工具實現硬件加速器了,而要設計 ASIC 則還需要做很多驗證和物理設計 (ESD,Package 等等),需要更多的時間。如果要針對特殊場合(如軍事和工業等對于可靠性

2016-12-23 16:52:40

攝像頭賣才賣 30塊,買一片ARM多少錢?后來ASIC發展了一些,稱為半定制專用集成電路,相對來說更接近FPGA,甚至在某些地方,ASIC就是個大概 念,FPGA屬于ASIC之下的一部分。什么是FPGA

2021-07-16 08:13:27

延長后續車型的生產,這也是為何少有汽車廠商選擇該技術路線的原因。而將eFPGA IP集成在ASIC中,就為這些廠商提供了FPGA的嵌入式硬件編程能力,又不會像獨立FPGA那樣加大成本和功率。小結

2021-11-29 10:07:05

)。在以算力為主要矛盾的FPGA設計中,(典型例子是神經網絡),FPGA中的DSP和BRAM IP的高效率決定了該設計的最終性能。 讓我們來看看目前應用廣泛的Xilinx 7系列的dsp

2023-03-28 11:14:04

本身昂貴的價格,應用的普及率上來看和ARM、DSP還是有一定的差距,但是在非常多的應用場合,工程師們還是要別無選擇的使用它。FPGA所固有的靈活性和并行性是其他芯片所不具備的,所以它的應用領域涵蓋

2016-07-11 06:47:38

增加了S/G傳輸模式,它卸載了處理器對寄存器的讀寫,通過獨立的S/G讀寫通道對存儲著命令描述符的內存進行訪問讀取、處理描述符,然后更新描述符寫入內存。幾種應用DMA的場合表4?20三種DMA的應用場合幾種

2022-10-14 15:23:41

ASIC(專用集成電路)

GPU的并行算力能力很強,但是它也有缺點,就是功耗高,體積大,價格貴。

進入21世紀后,算力需求呈現兩個顯著趨勢:

一,算力的使用場景,開始細分;

二,用戶對算力性能

2024-01-23 19:08:55

ASIC/ASSP和FPGA就如同印刷品和白紙使用了FPGA器件的電子產品,在產品發布后仍然可以對產品設計作出修改,大大方便了產品的更新以及針對新的協議標準作出的相應改進,從而可以加速產品的上市時間,并

2017-09-21 22:00:39

、ARM和DSP與ASIC相比,FPGA、ARM和DSP都具備與生俱來的可編程特性。或許身處開發第一線的底層工程師要說No了,很多ASIC不是也開放了一些可配置選項,實現“可編程”特性嗎?是的,但與FPGA

2017-09-23 22:20:59

較高的開發門檻以及器件本身昂貴的價格,應用的普及率上和ARM、DSP還是有一定的差距,但是在非常多的應用場合,工程師們還是會別無選擇的使用它。FPGA所固有的靈活性和并行性是其他芯片所不具備的,所以它

2017-10-09 18:53:07

中國通信網絡設備廠商華為正在其部分產品中或采用ASIC以取代Altera的FPGA。這項進展將影響Altera的銷售,并可能打擊“FPGA正在取代ASIC傳統地位”頗具爭議性的說法。華為首次采用ASIC到底會對Altera的銷售有何影響?FPGA和ASIC之間的拉鋸戰到底誰的勝算更大?

2019-09-17 06:26:40

單片機/FPGA/DSP/ASIC/ARM9有哪些優缺點?

2021-11-05 06:38:20

目前,市面上常用的芯片有單片機、FPGA、DSP、ASIC、ARM9,以下分別介紹這幾類芯片的優缺點:單片機:采用Atmel公司的AT89S52單片機作為主控制器。AT89S52是一個低功耗,高性能

2021-07-16 07:10:57

為了實現—是彈武器瞄準自動化,本文設計了基于DSP和FPGA的高速高精確度雙通道CCD圖像采集系統,采用QUartuBn在AJtera的FPGA器件CYCLONEII上設計了CCD驅動時序電路,采用

2014-11-07 14:54:07

系統的效率和功能可以得到最大限度的提高。 在電機控制等許多應用場合,需要產生多路頻率和脈沖寬度可調的PWM波形。本文用Altera公司FPGA產品開發工具QuartusⅡ,設計了6路PWM輸出接口,并

2019-05-06 09:18:16

(在線系統編程)。在電機控制等許多應用場合,需要產生多路頻率和脈沖寬度可調的PWM波形,本文通過使用Altera公司FPGA產品開發工具QuartusⅡ,設計了6路PWM輸出接口,并下載到FPGA

2019-04-25 07:00:05

雖然并不如預想中明朗,但中國3G的蓄勢待發和WiMax的推進以及并不太遙遠的4G、LTE等,將促進宏基站和家用基站市場的起飛。在傳統的ASIC及DSP+FPGA基站解決方案外,多核DSP浮出水面,基站解決方案開始承接新一輪的吐故納新。

2019-07-18 07:54:22

如何根據應用場合選擇功率分析儀的通訊接口?

2021-05-08 08:21:55

如何使用?能夠實現哪些功能? 3. FPGA是否可以實現DSP的功能,進而取代DSP?以前控制算法由DSP實現,現在是否可以在FPGA中實現控制算法?我剛開始學習FPGA/CPLD,只寫過一些簡單的verilog程序,請各位網友多多指教。

2013-07-22 10:01:08

在低延遲,硬件定制,接口靈活性和功耗方面具有優勢。由Berten DSP進行客觀評估也給出了相似的結論如下圖所示。三、面向 FPGA 的 NN 模型優化技術文獻[3]分析了可用于為FPGA(或ASIC

2023-02-08 15:26:46

我用的是TL138EVM-F的開發板,在用FPGA和DSP通信的時候遇到點問題。我看了創龍的例程有UPP的外部回環測試,上板也驗證成功了。我現在需要做的是通過FPGA向DSP發送有符號整型數據,再

2020-04-01 10:27:14

針對電機控制或者其他電力電子應用場合,各大芯片廠商不僅生產了各種芯片和功率器件,并且針對這些應用場合,設計了許多控制算法的類庫。??廠商提供的demo大部分都是基于狀態機的模型設計,并且將各部分

2021-07-09 07:15:24

請問該電路圖實物在幾M增益滾降后在40幾M為什么增益又開始變大了

2018-04-18 22:47:32

ofweek電子工程網訊對于高通來說,未來業務的增長賺取高額利潤的地方,還是在國內手機廠商上,所以這是他們為什么必須穩固自己在國內市場地位的原因。讓人沒有想到的是,高通竟瞄上了小米、OPPO

2017-11-10 15:30:10

功能集成在SoC內的方案。而CPU+FPGA+DSP的SoC技術現在也能提供更多的GMACs執行無線DSP算法了。

2011-07-21 10:52:00

軟件無線電設計中ASIC、FPGA和DSP怎么選?

2021-04-28 06:09:22

ASIC、FPGA和DSP的應用領域呈現相互覆蓋的趨勢,使設計人員必須在軟件無線電結構設計中重新考慮器件選擇策略問題。

2019-09-02 07:58:00

ASIC、FPGA和DSP的應用領域呈現相互覆蓋的趨勢,使設計人員必須在軟件無線電結構設計中重新考慮器件選擇策略問題。從可編程性、集成度、開發周期、性能和功率五個方面探究,你會發現軟件無線電設計中選擇ASIC、FPGA和DSP時需要考慮哪些因素?

2019-08-16 07:51:25

在緊迫的時間要求和一次成功的巨大壓力下,ASIC仿真已成為設計流程中一個關鍵的環節。但一直以來,設計人員在ASIC仿真方面的優選并不多。現在,許多設計人員開始轉而選用一種新工具——基于FPGA的協

2019-07-23 06:24:16

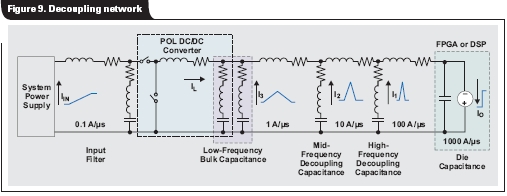

具有多個電壓軌的FPGA和DSP電源設計實例

大多數電子產品由于包含一個或多個FPGA或DSP數字處理芯片而需要提供多個電源軌。在為這些數字IC供電時,

2009-09-25 10:28:52 701

701

基于DSP+FPGA+ASIC的實時圖像處理系統

1.引言

隨著紅外焦平面陣列技術的快速發展,紅外成像系統實現了高幀頻、高分辨率、高可靠性及微型化,在目標跟蹤

2010-01-13 10:39:49 1115

1115

簡述FPGA_和DSP的優缺點及使用場合,實用版

2016-02-16 17:07:02 14

14 ,還號稱ASIC終結者。但是他在成績面前不驕傲自滿,繼續努力,最近兩大FPGA廠商又都推出了帶DSP平臺的FPGA,開始行使起DSP的“職能”,把手伸到到了DSP的地盤。于是這哥仨掐起來了,美其名曰

2018-11-17 11:30:34 741

741

在相當長的一段時間內,FPGA、ASIC、DSP三者不同的技術特征造就了它們不同的應用領域,DSP在數字信號方面是絕對的霸主,ASIC是專業定制領域的牛人,而FPGA由于其價格高、功耗大,主要

2018-11-29 14:37:02 647

647

經過20多年的努力后,在工藝技術進步和市場需求的推動下,“大器晚成”的FPGA終于從外圍邏輯應用進入到信號處理系統核心。在多個應用場合擊敗ASIC后,現在FPGA廠商又開始將目光瞄向了一向是親密戰友的DSP陣營。

2019-01-03 15:32:08 1305

1305

ASIC芯片一旦流片功能就無法改變,基本專片專用。而FPGA可配置特性就可以應用在功能會改變的場合,例如,原型驗證,ASIC設計過程中會使用到FPGA來進行原型驗證;功能升級,在產品中采用FPGA實現一些業內暫時還沒成熟的解決方案,可以在后續功能變動時方便升級。

2019-08-25 10:40:01 10934

10934

FPGA 要取代 ASIC 了,這是 FPGA 廠商喊了十多年的口號。可是,FPGA 地盤占了不少,ASIC 也依舊玩得愉快。這兩位仁兄到底有啥不一樣呢?

2020-12-25 11:56:57 9

9 FPGA_ASIC-DSP和FPGA共用FLASH進行配置的方法(哪些專業適合嵌入式開發)-該文檔為FPGA_ASIC-DSP和FPGA共用FLASH進行配置的方法講解文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 11:16:55 21

21 arm,asic,dsp,fpga,mcu,soc各自的特點人工智能受到越來越多的關注,許多公司正在積極開發能實現移動端人工智能的硬件,尤其是能夠結合未來的物聯網應用,對于移動端人工智能硬件的實現

2021-11-05 20:21:02 18

18 ,稱為半定制專用集成電路,相對來說更接近FPGA,甚至在某些地方,ASIC就是個大概 念,FPGA屬于ASIC之下的一部分。FPGA基本就是高端的CPLD,兩者非常接近。我現在用的是ALTERA...

2021-11-15 19:21:02 11

11 FPGA要取代ASIC了,這是FPGA廠商喊了十多年的口號。可是,FPGA地盤占了不少,ASIC也依舊玩得愉快。那么,這兩位仁兄到底有啥不一樣呢?

2023-03-31 14:41:41 1138

1138

FPGA和ASIC都是數字電路的實現方式,但它們有不同的優缺點和應用場景。本文將以通俗易懂的方式解釋FPGA和ASIC的概念、基本組成、及其應用場景。

2023-08-14 16:37:35 1152

1152 FPGA和ASIC作為數字電路的常見實現方式,其聯系和區別備受關注。本文將從FPGA和ASIC的基本概念入手,深入研究它們的區別與聯系,以幫助讀者更好地理解兩者的應用場景和選擇方法。

2023-08-14 16:38:51 1583

1583 FPGA和ASIC是數字電路中常見的實現方式,因此人們經常會想要了解哪種芯片在未來的發展中更具有前途。然而,這取決于具體的應用場景和需求。在本文中,我們將探討FPGA和ASIC的優劣勢,并分析哪種芯片在特定的應用場景中更具有優勢。

2023-08-14 16:40:20 1028

1028 kk模組的具體應用場合

2023-11-18 18:11:01 309

309

電子發燒友App

電子發燒友App

評論