隨著FPGA在數(shù)據(jù)中心加速和Smart NIC在SDN和NFV領域的廣泛應用,基于以太網(wǎng)接口的FPGA開發(fā)板越來越受到關注。而更高速率的以太網(wǎng)接口技術則是應用的關鍵,本文將詳細介紹基于FPGA的10G以太網(wǎng)接口的原理及調(diào)試技術。

10G以太網(wǎng)接口簡介

1、10G以太網(wǎng)結構

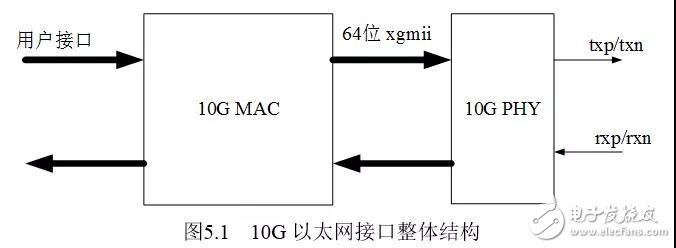

10G以太網(wǎng)接口分為10G PHY和10G MAC兩部分。如下圖所示。

本設計中使用了Xilinx公司提供的10GEthernet PCS/PMA IP核充當連接10GMAC的PHY芯片,然后將該IP核約束到光模塊上構建完整的物理層。需要說明的是本設計主要是完成以太網(wǎng)二層邏輯設計,不涉及PHY層的邏輯設計,如:bit同步、字節(jié)同步、字同步、64b/66b編解碼等。

2、10G以太網(wǎng)接口PHY

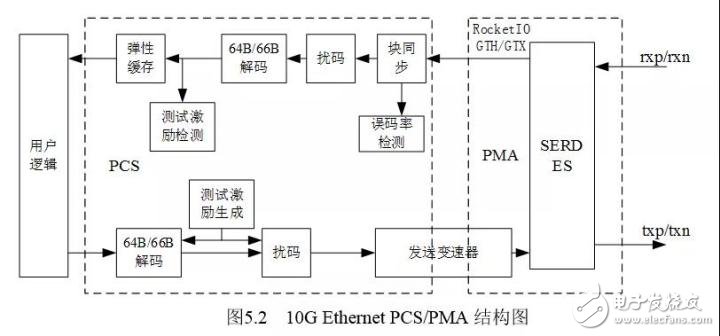

10G EthernetPCS/PMA的整體結構如圖5.2所示,其核心是基于RocketIO GTH/GTX來實現(xiàn)的。從圖中可知,該模塊分為PCS層和PMA層,對于發(fā)送數(shù)據(jù),PCS層主要功能是對數(shù)據(jù)進行64B/66B編碼、擾碼、發(fā)送變速等功能。同時在測試模式下還提供了一個測試激勵源,用于對鏈路進行檢測。PMA層的主要功能是提供并串轉換、對串行信號進行驅動并發(fā)送等功能。對于接收數(shù)據(jù),PMA層的主要功能是將接收到的高速差分信號進行串并轉換、bit同步、時鐘恢復等功能,PCS層對于從PMA層接收到的數(shù)據(jù)進行塊同步、解擾碼、64B/66B解碼、彈性緩存等。同時在測試模式下還提供測試激勵檢測功能,用于檢測鏈路工作狀態(tài)。

在接口調(diào)試過程中,可能用到PMA層的近端環(huán)回和遠端環(huán)回功能。PMA近端回環(huán),用于測試IP核內(nèi)部自回環(huán);PMA遠端回環(huán),用于將接收到的遠端10G PHY發(fā)送的的數(shù)據(jù)在PMA層直接回環(huán)發(fā)送給遠端10G PHY,而不經(jīng)過本地的PCS層。

3、10G以太網(wǎng)接口時鐘布局設計

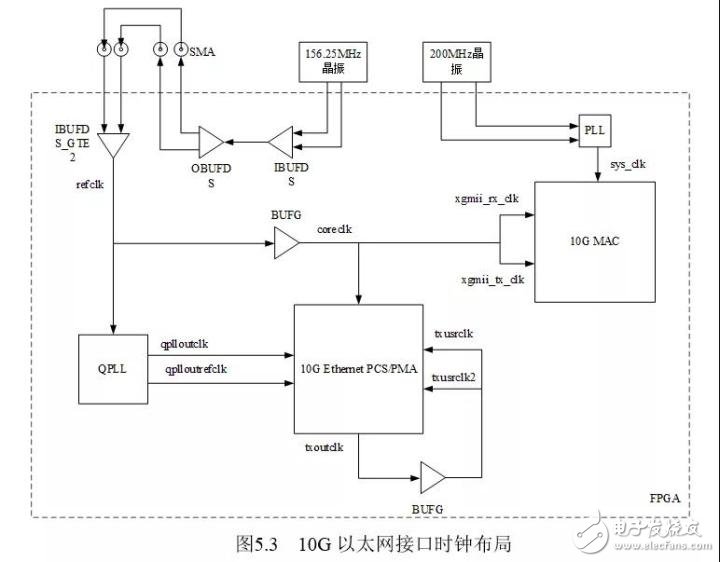

由于10G Ethernet PCS/PMA是Xilinx官方提供的一款IP核,所以我們需要做的工作是結合開發(fā)板的實際情況,為該IP核以及其他模塊設計合理的時鐘電路,使其能夠正常工作。本文選用Xilinx VC709開發(fā)板作為上板調(diào)試的硬件平臺,因此我們的時鐘布局需要充分考慮此開發(fā)板的結構來設計,具體的時鐘布局如圖5.3所示。

由于VC709開發(fā)板連接光模塊的Quad并沒有直接輸入的參考時鐘,而是連接到一對SMA接口,因此我們將156.25Mhz晶振產(chǎn)生的時鐘經(jīng)過FPGA內(nèi)部的IBUFDS、OBUFDS驅動后輸出到另一對SMA接口,并通過同軸電纜將兩對SMA接口互聯(lián),從而使連接光模塊的Quad具有輸入?yún)⒖紩r鐘。

對于FPGA內(nèi)部的時鐘布局主要分為以下4部分:

(a)輸入的差分參考時鐘經(jīng)過一個參考鐘專用緩存(IBUFDS_GTE2)變?yōu)閱味藭r鐘refclk,然后將refclk分為兩路,一路接到QPLL(QuadraturephasePhase Locking Loop),另一路時鐘經(jīng)過一個BUFG后轉變?yōu)槿謺r鐘coreclk,繼續(xù)將coreclk分為兩路,一路作為10G MAC核XGMII接口的收發(fā)時鐘(xgmii_rx_clk和xgmii_tx_clk),另一路用于驅動10G Ethernet PCS/PMA IP核內(nèi)部用戶側的邏輯。

(b) 對于QPLL輸出的兩路時鐘qplloutclk和qplloutrefclk,主要是用于IP核內(nèi)GTH收發(fā)器使用的高性能時鐘,其中qplloutclk直接用于驅動GTH內(nèi)發(fā)送端的串行信號,其頻率為5.15625GHz。qplloutrefclk用于驅動GTH內(nèi)部部分邏輯模塊,頻率為156.25MHz。

(c) txoutclk是由10G Ethernet PCS/PMA IP產(chǎn)生的一個322.26MHz的時鐘,該時鐘經(jīng)過BUFG后分為兩路,其中txusrclk用于驅動IP核內(nèi)GTH的32bits總線數(shù)據(jù),txusrclk2用于驅動IP核內(nèi)PCS層部分模塊。

(d)200MHz的晶振產(chǎn)生差分時鐘輸入到FPGA內(nèi)的PLL(Phase LockingLoop)模塊,PLL模塊以200MHz差分鐘為驅動時鐘生成192MHz用戶鐘(sys_clk)發(fā)送給10G MAC核用戶側。

4、仿真驗證

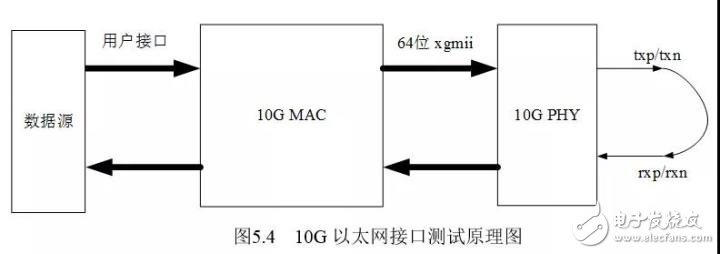

在本節(jié)中我們主要是對10G MAC核和10G Ethernet PCS/PMA IP核進行聯(lián)合仿真測試,用于檢測兩個模塊結合后能否穩(wěn)定運行。具體的測試原理如圖5.4所示。

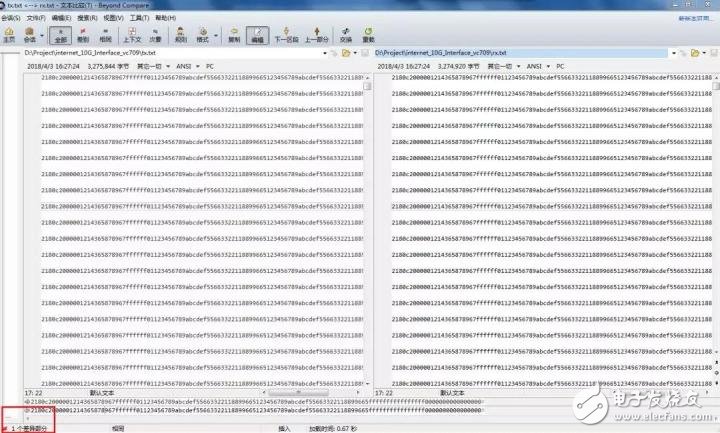

將10G Ethernet PCS/PMA IP核的高速串行差分信號的輸入輸出相連,實現(xiàn)回環(huán)測試。我們在10G MAC核的用戶側的設置一個數(shù)據(jù)源用于發(fā)送數(shù)據(jù)幀,數(shù)據(jù)經(jīng)過MAC核后轉變?yōu)闃藴室蕴W(wǎng)幀,通過XGMII接口發(fā)送到10G Ethernet PCS/PMA IP核,10G Ethernet PCS/PMA IP核將其變?yōu)楦咚俅胁罘中盘栞敵觯咚俅胁罘中盘柦?jīng)過回環(huán)被10GEthernet PCS/PMA IP核接收,重復上述過程的逆過程,最終數(shù)據(jù)在10G MAC核的用戶側接收接口被恢復。本測試具體分為3個步驟:定長最短幀(64Bytes)仿真測試、定長最長幀(1518Bytes)仿真測試、隨機幀長仿真測試。在每一個測試步驟中,我們要盡可能模擬10Gbps的業(yè)務流。對于數(shù)據(jù)的檢測,我們不但要對比波形是否正確,還要將10GMAC核用戶側的收發(fā)數(shù)據(jù)分別記錄到兩個文檔內(nèi),并使用軟件對兩個文檔內(nèi)的數(shù)據(jù)對比來判斷收發(fā)數(shù)據(jù)是否一致。由于篇幅限制,我們只給出定長最短幀的仿真結果截圖。

圖5.5 定長最短幀仿真圖

圖5.6 定長最短幀收發(fā)數(shù)據(jù)對比圖

10G以太網(wǎng)接口板級調(diào)試

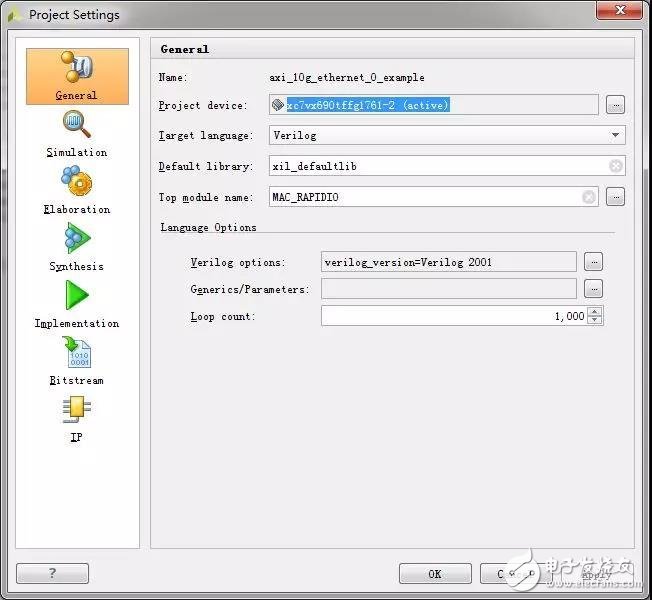

1、工程設置

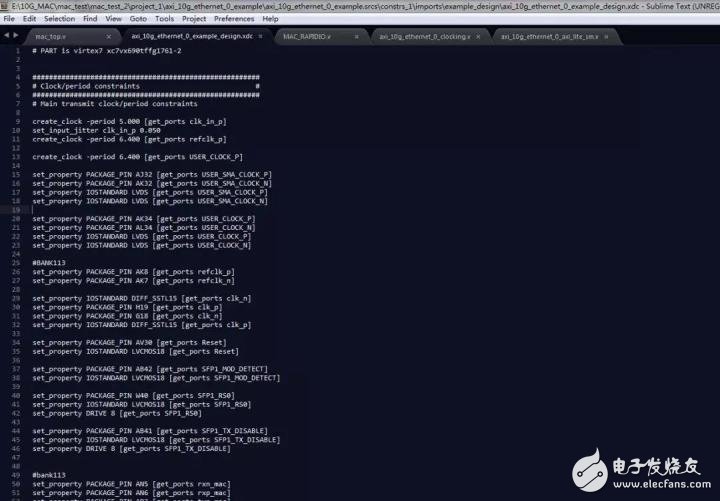

軟件環(huán)境為VIVADO2016.2,芯片設置為xc7vx690tffg1761-2 (active),板子采用Xilinx的VC709開發(fā)板。

VC709開發(fā)板實物圖

Vivado選擇FPGA型號界面

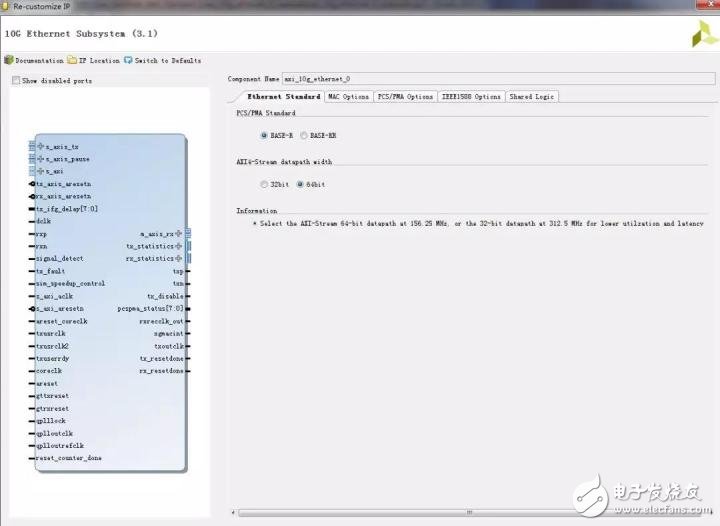

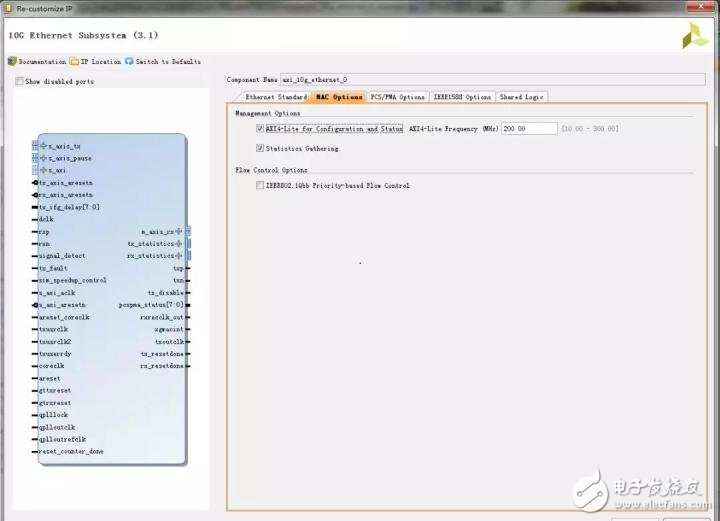

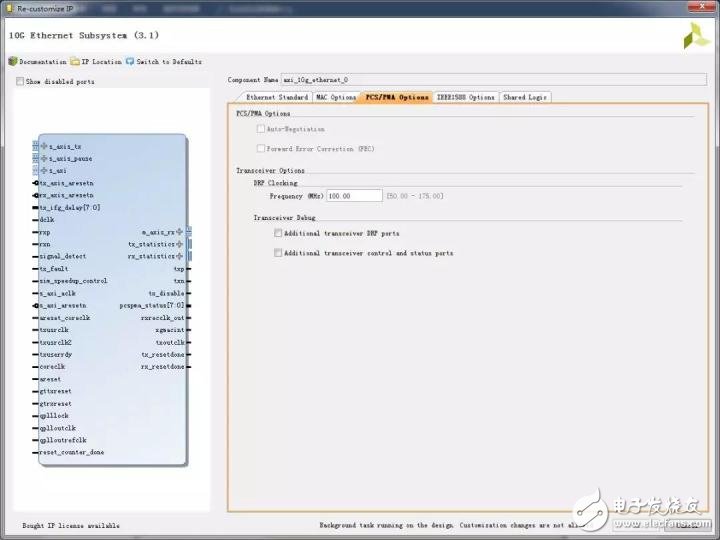

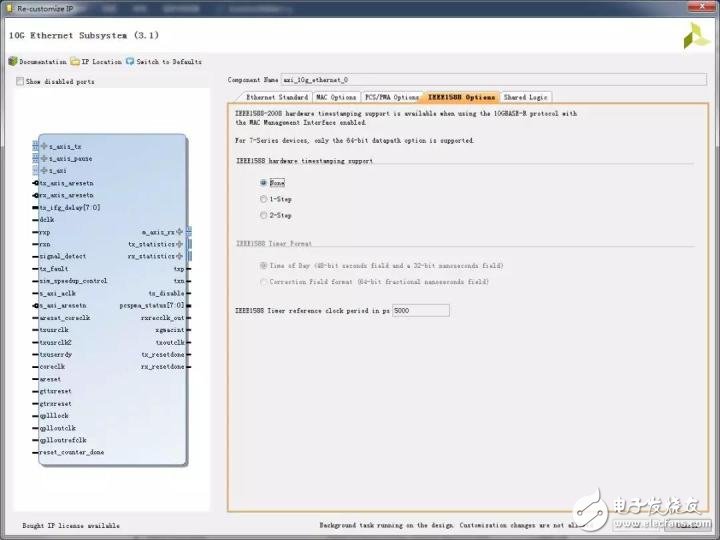

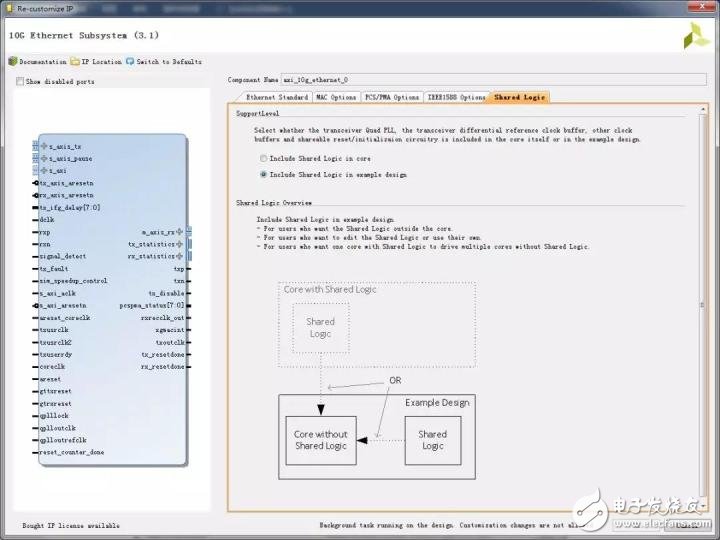

首先選擇IP核,在界面中選擇10G Ethernet Subsystem,PCS/PMA選擇 BASE-R,位寬選擇為64bit,其他標簽中的選項默認即可。

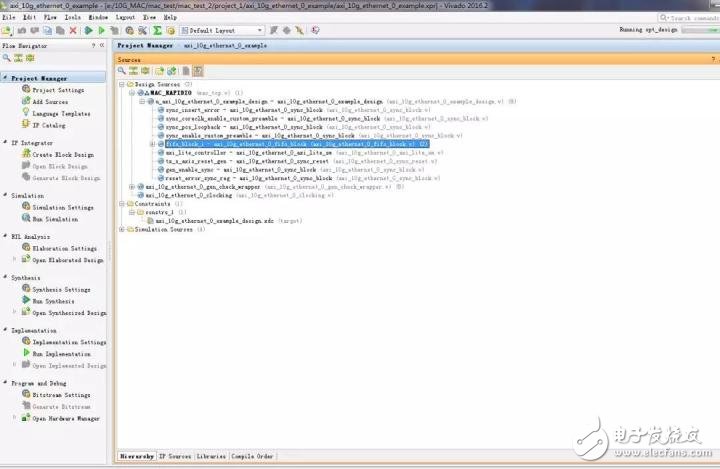

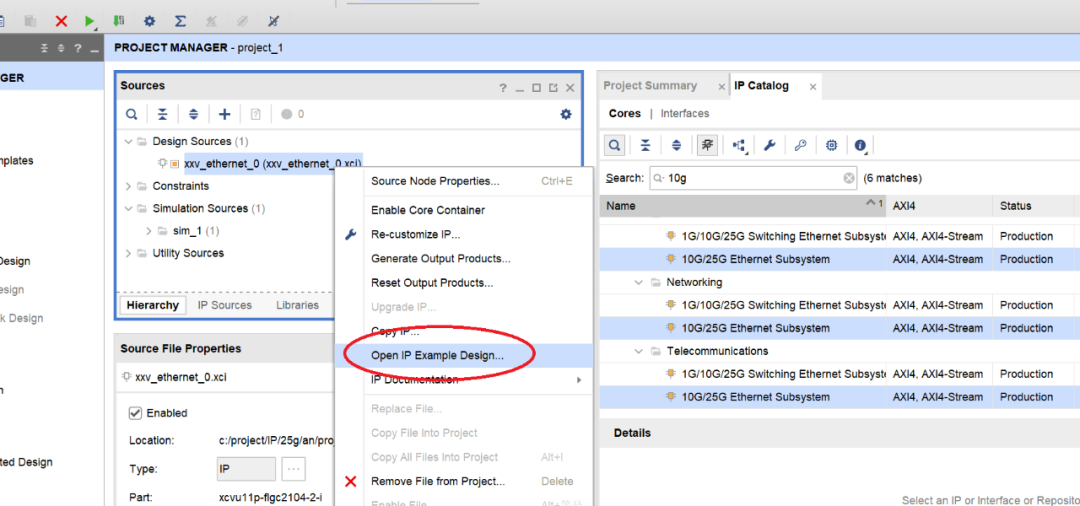

待IP核生成結束之后,右鍵IP核,選擇Open Ip Example Design,VIVADO便會自動生成一個Example Design,如下圖所示:

此時example design設置完成,此時的工程中自帶一個數(shù)據(jù)源,即axi_10g_ethernet_0_gen_check_wrapper模塊,但此數(shù)據(jù)源通過函數(shù)產(chǎn)生數(shù)據(jù),不能綜合,所以為配合Testcenter打流測試,將此數(shù)據(jù)源刪掉。

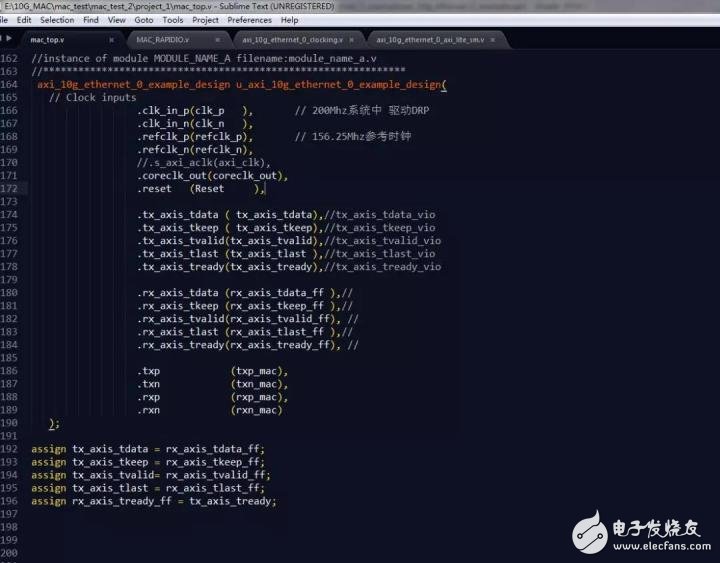

為方便進行管腳分配,在生成的example design上新生成了一個頂層文件,并在此頂層模塊中將用戶側輸入輸出的數(shù)據(jù)接在一起,實現(xiàn)MAC核的自回環(huán)。

此外在xdc文件中,管腳分配如下圖所示:

2、上板驗證

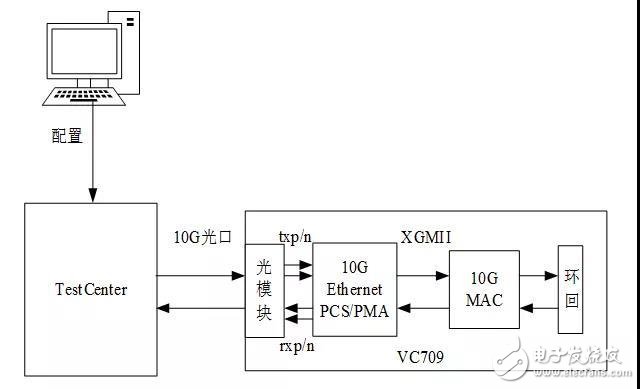

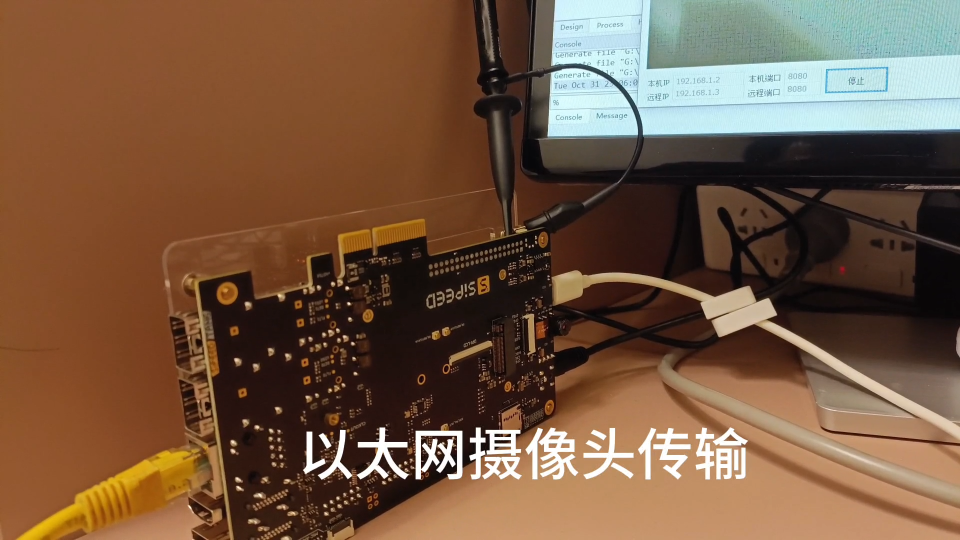

板級驗證環(huán)境連接圖如下,通過10G TestCenter用光口給VC709板子打流,在VC709板子的690T FPGA內(nèi)部編寫邏輯進行用戶側的環(huán)回,通過觀察連接TestCenter的配置PC機上界面,就可以判斷回環(huán)的測試是否成功。

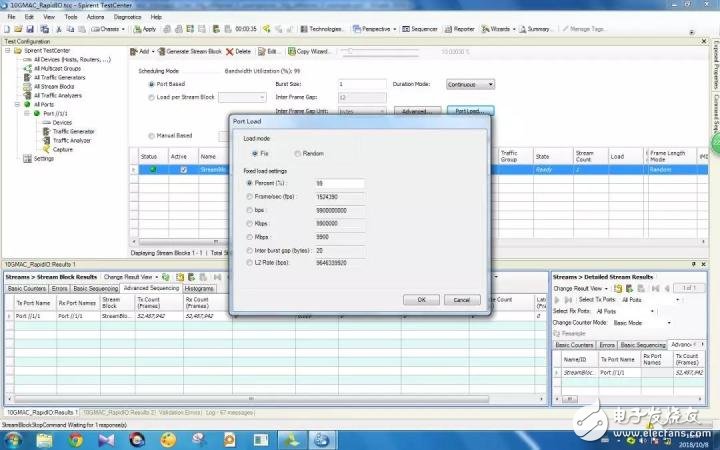

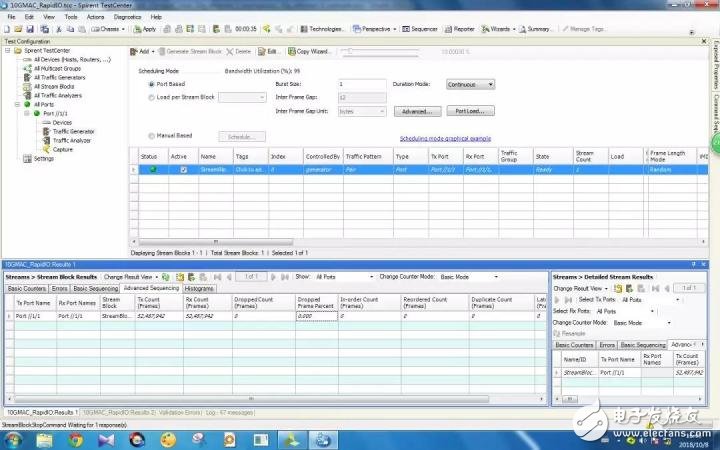

通過10G Testcenter打流測試,首先配置測試環(huán)境,幀長為隨機幀長(64~1518),速率設置為10G(實際設置為9.9G,當滿速10G時Testcenter會出現(xiàn)一些丟幀錯誤,9.9G不會出現(xiàn)問題,但我們采用自己寫的10G以太網(wǎng)MAC核,而非Vivado工具生成的MAC核時,可以支持滿負荷線速處理,本文只給出采用Vivado生成的MAC核的演示結果)。

測試結果如下圖所示,可以發(fā)現(xiàn)數(shù)據(jù)可以正常收發(fā),且沒有丟幀。

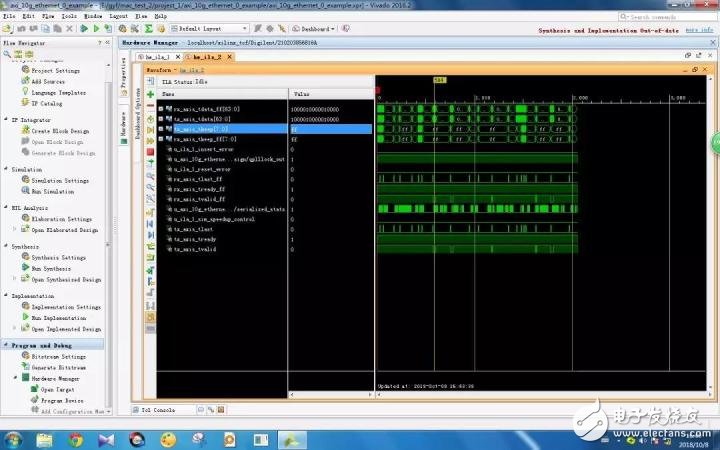

并在VIVADO中抓取了用戶側信號,結果如下圖所示,數(shù)據(jù)收發(fā)正常。

本例程僅說明回環(huán)測試,在實際應用中,數(shù)據(jù)進來后,就可以用FPGA進行各種需要的處理。如矩陣運算、圖像處理、機器學習、壓縮、非對稱加密、Bing 搜索等。可以大幅度的降低CPU軟件的負荷,提高整體的處理能力。

參考時鐘管腳分配注意事項

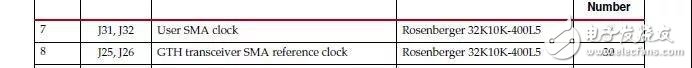

根據(jù)第一部分圖5.3有關VC709板子時鐘布局的介紹,給10G以太網(wǎng)接口提供參考時鐘的SMA接口如下圖VC709開發(fā)板上紅色框內(nèi)標記7和8兩個接口,在實際上板調(diào)試過程中,需要手動用同軸電纜將兩個接口連接起來。

用同軸線連接后的實物圖如下所示:

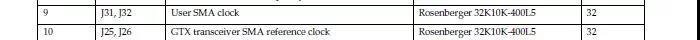

查看用戶手冊,可以發(fā)現(xiàn)7和8接口描述如下。

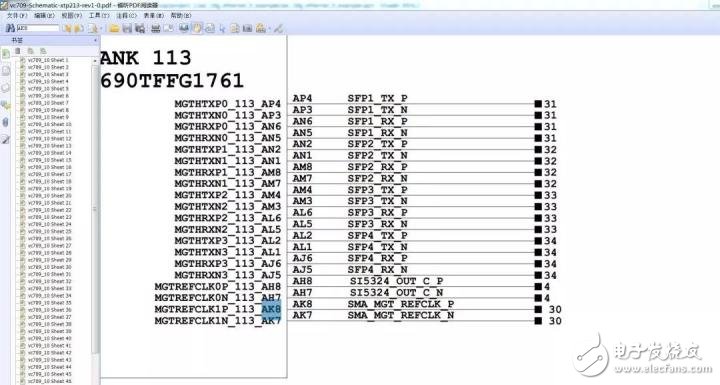

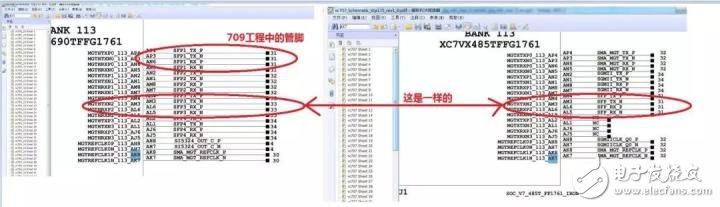

查看VC709原理圖,可以發(fā)現(xiàn)對應690T FPGA管腳的參考時鐘如下圖:

另外,在Xilinx系列開發(fā)板中,VC707板子也具有10G的以太網(wǎng)接口,使用方法與VC709相同。

在VC707板子上,需要用同軸線連接的管腳是上圖中的9和10。

VC709板子上VC707板子上與10G接口相關的FPGA管腳對比圖如下,從圖中可以看出,VC709開發(fā)板可以接10G的接口數(shù)明顯多于VC707開發(fā)板。

上板調(diào)試過程中遇到的問題

1、時序違例問題。

問題描述:在使用軟件vivado 2016.2完成對10G以太網(wǎng)接口綜合實現(xiàn)后,發(fā)現(xiàn)軟件報告該工程有幾處時序路徑的建立時間無法滿足,可能會出現(xiàn)時序錯誤。

查找原因:通過查看時序報告,并結合工程的實際設計了解到,出現(xiàn)問題的位置是10G MAC核的異步FIFO,由于此FIFO的兩個時鐘為異步時鐘,導致軟件在對其進行布局布線時無法同時滿足兩個時鐘域的要求,因此出現(xiàn)建立時間報紅的問題。

解決方法:由于此FIFO內(nèi)的核心是一個雙口RAM,此RAM本身就可以實現(xiàn)數(shù)據(jù)的跨時鐘域傳輸,所以,此問題并不會出現(xiàn)時序錯誤。通過時序約束對幾處時序違例的位置的時序路徑進行忽略,解決該問題。

2、10G以太網(wǎng)接口無法接收數(shù)據(jù)的問題

問題描述:在對10G以太網(wǎng)接口進行上板測試時,發(fā)現(xiàn)此接口無法從交換機接收數(shù)據(jù),10G EthernetPCS/PMA IP核的狀態(tài)信號顯示鏈路失同步、鏈路狀態(tài)為低。

查找原因:由于是接口出現(xiàn)問題,因此使用Xilinx官方提供的專用測試接口的ibertIP核對其進行測試,發(fā)現(xiàn)ibert的近端PCS回環(huán)和PMA回環(huán)都可以通過測試,但是在使用外部光纖進行回環(huán)時無法通過測試,因此分析可能是光模塊的問題導致10G以太網(wǎng)接口無法接收數(shù)據(jù)。通過查閱開發(fā)板VC709的官方手冊后發(fā)現(xiàn),此開發(fā)板的光模塊的默認狀態(tài)是關閉的,要通過代碼對其進行配置才能使光模塊正常工作。

解決方法:查閱手冊,根據(jù)手冊對光模塊進行配置。再次進行測試,10G以太網(wǎng)接口可以接收數(shù)據(jù),問題解決。

3、Vivado 2016.2軟件BUG問題

發(fā)現(xiàn)了vivado2016.2版本的一個BUG!

參考文獻

[1] Xilinx.ug887-2013.VC709evaluation board for the Virtex-7 FPGA user guide[S].Xilinx, 2013.

[2] Xilinx.ug885-2016.VC707evaluation board for the Virtex-7 FPGA user guide[S].Xilinx, 2016.

[3] 付新宇. 10G HIMAC協(xié)處理器關鍵技術研究.[D].西安電子科技大學,2018.

應用場景

VC709和VC707開發(fā)板上還有千兆的接口模式,如SGMII接口等,具體調(diào)試見本公眾號之前文章:SGMII接口調(diào)試。同時,隨著以太網(wǎng)接口速率的提升,10G、20G、40G甚至100G的以太網(wǎng)接口應用越來越廣泛,具體來講主要有兩個關鍵的應用領域。

1、數(shù)據(jù)中心加速。

在一些數(shù)據(jù)中心采用10G或者更高速率的以太網(wǎng)接口加FPGA的模式,可以在數(shù)據(jù)進入到服務器之前采用硬件的方式進行快速的處理,降低服務器CPU的負荷,見本公眾號之前文章:深度 | 如何評價微軟在數(shù)據(jù)中心使用 FPGA ?;

2、SDN/NFV

把上面的應用場景擴展一下,就可以把帶有FPGA的以太網(wǎng)卡用來降低各種各樣場景下的CPU負荷,目前較為流行的概念是SMART NIC即智能網(wǎng)卡,其核心是通過FPGA(現(xiàn)場可編程門陣列)協(xié)助CPU處理網(wǎng)絡負載,編程網(wǎng)絡接口功能,具有以下特征:

通過FPGA本地化編程支持數(shù)據(jù)面和控制面功能定制,協(xié)助CPU處理網(wǎng)絡負載;

通常包含多個端口和內(nèi)部交換機,快速轉發(fā)數(shù)據(jù)并基于網(wǎng)絡數(shù)據(jù)包、應用程序套接字等智能映射到到相關應用程序;

檢測和管理網(wǎng)絡流量。

Smart NIC能夠提升應用程序和虛擬化性能,實現(xiàn)軟件定義網(wǎng)絡(SDN)和網(wǎng)絡功能虛擬化(NFV)的諸多優(yōu)勢,將網(wǎng)絡虛擬化、負載均衡和其他低級功能從服務器CPU中移除,確保為應用提供最大的處理能力。與此同時,智能網(wǎng)卡還能夠提供分布式計算資源,使得用戶可以開發(fā)自己的軟件或提供接入服務,從而加速特定應用程序。

目前業(yè)界提供基于FPGA的Smart NIC的廠商包括Accolade、BittWare、Enyx、Ethernity、Napatech、Netcope、Reflex CES、Silicom和Solarflare,通常集成自Intel或Xilinx的FPGA來實現(xiàn)。此外,Broadcom,Cavium,Intel,Kalray,Mellanox,Netronome,Silicom和SolidRun均可提供基于處理器的Smart NIC,使用帶有集成處理器內(nèi)核或FPGA的處理器或智能I/O處理器;亞馬遜和谷歌已經(jīng)開發(fā)了Smart NIC ASIC。

電子發(fā)燒友App

電子發(fā)燒友App

評論