近年來, 隨著數字信號處理(DSP) 和超大規模集成電路(VLSI) 技術的發展, 正交頻分復用OFDM(Orthogonal Frequency Division Multiplexing)技術的應用有了長足的進步和廣闊的發展前景。IEEE802.11a中就將正交頻分復用作為物理層的傳輸技術;歐盟在數字音頻廣播(DAB)、地面數字視頻廣播(DVB2T)、高清晰度電視(HDTV)以及2003年4月公布的無線城域網(WMAN)802.16a等研究中都使用了正交頻分復用技術作為信道的傳輸手段。在正交頻分復用技術逐漸成熟的今天, 如何降低通信系統的成本, 使之更廣泛地應用于數傳系統中, 已成為正交頻分復用研究的熱點。本文基于802.16a協議的原理架構,本著小成本、高效率的設計思想,建立了一個基于FPGA的可實現流水化運行的OFDM系統的硬件平臺,包括模擬前端及OFDM調制器及OFDM 解調器,用來實現OFDM的遠距離無線傳輸系統。

1 模擬前端

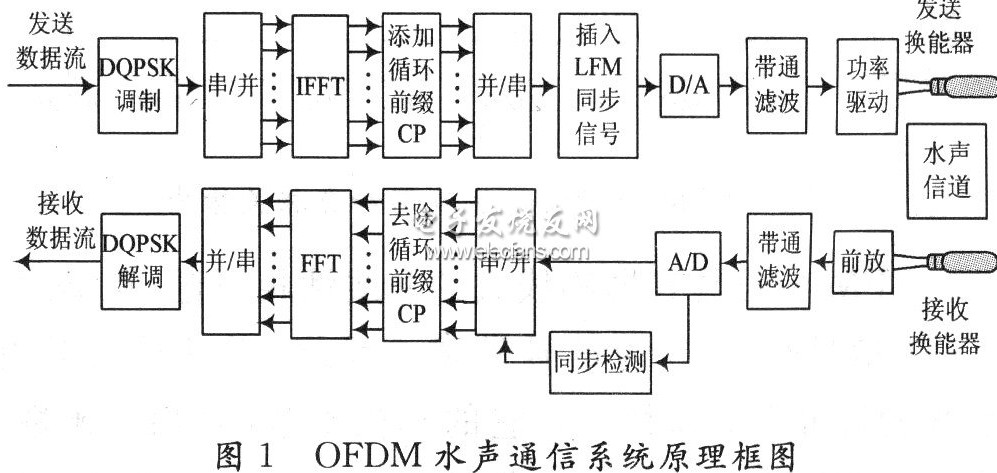

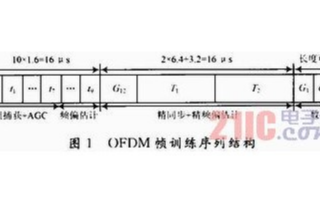

發送端DA模塊主要由XILINX公司的FPGA-XC2V1000芯片和數模轉換芯片AD9765、濾波器和放大器構成,基帶處理調制后數據在控制時鐘同步下送入FPGA進行降峰均比等算法的處理,然后經過交織將其送入AD9765進行數模轉換并上變頻到70MHz,輸出的模擬信號再經聲表濾波器后放大進入下一級射頻模塊。發送端DA模塊硬件結構框圖如圖1所示。

接收端AD模塊主要由增益放大器、帶通濾波、采樣芯片AD9238和數字下變頻器GC1012構成。AD模塊的主要功能是完成中頻信號的采樣和數字下變頻,在FPGA XC2V1000中完成符號同步算法,其輸出送OFDM解調器。接收端AD模塊硬件結構框圖如圖2所示。

射頻模塊工作在70MHz中頻上,射頻模塊的功能是將完成調制的中頻信號搬移到射頻波段上,或者將空中的接收信號下變頻到模擬前端所需的中頻波段上。

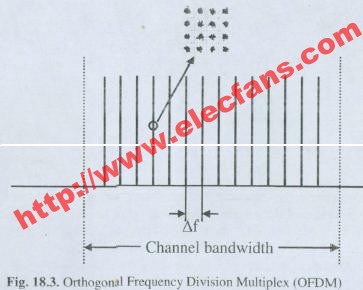

2 OFDM 調制器實現架構

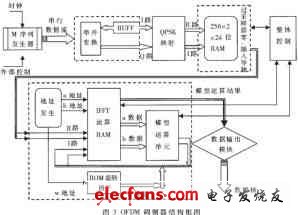

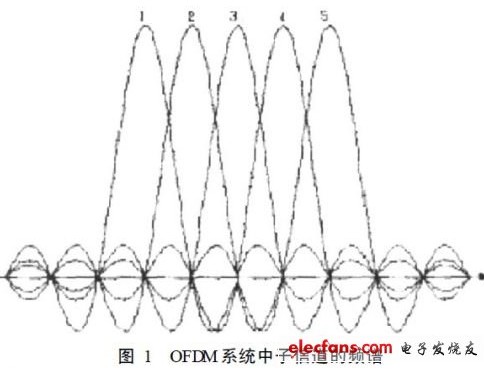

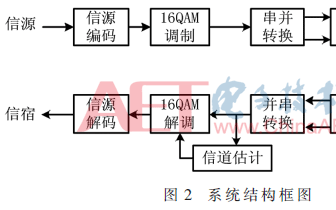

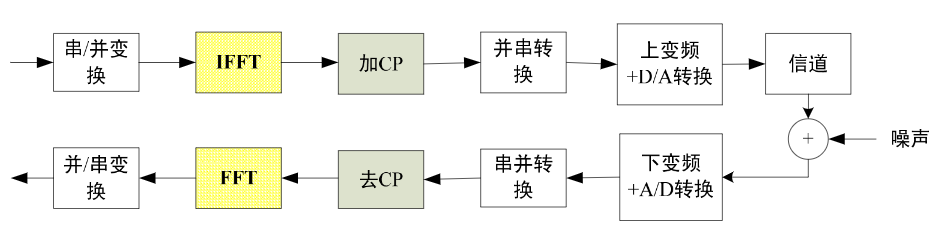

在OFDM系統中,OFDM調制器主要完成OFDM數據的調制。圖3為OFDM調制器的結構框圖。OFDM的調制器采用N=120個數據子信道,8個導頻信道。120個數據子信道都采用 QPSK的信道調制,8個導頻信道采用BPSK的信道調制。為了使用基帶傳輸,進行添零處理(添加128個0),使頻帶擴展1倍。經過逆序處理后,采用256點的IFFT進行 OFDM調制。系統時鐘為80MHz,用 FPGA 完成數據的編碼和調制,最后以讀時鐘為500kHz的速率送往 D/A。

在FPGA中,按照具體的參數要求實現了OFDM系統中的調制功能,其工作流程為:數據發生器(M序列產生器)發送數據,串并轉換后存儲在 256×2位的RAM_in中,當接收夠一幀數據所需要的信息量后,從RAM_in中讀取數據進行QPSK映射、過采樣添零,隨后插入導頻模塊。與此同時,IFFT模塊接收QPSK映射、過采樣添零和插入導頻模塊發送出的數據;當 QPSK、添零、共軛模塊處理完1個數據包的數據后,IFFT 模塊開始計算,進行OFDM的IFFT調制,經IFFT 模塊計算后的數據輪換存入RAM_ou1或者RAM_ou2;控制模塊發出使能信號,先從數據輸出模塊中讀取同步頭發送,同步頭發送完成后,再從RAM_ou1或者RAM_ou2中讀取循環前綴和數據塊;當 IFFT 模塊計算完的數據全部送出后,控制模塊判斷開始處理下一包數據,處理到第10包數據,則通知外部控制器一幀數據處理完成。[next]

3 OFDM 解調器實現架構

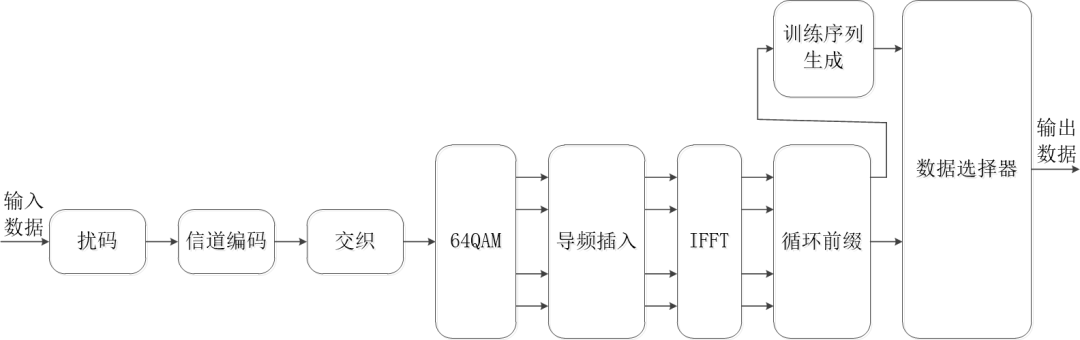

在OFDM系統中,解調器主要是對接收 A/D 采樣來的數據進行解調。圖4為OFDM解調器的結構框圖。

在FPGA中,按照參數要求實現:將從A/D以500kHz的速率采樣來的數據存入 RAM 當中,當接收到第64個幀頭數據時,開始計算局部自相關函數;每接收到一個幀頭數據,取出8位(最高位無效,剩余7位為巴克碼),計算一次x(i)*x(i+j),并存儲、判斷,是否有相關最大值,如果有,則判斷計數器加1,在一個幀頭短前導字部分中,共有10個短前導字片,每一片為64個采樣點;當接收到第640個數據后,判斷累加器是否超過了門限值640×3,如果累加門限值達到1920,則認為有幀到達,整體控制模塊產生使能信號,表示粗同步結束,準備接受長前導字,進行細同步和頻偏估計計算,否則,將累加計數器清零,重新開始接受幀頭;幀到達檢測和幀同步過程完成后,再將接收到的數據存入到解幀模塊的數據RAM中;當數據RAM中存滿256點的數據后,整體控制模塊發出讀使能信號、解幀使能信號和FFT的START信號,從RAM中讀取數據,送往FFT 進行OFDM的解調;然后去除循環前綴,去除添加的零和導頻信息;最后經過QPSK的反映射和并串轉換后,還原成原始數據讀出,并等下一幀數據的接收。

4 系統調試與性能分析

采用OFDM技術的無線城域網通信系統是一個比較復雜的系統。利用Matlab仿真完成系統可行性論證后,需要考慮如何利用FPGA完成這個算法流程,這需要考慮采用特定FPGA進行運算時有限字長以及浮點運算的特點和系統所占用的FPGA資源,以保證系統的規模不至于過大而超過特定FPGA計算的存儲能力。經過在硬件設備上的調試,最終完成采用OFDM技術的城域網無線通信系統。

通過仿真完成可行性論證后,在以Altera公司的EP1C6Q240C8芯片為基礎的FPGA硬件平臺上,實現了以QPSK為調制形式,以FFT/IFFT變換為主的OFDM技術的城域網無線通信系統。

4.1 IFFT模塊

發送端系統的主時鐘頻率設計為80MHz,整體采用同步時序邏輯。發送端M序列的產生速率設定為80Mbps。送往D/A的數據速率設定為500kHz。在數據接收模塊,數據收到后立刻存儲,占用時間即為PC發送數據的時間。在QPSK、添零、導頻插入模塊,由于沒有中間存儲器,從RAM讀出數據,經過映射后就直接輸出,整個模塊需要256個時鐘周期。IFFT 模塊采用流水線結構的算法,計算256點 IFFT需要128×8個蝶型單元,合計需要40 960個時鐘,加上輸入輸出所占用的時間,總共約需要41 216個時鐘周期(中間有一些狀態的跳轉,合計512μs)。在數據輸出模塊,其輸入是 IFFT 模塊的輸出,它的輸出速率由 D/A控制。在FPGA中,OFDM調制器的邏輯單元的使用情況見表1,OFDM解調器的邏輯單元的使用情況見表2, IFFT的運算結果見圖5。

在表1和表2中,調制器和解調器中所含有的引腳數過多,主要原因是在這些引腳中還含有很多用于調試和測量的引腳,在整個系統調試時,可以將調試和測量用的引腳去掉,只留有數據、地址和控制引腳。

在解調器中需要用到大量的存儲單元,但考慮到Cyclone系列的存儲單元有限,而邏輯單元豐富的情況,故在解調器中,在幾乎耗盡EAB單元時,用邏輯單元來構造所需的存儲器,可以實現正常的存儲功能。[next]

在開發工程中,主要用到的開發工具由 Altera 公司的QuartusII 及Mathworks 公司的 Matlab。

驗證過程如下:

·Matlab隨機生成一組128個復數,然后按照 OFDM 幀格式插入0得到256復數點的一個符號,并寫入文件(如 datain.dat);

在QuartusII中生成 IFFT 的仿真波形文件(ifft.vwf),另存為 ifft.tbl,并刪除其余信號,僅保留 I&Q(輸入數據,24bit);

在UltraEdit中打開ifftt.tbl、datain.dat,用datain.dat 中的隨機數代替ifft.tbl 中的 I&Q 數據,保存ifft.tbl;

在QuartusII中打開 ifft.tbl,將I&Q復制到 ifft.vwf 中,開始運行仿真;

·將仿真結果另存為dataout.tbl,用Matlab讀取與原數據在Matlab下的IFFT變換結果進行比較分析。

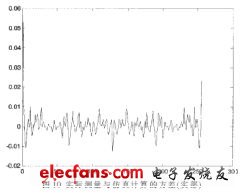

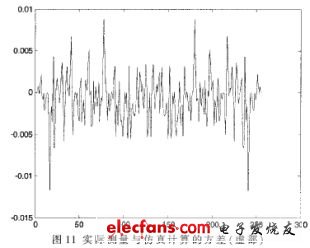

給出一組隨機數據輸入,經過FPGA中的IFFT模塊變換得到時域幅度如圖6(實部)、圖7(虛部)所示。

而將同樣的隨機數經過MATLAB變換,得到的時域幅度如圖8(實部)、圖9(虛部)所示。

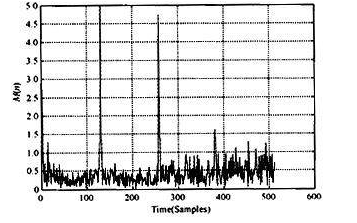

實際測量與仿真計算的方差分析如圖10(實部)、圖11(虛部)所示。兩者結果基本一致。

4.2 幀到達檢測同步模塊

對于幀到達檢測同步系統,要求盡可能在較短的時間內建立同步,并且在幀同步建立后應有較強的抗干擾能力。通常用漏同步概率P1、假同步概率P2和同步平均建立時間ts三個性能指標來表示同步性能的優劣。在本文的幀同步信號提取電路的建模與設計中,是以7位巴克碼識別器作為幀同步碼組的。在同步系統處于捕獲階段時,設置自動判決門限為7;在幀同步建立以后,則把判決門限降為6,這樣做的目的一方面是減少假同步的概率,另一方面是為了減少漏同步的概率。

漏同步概率P1:

假設系統的誤碼率為P,7位碼全部正確的概率是(1-P)7,因此判決門限電平為7時的漏同步概率為P1=1-(1-P)7。若將判決門限改為6,此時允許有一位錯碼,出現一位錯碼的概率為C71P1(1-P)6。漏同步概率為P1=1-[(1-P)7+C71P1(1-P)6]。一般地,設幀同步碼組數目為n,判決器容幀同步碼組中最大的錯碼數為m,則漏同步概率為:

從前面的幀同步系統的設計可以了解到,識別器只能被動地識別與幀同步碼組相同的碼組,如果在信息碼組中也出現了與幀同步碼組相同的碼組,這時識別器會把它誤認為幀同步碼組而出現假同步。

比較式(1)和式(2)可以看出,當m增大時,P1減小,P2增大,兩者是矛盾的,另外還可以看出,當n增大時,P1增大,而P2減小,兩者也是矛盾的。因此m和n的選擇要兼顧P1和P2的要求。

平均同步建立時間ts:

假設漏同步和假同步都不發生,即P1=0,P2=0。在最壞的情況下,實現幀同步最多需要一幀的時間。若一幀的碼元為N,碼元寬度為Tb,則最長的幀時間為NTb。如果同時出現漏同步和假同步,需要額外的同步建立時間,由此得到幀同步平均建立時間為:

ts=(1+P1+P2)×NTb

4.3 數據傳輸速率評價

經過實際測試,針對256點結合QPSK調制,每解調出一個符號平均所需要的指令周期為41 216個時鐘周期,即512μs。對此實際調試情況,分析其實測參數數據如下:

一個OFDM符號內包含的比特數為:1/2(卷積碼)×2bit(QPSK)×120(用戶子載波)+2bit(BPSK)×8(導頻子載波數)=136bit,則除去導頻開銷,能夠用于數據傳輸的空中數據率為。

由此可見,實際測試的數據傳輸速率達到本系統要求(150kbps),表明此OFDM基帶處理系統的數據傳輸性能充分滿足所制定的標準。

本文建立的基于FPGA的可實現流水化運行的OFDM系統的硬件平臺,經系統調試和性能評價,符合設計要求,該硬件平臺的實現使得低成本高速OFDM調制設備的實現成為可能。

電子發燒友App

電子發燒友App

評論