SOPC中自定義外設和自定義指令性能分析

NiosII是一個建立在FPGA上的嵌入式軟核處理器,靈活性很強。作為體現NiosII靈活性精髓的兩個最主要方面,自定義外設和自定義指令的性能開始受到越來越多開發者的關注。本文在對NiosII自定義外設和自定義指令進行深入研究后,采用實驗的方法,通過實例CRC32對比了在實現相同功能的情況下,自定義外設和自定義指令的性能差異,并從自定義外設和自定義指令的實現機理上給予說明。分析結果表明: 在SOPC系統中,如果系統的實時性要求非常高,那么采取自定義外設來實現系統中關鍵處理模塊無疑是最佳選擇。

關鍵詞 自定義外設 自定義指令 CRC校驗 性能分析 SOPC

引言

NiosII是一個嵌入式軟核處理器,除了可以根據需要任意添加已經提供的各種外設以外,用戶還可以通過定制自定義外設和自定義指令的方式來滿足各種應用需求。定制用戶外設和用戶指令是使用NiosII嵌入式軟核處理器的重要特征。定制的用戶外設能夠以“硬件加速器”的形式實現各種各樣用戶要求的功能;同時定制的用戶指令,可以把一個復雜的標準指令序列簡化為一條用硬件實現的單個指令,以增強對實時軟件算法的處理能力。近來,隨著國內SOPC開發的逐步深入,這兩者的性能開始成為一個關注的焦點。本文通過CRC32對SOPC系統中的自定義外設和自定義指令的實現以及對性能差異所作的詳細分析,給廣大SOPC開發人員提供參考。

1? CRC自定義外設的實現

1.1? SOPC系統中自定義外設的組成和結構

自定義外設作為NiosII軟核處理器超強靈活性的體現,其開發遵循一定的規律。一個用戶自定義外設必須進行硬件設計,也就是說,必須用硬件描述語言來描述出硬件的邏輯組成。一般來說,一個自定義外設主要由下列部分組成:

① ?描述自定義外設邏輯的硬件描述文件部分(主要是HDL程序)。

②? 軟件文件,一個用來定義外設寄存器的C語言頭文件,以及讓程序員控制這個元件的軟件驅動程序。

③? 元件的描述文件(class.ptf)。該文件定義了元件的架構,提供了SOPC Builder將該元件集成到一個系統的各種信息。該文件由元件編輯器根據用戶提供的硬件和軟件文件以及在圖形用戶界面中設置的各個選項和參數自動生成。圖1給出了帶Avalon從端口的自定義外設組成框圖。

從圖中可以看出,一個典型的自定義外設主要由下列功能模塊組成:

①? 任務邏輯。任務邏輯實現外設的基本功能,是必不可少的組成部分。

②? 寄存器文件。寄存器文件部分提供任務邏輯和外界交換信息的橋梁。有了寄存器文件,用戶就可以通過Avalon接口采用“基地址+地址偏移量”的方法來訪問外設內部的各個寄存器。

③? Avalon接口。Avalon接口為寄存器文件提供了一個標準的Avalon前端。該模塊使用Avalon規定的信號來訪問寄存器文件,并且支持任務邏輯的傳輸類型。

1.2? CRC32自定義外設的實現

CRC32校驗可以由軟件或硬件來實現。現多采用超大規模集成電路芯片以硬件方式實現。例如:

其硬件實現原理如圖2所示。

編碼運算過程如下:

開關關閉,k位數據移入寄存器,同時送到外部。當k位信息全部送到外部時,除法運算也正好進行完畢,寄存器中的r位數據就構成了余項的系數序列,即形成了校驗碼。然后切斷除法反饋電路,將移位寄存器的每一位逐次輸出到信道中。這些校驗碼與原來的數據位一起構成了完整的碼字。

采用HDL語言來描述出CRC32的硬件實現,命名為crc.v。在SOPC Builder元件編輯器中加入該元件,其中自定義外設的接口信號和Avalon信號類型的一一對應關系如表1所列。

當把自定義外設加入到SOPC系統中時,系統自動生成一個system.h文件。在system.h中生成的CRC自定義外設的相關信息如下:

#defineCRC_NAME "/dev/crc"

#defineCRC_TYPE "avalon_crc"

#defineCRC_BASE 0x06210880

根據system.h中的信息,可以建立名稱為altera_avalon_crc_regs.h的寄存器頭文件。在這個C頭文件中,用清晰的宏符號描述出設備的寄存器集合,并且給出其訪問方法。

#ifndef __ALTERA_AVALON_CRC_REGS_H__

#define __ALTERA_AVALON_CRC_REGS_H__

#include

#defineCRC_INIT_REG0

#defineCRC_WRITE_REG4

#defineCRC_READ_REG016

#defineCRC_READ_REG120

#defineCRC_READ_REG224

#defineCRC_READ_REG328

#defineCRC_INITIALIZATION(base)

IOWR_32DIRECT(base, CRC_INIT_REG, 0)

#defineCRC_WRITEDATA_8(base,data)

IOWR_8DIRECT(base, CRC_WRITE_REG, data)

#defineCRC_WRITEDATA_16(base,data)

IOWR_16DIRECT(base, CRC_WRITE_REG, data)

#defineCRC_WRITEDATA_32(base,data)

IOWR_32DIRECT(base, CRC_WRITE_REG, data)

#defineCRC_READRESULT_32(base)

IORD_32DIRECT(base, CRC_READ_REG0)

#defineCRC_READRESULT_64(base)

IORD_32DIRECT(base, CRC_READ_REG1)

#defineCRC_READRESULT_96(base)

IORD_32DIRECT(base, CRC_READ_REG2)

#defineCRC_READRESULT_128(base)

IORD_32DIRECT(base, CRC_READ_REG3)

#endif? //__ALTERA_AVALON_CRC_REGS_H__

該頭文件定義了CRC IP核的寄存器訪問宏。用戶可以通過Avalon接口采用“基地址+地址偏移量”的方法來訪問外設內部的各個寄存器,以實現NiosII CPU對CRC IP核的控制。

2? CRC32自定義指令的實現

2.1? 自定義指令的原理和開發

自定義指令是基于NiosII處理器的SOPC系統的一個重要特征。NiosII處理器自定義指令不僅擴展了CPU的指令集,還能提高對時間要求嚴格的軟件運行速度,因此提高了系統的整體性能。采用自定義指令,用戶可以實現傳統處理器無法達到的最佳性能。在對數據處理速度要求比較高的場合,把由標準指令序列實現的核心功能變成由一條用戶定制的指令來實現,這樣可以明顯提高軟件的執行效率。基于硬件處理模塊的自定義指令可通過單個時鐘周期或多個時鐘周期的硬件算法操作完成原本十分復雜的處理任務。NiosII處理器最多支持256條定制指令,加速通常由軟件實現的復雜數學運算。

自定義用戶指令實質上就是讓軟核處理器實現由硬件邏輯實現的某種功能,這個硬件邏輯連接到NiosII處理器的算術邏輯單元上。對于NiosII的標準指令,NiosII使用ALU來完成相應的算術邏輯操作;對于自定義指令,則采用用戶自己建立的硬件邏輯來完成運算。

2.2? CRC32定制指令的實現

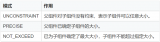

在前面開發的CRC自定義外設的基礎上,按照定制指令所要求的設計方式,把前面開發的自定義外設改寫成一條指令。本設計中,CRC自定義指令是作為多周期指令來實現的,在多周期指令要求中必須包括信號clk、clk_en、reset,其他的信號不是必需的。

由于在SOPC系統中自定義外設的接口類型與自定義指令的接口類型要求不一樣,因此要求在自定義外設的基礎上必須加上一個接口文件。這個接口文件的作用是為了與多周期指令的端口信號類型對應。接口文件端口信號和自定義外設端口的對應關系如表2所列。

開發完成后,把自定義指令加到NiosII CPU中。生成系統后,在生成的system.h文件中,關于CRC自定義指令的宏如下:

#define?? ALT_CI_CRC_CUSTOM_INSTRUCTION_N 0x00000000

#define ALT_CI_CRC_CUSTOM_INSTRUCTION(A,B)__

builtin_custom_inii

(ALT_CI_CRC_CUSTOM_INSTRUCTION_N,(A),(B))

其中,“ALT_”是宏定義的前綴,表示為Altera公司;CI是用戶定制指令的意思;CI_CRC_CUSTOM_INSTRUCTION是用戶指令的邏輯模塊名稱;N表示指令操作碼。

3? 自定義外設和自定義指令在SOPC系統中的運行和驗證

前面已經分別用自定義外設和自定義指令的方式實現了CRC32。那么自定義外設和自定義指令執行性能如何?在實現相同功能的情況下,何種方式在執行過程中更有優勢?它們之間的差異有多大?在這一部分將通過測試給予充足的驗證。

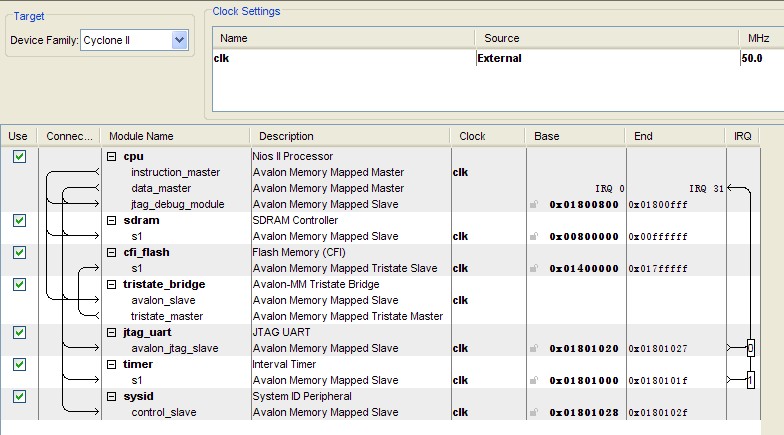

3.1? 驗證平臺的硬件系統

采用以CycloneII系列EP2C35為核心芯片的SOPC開發系統,來搭建實驗所需要的硬件平臺。在這個硬件平臺中,需要添加系統工作需要的外設,包括NiosII CPU、Timer、Avalon三態橋,外部RAM接口和Flash等。在該硬件系統中,首先要加入自己定制的外設邏輯,同時在NiosII CPU中加入開發的自定義指令。在同一系統中同時加入實現相同功能的自定義外設和自定義指令是為了得到對比結果。系統時鐘設置在50 MHz。在本設計中,有大量的數據從SSRAM傳輸到CRC處理模塊中,這些數據在傳輸過程中不需要進行算術邏輯運算,如果通過CPU來操作,會消耗大量的CPU時間。為了提高CPU的工作效率,采用DMA(直接存儲器訪問)來完成。利用DMA控制器方式,在CRC自定義外設和SSRAM存儲器之間建立一條DMA傳輸通道,讓硬件自動讀取數據信息。在DMA傳輸過程中,首先通過中斷由CPU對DMA進行初始化設置,打開DMA傳輸通道,使DMA在沒有CPU干預的情況下進行傳輸。然后DMA直接將SSRAM存儲器中的數據傳輸到CRC處理模塊中,直到數據傳輸完成。所添加的DMA通道,讀端口通過Avalon三態橋連接到了SSRAM,寫端口連接到了自定義外設CRC,如圖3所示。

特別注意的是,在該硬件平臺中,要加入一個時間標記服務定時器high_res_timer(也就是經常說的“時間戳”)。該服務可以幫助設計人員查找出耗時最長的功能函數,定位優化目標,檢測某個功能部件的運行情況。在這里,主要是利用該“時間戳”來測量CRC32不同方式的執行時間,為分析各種方式的性能差異奠定基礎。

3.2? 軟件開發

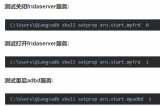

在NiosII IDE開發環境中,分別使用自定義外設、自定義指令和軟件的方式來實現CRC32。

①? 軟件實現方式:數據的讀取、處理、保存等全部由軟件來實現。

②? 用戶自定義指令方式:處理過程使用CRC32自定義指令來完成。

③? 用戶自定義外設方式:使用DMA通道完成數據的讀取、保存,NiosII處理器控制外設完成CRC32的處理。

完成上面的工作后,編譯工程,下載到SOPC開發板中。從NiosII控制臺中,可以看到如下輸出信息,如圖4所示。

4? 性能對比和分析

在NiosII IDE上面可以觀察到用軟件、自定義指令、自定義外設實現CRC32的各種情況。這幾種方式的運行結果是相同的,但用軟件實現的時間是12 381.33 ms,采用優化的軟件設計時間是8 393.02 ms,采用自定義指令的時間是164.69 ms,而采用自定義外部設備時則用了12.08 ms。從結果可以分析出,純用軟件來執行,運行速度最低;如果把標準指令序列實現的核心功能由一條用戶自定義指令來實現,可以明顯提高系統的執行效率;如果采用自定義外設,即將軟件實現的功能全部由硬件來實現,則速度又大大提高。從圖5中可以更清楚地看到這種對比: 從左到右依次是軟件方式、改進軟件方式、自定義指令方式、自定義外設方式。由此可知,自定義外設執行效率最高,其次是自定義指令。

從實現機理上來講,自定義外設可以看作是和NiosII并行運行的一個硬件加速邏輯,中間CPU參與過程很少,這就為系統“全面加速”提供了堅實的基礎;而自定義指令由于硬件邏輯連接到NiosII處理器的算術邏輯單元上,只能實現“局部”加速。從實現結果來說,實現同樣的功能,自定義外設的執行效率是自定義指令的十幾倍以上;而隨著系統頻率的升高,這個差距會越來越大。如果系統在120 MHz,差距會在50倍左右。

結語

本文對SOPC系統中自定義外設和自定義指令的性能進行了詳細對比,并且給出了對比的詳細參數。在SOPC系統中,如果實時性要求非常高,那么采取自定義外設加DMA來完成系統中的關鍵處理模塊無疑是最佳選擇。

電子發燒友App

電子發燒友App

評論