我們生活在一個信息高速發達的時代,各種各樣電子產品層出不窮。對于廣大老百姓來說,電子琴可以說已經不再是什么“新鮮玩意”了,它現在作為一種休閑和娛樂的產品早就推出市面,面向百姓,進入了我們的生活。作為一個電子信息科學與技術專業的學生,了解這些電子產品的基本的組成和設計原理是十分必要的,我們學習過了計算機組成的理論知識,而我所做的課程設計正是對我學習的理論進行實踐和鞏固。

電子琴作為音樂與科技的產物,在電子化和信息化的時代,為音樂的大眾化做出了很大的貢獻,歌曲的制作大多數都要由電子琴來完成,然后通過媒介流傳開來,電視劇和電影的插曲、電視節目音效、甚至你的手機鈴聲,都很可能包含電子琴的身影。

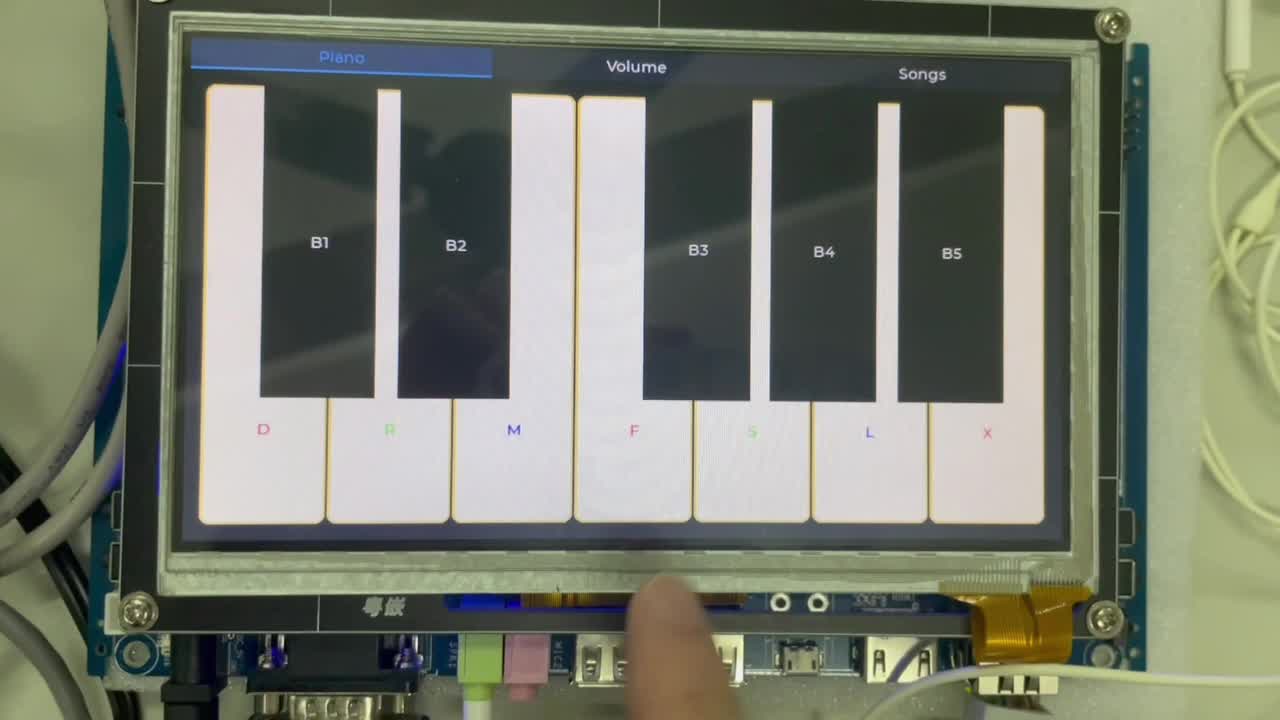

電子琴因其操作簡單, 且能模擬各種傳統樂器的音色, 而深受消費者喜愛。筆者介紹了一種電子琴的設計方法。該系統基于可編程邏輯器件 FPGA( FieldProgrammable Logical Device) 芯片 , 利用 VHDL 硬件描述語言設計系統核心部件, 再配以適當的外圍電路,可從琴鍵上進行演奏也可自動進行樂曲演奏, 可模擬傳統樂器笛、風琴、小號、單簧、基準頻率產生器雙簧等音色。該電子琴共有12 個琴鍵 ( 7 個白色琴鍵 , 5個黑色琴鍵) , 分高音、中音、低音 3 個音區, 演奏時音名可動態顯示。

原理分析

樂曲都是由一連串的音符組成,按照樂曲的樂譜依次輸出這些音符所對應的頻率,就可以在揚聲器上連續地發出各個音符的音調。為了準確地演奏出一首樂曲,僅僅讓揚聲器能夠發出聲音是遠遠不夠的,還必須準確地控制樂曲的節奏,即每個音符的持續時間。由此可見,樂曲中每個音符的發音頻率以及音符持續的時間是樂曲能夠連續演奏的兩個關鍵因素。

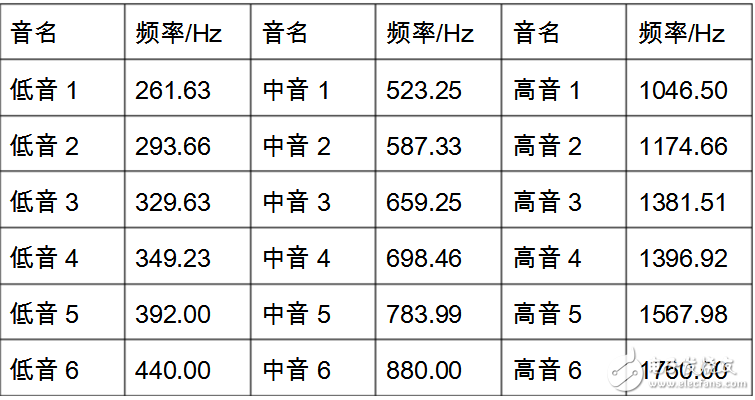

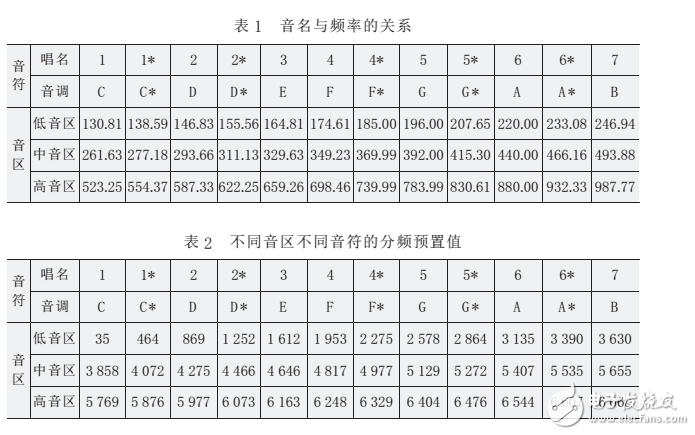

樂曲的12平均率規定:每2個八度音之間的頻率要相差1倍,比如簡譜中的中音2與高音2。在2個八度音之間,又可分為12個半音。另外,音符A(簡譜中的低音5)的頻率為392Hz,音符E到F之間、B到C之間為半音,其余為全音。由此可以計算出簡譜中從低音l至高音1之間每個音符的頻率。簡譜音名與頻率對應關系下圖2-1所示:

1 系統組成

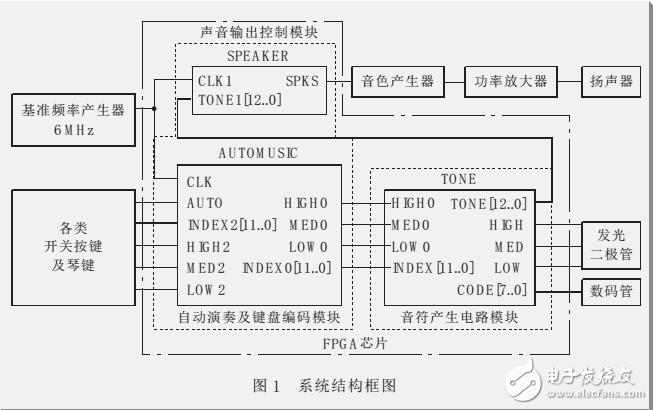

該電子琴系統組成框圖如圖 1 所示。

2 系統各部分電路設計

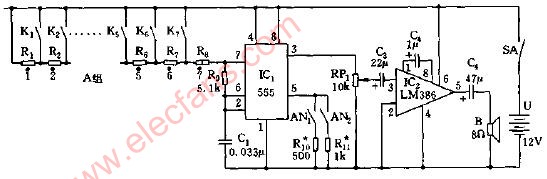

2.1 基準頻率產生器

電路由晶振與反相器 CC4069 構成時鐘脈沖振蕩器。振蕩器輸出的頻率為 6 MHz, 作為系統的基準頻率。

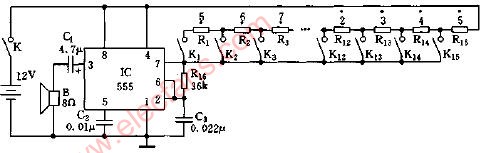

自動演奏及鍵盤編碼模塊( AUTOMUSIC 模塊)

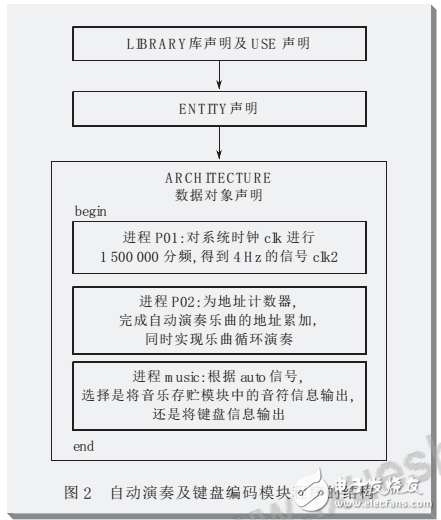

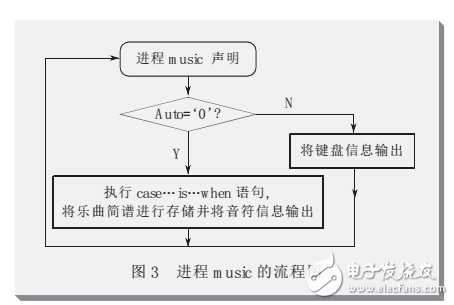

該模塊主要包括兩大內容: 鍵盤輸入編碼及樂曲自動演奏。其 VHDL 程序的結構如圖 2 所示, 包括 3 個進 程 : p01:process ( clk, Auto) 進程完成對系統時鐘 6 MHz 的 1 500 000 分頻, 得到 4 Hz 的信號 clk2, 作為另一進程的計數時鐘, 用來控制每個音階之間的停頓時間; p02: process( clk2) 進程為地址計數器, 計數范圍為0~音樂存貯模塊中音符的最大地址數。完成自動演奏樂曲的地址累加, 同時實現樂曲循環演奏; music: pro-cess ( count0, Auto, index2) 進程主要用來記錄所選樂曲的樂譜、根據樂譜產生 12 位發聲控制輸出 index0 信號。當 auto 為“0”時, 將存儲在此模塊中的 12位二進制數作為發聲控制信號 , 自動演奏樂曲。在記錄樂譜時 , 若將 1 拍的時間長度定為1 s, 因地址計數器的時鐘頻率為 4 Hz, 即 1/4 拍時間為 0.25 s,則 1 個全音音符需重復記錄 4次 , 2/4 拍音符重復記錄 2 次, 該進程的流程圖如圖 3所示。

該模塊程序中 clk 接基準頻率產生器, 輸入系統的基準頻率 6 MHz; auto 為鍵盤輸入演奏與自動演奏的切換開關, 即當 auto=“0”時, 選擇音樂存儲器里的樂曲 , 自動演奏 ; auto=“1”時 , 選擇鍵盤輸入的信號 , 從琴鍵上演奏。high2, med2, low2 分別接鍵盤上高、中、低音的控制開關 , Index2[0]~Index2[11]分別接鍵盤上的12 個琴鍵, HIGH0, med0, low0 分別輸出音調的音區信息( 分別對應高音、中音、低音區) ; Index0[0]~Index0[11]輸出琴鍵編碼或音樂存儲器里的樂曲的音符編碼。

2.3 音符產生電路模塊( Tone 模塊)

該模塊的作用是產生各音符的分頻預置值。根據各音名與頻率的關系( 如表 1) 以及聲音輸出控制模塊( speaker 模塊) 中數控分頻器的設計, 分別計算出高音區、中音區、低音區不同音符的分頻預置值, 如表 2 所示。( 在表 1、表 2 中, 音符 1、2、3、4、5、6、7 對應電子琴的 7 個白色琴鍵, 音符 1*、2*、4*、5*、6* 對應電子琴的 5個黑色琴鍵。) 程序中 Index 為 AUTOMUSIC 模塊傳入的音符編碼, high0, med0, low0 為 AUTOMUSIC 模塊傳入表示音符所處音區, 如 high0=‘1’表示音符處于高音區 ; low0=‘1’表 示音符處于低音區 ; 程序中 Tone 為輸出音符分頻預置值, 因最大的預置數為 6 668, 為節省硬件資源及提高系統運行速度, 將 Tone 取值范圍定為0~16#1E00#; HIGH, med, low 輸出音符所處音區, 接外電路的發光二極管 , 高電平有效 ; CODE 端口接數碼管, 輸出音符的顯示數碼。該模塊 VHDL 程序的結構如圖 4 所示, 程序主要部分 se 進程流程圖如圖 5 所示。

2.4 聲音輸出控制模塊( speaker 模塊)

該模塊主要電路為數控分頻器。其 VHDL 程序結構如圖 6 所示。程序中 CLK1 輸入系統的基準頻率 6 MHz, TONE1 接 Tone 模塊傳來的分頻預置值, SPKS 輸出端接音色產生器, 輸出各音符所對應的頻率。該程序包括 3 個進程 , 其中 DivideCLK : PROCESS( clk1) 進程功能將系統的基準頻率 6 MHz 進行 3 分頻得到 2 MHz 的頻率, 由信號 PreCLK 傳給 GenSpkS:PROCESS( PreCLK, Tone1) 進程。在設計中 PreCLK 頻率太大,會使在 GenSpkS 進程分頻中占用太多的硬件資源 ,PreCLK 頻率太小 GenSpkS 進程分頻后輸出音符頻率誤差太大, 綜合考慮這兩個方面, PreCLK 選用 2 MHz的頻率。GenSpkS 進程由一個初值可變的加法計數器構成, 初值為 Tone 模塊傳來的分頻預置值( Tone1) 。分頻后得到的頻率 FullSpkS 為對應的音符頻率的 2 倍。由于 FullSpkS 頻率的脈寬很窄, 為便于驅動揚聲器, 將FullSpkS 信 號 傳 給 進 程 DelaySpkS:PROCESS ( Full-SpkS) , 在此進程中利用一個 D 觸發器將 FullSpkS 信號進行二分頻, 使到達揚聲器的波形為對稱方波, 此時輸出的頻率即達到所對應音符的實際頻率。

2.4 在 FPGA 芯片中頂層文件的原理圖該原理圖

如圖 7 所示。輸入端 CLK1, CLK 接系統的基準頻率 6 MHz, AUTO 接鍵盤輸入演奏與自動演奏的切換開關 , 總線 INDEX2[11..0]接鍵盤上的 12 個琴鍵, HIGH2, MED2, LOW2 分別接鍵盤上高、中、低音的控制開關; 輸出端 HIGH, MED, LOW 分別接發光二極管, 指示音調的音區信息( 分別對應高音、中音、低音區) , CODE[7..0]接 LED 數碼管, 輸出音符的顯示數碼,SPKS 輸出端接音色產生器,輸出各音符所對應的頻率。

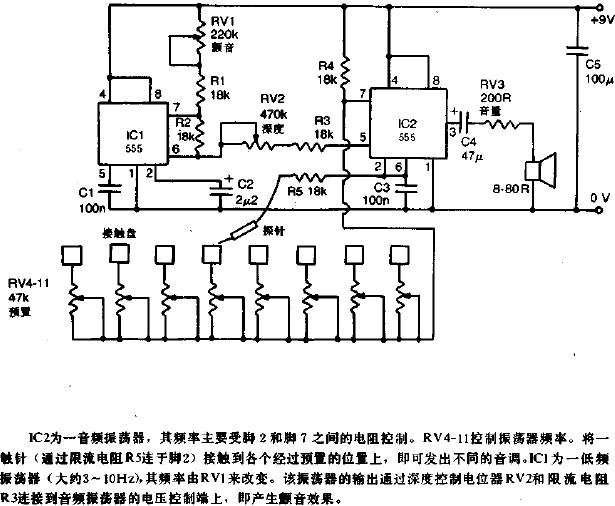

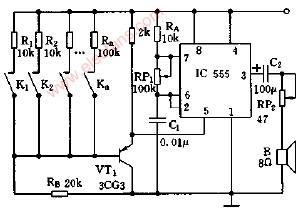

2.6 音色產生器

音色指樂音的音域范圍、頻譜成分及其包絡特性等。音色產生器的功能是模擬各種傳統樂器如笛子、小 號、雙簧、風琴等的樂音。這些樂音的區別表現在發同風琴一音符時, 波形的頻譜與包絡特性不同。由此設計的一種簡單音色產生電路如圖 8 所示。其中, 74LS93 的輸入脈沖 CLK0 來自 FPGA 芯片的音符頻率輸出端 spks; 74LS93 的輸出端 Q0~Q3 為音符頻率 spks 的 2,4, 8 及 16 分頻信號。電阻 R1~R10 組成權電阻相加網絡, 可產生由不同頻率成分與不同幅度組成的各種波形。適當選擇 R1~R10 的阻值或一定比值( 與樂器標準音比較后定) , 可獲得如圖 8 所示的笛子、小號、雙簧、風琴等的基本樂音。再經 RC 濾波輸出, 以改善音色。

該設計將電子琴系統的核心部分集成在可編程邏輯器件FPGA 芯片上, 大大簡化了外部電路, 較以前的傳統設計, 既減少了所用芯片的種類和數量 ,縮小了體積, 降低了功耗, 提高了系統的整體性能,對系統在使用中的故障率大為減少。此外, 這種基于可編程邏輯器件以 VHDL 硬件描述語言進行設計, 在電子設計的各個階段、各個層次進行計算機模擬驗證, 保證設計過程的正確性, 可降低設計成本 , 縮短設計周期, 具有廣闊的應用前景。

電子發燒友App

電子發燒友App

評論