1、CORDIC 理論

1.1、 坐標(biāo)旋轉(zhuǎn)數(shù)字計(jì)算機(jī)CORDIC

坐標(biāo)旋轉(zhuǎn)數(shù)字計(jì)算機(jī)CORDIC(COordinate Rotation DIgital Computer)算法,通過移位和加減運(yùn)算,能遞歸計(jì)算常用函數(shù)值

2010-07-28 17:57:22 1661

1661 仿真波形表明,計(jì)算結(jié)果與MATLAB浮點(diǎn)運(yùn)算相近,滿足一般計(jì)算需求。若想提高精度,可以增加CORDIC輸出數(shù)據(jù)位寬。

2020-12-25 14:02:12 5952

5952

請問CORDIC算法用verilog算法實(shí)現(xiàn)時(shí),角度累加器中的45度,26.56度,14.04度怎么跟verilog語言相對應(yīng)?

2015-07-11 20:18:57

CORDIC(Coordinate Rotation Digital Computer)算法即坐標(biāo)旋轉(zhuǎn)數(shù)字計(jì)算方法,是 J.D.Volder1于 1959 年首次提出,主要用于三角函數(shù)、雙曲線、指數(shù)

2023-08-09 06:45:44

本文重點(diǎn)介紹:1、各種處理器的特點(diǎn):簡要對比各種處理器的特點(diǎn)2、圖片處理算法的特點(diǎn):介紹圖片處理算法的特點(diǎn)3、FPGA加速性能的主要因素:分析FPGA能夠加速圖片處理的原因4、HEVC算法之FPGA

2018-08-01 09:55:53

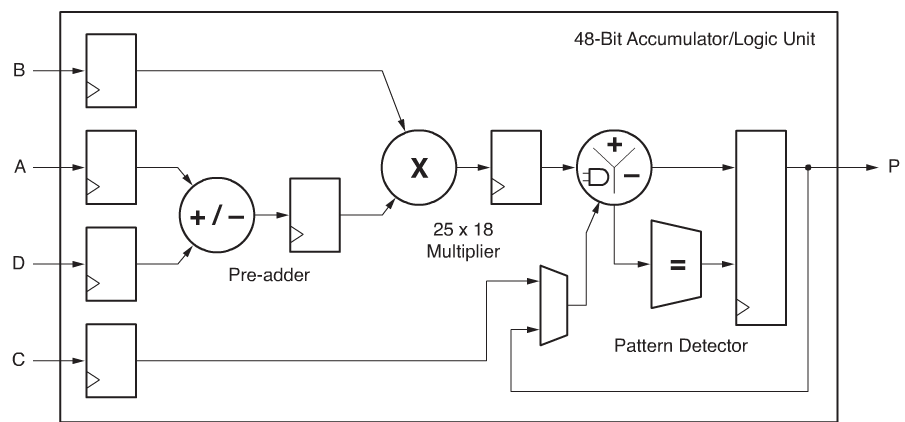

計(jì)算機(jī)時(shí)發(fā)明的。這是一種設(shè)計(jì)用于計(jì)算數(shù)學(xué)函數(shù)、三角函數(shù)和雙曲函數(shù)的簡單算法。這種算法的真正優(yōu)勢在于只需要采用極小型的 FPGA封裝就可以實(shí)現(xiàn)它。CORDIC 只需要一個(gè)小型查找表,加上用于執(zhí)行移位和加

2019-09-19 09:07:16

算法是程序的靈魂,本資料詳細(xì)介紹了數(shù)學(xué)建模當(dāng)中的主要幾個(gè)算法的應(yīng)用分析,希望對大家在編程解決其他問題的時(shí)候有所幫助

2016-11-11 09:40:25

ARM/DSP/FPGA的區(qū)別是什么?對比分析哪個(gè)好?

2021-11-05 06:08:20

CPLD與FPGA對比分析哪個(gè)好?

2021-06-21 06:10:12

CPLD與FPGA的對比分析哪個(gè)好?

2021-11-05 08:20:40

DSP、MCU、ARM、CPLD/FPGA對比分析哪個(gè)好?

2021-10-22 07:17:10

Fourier Transform,DFT)是信號分析與處理中的一種重要變換。因直接計(jì)算DFT的計(jì)算量與變換區(qū)間長度N的平方成正比,當(dāng)N較大時(shí),計(jì)算量太大,所以在快速傅里葉變換(FFT)出現(xiàn)以前,直接用DFT算法進(jìn)行譜分析和信號的實(shí)時(shí)處理是不切實(shí)際的。1965年由全文下載

2010-05-28 13:38:38

本文深入討論了GraphSAGEGNN算法的數(shù)學(xué)原理,并從多個(gè)維度分析了GNN加速器設(shè)計(jì)中的技術(shù)挑戰(zhàn)。

2021-06-17 08:56:40

LCR-TDD系統(tǒng)初始頻偏估計(jì)算法對比分析哪個(gè)好?

2021-06-02 06:14:26

使用LabVIEW FPGA模塊中的CORDIC IP核,配置arctan(X/Y)算法,配置完成之后,IP核只有一個(gè)輸入。我參考網(wǎng)上VHDL CORDIC IP核,說是將XY合并了,高位X低位Y。不知道在LabVIEW中如何將兩個(gè)值X、Y合并成一個(gè)(X、Y均為定點(diǎn)數(shù))。具體情況如下圖:

2019-09-10 20:07:07

跟大家分享下MATLAB數(shù)學(xué)建模算法及實(shí)例分析

2014-03-06 23:06:16

工程計(jì)算、數(shù)學(xué)建模、計(jì)算機(jī)模擬、算法研究、數(shù)據(jù)分析與處理、科學(xué)與工程繪圖、應(yīng)用軟件開發(fā)、數(shù)值計(jì)算、圖形、圖像處理,支持遞歸函數(shù),還有多種工具箱(不同領(lǐng)域)。

2023-09-22 08:19:42

小弟最近在做信號發(fā)生器,網(wǎng)上查看了一下,使用cordic算法也可以在一定精度范圍內(nèi)實(shí)現(xiàn)sin函數(shù)的計(jì)算,DDS技術(shù)是通過查表的方式提取事先準(zhǔn)備好的波形文件(或者其他格式),求大神幫忙分析一下這兩者。

2015-11-11 16:38:42

的實(shí)踐經(jīng)驗(yàn);有模式識別和圖像處理算法設(shè)計(jì)、算法分析的能力。 3、具備扎實(shí)的線性代數(shù)、概率論與數(shù)理統(tǒng)計(jì),矩陣論等數(shù)學(xué)基礎(chǔ)。 4、主動(dòng)性強(qiáng),思維活躍,有創(chuàng)新意識,能夠承受工作上的壓力。 5、動(dòng)手能力強(qiáng),具有快速

2013-01-23 09:02:20

收機(jī)擴(kuò)頻碼的捕獲以及數(shù)據(jù)解調(diào)性能的影響,從而提高接收機(jī)的性能。頻偏校正電路中通常需要根據(jù)給定相位產(chǎn)生余弦信號和正弦信號,其中最重要的實(shí)現(xiàn)技術(shù)是CORDIC(CoordinateRotationDigitalComputer,坐標(biāo)旋轉(zhuǎn)數(shù)字計(jì)算機(jī))算法。

2019-09-19 07:17:19

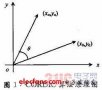

最近出于項(xiàng)目需要,對CORDIC算法深入學(xué)習(xí)下。剛開始的時(shí)候上網(wǎng)搜了下資料發(fā)現(xiàn)一上來就直接是推導(dǎo)公式,然后工程運(yùn)用與理論推導(dǎo)聯(lián)系太少感覺無從下手!對于像我們數(shù)學(xué)丟了很多年的同學(xué)來說實(shí)在是痛苦啊。好在

2014-08-11 14:05:05

卡爾曼濾波算法對比其他的濾波算法有什么優(yōu)點(diǎn)

2023-10-11 06:42:24

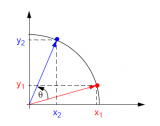

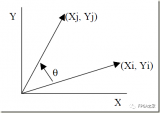

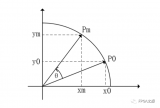

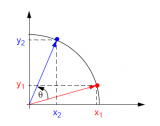

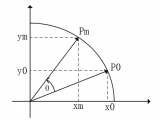

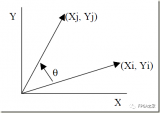

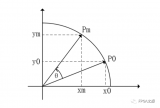

三角函數(shù)和雙曲線函數(shù)的低成本逐次逼近算法。最初由Jack Volder在1959年提出,它被廣泛用于早期計(jì)算器當(dāng)中。CORDIC算法通過基本的加和移位運(yùn)算代替乘法運(yùn)算,具體原理不在此贅述。坐標(biāo)旋轉(zhuǎn)算法示意圖

2022-08-10 14:38:16

。我們提出了一種基于CORDIC(坐標(biāo)旋轉(zhuǎn)數(shù)字計(jì)算機(jī))技術(shù)的無開方無除法的MQR陣分解方法,并應(yīng)用于自適應(yīng)陣抗干擾處理,取得了良好的效果。CORDIC算法最初由Volder提出,最早用于三角函數(shù)的計(jì)算

2020-11-23 09:15:32

基于Cordic的正弦信號發(fā)生器建模仿真(1)信號頻率范圍10Hz—200KHz;(2)給出Cordic算法信號發(fā)生器;(3)可以隨時(shí)改變頻率控制字或相位控制字。

2015-07-03 12:40:17

c/4]范圍內(nèi)時(shí),可以采用 FPGA 的 IP CORE(CORDIC 算法)實(shí)現(xiàn)雙曲正弦函數(shù)和雙曲余弦函數(shù),因此在 FPGA 內(nèi)部求以 2 為底的指數(shù)函數(shù)時(shí),可以先將自變量歸一化在[0,1]內(nèi),然后將自

2020-08-14 09:06:10

亮度分布特性有力的工具,根據(jù)它的結(jié)果可以進(jìn)行諸如灰度拉伸、自動(dòng)對比度、動(dòng)態(tài)伽馬調(diào)整等操作。圖1 Lena 圖像的灰度直方圖統(tǒng)計(jì)FPGA算法統(tǒng)計(jì)在計(jì)算機(jī)或者DSP 上實(shí)現(xiàn)直方圖統(tǒng)計(jì)時(shí),我們通常會使用數(shù)組

2012-05-14 12:37:37

HDL硬件描述語言對優(yōu)化前后的算法進(jìn)行了編碼實(shí)現(xiàn)。仿真和實(shí)驗(yàn)結(jié)果表明,優(yōu)化后的數(shù)字三相鎖相環(huán)大大節(jié)省了FPGA的資源,并能快速、準(zhǔn)確地鎖定相位,具有良好的性能。關(guān)鍵詞:FPGA;三相鎖相環(huán);乘法復(fù)用;CORDIC

2019-06-27 07:02:23

大家好,這是一個(gè)UDP實(shí)現(xiàn)的16位定點(diǎn)CORDIC,用于計(jì)算給定角度的正弦和余弦。它在PSoC 3上被支持,并且可能(忽略警告)運(yùn)行到33 MHz。我已經(jīng)附上了一個(gè)演示項(xiàng)目與項(xiàng)目庫,所以嘗試運(yùn)行它在

2019-05-24 10:03:12

的性能。但傳統(tǒng)CORDIC算法中每次CORDIC迭代方向需由剩余角度的計(jì)算來確定,影響了工作速度。為此,本文根據(jù)定點(diǎn)FFT復(fù)乘中旋轉(zhuǎn)因子的旋轉(zhuǎn)方向可預(yù)先確定的特點(diǎn),對CORDIC算法做了一些改進(jìn),在節(jié)省

2011-07-11 21:32:29

在《算法電路的合成:FPGA,ASIC和嵌入式系統(tǒng)》中,作者采用了一種新穎的方法來呈現(xiàn)用于合成算法電路的方法和示例,以更好地反映當(dāng)今計(jì)算機(jī)系統(tǒng)設(shè)計(jì)者和工程師的需要。不像其他出版物,將討論限制

2018-12-20 16:14:53

有關(guān)數(shù)學(xué)運(yùn)算快速算法的論文。

2016-04-14 09:34:59

嗨,我已經(jīng)實(shí)現(xiàn)了radix2 / 4&在ISE 14.1中沒有使用cordic的分裂基數(shù)FFT算法。它們運(yùn)行良好... o / p即將到來,但問題是代碼是不可合成的。為了使代碼可合成,我必須

2020-03-06 08:40:29

本文利用CORDIC算法在FPGA上實(shí)現(xiàn)了高速自然對數(shù)變換器。

2021-04-30 06:05:22

大多選用這種算法。硬件實(shí)現(xiàn)上,最初是采用單片DSP芯片實(shí)現(xiàn),其原理為:圖像數(shù)據(jù)實(shí)時(shí)的傳輸給DSP,DSP接收完1塊數(shù)據(jù)后,再對整塊數(shù)據(jù)進(jìn)行增強(qiáng)處理,這樣勢必會造成時(shí)間的延遲,不能滿足精確制導(dǎo)武器系統(tǒng)實(shí)時(shí)性的要求。后來硬件結(jié)構(gòu)發(fā)展為采取DSP,FPGA芯片相結(jié)合的方式。

2019-08-16 07:10:22

電力系統(tǒng)故障分析的計(jì)算機(jī)算法李長松Spring 2017回顧:電力系統(tǒng)計(jì)算機(jī)輔助分析步驟:靜穩(wěn)計(jì)算確定工程問題? 確定系統(tǒng)受到小擾動(dòng)下的穩(wěn)定恢復(fù)能力? 發(fā)電機(jī)組和負(fù)荷的模型建立數(shù)學(xué)模型 ? 電力網(wǎng)絡(luò)的模型? 線性化小擾動(dòng)方程? 直接計(jì)算特征根法尋找求解算法...

2021-09-10 06:52:51

監(jiān)控圖象傳輸方式對比分析

2012-08-20 12:53:09

正在做一個(gè)課題,用FPGA控制AD9910,但是本人想把基于ROM表的改成基于CORDIC算法的,這樣還能不能用FPGA實(shí)現(xiàn)控制AD9910,理論上應(yīng)該可以的,但是不知道這樣有沒有意義一般都是直接用

2018-12-01 08:47:01

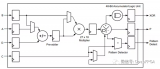

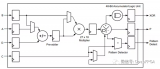

就已經(jīng)出現(xiàn),隨著FPGA芯片價(jià)格的不斷降低,其在工業(yè)領(lǐng)域的應(yīng)用正在飛速發(fā)展,采用FPGA來實(shí)現(xiàn)SVPWM調(diào)制算法也將層出不窮2. 系統(tǒng)任務(wù)分析及實(shí)現(xiàn)SVPWM調(diào)制算法相對比較復(fù)雜,在完成系統(tǒng)控制任務(wù)

2022-01-20 09:34:26

數(shù)學(xué)建模與數(shù)學(xué)實(shí)驗(yàn)-回歸分析1、直觀了解回歸分析基本內(nèi)容。2、掌握用數(shù)學(xué)軟件求解回歸分析問題。1、回歸分析的基本理論。2、用數(shù)學(xué)軟件求解回歸分析問題。3、實(shí)

2008-12-03 10:05:43 0

0 分析了CORDIC算法的基本原理和MVR-CODIC算法的特點(diǎn)。在此基礎(chǔ)上,提出了一種改進(jìn)型MVR-CODIC算法,利用查ROM表代替原算法中比例因子的計(jì)算方法,討論了改進(jìn)后算法的所需ROM表的容

2009-03-04 22:26:26 28

28 針對在工業(yè)中越來越多的使用到的FFT,本文設(shè)計(jì)出了一種利用CORDIC 算法在FPGA 上實(shí)現(xiàn)快速FFT 的方法。CORDIC 實(shí)現(xiàn)復(fù)數(shù)乘法比普通的計(jì)算器有結(jié)構(gòu)上的優(yōu)勢,并且采用了循環(huán)結(jié)構(gòu)

2009-08-24 09:31:10 9

9 組合數(shù)學(xué)的算法與程序設(shè)計(jì)用計(jì)算機(jī)編程解題的核心問題是算法,而組合數(shù)學(xué)是算法的主要內(nèi)容。組合數(shù)學(xué)對于參加信息學(xué)奧林匹克活動(dòng)的青少年而言,是一門提高思維能力、分析與判

2009-10-24 12:32:53 67

67 CORDIC 算法在通信和圖像處理等各個(gè)領(lǐng)域有著廣泛的應(yīng)用,但是浮點(diǎn)CORDIC 由于迭代延時(shí)大且實(shí)現(xiàn)復(fù)雜沒有得到很好的應(yīng)用,本文提出了一種修正浮點(diǎn)CORDIC 算法: 高精度順序迭代HPOR

2009-12-15 14:27:24 14

14 基于CORDIC 算法的NCO 實(shí)現(xiàn)田力, 馮琦(西安電子科技大學(xué) 電路設(shè)計(jì)研究所,陜西 西安 710071)摘要:NCO 在信號處理方面有著廣泛的應(yīng)用。而函數(shù)發(fā)生器是NCO 中的關(guān)鍵部分,

2009-12-15 14:30:33 23

23 采用按時(shí)間抽選的基4原位算法和坐標(biāo)旋轉(zhuǎn)數(shù)字式計(jì)算機(jī)(CORDIC)算法實(shí)現(xiàn)了一個(gè)FFT實(shí)時(shí)譜分析系統(tǒng)。整個(gè)設(shè)計(jì)采用流水線工作方式,保證了系統(tǒng)的速度,避免了瓶頸的出現(xiàn);整個(gè)系統(tǒng)

2010-06-25 17:58:59 23

23 針對在工業(yè)中越來越多的使用到的FFT,本文設(shè)計(jì)出了一種利用CORDIC算法在FPGA上實(shí)現(xiàn)快速FFT的方法。CORDIC實(shí)現(xiàn)復(fù)數(shù)乘法比普通的計(jì)算器有結(jié)構(gòu)上的優(yōu)勢,并且采用了循環(huán)結(jié)構(gòu)的CORDIC算

2010-08-09 15:39:20 55

55 CORDIC算法是用于計(jì)算三角、反三角、指數(shù)、對數(shù)等超越函數(shù)的簡捷算法。將該算法應(yīng)用在以單片機(jī)為核心的三軸電子羅盤中,用于實(shí)現(xiàn)羅盤的傾斜補(bǔ)償并計(jì)算俯仰角、橫滾角和航向

2010-10-18 16:52:57 0

0 研究了一種利用CORDIC算法的矢量及旋轉(zhuǎn)模式對載波同步中相位偏移進(jìn)行估計(jì)并校正的方法。設(shè)計(jì)并實(shí)現(xiàn)了基于CORDIC算法的數(shù)字鎖相環(huán)。通過仿真,驗(yàn)證了設(shè)計(jì)的有效性和高效性。

2010-12-15 14:49:43 0

0 本文提出了應(yīng)用CORDIC(Coordinate Rotation Digital Computer)算法實(shí)時(shí)計(jì)算正弦值的方案,并基于CORDIC算法在FPGA芯片上設(shè)計(jì)了2FSK調(diào)制器。這不僅能夠節(jié)省大量的FPGA邏輯資源,而且能很好地兼顧速度

2011-05-31 10:22:06 1508

1508

CORDIC算法將復(fù)雜的算術(shù)運(yùn)算轉(zhuǎn)化為簡單的加法和移位操作,然后逐次逼近結(jié)果。這種方法很好的兼顧了精度、速度和硬件復(fù)雜度,它與VLSI技術(shù)的結(jié)合對DSP算法的硬件實(shí)現(xiàn)具有極大的意義

2011-06-27 17:27:26 66

66 在研究CORDIC算法的數(shù)學(xué)基礎(chǔ)上,采用流水線的硬件結(jié)構(gòu)實(shí)現(xiàn)了該算法,并在Altera公司的FPGA芯片上進(jìn)行了驗(yàn)證,使正余弦函數(shù)的計(jì)算達(dá)到了實(shí)時(shí)性、高精度的要求。

2011-12-16 14:30:00 33

33 摘要: 傳統(tǒng)的基于查表法的數(shù)控振蕩器耗費(fèi)大量的FPGA片內(nèi)資源。為了解決這一問題,提出了一種基于CORDIC(coordinate rotation digital compute,坐標(biāo)旋轉(zhuǎn)數(shù)值計(jì)算)算法的數(shù)控振蕩器的設(shè)計(jì)方

2012-05-28 16:04:59 39

39 摘要: 傳統(tǒng)的基于查表法的數(shù)控振蕩器耗費(fèi)大量的FPGA片內(nèi)資源。為了解決這一問題,提出了一種基于CORDIC(coordinate rotation digital compute,坐標(biāo)旋轉(zhuǎn)數(shù)值計(jì)算)算法的數(shù)控振蕩器的設(shè)計(jì)方

2012-05-29 16:46:34 0

0 為了滿足現(xiàn)代高速通信中頻率快速轉(zhuǎn)換的需求,基于坐標(biāo)旋轉(zhuǎn)數(shù)字計(jì)算(CORDIC,Coordinate Rotation Digital Computer)算法完成正交直接數(shù)字頻率合成(ODDFS,Orthogonal Direct Digital Frequency Synthes

2013-02-22 16:26:46 34

34 MATLAB數(shù)學(xué)建模算法及實(shí)例分析,了解MATLAB

2016-01-22 14:06:50 0

0 遺傳算法的數(shù)學(xué)基礎(chǔ),有需要的可以下來看看

2016-07-20 16:51:51 12

12 論文闡述了CORDIC 算法的基本原理,在旋變解碼、坐標(biāo)變換、SVPWM、輸出限幅等算法中的應(yīng)用,并給出了實(shí)現(xiàn)方法及運(yùn)算值與實(shí)際值的對比,證明了CORDIC 算法具有運(yùn)算精度高,占用資源少,運(yùn)算速度快等特點(diǎn)。最后通過一臺額定9kW 的電動(dòng)車用永磁同步電機(jī)實(shí)驗(yàn)驗(yàn)證了算法的正確性和實(shí)用性。

2016-08-03 18:36:25 25

25 cordic算法verilog實(shí)現(xiàn)(簡單版)(轉(zhuǎn)載)module cordic(clk, phi, cos, sin); parameter W = 13, W_Z = 14; input clk; input [W_Z-1:0] phi; output[W-1:0]

2017-02-11 03:06:11 3044

3044

module cordic (clk,rst_n,ena,phase_in,sin_out,cos_out,eps); parameter DATA_WIDTH=8; parameter PIPELINE=8;

2017-02-11 03:07:08 3962

3962

以ISE10.1軟件為例,其集成的CORDIC算法IP為V3.0版本,具體步驟如下:

2017-02-11 11:16:49 2627

2627

CORDIC是在沒有專用乘法器(最小化門數(shù)量)情況下,一組完成特定功能的算法,包括平方、超越、Log、sin/cos/artan。原理為連續(xù)的旋轉(zhuǎn)一個(gè)較小的角度,以一定精度逼近想要的角度。

2017-02-11 19:24:06 5373

5373 陣列信號處理技術(shù)在遠(yuǎn)場信號DOA的估計(jì)方面的研究成為熱點(diǎn)。本文就四種經(jīng)典的DOA估計(jì)算法:MUSIC算法、ESPRIT算法、TLS-ESPRIT算法和Toeplitz矩陣重構(gòu)算法進(jìn)行對比研究,目的

2017-11-06 11:23:20 11

11 。 在1 月 20 日,騰訊云推出國內(nèi)首款高性能異構(gòu)計(jì)算基礎(chǔ)設(shè)施——FPGA 云服務(wù)器,將以云服務(wù)方式將大型公司才能長期支付使用的 FPGA 普及到更多企業(yè),企業(yè)只需支付相當(dāng)于通用CPU約40%的費(fèi)用,性能可提升至通用CPU服務(wù)器的30倍以上。

2017-11-15 20:20:08 2468

2468 針對傳統(tǒng)CORDIC算法流水線結(jié)構(gòu)的迭代次數(shù)過多,運(yùn)算速度不夠快,消耗硬件資源較多的缺點(diǎn),改進(jìn)了一種基于旋轉(zhuǎn)模式并行運(yùn)算的CORDIC算法。該算法采用二進(jìn)制兩極編碼和微旋轉(zhuǎn)角編碼進(jìn)行低位符號預(yù)測

2017-11-16 10:46:22 14

14 減運(yùn)算,就能計(jì)算常用三角函數(shù)值,如Sin,Cos,Sinh,Cosh等函數(shù)。 J. Walther在1974年在這種算法的基礎(chǔ)上進(jìn)一步改進(jìn),使其可以計(jì)算出多種超越函數(shù),更大的擴(kuò)展了Cordic 算法

2017-11-17 16:37:01 6470

6470

雖然CORDIC 是實(shí)現(xiàn) DSP 和數(shù)學(xué)函數(shù)最重要的算法之一,但許多設(shè)計(jì)人員并不熟悉。 作者:Adam P. Taylor 首席工程師 阿斯特里姆公司 (EADS Astrium

2019-10-06 10:52:00 1565

1565

CORDIC是在一個(gè)稱為二進(jìn)制搜索的循環(huán)中使用更簡單的數(shù)學(xué)運(yùn)算來計(jì)算數(shù)學(xué)函數(shù)的方法。最常用的CORDIC用于計(jì)算AtAN2(角度)和點(diǎn)的斜邊(距離)。CORDIC還可以用來計(jì)算其他數(shù)學(xué)函數(shù),如Sin和CoS。

2018-05-31 11:18:14 12

12 如圖,使用CORDIC算法計(jì)算平方根,FPGA資源的使用情況。邏輯單元使用了10%,乘法器使用的6個(gè),片上ram只是用的不到1%。可以說在資源有限的情況下,是非常好的選擇 。但是要注意,算法本身可使

2018-06-08 14:40:37 6289

6289

本文是基于FPGA實(shí)現(xiàn)Cordic算法的設(shè)計(jì)與驗(yàn)證,使用Verilog HDL設(shè)計(jì),初步可實(shí)現(xiàn)正弦、余弦、反正切函數(shù)的實(shí)現(xiàn)。將復(fù)雜的運(yùn)算轉(zhuǎn)化成FPGA擅長的加減法和乘法,而乘法運(yùn)算可以用移位運(yùn)算代替

2018-07-03 10:18:00 2350

2350

快速精確的反正弦函數(shù)運(yùn)算在現(xiàn)代工程中應(yīng)用廣泛。為了提高反正弦函數(shù)的精度和計(jì)算能力, 研究了基于CORD IC算法的反正弦函數(shù)運(yùn)算器的FPGA 實(shí)現(xiàn), 并通過改進(jìn)算法減小了誤差, 使誤差精度達(dá)到

2018-10-07 11:30:30 7908

7908 為提高圖像邊緣檢測的處理速度,提出一種基于CORDIC的高速Sobel算法實(shí)現(xiàn)。

2018-10-05 09:54:00 3279

3279

CORDIC(Coordinate Rotation Digital Computer)算法即坐標(biāo)旋轉(zhuǎn)數(shù)字計(jì)算方法,是J.D.Volder1于1959年首次提出,主要用于三角函數(shù)、雙曲線、指數(shù)、對數(shù)

2019-11-13 07:09:00 6103

6103 對數(shù)函數(shù)在粒子濾波、RBF 神經(jīng)網(wǎng)絡(luò)、圖像處理等領(lǐng)域廣泛運(yùn)用。CORDIC 算法( TheCoordinate Rotation Digital Computer )是一種用于計(jì)算一些常用的基本運(yùn)算

2020-08-07 17:14:00 12

12 主要介紹了坐標(biāo)旋轉(zhuǎn)數(shù)字計(jì)算(CORDIC)算法在US,g,鑒別器中的應(yīng)用,包括碼跟蹤環(huán)、鎖頻環(huán)和鎖相環(huán)鑒別器,并進(jìn)行了FPGA實(shí)現(xiàn)。在設(shè)計(jì)中,采用統(tǒng)一cORDIc算法優(yōu)化方法減少硬件開銷,用非流水

2021-01-22 16:12:00 8

8 提出了一種基于流水線CORDIC的算法實(shí)現(xiàn)QAM調(diào)制,可有效節(jié)省硬件資源,提高運(yùn)算速度。用Verilog HDL對本設(shè)計(jì)進(jìn)行了編程和功能仿真,仿真結(jié)果表明,本設(shè)計(jì)具有一定的實(shí)用性。

2021-02-01 14:54:02 6

6 框架結(jié)構(gòu),提出了一種高度并行、緊湊流水線的FPGA實(shí)現(xiàn)方案.用Verilog HDL硬件描述語言設(shè)計(jì)了編碼,在QuARTuSⅡ集成開發(fā)環(huán)境下,進(jìn)行了仿真驗(yàn)證,并寫入FPGA芯片,實(shí)現(xiàn)了“十字”形運(yùn)動(dòng)估計(jì)算法.經(jīng)測試表明:該設(shè)計(jì)方案搜索高效、邏輯簡潔,對比全搜索法占用硬件資源較小

2021-02-03 14:46:00 12

12 CORD IC算法是在許多角度計(jì)算方面有著廣泛應(yīng)用的經(jīng)典算法,通過考慮FPGA 的結(jié)構(gòu)、精度局限和速度要求,采用流水線技術(shù)(pipeline ) ,在FPGA 上用CORDIC算法實(shí)現(xiàn)了對于大吞吐量數(shù)據(jù)的向量傾角的計(jì)算,并對實(shí)際應(yīng)用中內(nèi)部步驟寄存器精度的選取給出了較為詳細(xì)的方法。

2021-03-03 15:55:00 6

6 CORDIC算法簡介 在信號處理領(lǐng)域,CORDIC(Coordinate Rotation Digital Computer,坐標(biāo)旋轉(zhuǎn)數(shù)字計(jì)算機(jī))算法具有重大工程意義。CORDIC算法由Vloder

2021-04-11 11:16:50 12494

12494

任何適合產(chǎn)品實(shí)現(xiàn)的算法,都是將簡易實(shí)現(xiàn)作為第一目標(biāo)。CORDIC算法是建立在適應(yīng)性濾波器、FFT、解調(diào)器等眾多應(yīng)用基礎(chǔ)上計(jì)算超越函數(shù)的方法。其核心思想是二分逐次逼近。???? CORDIC

2021-08-16 11:21:11 1827

1827

在FPGA硬件實(shí)現(xiàn)CORDIC的邏輯其實(shí)是很簡單的,就是設(shè)置好輸入輸出的位寬,然后建立好對應(yīng)的精度表,通過旋轉(zhuǎn)加得到運(yùn)算結(jié)果。

2022-10-17 11:58:58 2050

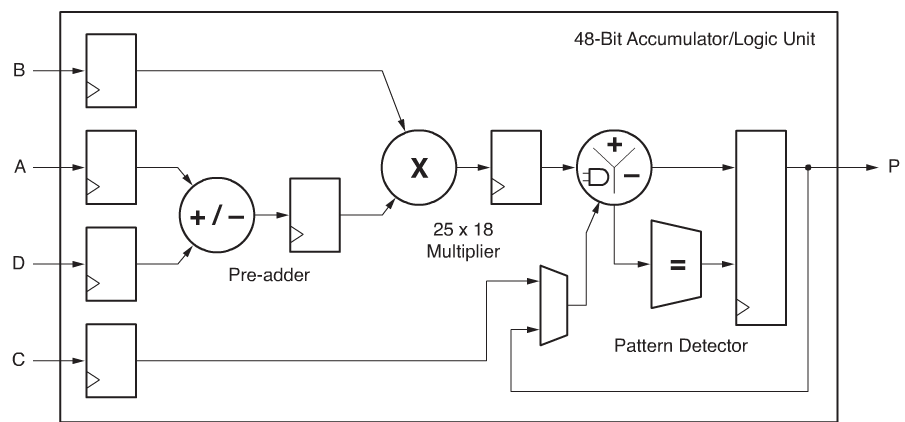

2050 FPGA以擅長高速并行數(shù)據(jù)處理而聞名,從有線/無線通信到圖像處理中各種DSP算法,再到現(xiàn)今火爆的AI應(yīng)用,都離不開卷積、濾波、變換等基本的數(shù)學(xué)運(yùn)算。

2022-10-31 14:48:15 2414

2414 在信號處理領(lǐng)域,CORDIC(Coordinate Rotation Digital Computer,坐標(biāo)旋轉(zhuǎn)數(shù)字計(jì)算機(jī))算法具有重大工程意義。

2023-03-28 09:39:03 1105

1105 由于FPGA可以對算法進(jìn)行并行化,所以FPGA 非常適合在可編程邏輯中實(shí)現(xiàn)數(shù)學(xué)運(yùn)算。

2023-05-15 11:29:15 2057

2057

CORDIC(Coordinate Rotation Digital Computer)算法即坐標(biāo)旋轉(zhuǎn)數(shù)字計(jì)算方法,是J.D.Volder1于1959年首次提出,主要用于三角函數(shù)、雙曲線、指數(shù)、對數(shù)的計(jì)算。

2023-08-31 14:54:21 1106

1106

由于在項(xiàng)目中需要使用的MPU6050,進(jìn)行姿態(tài)解算,計(jì)算中設(shè)計(jì)到arctan 和 sqr(x*2 + y * 2),這兩部分的計(jì)算,在了解了一番之后,發(fā)現(xiàn)Cordic算法可以很方便的一次性求出這兩個(gè)這兩部分的計(jì)算。

2023-09-27 09:30:26 685

685

電子發(fā)燒友網(wǎng)站提供《基于流水線CORDIC算法通用數(shù)字調(diào)制器的FPGA實(shí)現(xiàn)方案.pdf》資料免費(fèi)下載

2023-10-27 09:46:19 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評論