資料介紹

EDA設計

1,雖然每個小組可以優化局部功耗,但單個團隊不可能創建出一個低功耗設計。反之,任何一個小組都可能摧毀這種努力。

2,功率估計是一種精確的科學。但是,只有當你擁有了一個完整設計和一組正確的矢量后,這種概念才為真。

3,對任何問題而言,處理器通常是能效最低的方法,但因為它們具備了功能多重性,一般可以用最小面積獲得實現。

4,電源分配網絡應能夠在不損及電壓完整性的情況下,維持負載。

過去十年來,功率已經成為一個關鍵的設計考慮,并在工程師設計與驗證系統方面帶來了一些巨大的挑戰。物理學不再提供免費便車。

功率是能量被消耗的速率,這在十年前還不是熱門,但今天已是一個重要的設計考量。系統的能耗會帶來熱量、耗盡電池、增加電能分配網絡的壓力,并且加大成本。移動計算的發展最先推動了對降低能耗的期望,但能耗的效應現在已遠遠超出這個范圍,可能在業界帶來一些最大的結構性變化。對于服務器農場、云計算、汽車、芯片,以及依賴于能源獲取的泛在式傳感器網絡,這都是一個關鍵性問題

突然改變的原因是,物理學已把工藝技術帶到了90nm以下尺度。但是,隨著結點尺寸越來越小,電壓降低,從而造成功率的相應下降。通常,即使開發人員增加了更多功能,功率預算也會保持不變。在更小尺度下,電壓的縮放更加困難,無法維持。當電壓接近于閾值電壓時,開關時間就會增加。為補償這一問題,設計人員會降低閾值電壓,但這樣做顯著增加了泄漏電流和開關電流。

設計流程中的每個階段都對功耗有影響,從軟件架構到器件物理。雖然每個小組都可以做局部的功耗優化工作,但沒有一個團隊可以單獨創建出一個低功耗設計。反之,任何一個團隊都可能摧毀低功耗的努力。這種狀況就產生了一種對協同與交叉學科工具的新需求。功率問題不再止于芯片。它們遍及互連結構、電路板與系統設計、電源控制器等諸方面。當前的EDA工具并非按功率概念而建立,這意味著設計人員要采用改進型方法,而不是從頭開始的新方法。

物理原理的角色

一只芯片消耗的功率是開關(或動態)功率和無源(或泄漏)功率之和。功率的動態成分源于設計的容性負載。當某個線網從0轉換到1時,這個成分通過一個PMOS晶體管充電。從電源獲得的能量等于容性負載與電壓平方的乘積。系統將這個能量的一半存儲在電容中;另一半則耗散在晶體管上。對于從1至0的轉換,不會從電源獲得更多能量,但電荷要耗散在NMOS晶體管上。假設結點以頻率F變化,則動態功率為FCLVDD2,其中,CL是容性負載,VDD是電壓。雖然也存在其它形式的動態功率,但它們要小得多。

由于電壓是平方項,因此降低電壓有相當顯著的效果。不幸的是,性能也與電壓相關,因為增加電壓會增加柵極的驅動VGS-VT,其中VGS是柵源電壓,VT是閾值電壓。使用較陳舊的技術時,泄漏功率并不明顯。但隨著器件尺度的減小,很多區域中的泄漏變得更加顯著,包括柵極氧化物隧穿、亞閾值電壓、反偏結點、柵極導致的漏極泄漏,以及因熱載流子注入而產生的柵極電流等。

二氧化硅是常用的絕緣材料。在低厚度水平下,電子可以隧穿它。這種關系是指數型的,意味著厚度減半,泄漏增至四倍,在晶體管尺度降到130nm以下之前,這還不是一個問題。用高k電介質代替二氧化硅可以提供相近的器件性能,獲得更厚的柵級絕緣體,從而降低了這個電流。

晶體管有一個柵源閾值電壓,低于這個電壓時,通過器件的亞閾值電流就會呈指數倍下降。當降低電源電壓以減少動態功耗時,閾值電壓也減小,從而使柵極電壓擺幅低于器件關斷的閾值。亞閾值傳導會隨柵極電壓呈指數式變化。

在擴散區和阱之間,或在阱與基材之間的一個反偏構造,會產生小的反偏結泄漏。在MOS晶體管漏極結上的高電場效應會產生柵極導致的漏極泄漏,這通常要用制造技術來處理。柵極電流泄漏的原因是短溝道器件的閾值電壓漂移,并與器件中的高電場有關。對這個效應的控制主要也是靠制造技術。

設計人員要在動態功耗和靜態功耗之間做一個折中。降低電壓會減小動態功耗,但增加了靜態功耗。我們來看一只手機內的典型芯片。當器件工作時,泄漏要占所消耗功率的大約10%;其它90%是動態功耗。但當手機處于待機模式時(可能占到總時間的90%),芯片中的動態功耗就很少。因此,盡量減小兩種功耗有著相同的重要性。

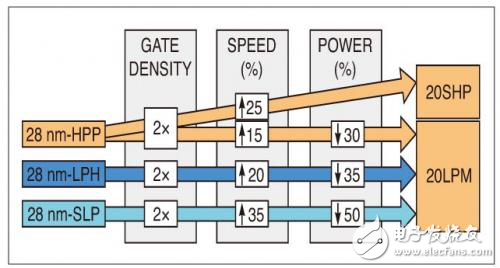

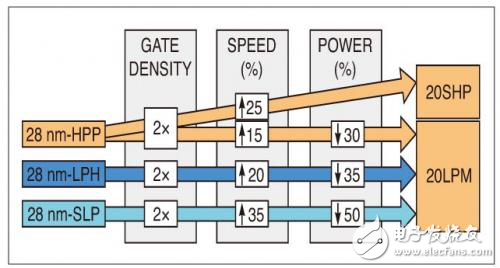

各種器件的功耗方面在持續地改進。例如,在相同頻率下,三星的28nm低功耗工藝比45nm低功耗工藝的動態功耗與待機功耗都減少了35%,與采用45nm低功耗的系統單芯片設計相比,28nm工藝在相同頻率下的動態功耗降低了60%.臺積電28nm高性能低功耗工藝的待機功耗要比其40nm低功耗工藝低40%以上。同時GlobalFoundries公司為其28nm結點提供了三種功率水平(圖1)。

圖1,臺積電的28-HPL工藝待機功耗較40-LP工藝低40%以上。而Global Foundries則為其28nm結點提供了三種功率水平

摩爾定律繼續有效,芯片在每個器件中封裝了更多功能。據Open-Silicon的營銷總監Colin Baldwin稱,客戶可以用近似的單位成本和兩倍的性能,設計出下一代器件,雖然總功耗會增加,但單只器件的功耗是下降的。時鐘頻率是另外一個緩慢上漲的變量,但在很多市場上增速都慢于工藝。Open-Silicon發現,大多數用戶試圖在略微增加總體功耗的情況下,集成更多的功能。因此,要維持相同的總功耗,就要看設計流程的其它部分中可以節省的能耗。

優化與比較

設計包含了估算與優化。估算可以對多個可能的實現選擇做出比較。另外,優化可以自動完成,或者可以在各種抽象水平上,用工具輔助完成。Apache/Ansys應用工程總監Arvind Shanmugavel認為,只有當擁有了一個完整設計和一組正確的矢量時,功率估算才是一種精確的科學。在未完成設計以前,根據定義,所有事物都是一種即將在設計中發生的估計。在設計早期的功率預算階段,應著眼于大的和相對的變化,而不是絕對的值。Atrenta公司的工程總監Venki Venkatesh認為,可以預期在RTL(寄存器傳輸級)到硅片之間有20%的偏差,而從門到硅片有10%的偏

1,雖然每個小組可以優化局部功耗,但單個團隊不可能創建出一個低功耗設計。反之,任何一個小組都可能摧毀這種努力。

2,功率估計是一種精確的科學。但是,只有當你擁有了一個完整設計和一組正確的矢量后,這種概念才為真。

3,對任何問題而言,處理器通常是能效最低的方法,但因為它們具備了功能多重性,一般可以用最小面積獲得實現。

4,電源分配網絡應能夠在不損及電壓完整性的情況下,維持負載。

過去十年來,功率已經成為一個關鍵的設計考慮,并在工程師設計與驗證系統方面帶來了一些巨大的挑戰。物理學不再提供免費便車。

功率是能量被消耗的速率,這在十年前還不是熱門,但今天已是一個重要的設計考量。系統的能耗會帶來熱量、耗盡電池、增加電能分配網絡的壓力,并且加大成本。移動計算的發展最先推動了對降低能耗的期望,但能耗的效應現在已遠遠超出這個范圍,可能在業界帶來一些最大的結構性變化。對于服務器農場、云計算、汽車、芯片,以及依賴于能源獲取的泛在式傳感器網絡,這都是一個關鍵性問題

突然改變的原因是,物理學已把工藝技術帶到了90nm以下尺度。但是,隨著結點尺寸越來越小,電壓降低,從而造成功率的相應下降。通常,即使開發人員增加了更多功能,功率預算也會保持不變。在更小尺度下,電壓的縮放更加困難,無法維持。當電壓接近于閾值電壓時,開關時間就會增加。為補償這一問題,設計人員會降低閾值電壓,但這樣做顯著增加了泄漏電流和開關電流。

設計流程中的每個階段都對功耗有影響,從軟件架構到器件物理。雖然每個小組都可以做局部的功耗優化工作,但沒有一個團隊可以單獨創建出一個低功耗設計。反之,任何一個團隊都可能摧毀低功耗的努力。這種狀況就產生了一種對協同與交叉學科工具的新需求。功率問題不再止于芯片。它們遍及互連結構、電路板與系統設計、電源控制器等諸方面。當前的EDA工具并非按功率概念而建立,這意味著設計人員要采用改進型方法,而不是從頭開始的新方法。

物理原理的角色

一只芯片消耗的功率是開關(或動態)功率和無源(或泄漏)功率之和。功率的動態成分源于設計的容性負載。當某個線網從0轉換到1時,這個成分通過一個PMOS晶體管充電。從電源獲得的能量等于容性負載與電壓平方的乘積。系統將這個能量的一半存儲在電容中;另一半則耗散在晶體管上。對于從1至0的轉換,不會從電源獲得更多能量,但電荷要耗散在NMOS晶體管上。假設結點以頻率F變化,則動態功率為FCLVDD2,其中,CL是容性負載,VDD是電壓。雖然也存在其它形式的動態功率,但它們要小得多。

由于電壓是平方項,因此降低電壓有相當顯著的效果。不幸的是,性能也與電壓相關,因為增加電壓會增加柵極的驅動VGS-VT,其中VGS是柵源電壓,VT是閾值電壓。使用較陳舊的技術時,泄漏功率并不明顯。但隨著器件尺度的減小,很多區域中的泄漏變得更加顯著,包括柵極氧化物隧穿、亞閾值電壓、反偏結點、柵極導致的漏極泄漏,以及因熱載流子注入而產生的柵極電流等。

二氧化硅是常用的絕緣材料。在低厚度水平下,電子可以隧穿它。這種關系是指數型的,意味著厚度減半,泄漏增至四倍,在晶體管尺度降到130nm以下之前,這還不是一個問題。用高k電介質代替二氧化硅可以提供相近的器件性能,獲得更厚的柵級絕緣體,從而降低了這個電流。

晶體管有一個柵源閾值電壓,低于這個電壓時,通過器件的亞閾值電流就會呈指數倍下降。當降低電源電壓以減少動態功耗時,閾值電壓也減小,從而使柵極電壓擺幅低于器件關斷的閾值。亞閾值傳導會隨柵極電壓呈指數式變化。

在擴散區和阱之間,或在阱與基材之間的一個反偏構造,會產生小的反偏結泄漏。在MOS晶體管漏極結上的高電場效應會產生柵極導致的漏極泄漏,這通常要用制造技術來處理。柵極電流泄漏的原因是短溝道器件的閾值電壓漂移,并與器件中的高電場有關。對這個效應的控制主要也是靠制造技術。

設計人員要在動態功耗和靜態功耗之間做一個折中。降低電壓會減小動態功耗,但增加了靜態功耗。我們來看一只手機內的典型芯片。當器件工作時,泄漏要占所消耗功率的大約10%;其它90%是動態功耗。但當手機處于待機模式時(可能占到總時間的90%),芯片中的動態功耗就很少。因此,盡量減小兩種功耗有著相同的重要性。

各種器件的功耗方面在持續地改進。例如,在相同頻率下,三星的28nm低功耗工藝比45nm低功耗工藝的動態功耗與待機功耗都減少了35%,與采用45nm低功耗的系統單芯片設計相比,28nm工藝在相同頻率下的動態功耗降低了60%.臺積電28nm高性能低功耗工藝的待機功耗要比其40nm低功耗工藝低40%以上。同時GlobalFoundries公司為其28nm結點提供了三種功率水平(圖1)。

圖1,臺積電的28-HPL工藝待機功耗較40-LP工藝低40%以上。而Global Foundries則為其28nm結點提供了三種功率水平

摩爾定律繼續有效,芯片在每個器件中封裝了更多功能。據Open-Silicon的營銷總監Colin Baldwin稱,客戶可以用近似的單位成本和兩倍的性能,設計出下一代器件,雖然總功耗會增加,但單只器件的功耗是下降的。時鐘頻率是另外一個緩慢上漲的變量,但在很多市場上增速都慢于工藝。Open-Silicon發現,大多數用戶試圖在略微增加總體功耗的情況下,集成更多的功能。因此,要維持相同的總功耗,就要看設計流程的其它部分中可以節省的能耗。

優化與比較

設計包含了估算與優化。估算可以對多個可能的實現選擇做出比較。另外,優化可以自動完成,或者可以在各種抽象水平上,用工具輔助完成。Apache/Ansys應用工程總監Arvind Shanmugavel認為,只有當擁有了一個完整設計和一組正確的矢量時,功率估算才是一種精確的科學。在未完成設計以前,根據定義,所有事物都是一種即將在設計中發生的估計。在設計早期的功率預算階段,應著眼于大的和相對的變化,而不是絕對的值。Atrenta公司的工程總監Venki Venkatesh認為,可以預期在RTL(寄存器傳輸級)到硅片之間有20%的偏差,而從門到硅片有10%的偏

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- EDA市場現狀分析及趨勢 4次下載

- 海爾空調故障代碼之功率模塊保護綜述 9次下載

- EDA工具CADENCE原理圖與PCB設計說明 55次下載

- 多軸機器人和機床中的時序挑戰綜述 11次下載

- 模擬電子技術之功率放大電路課件下載 64次下載

- 高效高功率同步整流升壓DC-DC芯片AMT6802 19次下載

- EDA多任務流調度算法實驗設計 5次下載

- 電子技術基礎教程之功率放大電路的詳細資料概述 30次下載

- EDA技術實用教程之EDA技術概述數字設計的流程及常用的EDA軟件工具介紹 45次下載

- EDA實用教程概述 0次下載

- 常用EDA軟件介紹

- EDA 技術在教學實踐中的應用2 0次下載

- 平坦世界的EDA 設計解決方案 0次下載

- EDA軟件在電路設計中的應用 0次下載

- EDA Tools in FPGA 0次下載

- SiC與GaN 功率器件中的離子注入技術挑戰 710次閱讀

- eda是什么化學試劑 EDA的應用場景 2240次閱讀

- eda工具軟件有哪些 EDA工具有什么優勢 861次閱讀

- EDA出現四大新趨勢 既是機遇也是挑戰 1829次閱讀

- EDA技術在組合邏輯電路中的設計概述 2728次閱讀

- EDA技術中的常用軟件與仿真工具介紹 9593次閱讀

- EDA技術概述 什么是EDA工具? 2.6w次閱讀

- 學eda技術必看的8本書_eda技術方面的書籍推薦 2.5w次閱讀

- 簡述什么是eda技術_eda技術好學嗎_如何學習EDA技術 3.7w次閱讀

- 什么是EDA工具?目前全球EDA行業的現狀是什么? 3.9w次閱讀

- PFC基礎概述之功率因數與規范要求解答 9293次閱讀

- eda是什么技術_eda為什么又叫單片機 1.9w次閱讀

- 基于EDA技術的電子設計要點 1412次閱讀

- 淺析SoC芯片設計中的動態功率估算挑戰 864次閱讀

- EDA技術進行數字電路設計 3647次閱讀

下載排行

本周

- 1電子電路原理第七版PDF電子教材免費下載

- 0.00 MB | 1497次下載 | 免費

- 2TC358743XBG評估板參考手冊

- 1.36 MB | 330次下載 | 免費

- 3單片機典型實例介紹

- 18.19 MB | 103次下載 | 1 積分

- 4S7-200PLC編程實例詳細資料

- 1.17 MB | 28次下載 | 1 積分

- 5筆記本電腦主板的元件識別和講解說明

- 4.28 MB | 18次下載 | 4 積分

- 6開關電源原理及各功能電路詳解

- 0.38 MB | 15次下載 | 免費

- 79天練會電子電路識圖

- 5.91 MB | 6次下載 | 免費

- 8100W短波放大電路圖

- 0.05 MB | 4次下載 | 3 積分

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234314次下載 | 免費

- 2PADS 9.0 2009最新版 -下載

- 0.00 MB | 66304次下載 | 免費

- 3protel99下載protel99軟件下載(中文版)

- 0.00 MB | 51209次下載 | 免費

- 4LabView 8.0 專業版下載 (3CD完整版)

- 0.00 MB | 51043次下載 | 免費

- 5555集成電路應用800例(新編版)

- 0.00 MB | 33564次下載 | 免費

- 6接口電路圖大全

- 未知 | 30321次下載 | 免費

- 7Multisim 10下載Multisim 10 中文版

- 0.00 MB | 28588次下載 | 免費

- 8開關電源設計實例指南

- 未知 | 21540次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935054次下載 | 免費

- 2protel99se軟件下載(可英文版轉中文版)

- 78.1 MB | 537794次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234314次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191183次下載 | 免費

- 7十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183278次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138039次下載 | 免費

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論