資料介紹

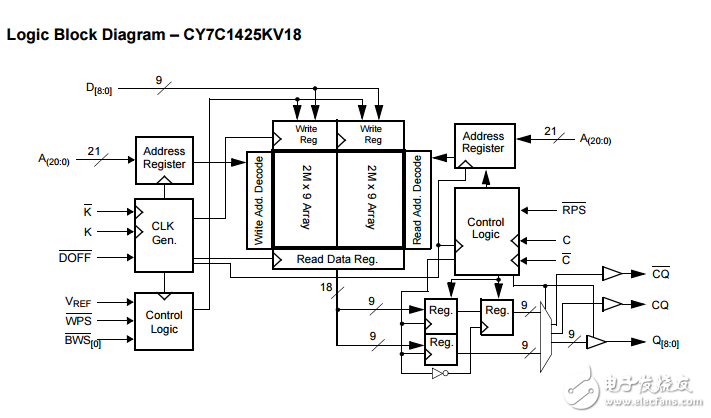

The CY7C1425KV18, CY7C1412KV18, and CY7C1414KV18 are 1.8 V synchronous pipelined SRAMs, equipped with QDR II architecture. QDR II architecture consists of two separate ports: the read port and the write port to access the memory array. The read port has dedicated data outputs to support read operations and the write port has dedicated data inputs to support write operations. QDR II architecture has separate data inputs and data outputs to completely eliminate the need to “turnaround” the data bus that exists with common I/O devices. Access to each port is through a common address bus. Addresses for read and write addresses are latched on alternate rising edges of the input (K) clock. Accesses to the QDR II read and write ports are completely independent of one another. To maximize data throughput, both read and write ports are equipped with DDR interfaces. Each address location is associated with two 9-bit words (CY7C1425KV18), 18-bit words (CY7C1412KV18), or 36-bit words (CY7C1414KV18) that burst sequentially into or out of the device. Because data can be transferred into and out of the device on every rising edge of both input clocks (K and K and C and C), memory bandwidth is maximized while simplifying system design by eliminating bus turnarounds. Depth expansion is accomplished with port selects, which enables each port to operate independently. All synchronous inputs pass through input registers controlled by the K or K input clocks. All data outputs pass through output registers controlled by the C or C (or K or K in a single clock domain) input clocks. Writes are conducted with on-chip synchronous self-timed write circuitry. For a complete list of related documentation, click here.

- 如何使用 QDR(TM) II SRAM 和 DDR II SRAM 用戶手冊

- CY7C1643KV18和CY7C1645KV18靜態存儲器的數據手冊免費下載 3次下載

- SRAM 72-Mbit QDR? II+ SRAM 4 字突發架構(2.5 周期讀延遲 17次下載

- SRAM 72-Mbit QDR? II SRAM 2 字突發結構 12次下載

- 18兆位DCD同步SRAM的流水線cy7c1386d 4次下載

- cy7c1663kv18/cy7c1665kv18數據手冊 6次下載

- cy7c1347g 4兆位(128K的×36)流水線同步SRAM 6次下載

- cy7c1381d 18兆位(512K的×36/1M×18) 流通過SRAM 5次下載

- y7c1383f 18兆位(512K的×36/1M×18)流過的SRAM 3次下載

- 18兆位QDR SRAM?II 四字突發結構cy7c1315kv18-250bzxc 2次下載

- cy7c1312kv18/cy7c1314kv18 18兆位QDR SRAM?II雙字突發結構 5次下載

- CY7C1380D-167AXC,18兆位(512K的×36/1M×18)流水線SRAM 2次下載

- 72兆位的流水線結構的SRAM?諾伯CY7C1472V25-200AXC 9次下載

- 72兆位流水線結構的SRAM?諾伯CY7C1470V33-167AXI 12次下載

- 72兆位QDR?II SRAM兩詞突發結構CY7C1512KV18-300BZXC 4次下載

- 什么是a位錯,c位錯,c+a位錯?如何區分三種位錯? 5205次閱讀

- 高速串行數據通信CY7B923芯片的性能特點及設計實例 4248次閱讀

- 基于Nios II和uClinux實現遠程測控服務器的設計 653次閱讀

- 采用5管單元的SRAM結構實現CPLD可編程電路的設計 1855次閱讀

- 基于CY7C68013芯片的LED顯示屏外部接口設計 1618次閱讀

- 通過CY7C68013微控制器實現數據低速控制、高速傳輸的設計 5060次閱讀

- 微雪電子CY7C68013A高速USB通信模塊簡介 2750次閱讀

- LPC213X通過μC/OS-II的多種移植方案 621次閱讀

- STM32單片機特性解析 9989次閱讀

- Wishbone總線的突發結束 3080次閱讀

- 用于DDR-QDR4存儲器的超薄穩壓器LTM4632 1384次閱讀

- QDR SRAM接口FPGA詳細Verilog代碼分享 8050次閱讀

- μC/OS-II系統基礎嵌入式開發編程教程 4369次閱讀

- 單片機中Avr和Stm32區別及選取技巧詳解 6669次閱讀

- 基于XC3S400和CY7C68013多路數據采集電路的設計 2712次閱讀

下載排行

本周

- 1TC358743XBG評估板參考手冊

- 1.36 MB | 330次下載 | 免費

- 2開關電源基礎知識

- 5.73 MB | 6次下載 | 免費

- 3100W短波放大電路圖

- 0.05 MB | 4次下載 | 3 積分

- 4嵌入式linux-聊天程序設計

- 0.60 MB | 3次下載 | 免費

- 5基于FPGA的光纖通信系統的設計與實現

- 0.61 MB | 2次下載 | 免費

- 651單片機窗簾控制器仿真程序

- 1.93 MB | 2次下載 | 免費

- 751單片機大棚環境控制器仿真程序

- 1.10 MB | 2次下載 | 免費

- 8基于51單片機的RGB調色燈程序仿真

- 0.86 MB | 2次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 2555集成電路應用800例(新編版)

- 0.00 MB | 33564次下載 | 免費

- 3接口電路圖大全

- 未知 | 30323次下載 | 免費

- 4開關電源設計實例指南

- 未知 | 21549次下載 | 免費

- 5電氣工程師手冊免費下載(新編第二版pdf電子書)

- 0.00 MB | 15349次下載 | 免費

- 6數字電路基礎pdf(下載)

- 未知 | 13750次下載 | 免費

- 7電子制作實例集錦 下載

- 未知 | 8113次下載 | 免費

- 8《LED驅動電路設計》 溫德爾著

- 0.00 MB | 6653次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935054次下載 | 免費

- 2protel99se軟件下載(可英文版轉中文版)

- 78.1 MB | 537796次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191185次下載 | 免費

- 7十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183279次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138040次下載 | 免費

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論