資料介紹

1引言

建立芯片模型是在早期進(jìn)行芯片架構(gòu)決策的有效方法,通過建模不僅可以對(duì)芯片的性能做出分析,還可以在硬件沒有完成之前開發(fā)軟件,不僅提高了產(chǎn)品成功率,而且縮短了研發(fā)周期。設(shè)計(jì)人員早期采用C/C++語言進(jìn)行硬件建模。但是隨著軟硬件復(fù)雜度的提高,C/C++語言難以再滿足要求。OSCI適時(shí)推出了SystemC語言來適應(yīng)新的需求。如今SystemC已經(jīng)被廣泛應(yīng)用于SoC軟硬件建模中。

目前大部分SystemC建模方面的文獻(xiàn)是作者對(duì)自己所設(shè)計(jì)芯片整體模型的描述,這種針對(duì)特定芯片設(shè)計(jì)的文獻(xiàn)雖然都有參考價(jià)值,但是其模型本身借鑒性有限。另一方面,構(gòu)成SoC硬件的基本組件因?yàn)榭芍赜玫木壒剩淠P驮O(shè)計(jì)具有更好的可借鑒性。這方面的研究成果相對(duì)較少,而且集中在總線建模方面,也可以看到多核設(shè)計(jì)方面的建模方法。

除了上述總線、CPU架構(gòu)外,片內(nèi)或片外存儲(chǔ)器同樣是系統(tǒng)關(guān)鍵模塊,對(duì)系統(tǒng)性能有著至關(guān)重要的影響。文獻(xiàn)[6]對(duì)SystemClick框架做了擴(kuò)展,從而通過存儲(chǔ)器模型能夠分析共享存儲(chǔ)器對(duì)性能的影響。文獻(xiàn)[7]針對(duì)多通道DRAM做了建模,并且分析了不同的配置和使用情況對(duì)性能的影響。這兩篇文獻(xiàn)都對(duì)所設(shè)計(jì)的模型做了詳盡的分析,具有很好的參考價(jià)值,但是兩者的通用性欠佳。本文提出了一個(gè)可配置的通用存儲(chǔ)器SystemC模型。

2 SystemC

SystemC可被視作C++硬件建模和仿真的擴(kuò)展庫,特別適合集成電路的建模,但它事實(shí)上可以用來描述更多的系統(tǒng)。SystemC通過確定仿真核心(simulation kernel)算法定義了處理并行事件和仿真時(shí)間的機(jī)制。SystemC還定義了模塊、端口、接口、通道等概念來組成一個(gè)復(fù)雜SoC的連接關(guān)系和層次結(jié)構(gòu)。因此,它解決了標(biāo)準(zhǔn)C++語言用于復(fù)雜硬件建模時(shí)的難題。

3存儲(chǔ)器的建模

3.1存儲(chǔ)器模型概述

為了能幫助設(shè)計(jì)人員分析系統(tǒng)性能并選擇最合適的存儲(chǔ)器構(gòu)造,存儲(chǔ)器模型需要反映出對(duì)性能造成影響的關(guān)鍵參數(shù),即帶寬、延時(shí)和仲裁機(jī)制。而這些參數(shù)又是由存儲(chǔ)器的結(jié)構(gòu)以及其它參數(shù)決定的。另一方面,本文希望提出一個(gè)通用的存儲(chǔ)器模型,因此會(huì)有更多的參數(shù)用于配置存儲(chǔ)器以模擬某種特定類型的存儲(chǔ)器特征,比如多端口SRAM.

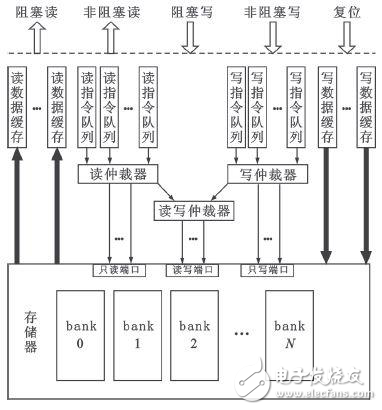

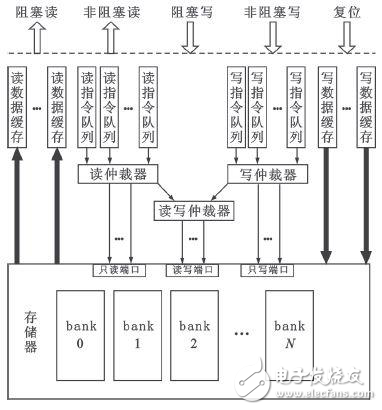

圖1給出了所設(shè)計(jì)的存儲(chǔ)器模型的結(jié)構(gòu)。它包括三個(gè)部分:一是模型接口;二是端口及bank可配置的存儲(chǔ)器;三是由讀寫通路及仲裁機(jī)制構(gòu)成的存儲(chǔ)器控制器。接口部分采用了事務(wù)級(jí)建模,而內(nèi)部模塊采用了時(shí)鐘精準(zhǔn)的建模,這樣在保證時(shí)間精度的同時(shí),方便了接口連接以及提高了仿真速度。

圖1可配置存儲(chǔ)器模型結(jié)構(gòu)

3.2存儲(chǔ)器接口

基于SystemC的存儲(chǔ)器模型接口,由SystemC定義的接口基類派生而來。整個(gè)存儲(chǔ)器模型是一個(gè)SystemC模塊,由于實(shí)現(xiàn)了所定義的存儲(chǔ)器模型接口,它成為SystemC概念中的hierarchal channel.因此,該存儲(chǔ)器模型將如同其它SystemC定義的通道,比如FIFO,一樣作為基本組件來連接其它的模塊從而構(gòu)造出SoC硬件系統(tǒng)。所設(shè)計(jì)存儲(chǔ)器具有如下所述事務(wù)級(jí)SystemC接口。

阻塞讀接口:該接口用來讀取給定地址的給定大小的數(shù)據(jù),當(dāng)數(shù)據(jù)沒有讀出時(shí),調(diào)用這個(gè)接口的模塊線程將被堵塞,直到數(shù)據(jù)讀出為止。除了地址和數(shù)據(jù),該接口還包含調(diào)用者的標(biāo)志信息。

非阻塞讀接口:與阻塞讀接口不同的是,如果在調(diào)用時(shí)讀指令不能被接受,則返回失敗。否則,不等待數(shù)據(jù)返回便成功退出。這樣調(diào)用接口的模塊線程可以在等待時(shí)間做其它事情。調(diào)用者通過監(jiān)聽存儲(chǔ)器模型廣播的當(dāng)前讀出數(shù)據(jù)多對(duì)應(yīng)調(diào)用者標(biāo)記來在之后讀出數(shù)據(jù)。

阻塞寫接口:該接口用來向存儲(chǔ)器給定地址寫入給定大小的數(shù)據(jù)。當(dāng)指令或?qū)憯?shù)據(jù)不能被存儲(chǔ)器模型接收時(shí),調(diào)用的線程被堵塞直到接受為止。除了地址和數(shù)據(jù),該接口還包含調(diào)用者的標(biāo)志信息。

非阻塞寫接口:與阻塞寫接口不同的是,當(dāng)指令或數(shù)據(jù)不能被接受時(shí),返回失敗而不等待。否則返回成功。

復(fù)位接口:用于復(fù)位存儲(chǔ)器模型。

為了不強(qiáng)制要求外部提供存儲(chǔ)器模型需要的時(shí)鐘,存儲(chǔ)器模型接口中不包含時(shí)鐘輸入。模型內(nèi)部有一個(gè)專門的時(shí)鐘產(chǎn)生線程。

建立芯片模型是在早期進(jìn)行芯片架構(gòu)決策的有效方法,通過建模不僅可以對(duì)芯片的性能做出分析,還可以在硬件沒有完成之前開發(fā)軟件,不僅提高了產(chǎn)品成功率,而且縮短了研發(fā)周期。設(shè)計(jì)人員早期采用C/C++語言進(jìn)行硬件建模。但是隨著軟硬件復(fù)雜度的提高,C/C++語言難以再滿足要求。OSCI適時(shí)推出了SystemC語言來適應(yīng)新的需求。如今SystemC已經(jīng)被廣泛應(yīng)用于SoC軟硬件建模中。

目前大部分SystemC建模方面的文獻(xiàn)是作者對(duì)自己所設(shè)計(jì)芯片整體模型的描述,這種針對(duì)特定芯片設(shè)計(jì)的文獻(xiàn)雖然都有參考價(jià)值,但是其模型本身借鑒性有限。另一方面,構(gòu)成SoC硬件的基本組件因?yàn)榭芍赜玫木壒剩淠P驮O(shè)計(jì)具有更好的可借鑒性。這方面的研究成果相對(duì)較少,而且集中在總線建模方面,也可以看到多核設(shè)計(jì)方面的建模方法。

除了上述總線、CPU架構(gòu)外,片內(nèi)或片外存儲(chǔ)器同樣是系統(tǒng)關(guān)鍵模塊,對(duì)系統(tǒng)性能有著至關(guān)重要的影響。文獻(xiàn)[6]對(duì)SystemClick框架做了擴(kuò)展,從而通過存儲(chǔ)器模型能夠分析共享存儲(chǔ)器對(duì)性能的影響。文獻(xiàn)[7]針對(duì)多通道DRAM做了建模,并且分析了不同的配置和使用情況對(duì)性能的影響。這兩篇文獻(xiàn)都對(duì)所設(shè)計(jì)的模型做了詳盡的分析,具有很好的參考價(jià)值,但是兩者的通用性欠佳。本文提出了一個(gè)可配置的通用存儲(chǔ)器SystemC模型。

2 SystemC

SystemC可被視作C++硬件建模和仿真的擴(kuò)展庫,特別適合集成電路的建模,但它事實(shí)上可以用來描述更多的系統(tǒng)。SystemC通過確定仿真核心(simulation kernel)算法定義了處理并行事件和仿真時(shí)間的機(jī)制。SystemC還定義了模塊、端口、接口、通道等概念來組成一個(gè)復(fù)雜SoC的連接關(guān)系和層次結(jié)構(gòu)。因此,它解決了標(biāo)準(zhǔn)C++語言用于復(fù)雜硬件建模時(shí)的難題。

3存儲(chǔ)器的建模

3.1存儲(chǔ)器模型概述

為了能幫助設(shè)計(jì)人員分析系統(tǒng)性能并選擇最合適的存儲(chǔ)器構(gòu)造,存儲(chǔ)器模型需要反映出對(duì)性能造成影響的關(guān)鍵參數(shù),即帶寬、延時(shí)和仲裁機(jī)制。而這些參數(shù)又是由存儲(chǔ)器的結(jié)構(gòu)以及其它參數(shù)決定的。另一方面,本文希望提出一個(gè)通用的存儲(chǔ)器模型,因此會(huì)有更多的參數(shù)用于配置存儲(chǔ)器以模擬某種特定類型的存儲(chǔ)器特征,比如多端口SRAM.

圖1給出了所設(shè)計(jì)的存儲(chǔ)器模型的結(jié)構(gòu)。它包括三個(gè)部分:一是模型接口;二是端口及bank可配置的存儲(chǔ)器;三是由讀寫通路及仲裁機(jī)制構(gòu)成的存儲(chǔ)器控制器。接口部分采用了事務(wù)級(jí)建模,而內(nèi)部模塊采用了時(shí)鐘精準(zhǔn)的建模,這樣在保證時(shí)間精度的同時(shí),方便了接口連接以及提高了仿真速度。

圖1可配置存儲(chǔ)器模型結(jié)構(gòu)

3.2存儲(chǔ)器接口

基于SystemC的存儲(chǔ)器模型接口,由SystemC定義的接口基類派生而來。整個(gè)存儲(chǔ)器模型是一個(gè)SystemC模塊,由于實(shí)現(xiàn)了所定義的存儲(chǔ)器模型接口,它成為SystemC概念中的hierarchal channel.因此,該存儲(chǔ)器模型將如同其它SystemC定義的通道,比如FIFO,一樣作為基本組件來連接其它的模塊從而構(gòu)造出SoC硬件系統(tǒng)。所設(shè)計(jì)存儲(chǔ)器具有如下所述事務(wù)級(jí)SystemC接口。

阻塞讀接口:該接口用來讀取給定地址的給定大小的數(shù)據(jù),當(dāng)數(shù)據(jù)沒有讀出時(shí),調(diào)用這個(gè)接口的模塊線程將被堵塞,直到數(shù)據(jù)讀出為止。除了地址和數(shù)據(jù),該接口還包含調(diào)用者的標(biāo)志信息。

非阻塞讀接口:與阻塞讀接口不同的是,如果在調(diào)用時(shí)讀指令不能被接受,則返回失敗。否則,不等待數(shù)據(jù)返回便成功退出。這樣調(diào)用接口的模塊線程可以在等待時(shí)間做其它事情。調(diào)用者通過監(jiān)聽存儲(chǔ)器模型廣播的當(dāng)前讀出數(shù)據(jù)多對(duì)應(yīng)調(diào)用者標(biāo)記來在之后讀出數(shù)據(jù)。

阻塞寫接口:該接口用來向存儲(chǔ)器給定地址寫入給定大小的數(shù)據(jù)。當(dāng)指令或?qū)憯?shù)據(jù)不能被存儲(chǔ)器模型接收時(shí),調(diào)用的線程被堵塞直到接受為止。除了地址和數(shù)據(jù),該接口還包含調(diào)用者的標(biāo)志信息。

非阻塞寫接口:與阻塞寫接口不同的是,當(dāng)指令或數(shù)據(jù)不能被接受時(shí),返回失敗而不等待。否則返回成功。

復(fù)位接口:用于復(fù)位存儲(chǔ)器模型。

為了不強(qiáng)制要求外部提供存儲(chǔ)器模型需要的時(shí)鐘,存儲(chǔ)器模型接口中不包含時(shí)鐘輸入。模型內(nèi)部有一個(gè)專門的時(shí)鐘產(chǎn)生線程。

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- FPGA中嵌入式塊存儲(chǔ)器的設(shè)計(jì)

- PLC系統(tǒng)存儲(chǔ)器與用戶存儲(chǔ)器的功能

- 存儲(chǔ)器介紹

- 嵌入式發(fā)動(dòng)機(jī)活塞溫度測試系統(tǒng)設(shè)計(jì)方案 22次下載

- 基于ARM的嵌入式Web服務(wù)器設(shè)計(jì)方案 20次下載

- 嵌入式硬件系統(tǒng)教程之嵌入式存儲(chǔ)技術(shù)的詳細(xì)資料說明 14次下載

- 嵌入式存儲(chǔ)器設(shè)計(jì)方案匯總 0次下載

- 嵌入式視頻系統(tǒng)的設(shè)計(jì)方案匯總 0次下載

- 嵌入式芯片的存儲(chǔ)器映射 101次下載

- 嵌入式存儲(chǔ)器內(nèi)建自修復(fù)技術(shù) 53次下載

- 采用嵌入式測試器實(shí)現(xiàn)SoC中存儲(chǔ)子系統(tǒng)的良品率設(shè)計(jì)

- 嵌入式存儲(chǔ)器發(fā)展現(xiàn)狀

- 嵌入式存儲(chǔ)器內(nèi)建自測試的一種新型應(yīng)用

- FPGA中嵌入式存儲(chǔ)器模塊的設(shè)計(jì)

- 嵌入式系統(tǒng)中基于FAT 表的存儲(chǔ)器管理

- 汽車SoC嵌入式存儲(chǔ)器的優(yōu)化診斷策略 701次閱讀

- 采用嵌入式相變存儲(chǔ)器的BEOL e-NVM解決方案 1515次閱讀

- 基于嵌入式環(huán)境的WiFi通信設(shè)計(jì)方案詳解 5593次閱讀

- 基于SCADE模型的高安全性嵌入式軟件解決方案設(shè)計(jì) 2665次閱讀

- 隨機(jī)存儲(chǔ)器在嵌入式操作系統(tǒng)中的應(yīng)用設(shè)計(jì)詳解 1315次閱讀

- 基于Linux操作系統(tǒng)平臺(tái)上的嵌入式網(wǎng)絡(luò)存儲(chǔ)器設(shè)計(jì)詳解 877次閱讀

- 嵌入式存儲(chǔ)器的全面解析 1.1w次閱讀

- 液晶顯示屏設(shè)計(jì)方案:基于Nios嵌入式軟核處理器 1081次閱讀

- 基于ASIC和SoC設(shè)計(jì)的嵌入式存儲(chǔ)器優(yōu)化解析 956次閱讀

- 嵌入式存儲(chǔ)器的主要設(shè)計(jì)標(biāo)準(zhǔn)分析及IP選用指南 1508次閱讀

- 嵌入式存儲(chǔ)器的設(shè)計(jì)方法和策略 1790次閱讀

- 一種嵌入式Web服務(wù)器的設(shè)計(jì)方案 4151次閱讀

- 為ASIC和SoC設(shè)計(jì)實(shí)現(xiàn)最佳化嵌入式存儲(chǔ)器 2994次閱讀

- MAXQ構(gòu)架上閃存和SRAM存儲(chǔ)器的分配 2425次閱讀

- TPMS外置編碼存儲(chǔ)器式輪胎定位技術(shù)設(shè)計(jì)方案 994次閱讀

下載排行

本周

- 1TC358743XBG評(píng)估板參考手冊(cè)

- 1.36 MB | 330次下載 | 免費(fèi)

- 2開關(guān)電源基礎(chǔ)知識(shí)

- 5.73 MB | 6次下載 | 免費(fèi)

- 3100W短波放大電路圖

- 0.05 MB | 4次下載 | 3 積分

- 4嵌入式linux-聊天程序設(shè)計(jì)

- 0.60 MB | 3次下載 | 免費(fèi)

- 5基于FPGA的光纖通信系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)

- 0.61 MB | 2次下載 | 免費(fèi)

- 6基于FPGA的C8051F單片機(jī)開發(fā)板設(shè)計(jì)

- 0.70 MB | 2次下載 | 免費(fèi)

- 751單片機(jī)窗簾控制器仿真程序

- 1.93 MB | 2次下載 | 免費(fèi)

- 8基于51單片機(jī)的RGB調(diào)色燈程序仿真

- 0.86 MB | 2次下載 | 免費(fèi)

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費(fèi)

- 2555集成電路應(yīng)用800例(新編版)

- 0.00 MB | 33564次下載 | 免費(fèi)

- 3接口電路圖大全

- 未知 | 30323次下載 | 免費(fèi)

- 4開關(guān)電源設(shè)計(jì)實(shí)例指南

- 未知 | 21548次下載 | 免費(fèi)

- 5電氣工程師手冊(cè)免費(fèi)下載(新編第二版pdf電子書)

- 0.00 MB | 15349次下載 | 免費(fèi)

- 6數(shù)字電路基礎(chǔ)pdf(下載)

- 未知 | 13750次下載 | 免費(fèi)

- 7電子制作實(shí)例集錦 下載

- 未知 | 8113次下載 | 免費(fèi)

- 8《LED驅(qū)動(dòng)電路設(shè)計(jì)》 溫德爾著

- 0.00 MB | 6653次下載 | 免費(fèi)

總榜

- 1matlab軟件下載入口

- 未知 | 935054次下載 | 免費(fèi)

- 2protel99se軟件下載(可英文版轉(zhuǎn)中文版)

- 78.1 MB | 537796次下載 | 免費(fèi)

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費(fèi)

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費(fèi)

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費(fèi)

- 6電路仿真軟件multisim 10.0免費(fèi)下載

- 340992 | 191185次下載 | 免費(fèi)

- 7十天學(xué)會(huì)AVR單片機(jī)與C語言視頻教程 下載

- 158M | 183278次下載 | 免費(fèi)

- 8proe5.0野火版下載(中文版免費(fèi)下載)

- 未知 | 138040次下載 | 免費(fèi)

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問

提問  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評(píng)論