資料介紹

元器件布局的10條規(guī)則:

遵照“先大后小,先難后易”的布置原則,即重要的單元電路、核心元器件應(yīng)當(dāng)優(yōu)先布局。

布局中應(yīng)參考原理框圖,根據(jù)單板的主信號(hào)流向規(guī)律安排主要元器件。

元器件的排列要便于調(diào)試和維修,亦即小元件周?chē)荒芊胖么笤⑿枵{(diào)試的元、器件周?chē)凶銐虻目臻g。

相同結(jié)構(gòu)電路部分,盡可能采用“對(duì)稱(chēng)式”標(biāo)準(zhǔn)布局,按照均勻分布、重心平衡、版面美觀的標(biāo)準(zhǔn)優(yōu)化布局。

同類(lèi)型插裝元器件在X或Y方向上應(yīng)朝一個(gè)方向放置。同一種類(lèi)型的有極性 分立元件也要力爭(zhēng)在X或Y方向上保持一致,便于生產(chǎn)和檢驗(yàn)。

發(fā)熱元件要一般應(yīng)均勻分布,以利于單板和整機(jī)的散熱,除溫度檢測(cè)元件以外的溫度敏感器件應(yīng)遠(yuǎn)離發(fā)熱量大的元器件。

布局應(yīng)盡量滿足以下要求:總的連線盡可能短,關(guān)鍵信號(hào)線最短;高電壓、大電流信號(hào)與小電流,低電壓的弱信號(hào)完全分開(kāi);模擬信號(hào)與數(shù)字信號(hào)分開(kāi);高頻信號(hào)與低頻信號(hào)分開(kāi);高頻元器件的間隔要充分。

去偶電容的布局要盡量靠近IC的電源管腳,并使之與電源和地之間形成的回路最短。

元件布局時(shí),應(yīng)適當(dāng)考慮使用同一種電源的器件盡量放在一起, 以便于將來(lái)的電源分隔。

布線

1. 布線優(yōu)先次序

鍵信號(hào)線優(yōu)先:摸擬小信號(hào)、高速信號(hào)、時(shí)鐘信號(hào)和同步信號(hào)等關(guān)鍵信號(hào)優(yōu)先布線。

密度優(yōu)先原則:從單板上連接關(guān)系最復(fù)雜的器件著手布線。從單板上連線 最密集的區(qū)域開(kāi)始布線。

注意點(diǎn):

盡量為時(shí)鐘信號(hào)、高頻信號(hào)、敏感信號(hào)等關(guān)鍵信號(hào)提供專(zhuān)門(mén)的布線層,并保證其最小的回路面積。必要時(shí)應(yīng)采取手工優(yōu)先布線、屏蔽和加大安全間距等方法。保證信號(hào)質(zhì)量。

電源層和地層之間的EMC環(huán)境較差,應(yīng)避免布置對(duì)干擾敏感的信號(hào)。

有阻抗控制要求的網(wǎng)絡(luò)應(yīng)盡量按線長(zhǎng)線寬要求布線。

2. 四種具體走線方式

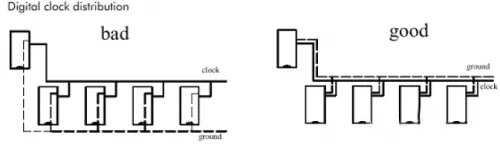

1 )時(shí)鐘的布線:

時(shí)鐘線是對(duì)EMC 影響最大的因素之一。在時(shí)鐘線上應(yīng)少打過(guò)孔,盡量避免和其它信號(hào)線并行走線,且應(yīng)遠(yuǎn)離一般信號(hào)線,避免對(duì)信號(hào)線的干擾。同時(shí)應(yīng)避開(kāi)板上的電源部分,以防止電源和時(shí)鐘互相干擾。

如果板上有專(zhuān)門(mén)的時(shí)鐘發(fā)生芯片,其下方不可走線,應(yīng)在其下方鋪銅,必要時(shí)還可以對(duì)其專(zhuān)門(mén)割地。對(duì)于很多芯片都有參考的晶體振蕩器,這些晶振下方也不應(yīng)走線,要鋪銅隔離。

2)直角走線:

直角走線一般是PCB布線中要求盡量避免的情況,也幾乎成為衡量布線好壞的標(biāo)準(zhǔn)之一,那么直角走線究竟會(huì)對(duì)信號(hào)傳輸產(chǎn)生多大的影響呢?

從原理上說(shuō),直角走線會(huì)使傳輸線的線寬發(fā)生變化,造成阻抗的不連續(xù)。其實(shí)不光是直角走線,頓角,銳角走線都可能會(huì)造成阻抗變化的情況。

直角走線的對(duì)信號(hào)的影響就是主要體現(xiàn)在三個(gè)方面:

拐角可以等效為傳輸線上的容性負(fù)載,減緩上升時(shí)間;阻抗不連續(xù)會(huì)造成信號(hào)的反射;直角尖端產(chǎn)生的EMI。

3)差分走線:

差分信號(hào)(Differential Signal)在高速電路設(shè)計(jì)中的應(yīng)用越來(lái)越廣泛,電路中最關(guān)鍵的信號(hào)往往都要采用差分結(jié)構(gòu)設(shè)計(jì)。

定義:通俗地說(shuō),就是驅(qū)動(dòng)端發(fā)送兩個(gè)等值、反相的信號(hào),接收端通過(guò)比較這兩個(gè)電壓的差值來(lái)判斷邏輯狀態(tài)“0”還是“1”。而承載差分信號(hào)的那一對(duì)走線就稱(chēng)為差分走線。

差分信號(hào)和普通的單端信號(hào)走線相比,最明顯的優(yōu)勢(shì)體現(xiàn)在以下三個(gè)方面:

抗干擾能力強(qiáng),因?yàn)閮筛罘肿呔€之間的耦合很好,當(dāng)外界存在噪聲干擾時(shí),幾乎是同時(shí)被耦合到兩條線上,而接收端關(guān)心的只是兩信號(hào)的差值,所以外界的共模噪聲可以被完全抵消。

能有效抑制EMI,同樣的道理,由于兩根信號(hào)的極性相反,他們對(duì)外輻射的電磁場(chǎng)可以相互抵消,耦合的越緊密,泄放到外界的電磁能量越少。

時(shí)序定位精確,由于差分信號(hào)的開(kāi)關(guān)變化是位于兩個(gè)信號(hào)的交點(diǎn),而不像普通單端信號(hào)依靠高低兩個(gè)閾值電壓判斷,因而受工藝,溫度的影響小,能降低時(shí)序上的誤差,同時(shí)也更適合于低幅度信號(hào)的電路。

目前流行的LVDS(low voltage differential signaling)就是指這種小振幅差分信號(hào)技術(shù)。

對(duì)于PCB工程師來(lái)說(shuō),最關(guān)注的還是如何確保在實(shí)際走線中能完全發(fā)揮差分走線的這些優(yōu)勢(shì)。也許只要是接觸過(guò)Layout的人都會(huì)了解差分走線的一般要求,那就是“等長(zhǎng)、等距”。

等長(zhǎng)是為了保證兩個(gè)差分信號(hào)時(shí)刻保持相反極性,減少共模分量;等距則主要是為了保證兩者差分阻抗一致,減少反射。“盡量靠近原則”有時(shí)候也是差分走線的要求之一。

4)蛇形線:

蛇形線是Layout中經(jīng)常使用的一類(lèi)走線方式。其主要目的就是為了調(diào)節(jié)延時(shí),滿足系統(tǒng)時(shí)序設(shè)計(jì)要求。

設(shè)計(jì)者首先要有這樣的認(rèn)識(shí):蛇形線會(huì)破壞信號(hào)質(zhì)量,改變傳輸延時(shí),布線時(shí)要盡量避免使用。

但實(shí)際設(shè)計(jì)中,為了保證信號(hào)有足夠的保持時(shí)間,或者減小同組信號(hào)之間的時(shí)間偏移,往往不得不故意進(jìn)行繞線。

注意點(diǎn):

成對(duì)出現(xiàn)的差分信號(hào)線,一般平行走線,盡量少打過(guò)孔,必須打孔時(shí),應(yīng)兩線一同打孔,以做到阻抗匹配。

相同屬性的一組總線,應(yīng)盡量并排走線,做到盡量等長(zhǎng)。從貼片焊盤(pán)引出的過(guò)孔盡量離焊盤(pán)遠(yuǎn)些。

3. 布線常用規(guī)則

1)走線的方向控制規(guī)則:

即相鄰層的走線方向成正交結(jié)構(gòu)。避免將不同的信號(hào)線在相鄰層走成同一方向,以減少不必要的層間竄擾;當(dāng)由于板結(jié)構(gòu)限制(如某些背板)難以避免出現(xiàn)該情況,特別是信號(hào)速率較高時(shí),應(yīng)考慮用地平面隔離各布線層,用地信號(hào)線隔離各信號(hào)線。

2)走線的開(kāi)環(huán)檢查規(guī)則:

一般不允許出現(xiàn)一端浮空的布線(Dangling Line), 主要是為了避免產(chǎn)生"天線效應(yīng)",減少不必要的干擾輻射和接受,否則可能帶來(lái)不可預(yù)知的結(jié)果。

3)阻抗匹配檢查規(guī)則:

同一網(wǎng)絡(luò)的布線寬度應(yīng)保持一致,線寬的變化會(huì)造成線路特性阻抗的不均勻,當(dāng)傳輸?shù)乃俣容^高時(shí)會(huì)產(chǎn)生反射,在設(shè)計(jì)中應(yīng)該盡量避免這種情況。

在某些條件下,如接插件引出線,BGA封裝的引出線類(lèi)似的結(jié)構(gòu)時(shí),可能無(wú)法避免線寬的變化,應(yīng)該盡量減少中間不一致部分的有效長(zhǎng)度。

4)走線長(zhǎng)度控制規(guī)則:

即短線規(guī)則,在設(shè)計(jì)時(shí)應(yīng)該盡量讓布線長(zhǎng)度盡量短,以減少由于走線過(guò)長(zhǎng)帶來(lái)的干擾問(wèn)題,特別是一些重要信號(hào)線,如時(shí)鐘線,務(wù)必將其振蕩器放在離器件很近的地方。

對(duì)驅(qū)動(dòng)多個(gè)器件的情況,應(yīng)根據(jù)具體情況決定采用何種網(wǎng)絡(luò)拓?fù)浣Y(jié)構(gòu)。

5)倒角規(guī)則:

PCB設(shè)計(jì)中應(yīng)避免產(chǎn)生銳角和直角, 產(chǎn)生不必要的輻射,同時(shí)工藝性能也不好。

6)器件去耦規(guī)則:

在印制版上增加必要的去耦電容,濾除電源上的干擾信號(hào),使電源信號(hào)穩(wěn)定。

在多層板中,對(duì)去耦電容的位置一般要求不太高,但對(duì)雙層板,去藕電容的布局及電源的布線方式將直接影響到整個(gè)系統(tǒng)的穩(wěn)定性,有時(shí)甚至關(guān)系到設(shè)計(jì)的成敗。

在雙層板設(shè)計(jì)中,一般應(yīng)該使電流先經(jīng)過(guò)濾波電容濾波再供器件使用。

在高速電路設(shè)計(jì)中,能否正確地使用去耦電容,關(guān)系到整個(gè)板的穩(wěn)定性。

7)器件布局分區(qū)/分層規(guī)則:

主要是為了防止不同工作頻率的模塊之間的互相干擾,同時(shí)盡量縮短高頻部分的布線長(zhǎng)度。

對(duì)混合電路,也有將模擬與數(shù)字電路分別布置在印制板的兩面,分別使用不同的層布線,中間用地層隔離的方式。

8)地線回路規(guī)則:

環(huán)路最小規(guī)則,即信號(hào)線與其回路構(gòu)成的環(huán)面積要盡可能小,環(huán)面積越小,對(duì)外的輻射越少,接收外界的干擾也越小。

9)電源與地線層的完整性規(guī)則:

對(duì)于導(dǎo)通孔密集的區(qū)域,要注意避免孔在電源和地層的挖空區(qū)域相互連接,形成對(duì)平面層的分割,從而破壞平面層的完整性,并進(jìn)而導(dǎo)致信號(hào)線在地層的回路面積增大。

10)3W規(guī)則:

為了減少線間串?dāng)_,應(yīng)保證線間距足夠大,當(dāng)線中心間距不少于3倍線寬時(shí),則可保持70%的電場(chǎng)不互相干擾,稱(chēng)為3W規(guī)則。如要達(dá)到98%的電場(chǎng)不互相干擾,可使用10W的間距。

11)屏蔽保護(hù)

對(duì)應(yīng)地線回路規(guī)則,實(shí)際上也是為了盡量減小信號(hào)的回路面積,多見(jiàn)于一些比較重要的信號(hào),如時(shí)鐘信號(hào),同步信號(hào)。

對(duì)一些特別重要,頻率特別高的信號(hào),應(yīng)該考慮采用銅軸電纜屏蔽結(jié)構(gòu)設(shè)計(jì),即將所布的線上下左右用地線隔離,而且還要考慮好如何有效的讓屏蔽地與實(shí)際地平面有效結(jié)合。

12)走線終結(jié)網(wǎng)絡(luò)規(guī)則:

在高速數(shù)字電路中, 當(dāng)PCB布線的延遲時(shí)間大于信號(hào)上升時(shí)間(或下降時(shí)間) 的1/4時(shí),該布線即可以看成傳輸線,為了保證信號(hào)的輸入和輸出阻抗與傳輸線的阻抗正確匹配,可以采用多種形式的匹配方法, 所選擇的匹配方法與網(wǎng)絡(luò)的連接方式和布線的拓樸結(jié)構(gòu)有關(guān)。

對(duì)于點(diǎn)對(duì)點(diǎn)(一個(gè)輸出對(duì)應(yīng)一個(gè)輸入) 連接, 可以選擇始端串聯(lián)匹配或終端并聯(lián)匹配。前者結(jié)構(gòu)簡(jiǎn)單,成本低,但延遲較大。后者匹配效果好,但結(jié)構(gòu)復(fù)雜,成本較高。

對(duì)于點(diǎn)對(duì)多點(diǎn)(一個(gè)輸出對(duì)應(yīng)多個(gè)輸出) 連接, 當(dāng)網(wǎng)絡(luò)的拓樸結(jié)構(gòu)為菊花鏈時(shí),應(yīng)選擇終端并聯(lián)匹配。當(dāng)網(wǎng)絡(luò)為星型結(jié)構(gòu)時(shí),可以參考點(diǎn)對(duì)點(diǎn)結(jié)構(gòu)。

星形和菊花鏈為兩種基本的拓?fù)浣Y(jié)構(gòu), 其他結(jié)構(gòu)可看成基本結(jié)構(gòu)的變形, 可采取一些靈活措施進(jìn)行匹配。

在實(shí)際操作中要兼顧成本、 功耗和性能等因素, 一般不追求完全匹配,只要將失配引起的反射等干擾限制在可接受的范圍即可。

13)走線閉環(huán)檢查規(guī)則:

防止信號(hào)線在不同層間形成自環(huán)。在多層板設(shè)計(jì)中容易發(fā)生此類(lèi)問(wèn)題, 自環(huán)將引起輻射干擾。

14)走線的分枝長(zhǎng)度控制規(guī)則:

盡量控制分枝的長(zhǎng)度,一般的要求是Tdelay<=Trise/20。

15)走線的諧振規(guī)則:

主要針對(duì)高頻信號(hào)設(shè)計(jì)而言, 即布線長(zhǎng)度不得與其波長(zhǎng)成整數(shù)倍關(guān)系, 以免產(chǎn)生諧振現(xiàn)象。

16)孤立銅區(qū)控制規(guī)則:

孤立銅區(qū)的出現(xiàn), 將帶來(lái)一些不可預(yù)知的問(wèn)題, 因此將孤立銅區(qū)與別的信號(hào)相接, 有助于改善信號(hào)質(zhì)量,通常是將孤立銅區(qū)接地或刪除。

在實(shí)際的制作中, PCB廠家將一些板的空置部分增加了一些銅箔,這主要是為了方便印制板加工,同時(shí)對(duì)防止印制板翹曲也有一定的作用。

17)重疊電源與地線層規(guī)則:

不同電源層在空間上要避免重疊。主要是為了減少不同電源之間的干擾, 特別是一些電壓相差很大的電源之間, 電源平面的重疊問(wèn)題一定要設(shè)法避免, 難以避免時(shí)可考慮中間隔地層。

18)20H規(guī)則:

由于電源層與地層之間的電場(chǎng)是變化的, 在板的邊緣會(huì)向外輻射電磁干擾。稱(chēng)為邊沿效應(yīng)。

解決的辦法是將電源層內(nèi)縮, 使得電場(chǎng)只在接地層的范圍內(nèi)傳導(dǎo)。以一個(gè)H(電源和地之間的介質(zhì)厚度)為單位,若內(nèi)縮20H則可以將70%的電場(chǎng)限制在接地層邊沿內(nèi);內(nèi)縮100H則可以將98%的電場(chǎng)限制在內(nèi)。

4. 其他

對(duì)于單雙層板電源線應(yīng)盡量粗而短。電源線和地線的寬度要求可以根據(jù)1mm的線寬最大對(duì)應(yīng)1A 的電流來(lái)計(jì)算,電源和地構(gòu)成的環(huán)路盡量小。

為了防止電源線較長(zhǎng)時(shí),電源線上的耦合雜訊直接進(jìn)入負(fù)載器件,應(yīng)在進(jìn)入每個(gè)器件之前,先對(duì)電源去藕。且為了防止它們彼此間的相互干擾,對(duì)每個(gè)負(fù)載的電源獨(dú)立去藕,并做到先濾波再進(jìn)入負(fù)載。

- PCB布線知識(shí)大全

- 7條實(shí)用的PCB布線規(guī)則

- PCB設(shè)計(jì)中布局布線實(shí)際技巧以及相關(guān)規(guī)則

- PCB電路板元件布局布線基本規(guī)則下載 0次下載

- PCB設(shè)計(jì)布局布線規(guī)則小總結(jié)資料下載

- PCB手動(dòng)布線規(guī)則 0次下載

- PCB繪制-布局布線規(guī)則 0次下載

- 高頻PCB板布線規(guī)則 0次下載

- EMI相關(guān)PCB布局布線規(guī)則 0次下載

- 高頻在PCB中的布線規(guī)則 0次下載

- PCB板基礎(chǔ)知識(shí)、布局原則、布線技巧、設(shè)計(jì)規(guī)則 0次下載

- Protel DXP布線規(guī)則設(shè)置 0次下載

- DDR布局布線規(guī)則與實(shí)例 0次下載

- protel se的布線規(guī)則 0次下載

- PADS 2005高速布線規(guī)則全集 0次下載

- 詳解Xpedition規(guī)則驅(qū)動(dòng)設(shè)計(jì) 1w次閱讀

- 進(jìn)行PCB布線時(shí)應(yīng)遵循哪些相關(guān)規(guī)則 5568次閱讀

- 混合信號(hào)PCB設(shè)計(jì)的布局和布線方法解析 1859次閱讀

- PCB布線在電磁兼容性設(shè)計(jì)時(shí)應(yīng)該遵循哪些規(guī)則 1938次閱讀

- 高速電路設(shè)計(jì)的布線布局的具體步驟和處理方法介紹 1532次閱讀

- PCB布線教程及經(jīng)驗(yàn)分享 2.3w次閱讀

- PCB設(shè)計(jì)布局布線技巧分享 1.1w次閱讀

- 如何風(fēng)度翩翩的進(jìn)行PCB布線_PCB布線規(guī)則分享 3854次閱讀

- PCB設(shè)計(jì)中元器件布局的10條規(guī)則,布線的規(guī)則是什么? 1.6w次閱讀

- pcb自動(dòng)布線設(shè)置_設(shè)置線間距與寬度設(shè)置_pcb布局布線技巧 3.5w次閱讀

- pcb布線心得(流程詳解、元件布局布線與EMC) 3921次閱讀

- 如何畫(huà)雙層pcb板_雙層pcb板布線規(guī)則(操作技巧與案例分析) 3w次閱讀

- 新手必看:PLC初級(jí)布線規(guī)則 5910次閱讀

- 細(xì)述PCB板布局布線基本規(guī)則 3609次閱讀

- 高速ADC PCB的布局布線技巧 3587次閱讀

下載排行

本周

- 1電子電路原理第七版PDF電子教材免費(fèi)下載

- 0.00 MB | 1491次下載 | 免費(fèi)

- 2單片機(jī)典型實(shí)例介紹

- 18.19 MB | 95次下載 | 1 積分

- 3S7-200PLC編程實(shí)例詳細(xì)資料

- 1.17 MB | 27次下載 | 1 積分

- 4筆記本電腦主板的元件識(shí)別和講解說(shuō)明

- 4.28 MB | 18次下載 | 4 積分

- 5開(kāi)關(guān)電源原理及各功能電路詳解

- 0.38 MB | 11次下載 | 免費(fèi)

- 6100W短波放大電路圖

- 0.05 MB | 4次下載 | 3 積分

- 7基于單片機(jī)和 SG3525的程控開(kāi)關(guān)電源設(shè)計(jì)

- 0.23 MB | 4次下載 | 免費(fèi)

- 8基于AT89C2051/4051單片機(jī)編程器的實(shí)驗(yàn)

- 0.11 MB | 4次下載 | 免費(fèi)

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費(fèi)

- 2PADS 9.0 2009最新版 -下載

- 0.00 MB | 66304次下載 | 免費(fèi)

- 3protel99下載protel99軟件下載(中文版)

- 0.00 MB | 51209次下載 | 免費(fèi)

- 4LabView 8.0 專(zhuān)業(yè)版下載 (3CD完整版)

- 0.00 MB | 51043次下載 | 免費(fèi)

- 5555集成電路應(yīng)用800例(新編版)

- 0.00 MB | 33562次下載 | 免費(fèi)

- 6接口電路圖大全

- 未知 | 30320次下載 | 免費(fèi)

- 7Multisim 10下載Multisim 10 中文版

- 0.00 MB | 28588次下載 | 免費(fèi)

- 8開(kāi)關(guān)電源設(shè)計(jì)實(shí)例指南

- 未知 | 21539次下載 | 免費(fèi)

總榜

- 1matlab軟件下載入口

- 未知 | 935053次下載 | 免費(fèi)

- 2protel99se軟件下載(可英文版轉(zhuǎn)中文版)

- 78.1 MB | 537793次下載 | 免費(fèi)

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費(fèi)

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費(fèi)

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費(fèi)

- 6電路仿真軟件multisim 10.0免費(fèi)下載

- 340992 | 191183次下載 | 免費(fèi)

- 7十天學(xué)會(huì)AVR單片機(jī)與C語(yǔ)言視頻教程 下載

- 158M | 183277次下載 | 免費(fèi)

- 8proe5.0野火版下載(中文版免費(fèi)下載)

- 未知 | 138039次下載 | 免費(fèi)

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問(wèn)

提問(wèn)  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評(píng)論