信號(hào)回溝,即波形邊緣的非單調(diào)性,是時(shí)鐘的大忌,尤其是出現(xiàn)在信號(hào)的門限電平范圍內(nèi)時(shí),由于容易導(dǎo)致誤觸發(fā),更是兇險(xiǎn)無比。所以當(dāng)客戶測試發(fā)現(xiàn)時(shí)鐘信號(hào)回溝,抱著一心改板的沉痛心情找到高速先生時(shí),高速先生絲毫不敢大意,一番分析確認(rèn)之后,給出的答復(fù)卻讓客戶喜出望外:測試點(diǎn)的時(shí)鐘回溝是真實(shí)存在的,但是芯片得到的時(shí)鐘信號(hào)質(zhì)量卻沒有問題,簡而言之,單板的時(shí)鐘信號(hào)沒問題,可以放心使用。

?

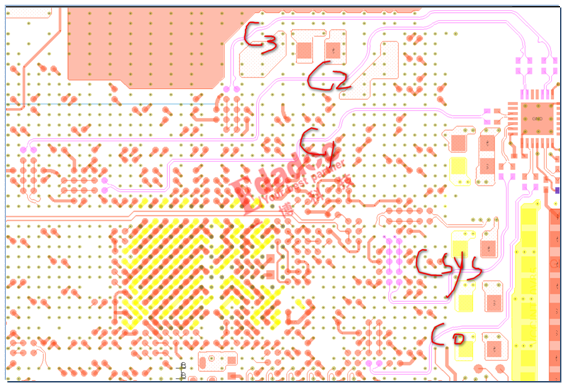

其實(shí),高速先生剛拿到單板時(shí)心里也沒底,因?yàn)闀r(shí)鐘信號(hào)頻率并不算低,有 400MHz,而且針對 5 路時(shí)鐘信號(hào)的設(shè)計(jì)查板也并未發(fā)現(xiàn)異常。

?

?

仿真初始階段,為了確認(rèn)模型的準(zhǔn)確性,首先對客戶提供的測試點(diǎn)上的波形進(jìn)行了仿真擬合,以 C0 通道時(shí)鐘為例,仿真波形的回溝如約而至,與測試波形的延時(shí)、回溝的位置基本一致,說明仿真建模沒有問題,看到這樣的結(jié)果,客戶的心開始下沉:回溝得到了仿真驗(yàn)證,這回沒得救了。

?

?

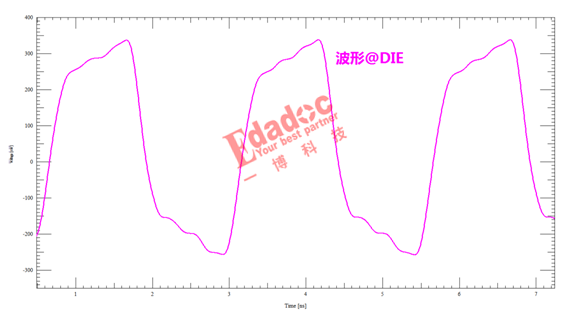

高速先生感覺可以再搶救一把,因?yàn)樽铌P(guān)鍵的芯片 DIE 上的時(shí)鐘波形還沒看到,還有一線生機(jī)。懷著忐忑的心情,高速先生按下了“Simulation”鍵,隨著 DIE 上的波形在屏幕上漸次展開,高速先生松了口氣,芯片上的時(shí)鐘回溝神奇的消失了!

?

?

看到這樣的結(jié)果,客戶既喜且疑,喜的是芯片上的時(shí)鐘信號(hào)正常,疑的是測試點(diǎn)明明就在芯片背面的過孔處,為何測試得到的時(shí)鐘波形會(huì)與芯片 DIE 上的天差地別?

?

測試最尷尬的莫過于“所測非所得”,出現(xiàn)這種情況,很多時(shí)候與測試點(diǎn)的位置選擇有關(guān),比如本案例:看起來芯片背面的過孔似乎距離芯片最近,最能反映芯片接收信號(hào)的真實(shí)情況,其實(shí)不然,我們最終需要關(guān)注的是芯片 DIE 上的信號(hào),而芯片的 DIE 與 PIN 之間還隔著千山萬水——芯片內(nèi)部封裝布線,尤其是封裝較大的 BGA 芯片,封裝布線的影響更加明顯,這也是很多芯片會(huì)提供封裝補(bǔ)償(Pin-delay)的原因

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問

提問  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻

上傳資料賺積分

上傳資料賺積分

評論