器件中的高功耗雖然是可以容忍的,但是在設(shè)計過程中,我們往往都在追求低功耗實現(xiàn)。上篇文章中,小編對MCU的低功耗設(shè)計有所解讀。為增進大家對功耗的了解程度,本文將對寄存器傳輸級低功耗設(shè)計方法予以介紹。

?

除了芯片的速度和面積等,人們對低功耗的期望也越來越高,因而在IC設(shè)計中加入低功耗設(shè)計非常必要。寄存器傳輸級的低功耗設(shè)計對降低整個芯片的功耗作用非常顯著,本文討論的三種寄存器傳輸級低功耗設(shè)計方法,經(jīng)驗證對動態(tài)功耗的降低很有效。

自集成電路問世以來,設(shè)計者在單個芯片上集成的晶體管的數(shù)量呈現(xiàn)出令人驚訝的增長速度。近30年,集成電路的發(fā)展一直遵循著“摩爾定律”:集成在芯片上的晶體管的數(shù)量每18個月就翻一番,芯片成本也相應(yīng)下降。

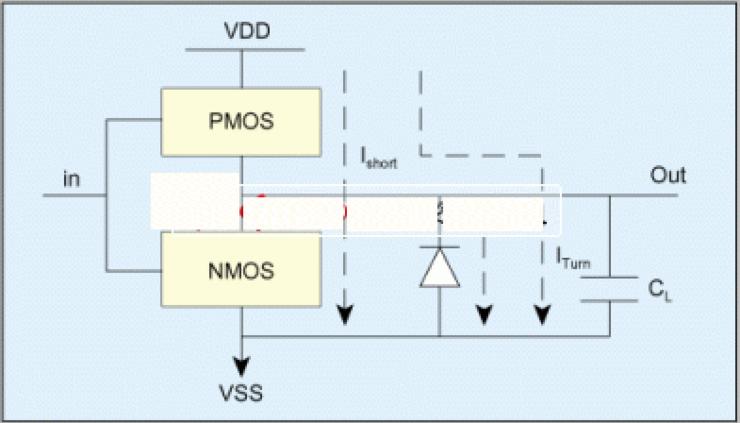

圖1:CMOS電路功耗的主要來源是動態(tài)功耗,由開關(guān)電流和短路電流造成

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問

提問  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻

上傳資料賺積分

上傳資料賺積分

評論