資料介紹

描述

您可能已經注意到,從版本 2021.1 開始,Vivado 中板預設文件的處理方式與 Xilinx Board Store 的引入略有不同。這是一個方便的添加,因為它意味著不再需要手動安裝各種常見 Xilinx、Digilent、Avnet 和 Trenz Electronics 板的板預設文件。您可以通過簡單地從板選擇中單擊“下載”來將它們安裝在創建新項目菜單中。

然而,由于Xilinx Board Store比較新,并且有其他供應商提供的基于 Xilinx 的開發板,因此仍然需要手動安裝板預設文件。這讓我有點難過,因為 Vivado 的文件結構也發生了變化,以前版本中手動安裝的舊目錄板預設文件不再存在。然而,在升級到 Vivado 2021.2 之后,我需要再次使用我的 ZynqberryZero,它恰好不在Xilinx Board Store 存儲庫中,這迫使我弄清楚板預設手動安裝。我在 Ubuntu 18.04 上運行 Vivado 2021.2。

添加電路板預設文件

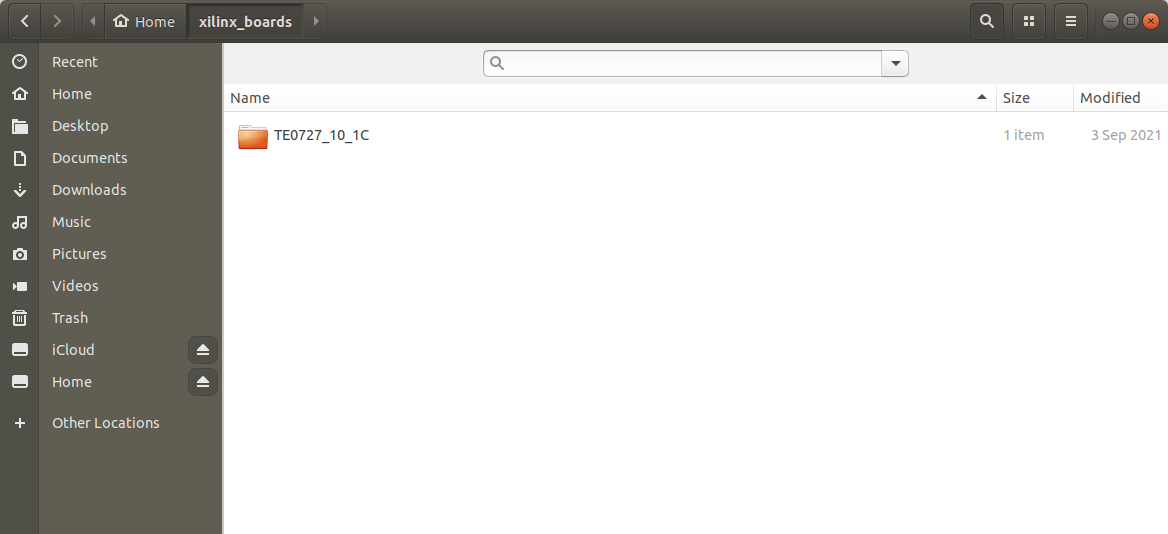

在易于記憶/訪問的地方為電路板預設文件創建本地目錄:

~$ mkdir -p xilinx_boards

將目標開發板的板子預設文件復制到其中:

~$ cp -R ./Downloads/zbzerodemo1/board_files/TE0727_10_1C ./xilinx_boards

獲取 Vivado 環境并啟動 Vivado,但不要打開項目。

~$ source /tools/Xilinx/Vitis/2021.2/settings64.sh

~$ vivado

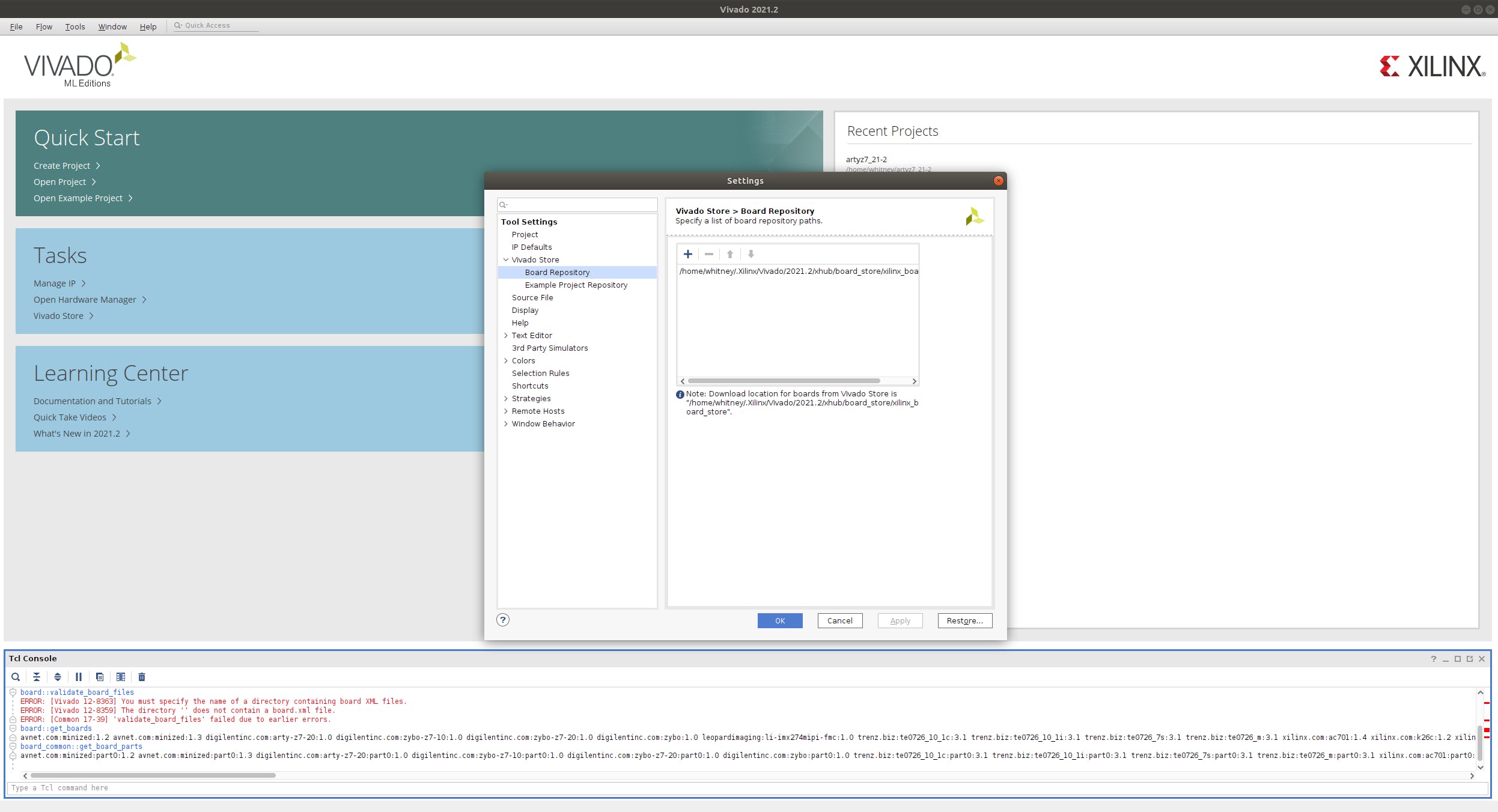

從工具菜單中選擇設置。

在“設置”菜單中,導航至Vivado Store > Board Repository 。

單擊+圖標并指向我們剛剛在彈出窗口中為電路板預設文件創建的本地目錄。單擊“選擇”返回“設置”窗口。

單擊Apply ,然后單擊 OK將更改保存到 Vivado 并關閉Settings窗口。

您會注意到已經指定了從Xilinx Board Store下載的電路板文件所在的目錄,剛剛創建的本地目錄將是 Vivado 在其中查找電路板預設文件的第二個位置。您現在可以簡單地復制任何新的電路板預設將文件復制到本地目錄,以便在以后的項目中使用。

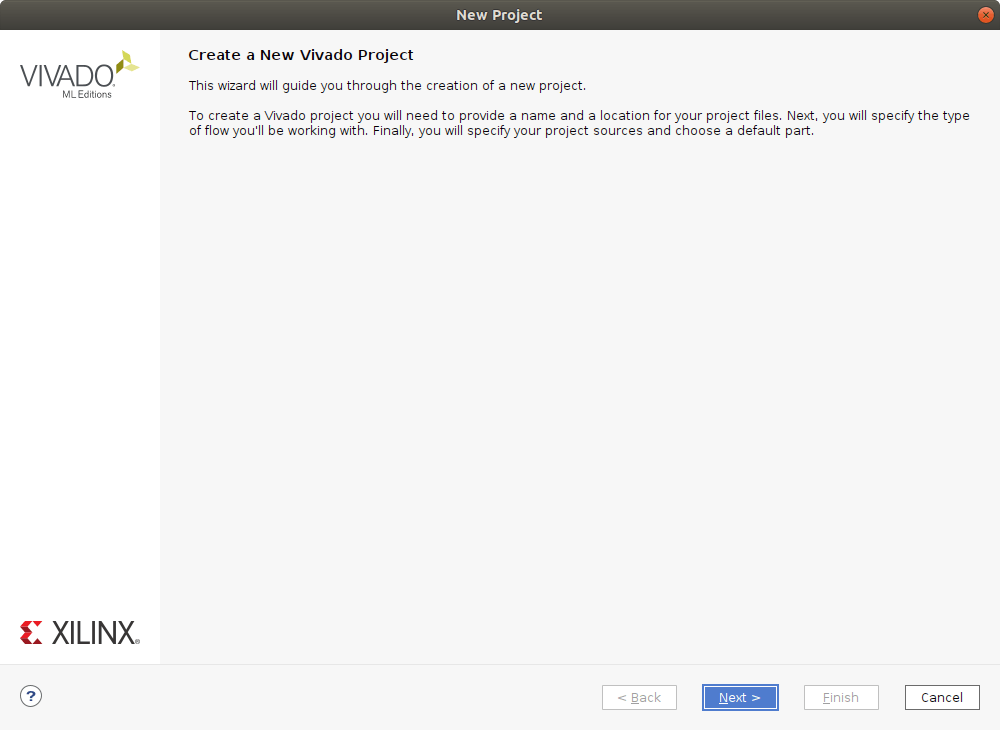

創建 Vivado 項目

要測試新的本地板預設目錄,請單擊創建項目。為其指定所需的名稱和項目位置,將其指定為RTL 項目并選中選項Do not specify sources at this time 。

對于Default Part ,切換到Boards選項卡并搜索TE0727 。選擇它并單擊下一步。

和成功!本地板預設存儲庫正在運行!

ZynqberryZero IP 存儲庫

由于 ZynqberryZero 的官方 IP 庫和塊設計 TCL 腳本尚不可用,我繼續手動升級它們并將它們附加到該項目。

在繼續 Vivado 項目中的設計之前,將下面附帶的 IP 庫復制到某個可訪問的位置。我個人喜歡將這樣的項目特定 IP 庫復制到我正在使用它們的相應 Vivado 項目目錄中。如果我使用一個來創建塊設計,我也會將塊設計 TCL 腳本放入 Vivado 項目目錄中在這種情況下。

將 IP 庫存儲庫和塊設計 TCL 腳本復制到項目中:

~$ mkdir -p //docs

~$ cp ./Downloads/zsys.tcl //docs

~$ cp -R ./Downloads/ip_lib //

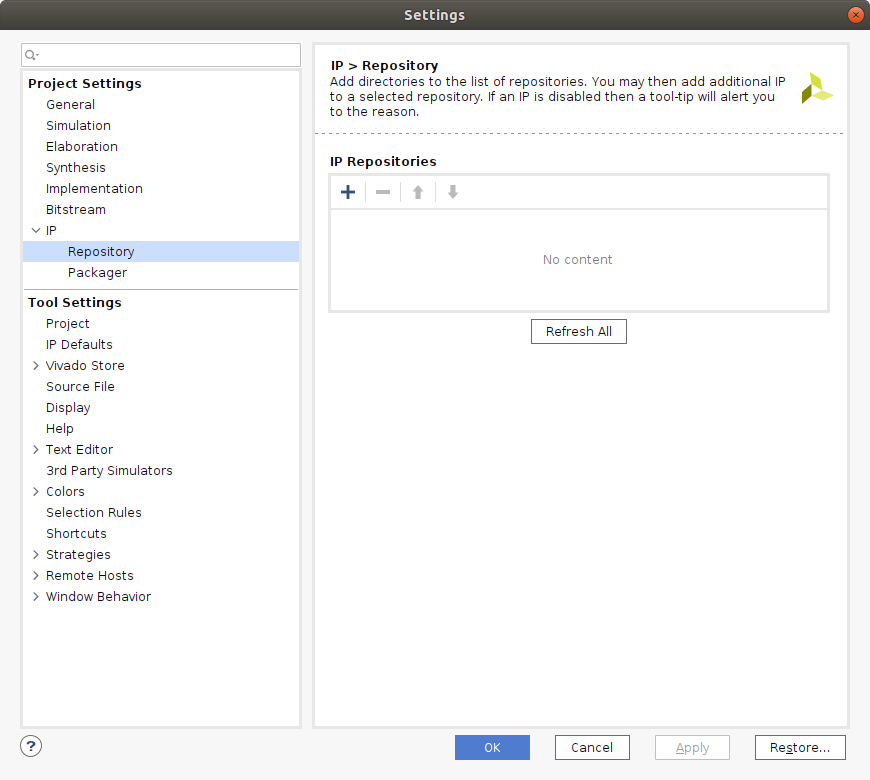

將 IP 庫復制到 Vivado 工程目錄后,需要將其作為有效的 IP 存儲庫添加到 Vivado 工程設置中。

在 Vivado 中打開設置,然后導航到IP下的存儲庫。單擊+按鈕并指向 IP 庫文件夾。

區塊設計

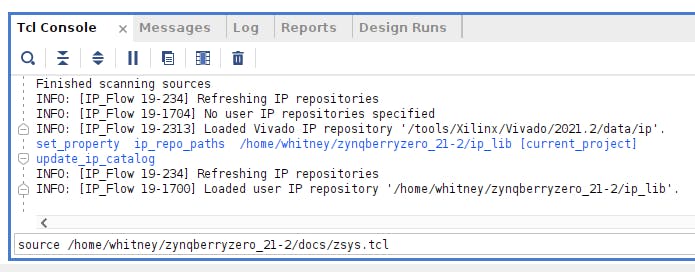

通過從 Vivado 項目的 TCL 控制臺運行以下命令,從 TCL 腳本為 ZynqberryZero 重新創建塊設計(從空白的新項目執行此操作,在運行此腳本之前不要單擊創建塊設計):

source //docs/zsys.tcl

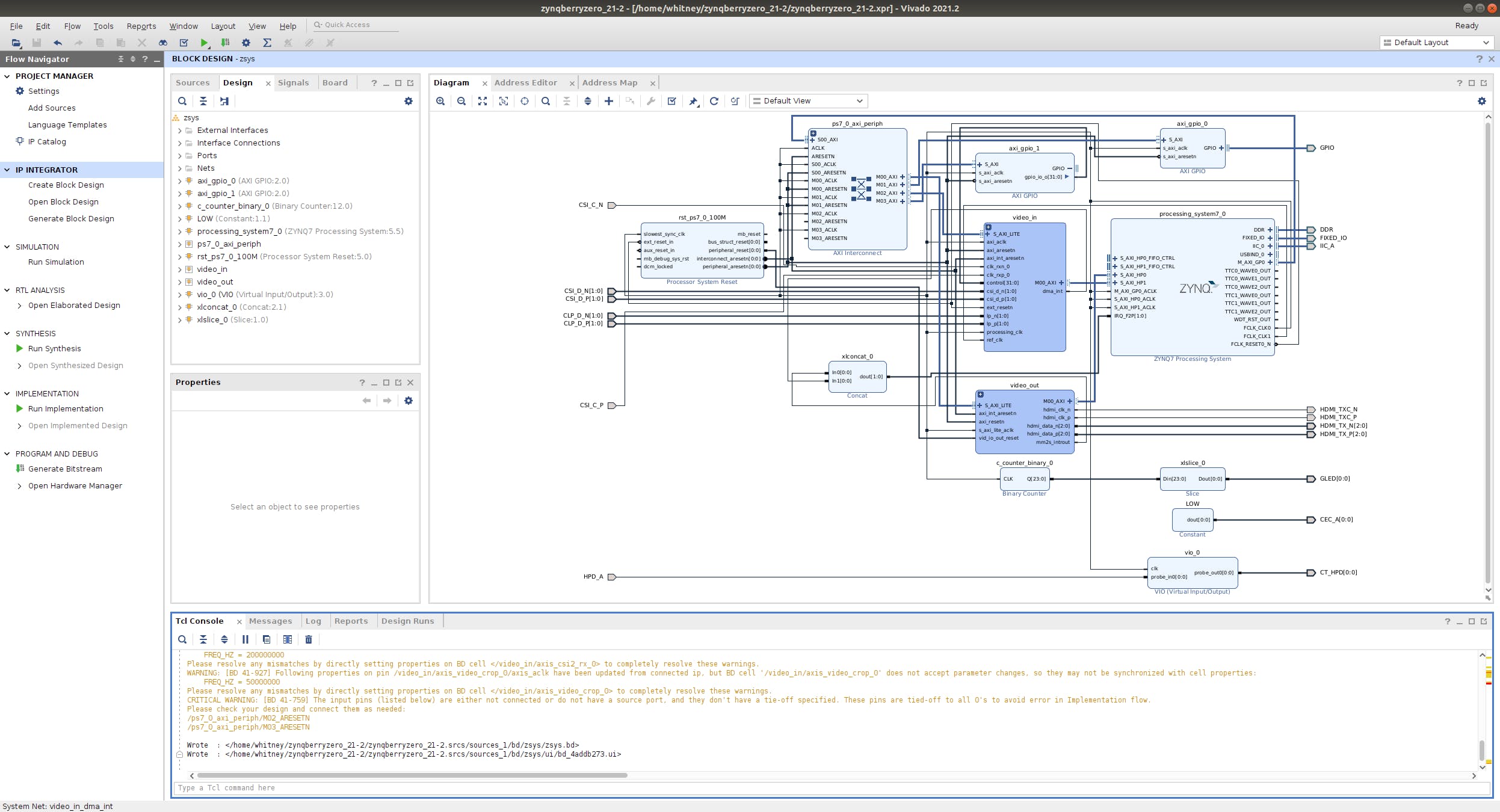

等待設計完全填充并發生所有連接。將有幾個關于如何連接重置線的嚴重警告,但現在可以忽略這些警告。

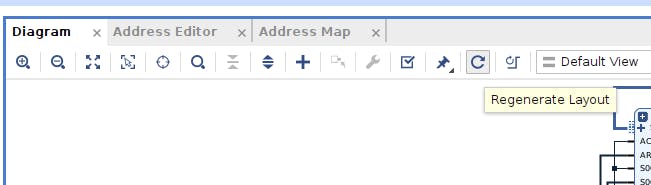

重新生成設計,使其看起來不那么凌亂:

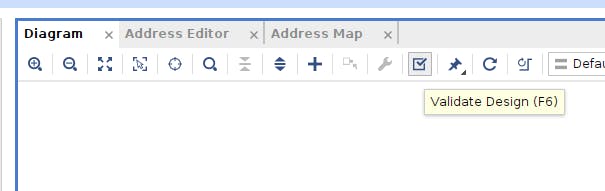

該腳本已經運行了設計驗證,但我仍然喜歡手動運行驗證以確保。

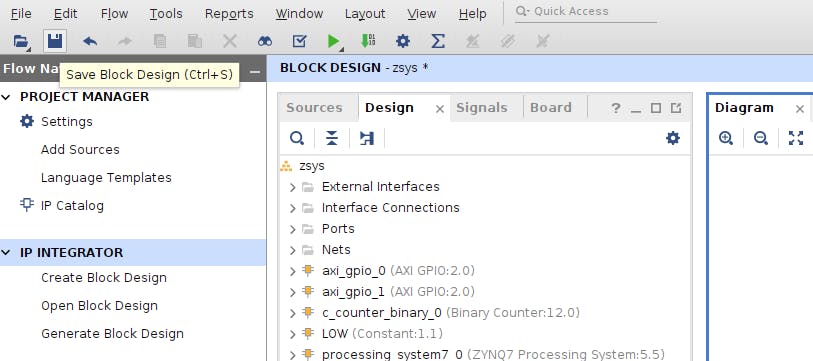

保存塊設計。

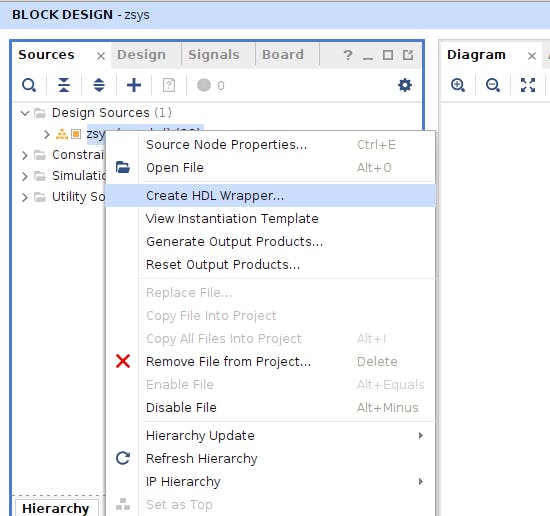

創建 HDL 包裝器以實例化項目中的模塊設計。右鍵單擊Sources選項卡中的模塊設計并選擇Create HDL Wrapper...

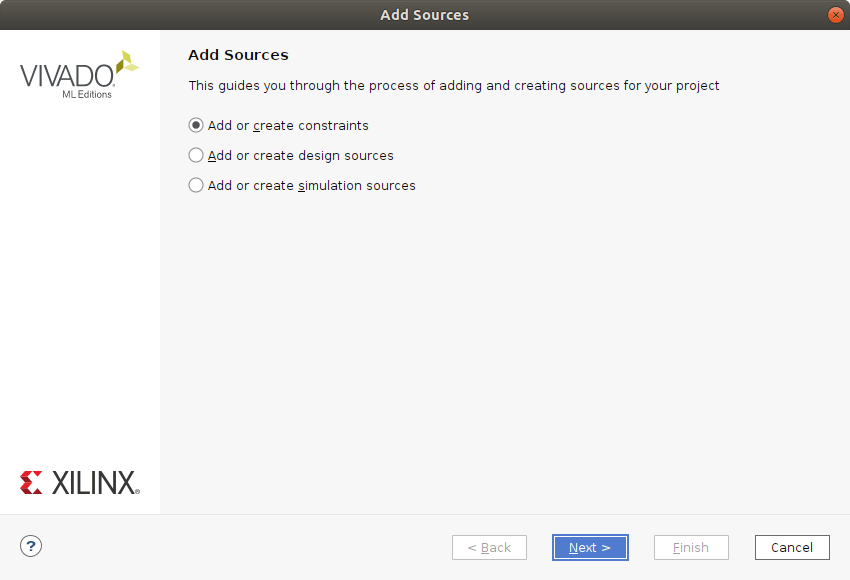

塊設計完成且頂層 HDL 包裝器就位后,需要添加設計約束以指定信號映射到 FPGA 上的封裝引腳等內容。

在Flow Navigator窗口中,單擊Add Sources 。選擇添加以創建約束,然后選擇添加文件并使用附加到本文的約束文件。確保在單擊Finish之前選擇了Copy constraints files into project選項。

由于存在多個約束文件,因此需要將一個約束文件指定為目標約束文件,以便 Vivado 知道在需要時將新約束寫入何處(但所有約束都會讀入設計中)。右鍵單擊Sources選項卡中的vivado_target.xdc約束文件,然后選擇Set as Target Constraint File 。

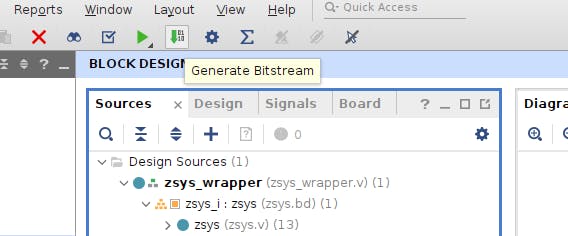

生成比特流

現在 ZynqberryZero 的完整硬件設計已經到位,是時候對其進行綜合、布局和布線并生成比特流了。您可以點擊Generate Bitstream ,Vivado 也會自動運行綜合和實現。

成功生成比特流后,導出用于 Vitis 的硬件,為 Zynq SoC 的 ARM 內核處理器開發軟件(是的,會有一些時序違規,但我還沒有看到任何問題,并且我仍在努力弄清楚如何修復它們)。

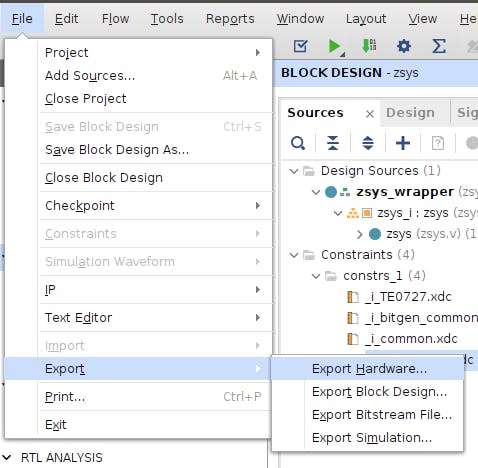

單擊文件>導出>導出硬件...

請務必選擇Include bitstream選項。我總是將硬件平臺導出到 Vivado 項目目錄的頂層(默認),但您可以選擇您喜歡的任何目錄。

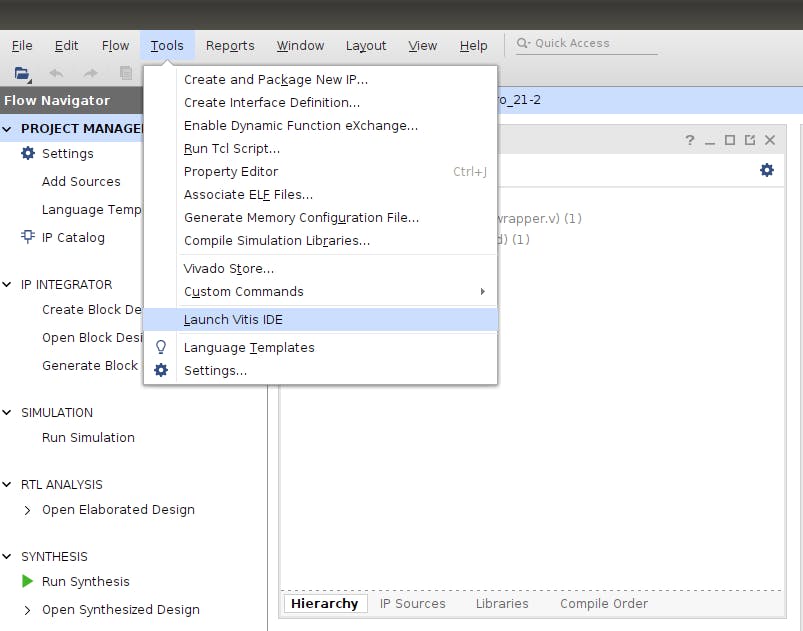

從 Vivado 導出硬件平臺后,通過在 Vivado 中選擇工具>啟動 Vitis IDE來啟動 Vitis 。

同樣,您可以選擇任何所需的目錄來啟動 Vitis 工作區,但我個人喜歡在 Vivado 項目目錄的頂層為其創建一個名為vitis_??workspace的文件夾。

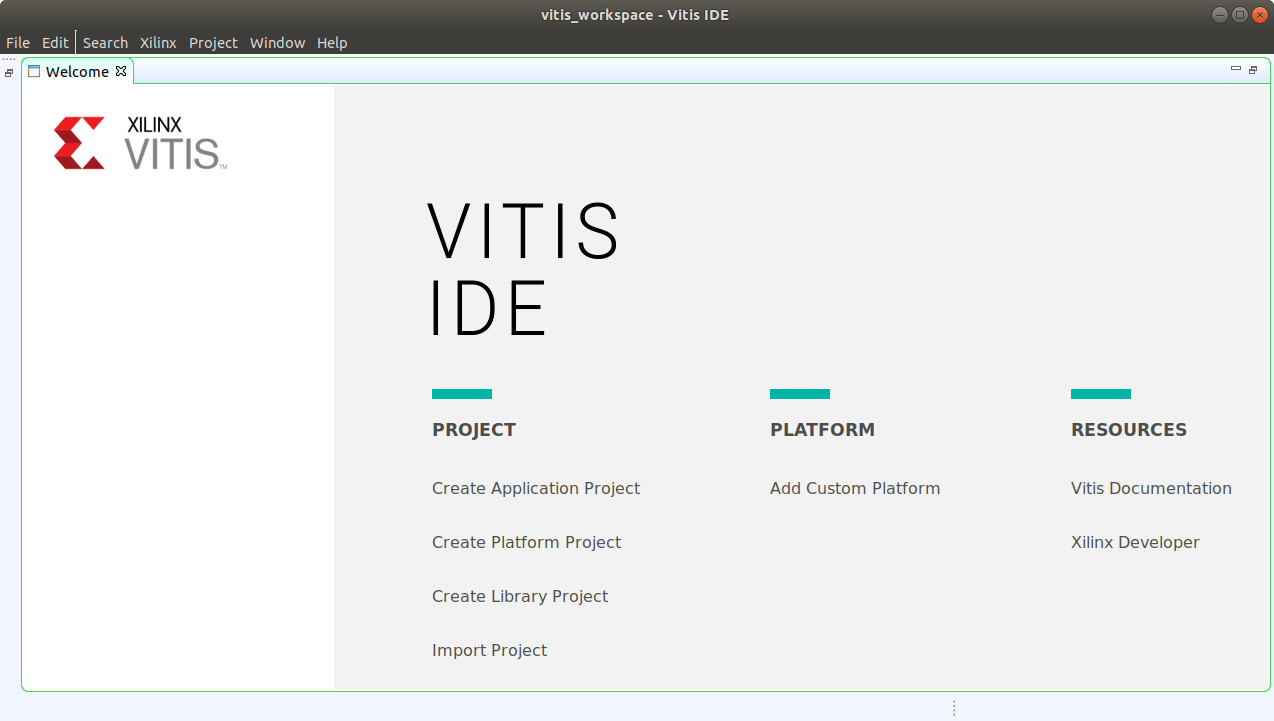

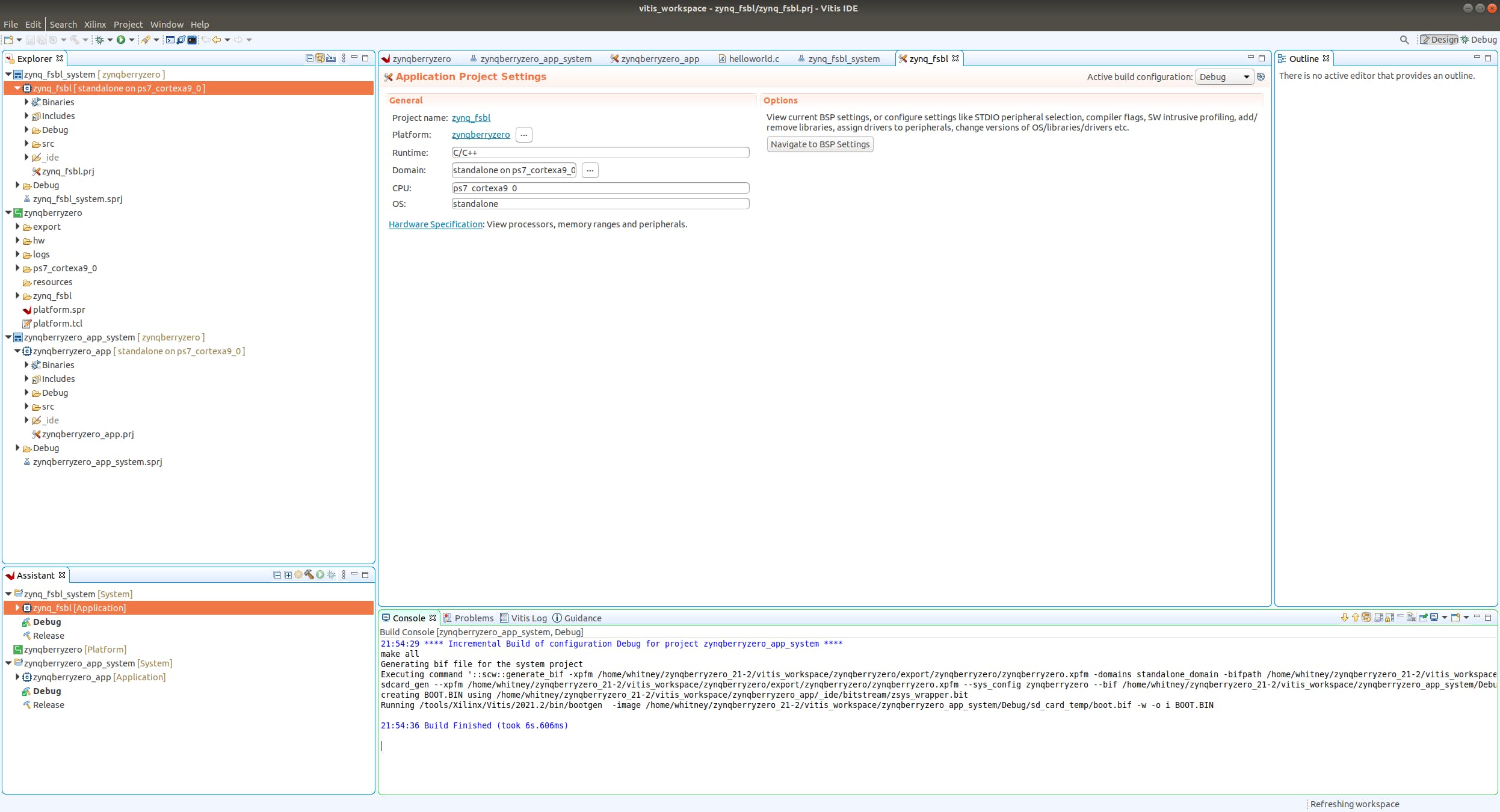

Vitis 平臺項目

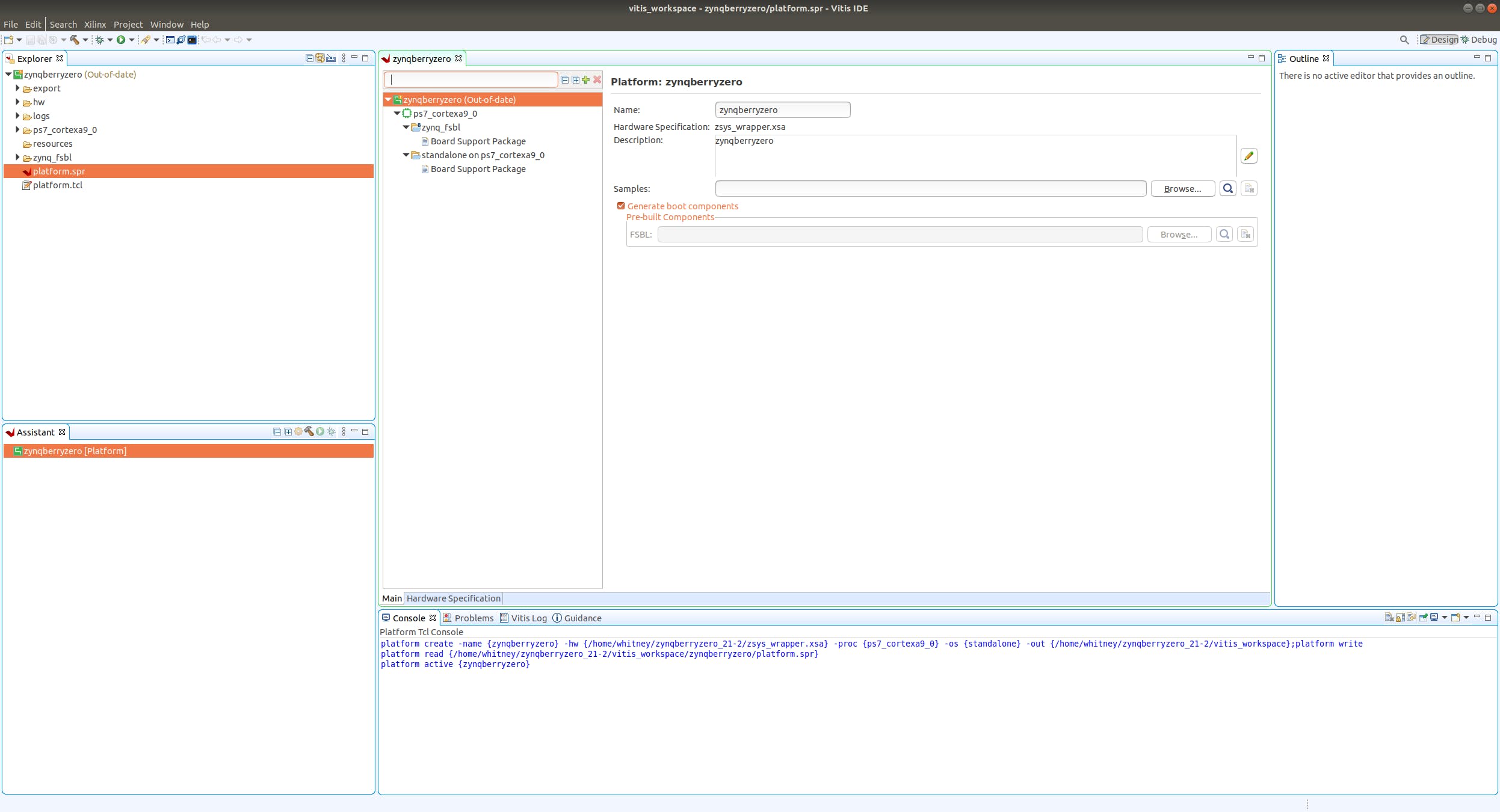

Vitis 啟動到新工作區后,通過選擇 Create Platform Project 創建新的平臺項目。為其指定所需的名稱,并指定從 Vivado 導出的硬件(XSA 文件)以用于要從中創建的平臺項目。

在平臺生成后構建平臺(因為它一開始會顯示過時)。

Vitis 應用項目

通過平臺項目準備好硬件平臺和 BSP(板級支持包)后,創建要在其上運行的應用項目。

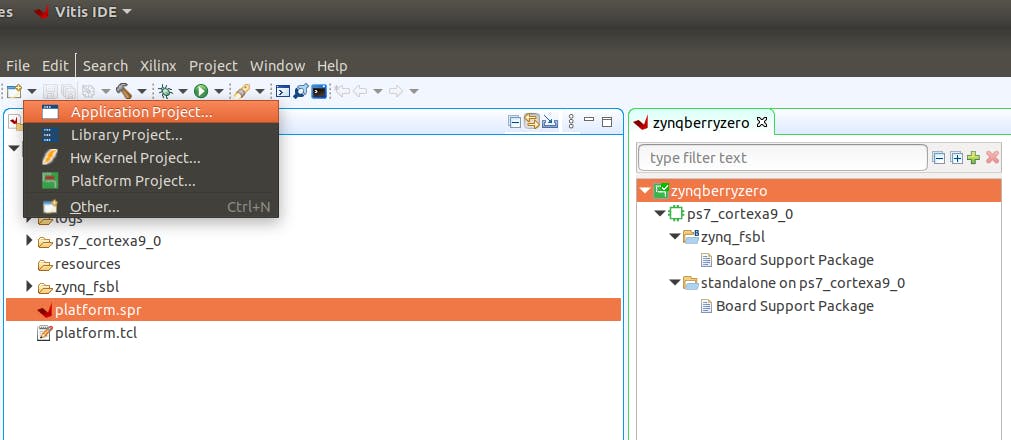

選擇新建>應用程序項目...

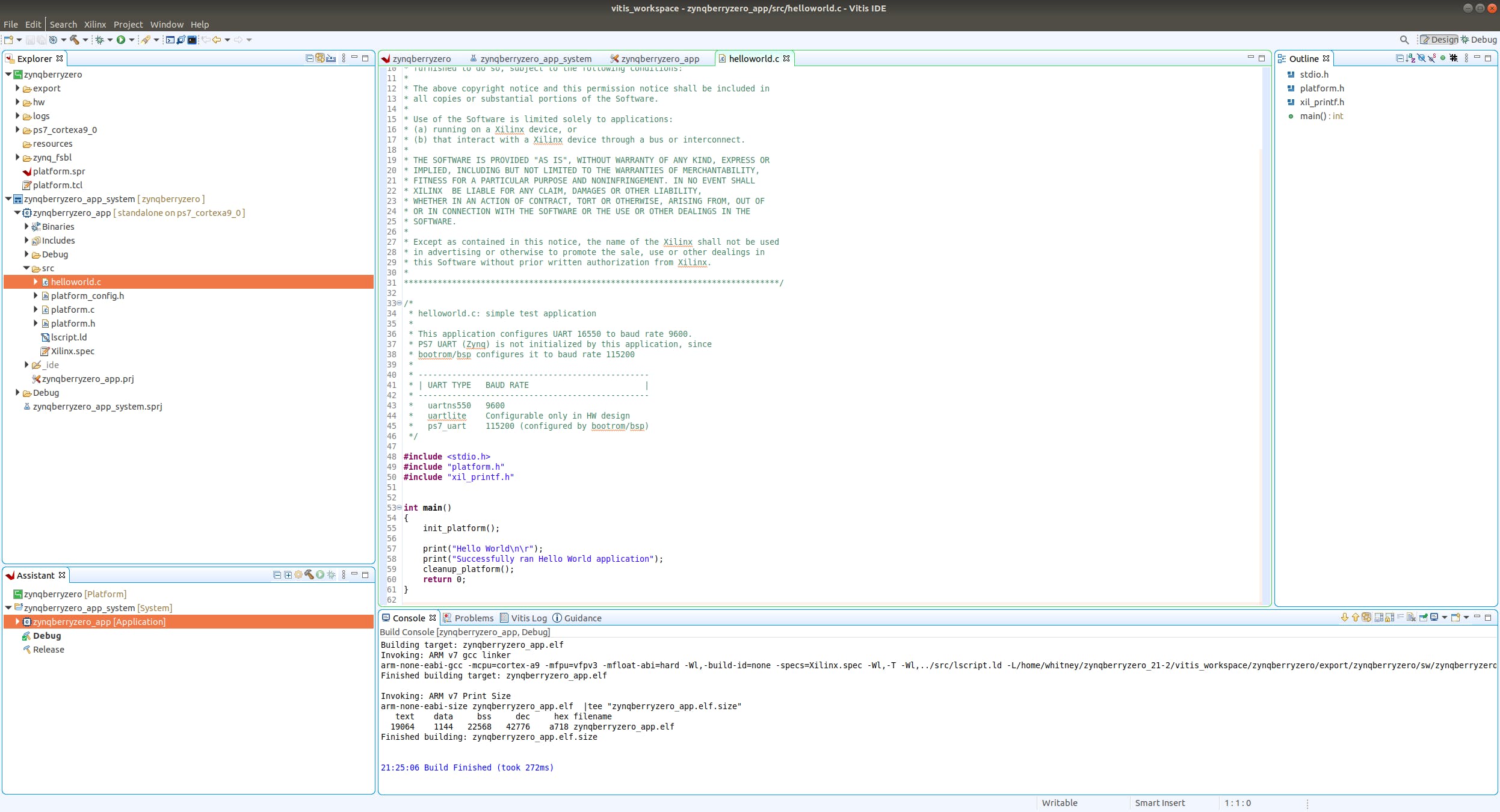

選擇上一步中由平臺項目創建的平臺,并為應用程序指定所需的名稱。使用Hello World應用程序模板。

生成后構建應用程序。

Zynq FSBL 應用項目

為了將 Hello World 應用程序刷入 ZynqberryZero 的 QSPI 閃存,需要創建和修改 Zynq 第一階段引導加載程序應用程序項目以從 JTAG 引導。Zynq 芯片需要從 JTAG 引導,以便主機 PC 可以將引導映像編程到 QSPI 閃存上。

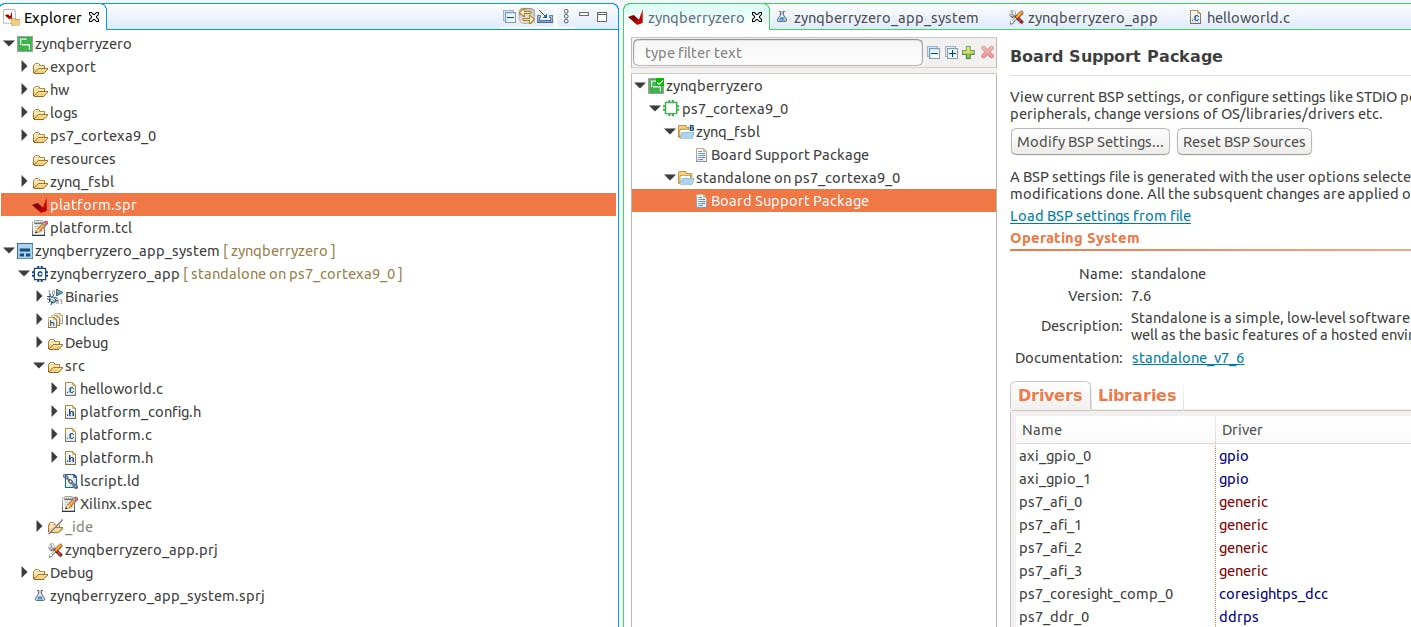

在創建 Zynq FSBL 應用程序之前,在平臺項目的獨立 BSP 中啟用通用 FAT 文件系統庫 (xilffs)。

從Explorer窗口中選擇 .xpr 文件,然后在 standalone on ps7_cortexa9_0下選擇Board Support Package 。單擊Modify BSP Settings...并選中xilffs旁邊的框。

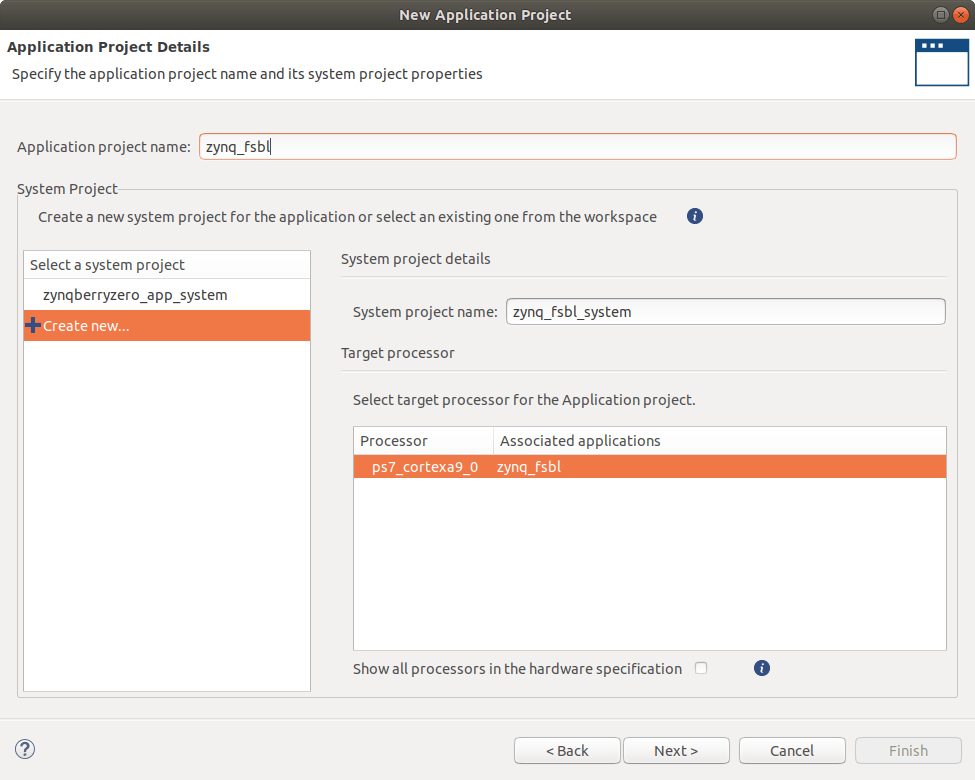

基于Zynq FSBL模板,按照之前的方法再創建一個應用工程:

等待 Zynq FSBL 的應用項目生成。

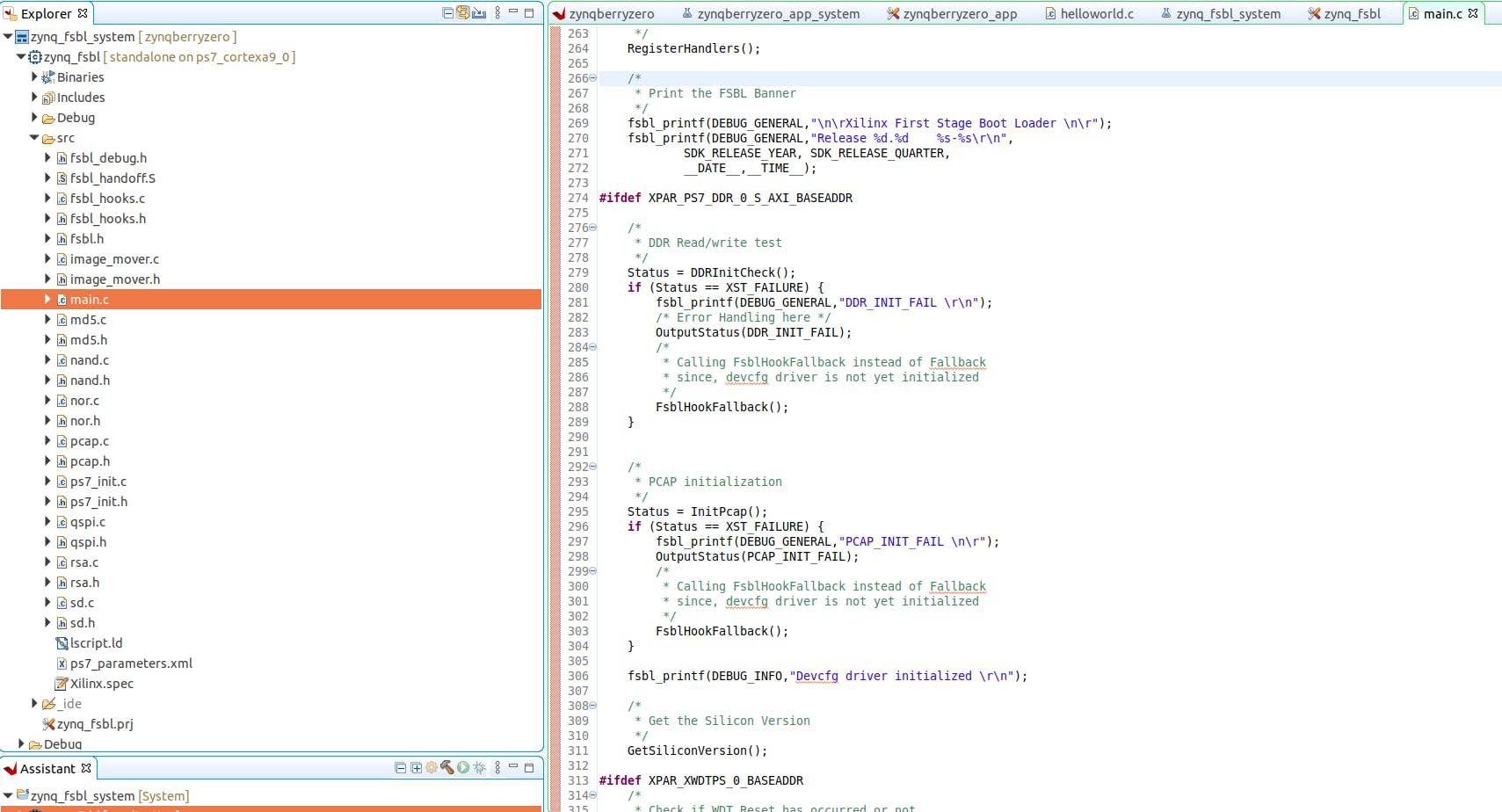

打開 main.c 并將啟動模式更新為 JTAG 啟動模式并跳過內存外設測試。

您還可以在下面找到修改后的 main.c。

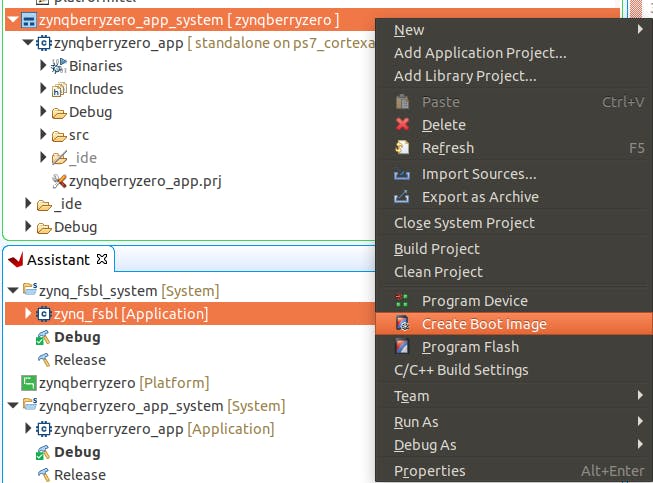

閃存 Zynqberry 零內存

通過在資源管理器窗口中右鍵單擊 Hello World 應用程序并選擇Create Boot Image來為 ZynqberryZero 創建啟動映像。由于從 Hello World 應用程序的右鍵單擊菜單中選擇了創建啟動映像選項,因此將自動生成啟動分區和文件路徑。

您可以看到 FPGA 比特流、Hello World ELF 和 QSPI Zynq FSBL 是構成 ZynqberryZero 的啟動二進制文件 (BOOT.BIN) 的啟動分區。

單擊創建圖像。

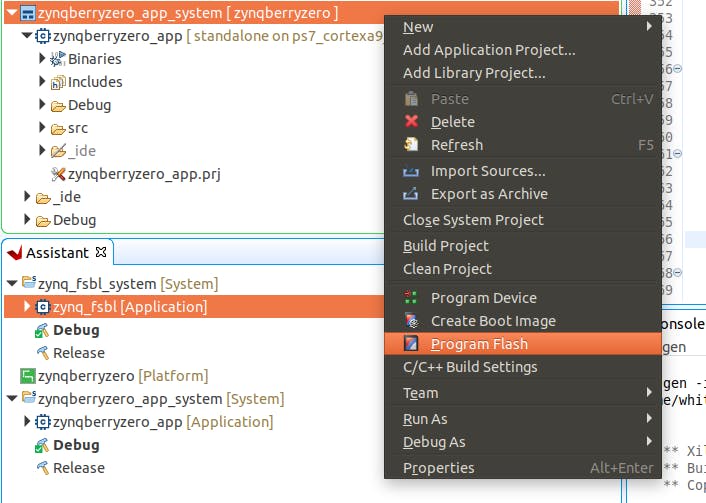

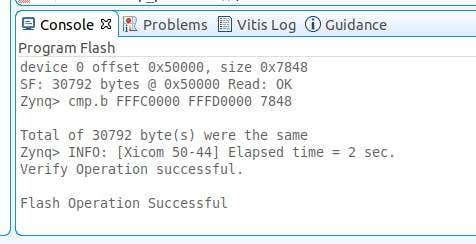

通過再次右鍵單擊資源管理器窗口中的 Hello World 應用程序并選擇Program Flash來對 ZynqberryZero 的 QSPI 閃存進行編程。

使用剛剛創建的引導二進制文件 (BOOT.BIN) 作為映像文件。設置Offset為0x0,Flash Type為qspi-x4-single,使用JTAG Zynq FSBL的ELF文件作為Init File 。還要選中Verify after flash選項。

?

- Vivado 2021.1中的Kria KV260入門

- 《Python編程入門》.pdf 0次下載

- MATLAB使用教程-初步入門大全.PPT 0次下載

- GitHub入門與實踐 0次下載

- Verilog HDL入門教程.pdf 115次下載

- Kicad5.1.5中文入門教程電子版下載 0次下載

- 松下PLC入門基礎培訓課件下載 125次下載

- MATLAB入門教程電子版下載 0次下載

- Xilinx_Vivado_zynq7000入門筆記 71次下載

- 什么是Vivado?資料下載

- Vivado設計流程指導說明 28次下載

- Vivado設計流程指導手冊 50次下載

- Vivado中xilinx_BRAM IP核使用

- PSIM仿真入門學習-課件下載 186次下載

- ZYBO入門指導手冊(一)v1.0——Vivado 21次下載

- Vivado Schematic中的實線和虛線有什么區別? 956次閱讀

- 在Vivado中實現ECO功能 2250次閱讀

- Tcl在Vivado中的應用 1288次閱讀

- Vivado里如何手動調整編譯順序 3470次閱讀

- Vivado中的Elaborate是做什么的? 1277次閱讀

- Vivado在FPGA設計中的優勢 1508次閱讀

- 如何升級Vivado工程腳本 1709次閱讀

- xilinx Vivado工具使用技巧 3934次閱讀

- Vivado軟件仿真DDS核的過程中應該注意的問題 9656次閱讀

- 基于linux系統實現的vivado調用VCS仿真教程 1.1w次閱讀

- Vivado 2017.1和Vivado 2016.4性能對比分析 9977次閱讀

- Vivado獲取License的步驟教程 5.9w次閱讀

- Vivado使用誤區與進階——在Vivado中實現ECO功能 5242次閱讀

- Tcl在Vivado中的基礎應用 4831次閱讀

- ISE約束導入vivado總共分幾步 8733次閱讀

下載排行

本周

- 1SMD LED選型手冊 貼片燈珠

- 5.47 MB | 3次下載 | 免費

- 2加密芯片的一種破解方法和對應加密方案改進設計

- 0.29 MB | 1次下載 | 免費

- 3多功能MPU芯片GC9005數據手冊

- 2.67 MB | 1次下載 | 免費

- 4碳化硅逆變焊機基本產品介紹

- 7.35 MB | 1次下載 | 免費

- 5基本半導體產品在Sic逆變焊機中的應用

- 7.27 MB | 1次下載 | 免費

- 6基本半導體產品在125kW工商業儲能PCS中的應用

- 10.74 MB | 1次下載 | 免費

- 7MOSFET參數解讀

- 1.59 MB | 1次下載 | 2 積分

- 8Modbus測試工具

- 0.72 MB | 1次下載 | 2 積分

本月

- 1使用單片機實現七人表決器的程序和仿真資料免費下載

- 2.96 MB | 44次下載 | 免費

- 23314A函數發生器維修手冊

- 16.30 MB | 13次下載 | 免費

- 3TPS54202H降壓轉換器評估模塊用戶指南

- 1.02MB | 9次下載 | 免費

- 4美的電磁爐維修手冊大全

- 1.56 MB | 9次下載 | 5 積分

- 5STM32F101x8/STM32F101xB手冊

- 1.69 MB | 8次下載 | 1 積分

- 6感應筆電路圖

- 0.06 MB | 7次下載 | 免費

- 7使用TL431設計電源

- 0.67 MB | 6次下載 | 免費

- 8LZC3106G高性能諧振控制器中文手冊

- 1.29 MB | 5次下載 | 1 積分

總榜

- 1matlab軟件下載入口

- 未知 | 935119次下載 | 10 積分

- 2開源硬件-PMP21529.1-4 開關降壓/升壓雙向直流/直流轉換器 PCB layout 設計

- 1.48MB | 420062次下載 | 10 積分

- 3Altium DXP2002下載入口

- 未知 | 233084次下載 | 10 積分

- 4電路仿真軟件multisim 10.0免費下載

- 340992 | 191367次下載 | 10 積分

- 5十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183335次下載 | 10 積分

- 6labview8.5下載

- 未知 | 81581次下載 | 10 積分

- 7Keil工具MDK-Arm免費下載

- 0.02 MB | 73807次下載 | 10 積分

- 8LabVIEW 8.6下載

- 未知 | 65987次下載 | 10 積分

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論