資料介紹

描述

這是一個由 5 部分組成的博客,以下是鏈接:

第 2 部分:在 Spartan 6 FPGA 上使用 Xilinx ISE 的組合邏輯

第 3 部分:在 Cyclone-IV FPGA 上使用 Quartus Prime 的順序邏輯

第 4 部分:在 Artix-7 FPGA 上使用 Vivado 的組合邏輯與順序邏輯

第 5 部分:最終項目 - DE0 Nano 開發板上的 Pong 游戲

本博客介紹了在 Spartan-6 FPGA 上從頭開始實現全加器,并概述了 Verilog HDL 編程風格。

FPGA設計流程:

我們來看第一步

1. 設計作品:

FPGA 設計輸入可以通過兩種方式完成,或者通過代表硬件描述語言的 HDL - 這是最常見的方法,或者通過原理圖輸入,其中可以拖放并將各種塊連接在一起或集成兩者。

我們將通過探索賽靈思 ISE 來討論設計條目!

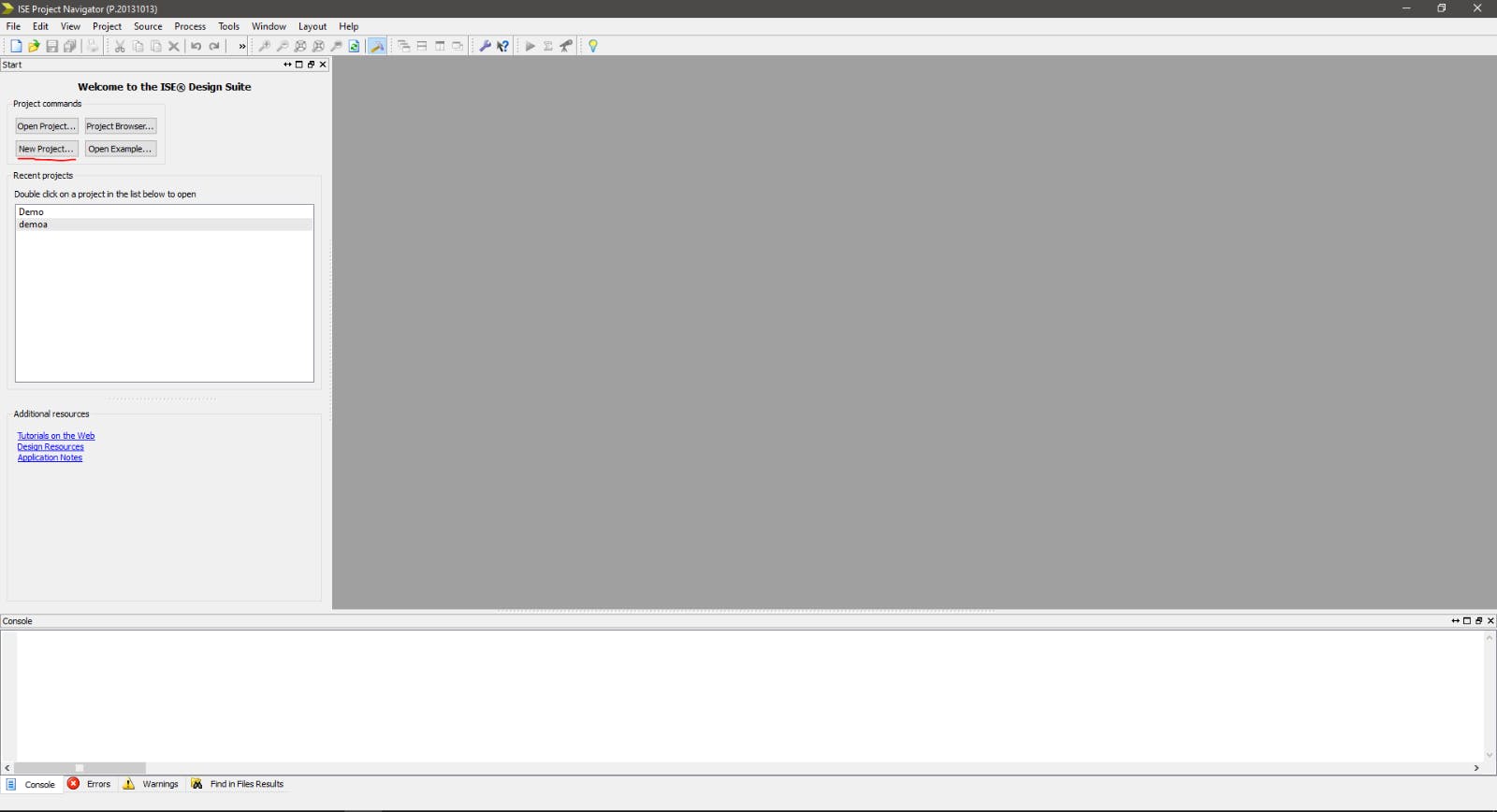

Xilinx ISE 入門:

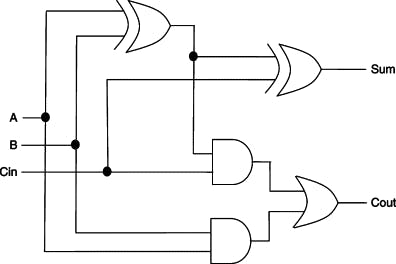

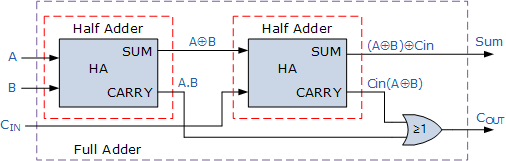

全加器電路(邏輯)

該電路的功能非常簡單,它增加了 3 位并給出了和和進位輸出。

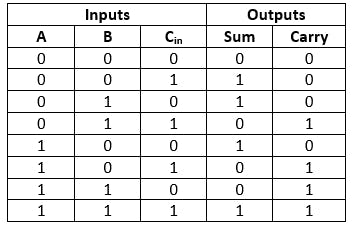

全加器真值表:

什么是組合邏輯?

組合邏輯是一種由布爾電路實現的數字邏輯,其中輸出僅是當前輸入的純函數,電路不包含任何存儲元件。

硬件描述語言 (HDL):

有很多 HDL,其中一些非常常用的 HDL 是 Verilog、VHDL、SystemVerilog。幾乎所有 FPGA 供應商都支持這些 HDL 進行綜合。

讓我們在這個博客中談談 Verilog。Verilog中有3種建模風格。

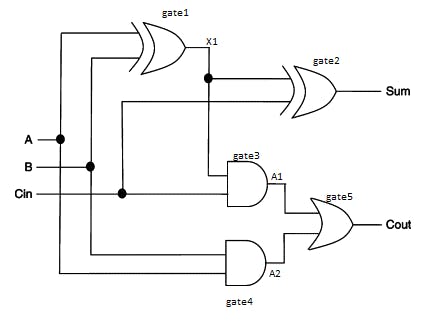

a) 結構:用門來描述邏輯電路的結構,有時也稱為門級建模。

b) 數據流:數據流建模根據從輸入到輸出的數據流來描述硬件。

c) 行為:這些包含程序語句,用于控制數據類型的模擬和操作變量。

a) 使用 Verilog 中的結構建模實現全加法器:

module Full_Adder (

input A, B, Cin,

output Sum, Cout

);

wire X1, A1, A2;

xor gate1 (X1, A, B),

gate2 (Sum, X1, Cin);

and gate3 (A1, A, B),

gate4 (A2, X1, Cin);

b) 使用 Verilog 中的數據流建模實現全加法器:

module Full_Adder (

input A, B, Cin,

output Sum, Cout

);

assign Sum = ( ( A ^ B ) ^ Cin ); // Sum = A xor B xor Cin

assign Cout = ( ( (A ^ B) & Cin ) | ( A & B ) ); // Carry out as the equation

endmodule

c) 使用 Verilog 中的行為建模實現全加法器:

module Full_Adder (

input A, B, Cin,

output reg Sum, Cout

);

always @ (A, B, Cin)

begin: add

{Cout,Sum} = A + B + Cin;

end

endmodule

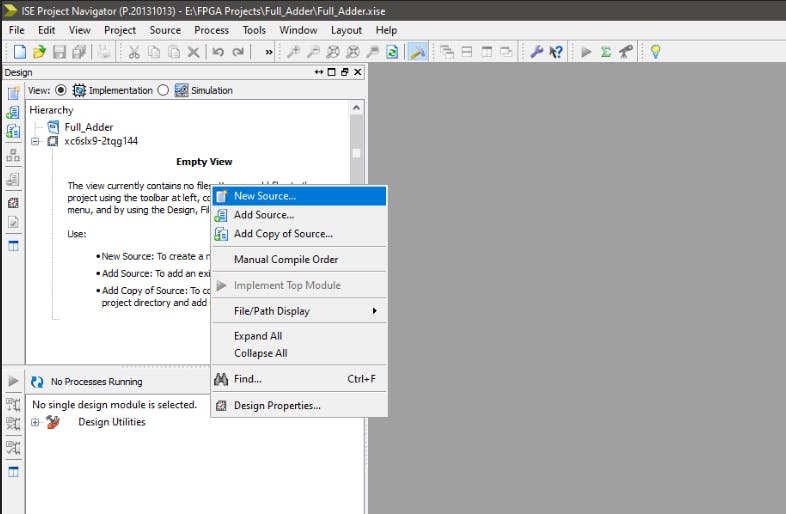

為 FPGA 設計準備文件:

一個典型的 FPGA 設計有兩組文件,一組文件包含指定設計的所有設計文件,另一組是約束文件,其中包含設計的所有約束,例如 FPGA 的時序約束和引腳映射。

保持設計模塊化是一種很好的做法,以便于開發和調試。

top.v 文件(當 Verilog 用作設計語言時)用于實例化層次結構中單個頂層設計中的所有模塊。

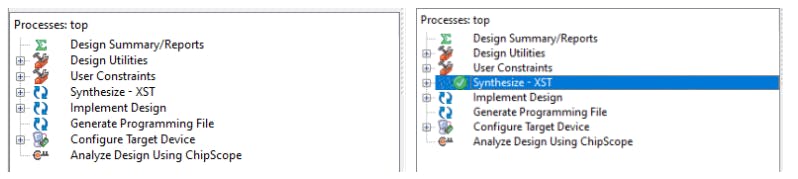

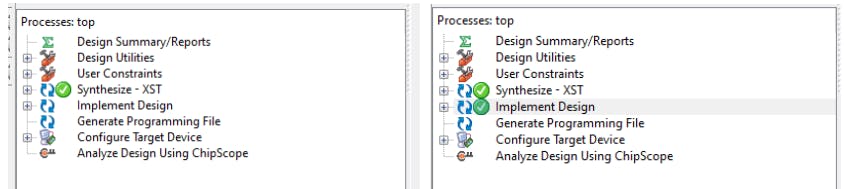

2、設計綜合:

在 FPGA 綜合過程中,高描述設計或 HDL 設計被轉換為門級表示或邏輯組件。

現在綜合設計

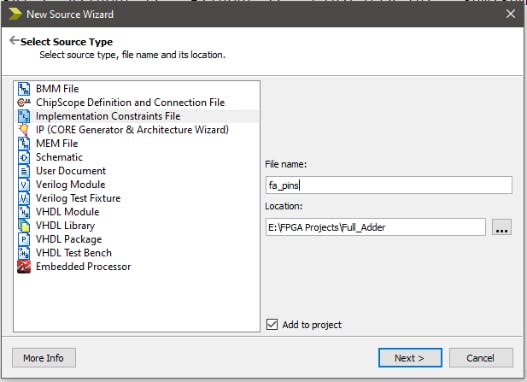

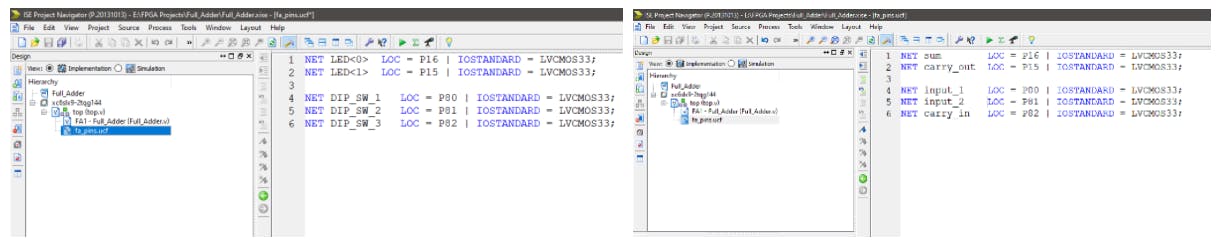

綜合完成后,我們需要添加約束文件以將 FPGA 的引腳映射到邏輯元件。

創建一個新源并在選項中選擇約束文件并為其命名。

幾乎所有 FPGA 開發板供應商都提供了一個主約束文件,其中包含所有引腳及其到 FPGA 的映射。

復制并粘貼項目所需的引腳,例如,用于 Sum 和 Carry 的 2 個 LED,然后是 3 個用于 3 個輸入的開關。

3、設計實現:

現在是實施設計的時候了。

實施工具將網表作為輸入并進行優化、布局和布線。

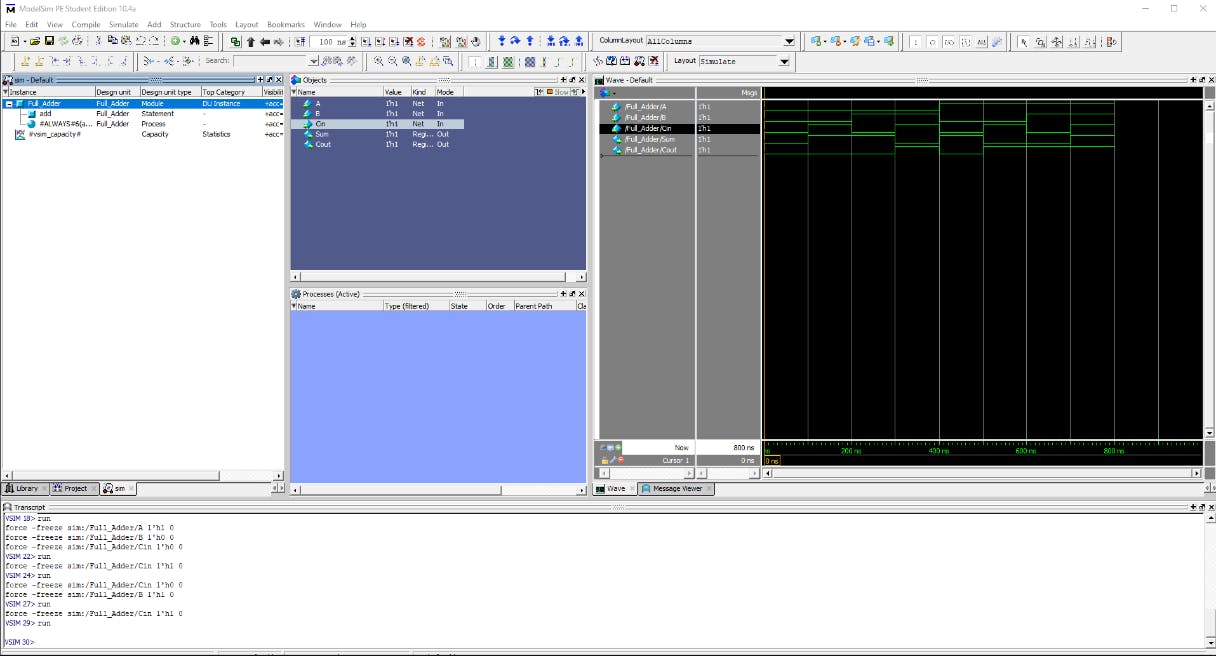

4. 設計驗證:

這是一個簡單的全加器設計,因此不需要驗證,但這樣做是一個很好的做法。使用 Modelsim 驗證設計

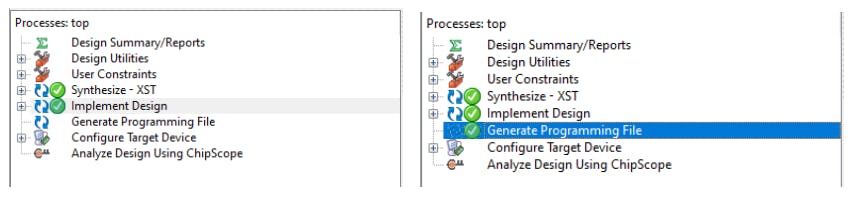

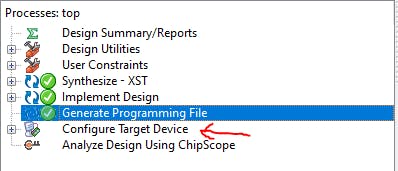

5. 生成編程文件:

編程文件用于對 FPGA 進行編程。該文件包含特定于 FPGA 的設計實現的所有信息。

6. 編程:

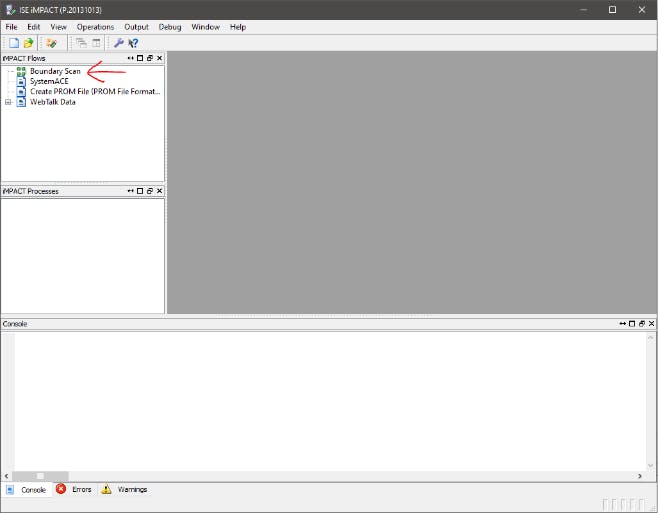

Xilinx ISE 有一個名為 iMPACT 的特定工具,用于對 FPGA 進行編程。

您將收到一條警告,要求您創建 iMPACT 文件,單擊“確定”。然后 iMPACT 工具將打開,然后單擊邊界掃描,然后單擊初始化鏈。

?

?

- PyTorch教程4.4之從頭開始實現Softmax回歸

- PyTorch教程3.4之從頭開始執行線性回歸

- 如何從頭開始制作六足機器人

- 從頭開始構建無人機

- Spartan-6 FPGA的配置教程說明 26次下載

- spartan-6 FPGA的配置資料說明 20次下載

- spartan-6 FPGA的時鐘資源的用戶指南資料免費下載 27次下載

- Spartan-6 FPGA塊RAM的技術參考資料免費下載 13次下載

- spartan-6 FPGA可配置邏輯塊的用戶指南資料免費下載 16次下載

- 如何在spartan-6 FPGA中使用GTP收發器的詳細資料說明 27次下載

- spartan-6 FPGA的設備引出線和包裝規格介紹 8次下載

- Spartan-6-FPGA配置講解 6次下載

- Spartan-6 FPGA電氣特性 21次下載

- Spartan-6 FPGA Configuration User Guide 31次下載

- Xilinx-Spartan6 FPGA實現MultiBoot

- 從頭開始設計揚聲器系統 469次閱讀

- FPGA設計:4位全加器代碼以及仿真 3071次閱讀

- 全加器的真值表 5.9w次閱讀

- digilentAnvyl:Spartan-6 FPGA訓練板介紹 3647次閱讀

- digilent Spartan-6 FPGA 介紹 3826次閱讀

- 如何從頭開始進行數據科學項目 2525次閱讀

- 什么是全加器 全加器工作原理 7.6w次閱讀

- 全加器是什么?全加器和半加器的區別? 7.2w次閱讀

- 一文詳解Spartan-6系列IO Tile結構 8098次閱讀

- 關于Xilinx公司出品的Spartan6系列FPGA的MultiBoot設計方案詳解 9851次閱讀

- Xilinx Spartan-6系列封裝概述和管腳分配 9196次閱讀

- Spartan-6 FPGA 的 ISE 工具快速入門視頻 6893次閱讀

- Spartan6開發中bufpll mapping error 2135次閱讀

- 在用Spartan6生成的Clock時在maping遇到的問題 2704次閱讀

- ZedBoard上的點燈簽名實驗(二):創建自定義IP 687次閱讀

下載排行

本周

- 1山景DSP芯片AP8248A2數據手冊

- 1.06 MB | 532次下載 | 免費

- 2RK3399完整板原理圖(支持平板,盒子VR)

- 3.28 MB | 339次下載 | 免費

- 3TC358743XBG評估板參考手冊

- 1.36 MB | 330次下載 | 免費

- 4DFM軟件使用教程

- 0.84 MB | 295次下載 | 免費

- 5元宇宙深度解析—未來的未來-風口還是泡沫

- 6.40 MB | 227次下載 | 免費

- 6迪文DGUS開發指南

- 31.67 MB | 194次下載 | 免費

- 7元宇宙底層硬件系列報告

- 13.42 MB | 182次下載 | 免費

- 8FP5207XR-G1中文應用手冊

- 1.09 MB | 178次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 2555集成電路應用800例(新編版)

- 0.00 MB | 33566次下載 | 免費

- 3接口電路圖大全

- 未知 | 30323次下載 | 免費

- 4開關電源設計實例指南

- 未知 | 21549次下載 | 免費

- 5電氣工程師手冊免費下載(新編第二版pdf電子書)

- 0.00 MB | 15349次下載 | 免費

- 6數字電路基礎pdf(下載)

- 未知 | 13750次下載 | 免費

- 7電子制作實例集錦 下載

- 未知 | 8113次下載 | 免費

- 8《LED驅動電路設計》 溫德爾著

- 0.00 MB | 6656次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935054次下載 | 免費

- 2protel99se軟件下載(可英文版轉中文版)

- 78.1 MB | 537798次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420027次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191187次下載 | 免費

- 7十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183279次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138040次下載 | 免費

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論