完善資料讓更多小伙伴認(rèn)識你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > 存內(nèi)計(jì)算

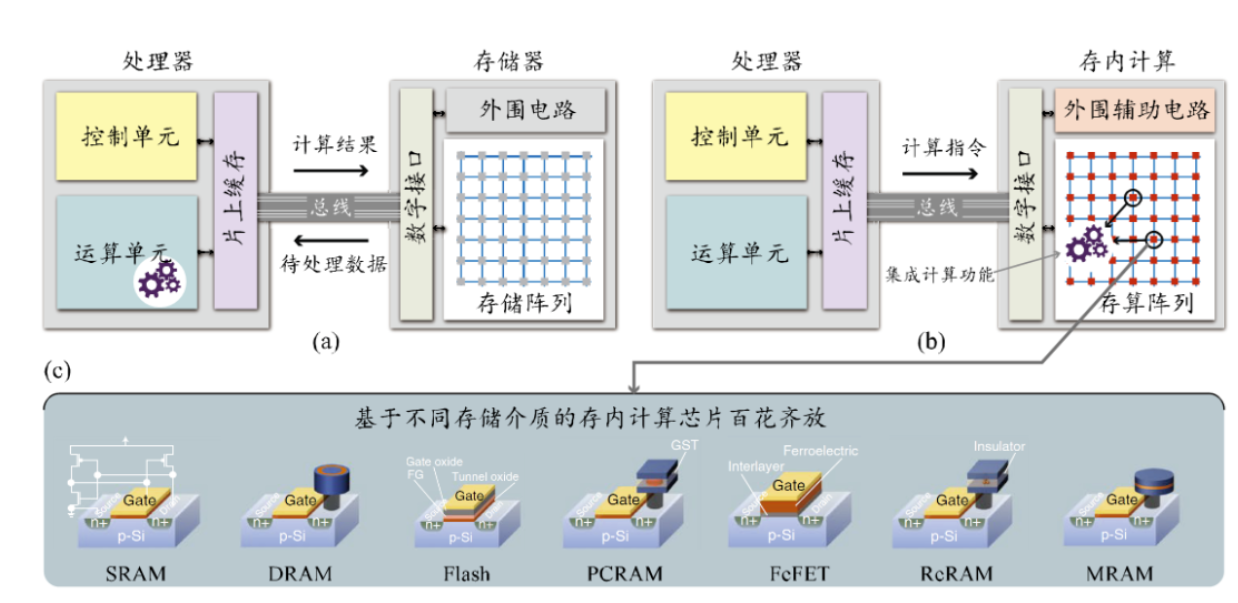

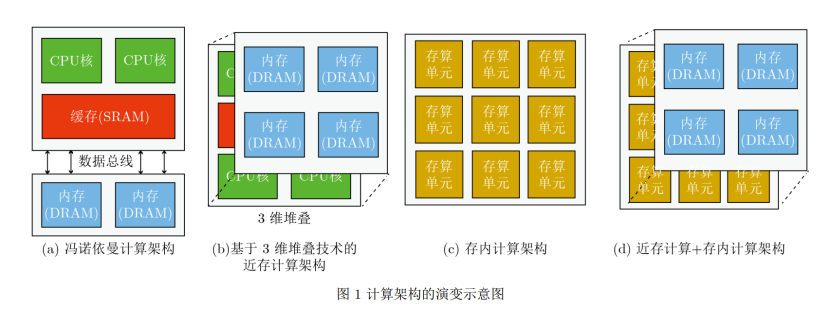

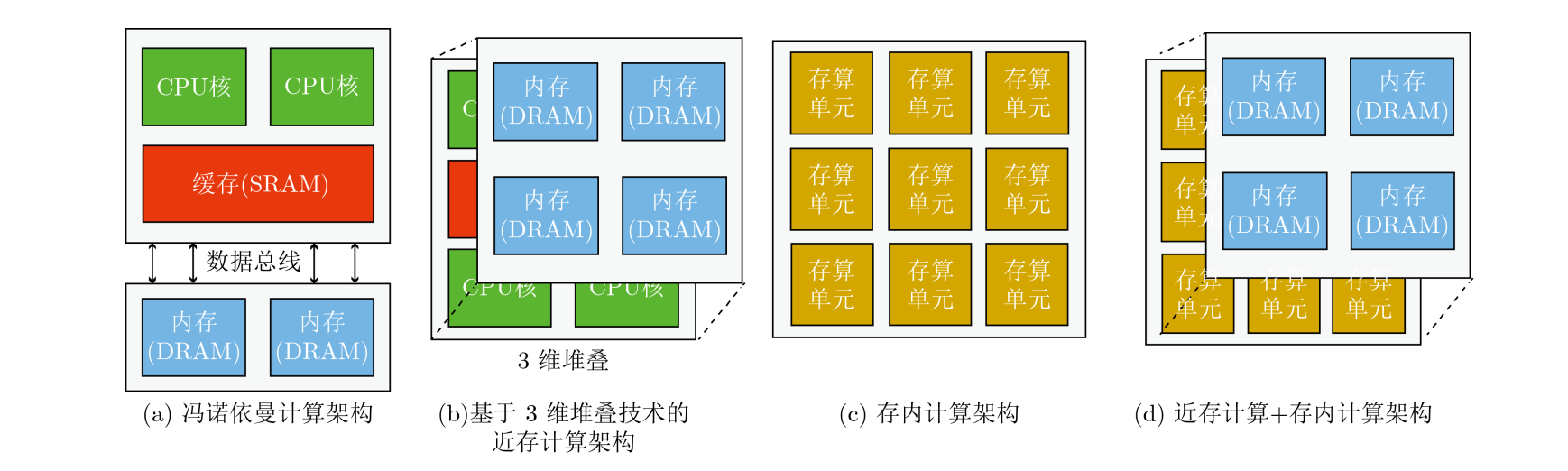

存內(nèi)計(jì)算,顧名思義就是把計(jì)算單元嵌入到內(nèi)存當(dāng)中。通常計(jì)算機(jī)運(yùn)行的馮·諾依曼體系包括存儲單元和計(jì)算單元兩部分,計(jì)算機(jī)實(shí)施運(yùn)算需要先把數(shù)據(jù)存入主存儲器,再按順序從主存儲器中取出指令。

存內(nèi)計(jì)算是一個(gè)由來已久的概念,其主要目的是為了解決內(nèi)存墻問題。

存內(nèi)計(jì)算,顧名思義就是把計(jì)算單元嵌入到內(nèi)存當(dāng)中。通常計(jì)算機(jī)運(yùn)行的馮·諾依曼體系包括存儲單元和計(jì)算單元兩部分,計(jì)算機(jī)實(shí)施運(yùn)算需要先把數(shù)據(jù)存入主存儲器,再按順序從主存儲器中取出指令,一條一條的執(zhí)行,數(shù)據(jù)需要在處理器與存儲器之間進(jìn)行頻繁遷移,如果內(nèi)存的傳輸速度跟不上CPU的性能,就會導(dǎo)致計(jì)算能力受到限制,即“內(nèi)存墻”出現(xiàn),例如,CPU處理運(yùn)算一道指令的耗時(shí)假若為1ns,但內(nèi)存讀取傳輸該指令的耗時(shí)可能就已達(dá)到10ns,嚴(yán)重影響了CPU的運(yùn)行處理速度。

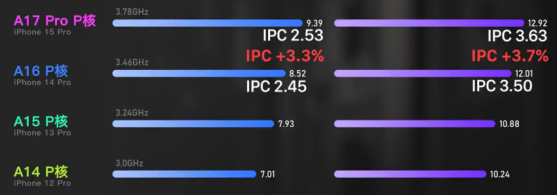

在過去幾十年中,處理器的運(yùn)行速度隨著摩爾定律高速提升,然而計(jì)算機(jī)中的主存儲器DRAM是基于電容充放電實(shí)現(xiàn)的高密度存儲方案,其性能(速度)取決于電容充放電速度以及DRAM與處理器之間的接口帶寬,總體來看其性能提升速度遠(yuǎn)遠(yuǎn)慢于處理器速度,目前DRAM的性能已經(jīng)成為了整體計(jì)算機(jī)性能的一個(gè)重要瓶頸,即所謂阻礙性能提升的“內(nèi)存墻”。

除了性能之外,內(nèi)存對于能效比的限制也成了傳統(tǒng)馮諾伊曼體系計(jì)算機(jī)的一個(gè)瓶頸,尤其是對于人工智能(神經(jīng)網(wǎng)絡(luò)模型)應(yīng)用來說。神經(jīng)網(wǎng)絡(luò)的特點(diǎn)就是計(jì)算量大,而且計(jì)算過程中涉及到的數(shù)據(jù)量也很大,使用傳統(tǒng)馮諾伊曼架構(gòu)會頻繁讀寫內(nèi)存。目前的DRAM一次讀寫32bit數(shù)據(jù)消耗的能量比起32bit數(shù)據(jù)計(jì)算消耗的能量要大兩到三個(gè)數(shù)量級,因此成為了總體計(jì)算設(shè)備中的能效比瓶頸。

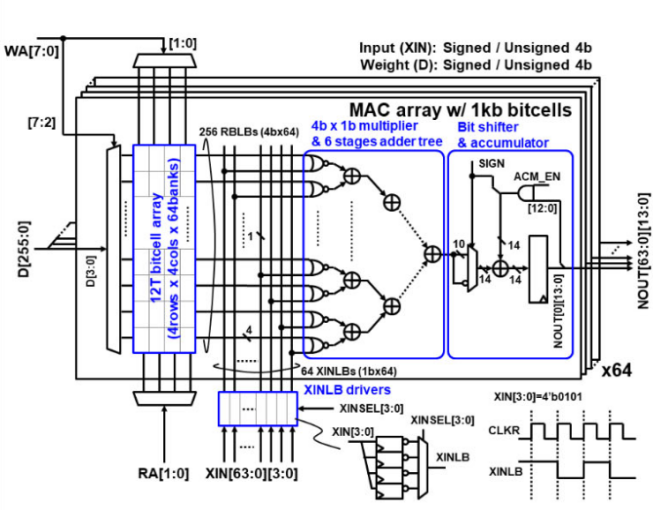

存內(nèi)計(jì)算就是為了解決內(nèi)存墻問題而提出的方案。如前所述,馮諾依曼架構(gòu)的計(jì)算機(jī)系統(tǒng)把存儲器和處理器分割成了兩個(gè)部分,而處理器頻繁訪問存儲器的開銷就形成了內(nèi)存墻。存內(nèi)計(jì)算的基本思路就是把計(jì)算和存儲合二為一,從而實(shí)現(xiàn)減少處理器訪問存儲器的頻率(因?yàn)橛?jì)算已經(jīng)在存儲器內(nèi)完成了大部分)。嚴(yán)格來說,存內(nèi)計(jì)算還可以分為兩種思路。第一種思路主要偏向于電路革新,其方法是通過電路革新讓存儲器本身就具有計(jì)算能力,例如在存儲器數(shù)據(jù)讀出的decoder等地方做改動(dòng)來實(shí)現(xiàn)計(jì)算等。

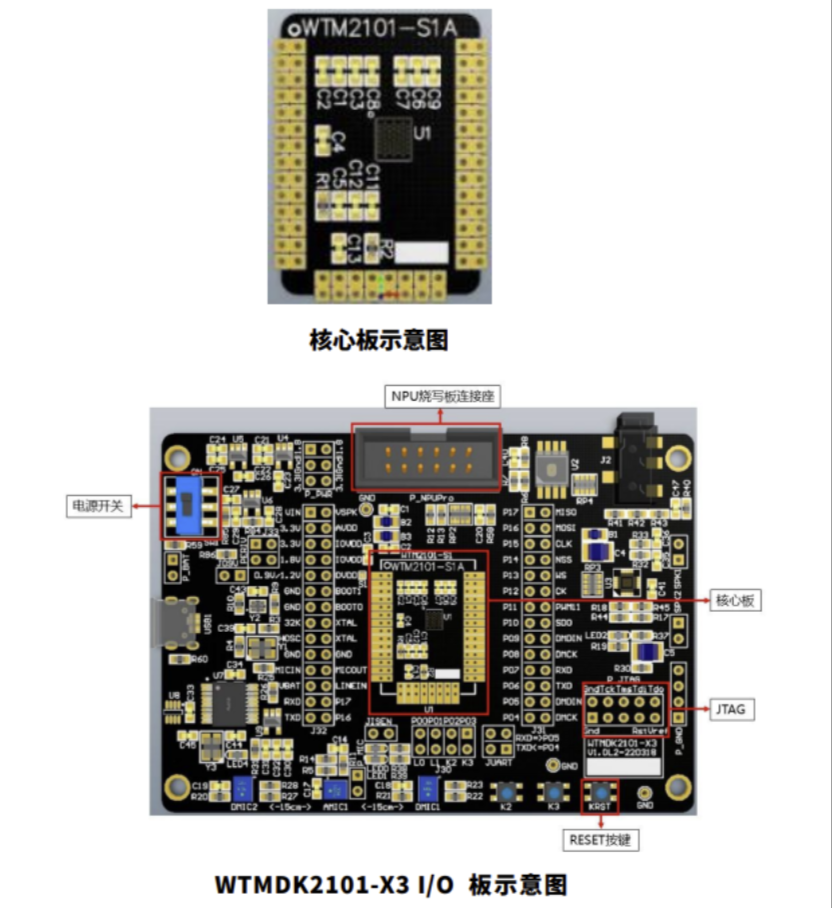

1024 CSDN 程序員節(jié)-基于存內(nèi)計(jì)算WTM2101芯片開發(fā)板驗(yàn)證語音識別

整體流程為 訓(xùn)練得到模型,并轉(zhuǎn)換為知存科技開發(fā)板相應(yīng)格式模型。工具鏈編譯模型,得到模型權(quán)重表。燒寫模型權(quán)重。燒寫代碼。成功運(yùn)行后,當(dāng)我們對著開發(fā)板說出“...

2024-05-20 標(biāo)簽:AI數(shù)據(jù)庫語音識別 885 0

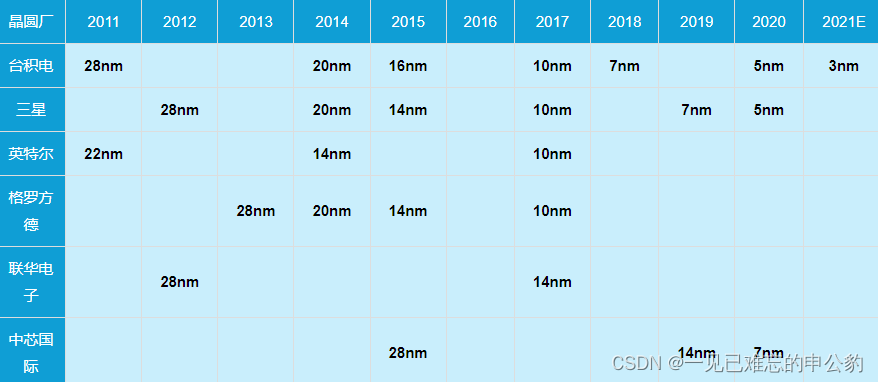

存內(nèi)計(jì)算——助力實(shí)現(xiàn)28nm等效7nm功效

可重構(gòu)芯片嘗試在芯片內(nèi)布設(shè)可編程的計(jì)算資源,根據(jù)計(jì)算任務(wù)的數(shù)據(jù)流特點(diǎn),動(dòng)態(tài)構(gòu)造出最適合的計(jì)算架構(gòu),國內(nèi)團(tuán)隊(duì)設(shè)計(jì)并在12nm工藝下制造的CGRA芯片,已經(jīng)...

存內(nèi)計(jì)算原理分類——數(shù)字存內(nèi)計(jì)算與模擬存內(nèi)計(jì)算

數(shù)字存內(nèi)計(jì)算與模擬存內(nèi)計(jì)算各有優(yōu)劣,都是存算一體發(fā)展進(jìn)程中的重點(diǎn)發(fā)展路徑,數(shù)字存內(nèi)計(jì)算由于其高速、高精度、抗噪性強(qiáng)、工藝技術(shù)成熟、能效比高等特點(diǎn),更適用...

存內(nèi)計(jì)算芯片研究進(jìn)展以及應(yīng)用-以基于Nor Flash的卷積神經(jīng)網(wǎng)絡(luò)量化以及部署

經(jīng)過對動(dòng)態(tài)閾值量化算法的實(shí)驗(yàn)驗(yàn)證,包括實(shí)驗(yàn)平臺及相關(guān)設(shè)置、在CIFAR-10數(shù)據(jù)集上對參數(shù)和激活層進(jìn)行的驗(yàn)證以及對AlexNet、VGG16和ResNe...

2024-05-17 標(biāo)簽:數(shù)據(jù)集卷積神經(jīng)網(wǎng)絡(luò)存算一體 1650 0

從MRAM的演進(jìn)看存內(nèi)計(jì)算的發(fā)展

我國的存內(nèi)計(jì)算產(chǎn)業(yè)也開始迅猛發(fā)展,知存科技、九天睿芯、智芯科、后摩智能、蘋芯科技等國內(nèi)專注存內(nèi)計(jì)算賽道的新興公司紛紛獲得融資,加速在該領(lǐng)域的早期市場布局...

論基于電壓域的SRAM存內(nèi)計(jì)算技術(shù)的嶄新前景

這篇文章總結(jié)了馮·諾伊曼架構(gòu)及其在處理數(shù)據(jù)密集型應(yīng)用中所面臨的性能和能耗問題。為了應(yīng)對這一挑戰(zhàn),文章介紹了存內(nèi)計(jì)算技術(shù),其中重點(diǎn)討論了基于電壓域的SRA...

2024-05-17 標(biāo)簽:存儲器數(shù)據(jù)傳輸sram 983 0

探索存內(nèi)計(jì)算—基于 SRAM 的存內(nèi)計(jì)算與基于 MRAM 的存算一體的探究

本文深入探討了基于SRAM和MRAM的存算一體技術(shù)在計(jì)算領(lǐng)域的應(yīng)用和發(fā)展。首先,介紹了基于SRAM的存內(nèi)邏輯計(jì)算技術(shù),包括其原理、優(yōu)勢以及在神經(jīng)網(wǎng)絡(luò)領(lǐng)域...

2024-05-16 標(biāo)簽:存儲器神經(jīng)網(wǎng)絡(luò)sram 2816 0

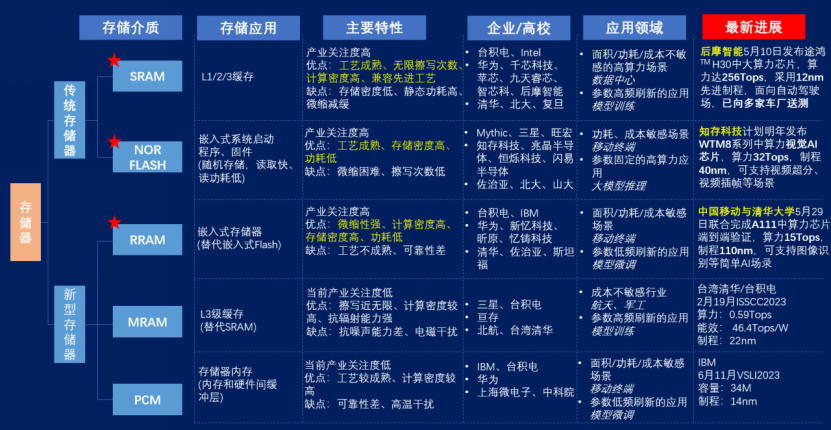

存內(nèi)計(jì)算芯片的基石-存儲介質(zhì)匯總

作為新的計(jì)算架構(gòu),存內(nèi)計(jì)算(Computing In Memory,CIM)被認(rèn)為是具有潛力的革命性技術(shù)。重點(diǎn)是將存儲與計(jì)算融合,有效克服馮·諾依曼架構(gòu)...

存內(nèi)計(jì)算芯片研究進(jìn)展及應(yīng)用

在NOR Flash存內(nèi)計(jì)算芯片當(dāng)中,向量-矩陣乘法運(yùn)算基于電流/電壓的跨導(dǎo)與基爾霍夫定律進(jìn)行物理實(shí)現(xiàn),如圖7(a)所示。因此,其核心是設(shè)計(jì)NOR Fl...

知存科技助力AI應(yīng)用落地:WTMDK2101-ZT1評估板實(shí)地評測與性能揭秘

隨著當(dāng)今數(shù)據(jù)迅速增長,傳統(tǒng)的馮諾依曼架構(gòu)內(nèi)存墻正在成為計(jì)算性能進(jìn)一步提升的阻礙。新一代的存內(nèi)計(jì)算(IMC)和近存計(jì)算(NMC)架構(gòu)有望突破這一瓶頸,顯著...

專注存內(nèi)計(jì)算的知存科技榮獲2024全球(中國)半導(dǎo)體市場年度最佳企業(yè)獎(jiǎng)

在近日舉行的2024-2025全球半導(dǎo)體市場峰會上,知存科技憑借在市場競爭力及未來前景方面的卓越表現(xiàn),榮獲世界集成電路協(xié)會(World Integrat...

知存科技啟動(dòng)首屆存內(nèi)計(jì)算創(chuàng)新大賽

存內(nèi)計(jì)算作為一項(xiàng)打破“內(nèi)存墻”“功耗墻”的顛覆性技術(shù),消除了存與算的界限,相比CPU或GPU能夠?qū)崿F(xiàn)更高計(jì)算并行度、更大專用算力,達(dá)成數(shù)量級的能效提升。...

2024-11-21 標(biāo)簽:cpu知存科技存內(nèi)計(jì)算 243 0

西門子 EDA的內(nèi)存技術(shù)專家Jongsin Yun說, SRAM 的微縮滯后于邏輯收縮,主要是由于最新技術(shù)中嚴(yán)格的設(shè)計(jì)規(guī)則。過去,我們對 SRAM 有單...

2023-12-15 標(biāo)簽:轉(zhuǎn)換器西門子DDR 498 0

蘋芯科技Pimchip-S系列存算一體芯片為智能化產(chǎn)業(yè)高效賦能

2023世界人工智能大會(以下簡稱“WAIC”)于7月6-8日在上海舉辦,以“智聯(lián)世界 生成未來”為主題,聚焦通用人工智能發(fā)展,營造良好創(chuàng)新生態(tài),擁抱智...

知存科技介紹,WTM2101可使用sub-mW級功耗完成大規(guī)模深度學(xué)習(xí)運(yùn)算,特別適合可穿戴設(shè)備中的智能語音和智能健康服務(wù)。

2023-02-09 標(biāo)簽:cpusoc存內(nèi)計(jì)算 1575 0

WTM存內(nèi)計(jì)算芯片助力AI應(yīng)用新圖景

中國集成電路設(shè)計(jì)業(yè)2022年會暨廈門集成電路產(chǎn)業(yè)創(chuàng)新發(fā)展高峰論壇(ICCAD 2022)在廈門國際會展中心圓滿閉幕。數(shù)百家企業(yè)亮相展區(qū),百余位學(xué)術(shù)及企業(yè)...

電子發(fā)燒友網(wǎng)報(bào)道(文/周凱揚(yáng))無論是前段時(shí)間爆火的繪圖模型Stable Diffusion,還是大規(guī)模語言模型ChatGPT,AI無疑已經(jīng)成了新時(shí)代的自...

2022-12-13 標(biāo)簽:存內(nèi)計(jì)算 1770 0

提到多模態(tài)融合感知, 我們難免會覺得有些困惑 “模態(tài)”,可理解為“感官” 多模態(tài)即將多種感官融合 不夠直觀? 那今天我們就以一道競猜題開場 ...

蘋芯科技成立于2021年,專注于存內(nèi)計(jì)算AI芯片研究與應(yīng)用,希望通過SRAM技術(shù)路線突破傳統(tǒng)馮·諾依曼結(jié)構(gòu)所造成的存儲墻局限,為人工智能行業(yè)下的多元場景...

2022-08-08 標(biāo)簽:cpu存儲存內(nèi)計(jì)算 5237 0

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |