完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > 蝕刻

最早可用來(lái)制造銅版、鋅版等印刷凹凸版,也廣泛地被使用于減輕重量(Weight Reduction)儀器鑲板,銘牌及傳統(tǒng)加工法難以加工之薄形工件等的加工;經(jīng)過不斷改良和工藝設(shè)備發(fā)展,亦可以用于航空、機(jī)械、化學(xué)工業(yè)中電子薄片零件精密蝕刻產(chǎn)品的加工,特別在半導(dǎo)體制程上,蝕刻更是不可或缺的技術(shù)。

文章:420個(gè) 瀏覽:15542次 帖子:14個(gè)

但隨著技術(shù)迭代,晶體管尺寸持續(xù)縮減,電阻電容(RC)延遲已成為制約集成電路性能的關(guān)鍵因素。在90納米及以下工藝節(jié)點(diǎn),銅開始作為金屬互聯(lián)材...

干法刻蝕的概念、碳硅反應(yīng)離子刻蝕以及ICP的應(yīng)用

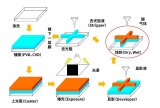

碳化硅(SiC)作為一種高性能材料,在大功率器件、高溫器件和發(fā)光二極管等領(lǐng)域有著廣泛的應(yīng)用。其中,基于等離子體的干法蝕刻在SiC的圖案化及電子器件制造中...

為了改善上述蝕刻柱狀結(jié)構(gòu)以及離子布植法制作面射型雷射的缺點(diǎn),在1994年從德州大學(xué)奧斯丁分校獲得博士學(xué)位的D.L. Huffaker 首次發(fā)...

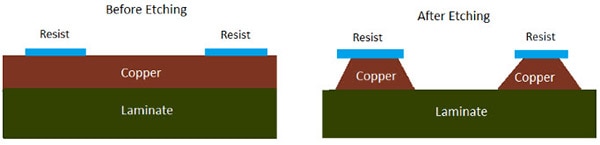

作者:Jake Hertz 在眾多可用的 PCB 制造方法中,化學(xué)蝕刻仍然是行業(yè)標(biāo)準(zhǔn)。蝕刻以其精度和可擴(kuò)展性而聞名,它提供了一種創(chuàng)建...

與亞微米工藝類似,側(cè)墻工藝是指形成環(huán)繞多晶硅的氧化介質(zhì)層,從而保護(hù)LDD 結(jié)構(gòu),防止重?fù)诫s的源漏離子注入到LDD結(jié)構(gòu...

蝕刻的歷史方法是使用濕法蝕刻劑的浸泡技術(shù)。該程序類似于前氧化清潔沖洗干燥過程和沉浸顯影。晶圓被浸入蝕刻劑罐中一段時(shí)間,轉(zhuǎn)移到?jīng)_洗站去除酸,然后轉(zhuǎ...

傳統(tǒng)的2D視覺技術(shù)已經(jīng)無(wú)法滿足高精度的印刷電路板(PCB)外觀檢測(cè)。3D成像技術(shù)則以其獨(dú)特的優(yōu)勢(shì),輕松地在視野范...

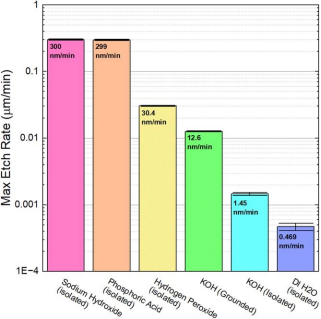

引言 鍺是下一代背面成像器的有希望的替代品,因?yàn)樽罱耐|(zhì)外延生長(zhǎng)已經(jīng)產(chǎn)生了非常低的缺陷密度。鍺的固有特性使其能夠進(jìn)行高速硬X射線檢...

干式蝕刻是為對(duì)光阻上的圖案忠實(shí)地進(jìn)行高精密加工的過程,故選擇材料層與光阻層的蝕刻速率差(選擇比)較大、且能夠確保蝕刻的非等向性(主要隨材料層的厚度方向進(jìn)...

2024-04-18 標(biāo)簽:蝕刻 799 0

芯片制造是當(dāng)今世界最為復(fù)雜的工藝過程。這是一個(gè)由眾多頂尖企業(yè)共同完成的一個(gè)復(fù)雜過程。本文努力將這一工藝過程做一個(gè)匯總,對(duì)這個(gè...

芯片制造的最后一道工序?yàn)闇y(cè)試,其又可分為一般測(cè)試和特殊測(cè)試,前者是將封裝后的芯片置于各種環(huán)境下測(cè)試其電氣特性,如消耗功率、運(yùn)行速度、耐壓...

細(xì)述幾種高效晶體硅太陽(yáng)能電池技術(shù)

一般高效單晶硅電池采用化學(xué)腐蝕制絨技術(shù),制得絨面的反射率可達(dá)到10%以下。目前較為先進(jìn)的制絨技術(shù)是反應(yīng)等離子蝕刻技術(shù)(RIE),該...

2024-03-19 標(biāo)簽:太陽(yáng)能電池蝕刻晶體硅 1935 0

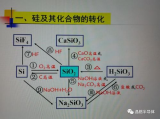

硅元素在自然界中主要以氧化物形式為主的化合物狀態(tài)存在。這些化合物在常溫下的化學(xué)性質(zhì)十分穩(wěn)定。而在高溫下,硅幾乎可以所有物質(zhì)發(fā)生化學(xué)反...

2024-03-15 標(biāo)簽:晶圓半導(dǎo)體材料蝕刻 3496 0

現(xiàn)在對(duì) 2 個(gè)晶圓進(jìn)行處理,為粘合做好準(zhǔn)備。它們經(jīng)過 N2 等離子體處理以激活表面。等離子處理改變了表面的特性,以增加表面能并使其更加親...

在封裝史上,最后一次重大范式轉(zhuǎn)變是從引線鍵合到倒裝芯片。從那時(shí)起,更先進(jìn)的封裝形式(例如晶圓級(jí)扇出和 TCB)一直是相同核心原理的漸進(jìn)式改進(jìn...

2024-02-27 標(biāo)簽:晶圓芯片設(shè)計(jì)蝕刻 3826 0

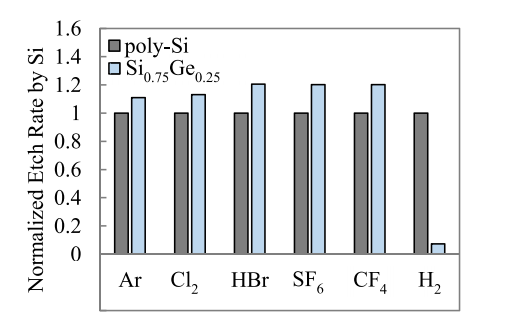

硅雙通道光纖低溫等離子體蝕刻控制與SiGe表面成分調(diào)制

在過去的幾年中,MOSFET結(jié)構(gòu)從平面結(jié)構(gòu)改變?yōu)轹捫徒Y(jié)構(gòu)(FinFETs ),這改善了短溝道效應(yīng),并導(dǎo)致更高...

各種疊層結(jié)構(gòu)的PCB圖內(nèi)部架構(gòu)設(shè)計(jì)

今天畫了幾張多層PCB電路板內(nèi)部結(jié)構(gòu)圖,用立體圖形展示各種疊層結(jié)構(gòu)的PCB圖內(nèi)部架構(gòu)。

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語(yǔ)言教程專題 教程专题

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無(wú)刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無(wú)人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |