完善資料讓更多小伙伴認識你,還能領(lǐng)取20積分哦,立即完善>

標簽 > DDR2

DDR2/DDR II(Double Data Rate 2)SDRAM是由JEDEC(電子設(shè)備工程聯(lián)合委員會)進行開發(fā)的新生代內(nèi)存技術(shù)標準

DDR2/DDR II(Double Data Rate 2)SDRAM是由JEDEC(電子設(shè)備工程聯(lián)合委員會)進行開發(fā)的新生代內(nèi)存技術(shù)標準,它與上一代DDR內(nèi)存技術(shù)標準最大的不同就是,雖然同是采用了在時鐘的上升/下降沿同時進行數(shù)據(jù)傳輸?shù)幕痉绞剑獶DR2內(nèi)存卻擁有兩倍于上一代DDR內(nèi)存預(yù)讀取能力(即:4bit數(shù)據(jù)讀預(yù)取)。換句話說,DDR2內(nèi)存每個時鐘能夠以4倍外部總線的速度讀/寫數(shù)據(jù),并且能夠以內(nèi)部控制總線4倍的速度運行。

由于DDR2標準規(guī)定所有DDR2內(nèi)存均采用FBGA封裝形式,而不同于廣泛應(yīng)用的TSOP/TSOP-Ⅱ封裝形式,F(xiàn)BGA封裝可以提供了更為良好的電氣性能與散熱性,為DDR2內(nèi)存的穩(wěn)定工作與未來頻率的發(fā)展提供了堅實的基礎(chǔ)。回想起DDR的發(fā)展歷程,從第一代應(yīng)用到個人電腦的DDR200經(jīng)過DDR266、DDR333到今天的雙通道DDR400技術(shù),第一代DDR的發(fā)展也走到了技術(shù)的極限,已經(jīng)很難通過常規(guī)辦法提高內(nèi)存的工作速度;隨著Intel最新處理器技術(shù)的發(fā)展,前端總線對內(nèi)存帶寬的要求是越來越高,擁有更高更穩(wěn)定運行頻率的DDR2內(nèi)存將是大勢所趨。

DDR2/DDR II(Double Data Rate 2)SDRAM是由JEDEC(電子設(shè)備工程聯(lián)合委員會)進行開發(fā)的新生代內(nèi)存技術(shù)標準,它與上一代DDR內(nèi)存技術(shù)標準最大的不同就是,雖然同是采用了在時鐘的上升/下降沿同時進行數(shù)據(jù)傳輸?shù)幕痉绞剑獶DR2內(nèi)存卻擁有兩倍于上一代DDR內(nèi)存預(yù)讀取能力(即:4bit數(shù)據(jù)讀預(yù)取)。換句話說,DDR2內(nèi)存每個時鐘能夠以4倍外部總線的速度讀/寫數(shù)據(jù),并且能夠以內(nèi)部控制總線4倍的速度運行。

由于DDR2標準規(guī)定所有DDR2內(nèi)存均采用FBGA封裝形式,而不同于廣泛應(yīng)用的TSOP/TSOP-Ⅱ封裝形式,F(xiàn)BGA封裝可以提供了更為良好的電氣性能與散熱性,為DDR2內(nèi)存的穩(wěn)定工作與未來頻率的發(fā)展提供了堅實的基礎(chǔ)。回想起DDR的發(fā)展歷程,從第一代應(yīng)用到個人電腦的DDR200經(jīng)過DDR266、DDR333到今天的雙通道DDR400技術(shù),第一代DDR的發(fā)展也走到了技術(shù)的極限,已經(jīng)很難通過常規(guī)辦法提高內(nèi)存的工作速度;隨著Intel最新處理器技術(shù)的發(fā)展,前端總線對內(nèi)存帶寬的要求是越來越高,擁有更高更穩(wěn)定運行頻率的DDR2內(nèi)存將是大勢所趨。

種類區(qū)別

延遲問題

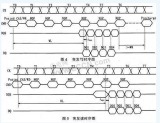

從上表可以看出,在同等核心頻率下,DDR2的實際工作頻率是DDR的兩倍。這得益于DDR2內(nèi)存擁有兩倍于標準DDR內(nèi)存的4BIT預(yù)讀取能力。換句話說,雖然DDR2和DDR一樣,都采用了在時鐘的上升延和下降延同時進行數(shù)據(jù)傳輸?shù)幕痉绞剑獶DR2擁有兩倍于DDR的預(yù)讀取系統(tǒng)命令數(shù)據(jù)的能力。也就是說,在同樣100MHz的工作頻率下,DDR的實際頻率為200MHz,而DDR2則可以達到400MHz。這樣也就出現(xiàn)了另一個問題:在同等工作頻率的DDR和DDR2內(nèi)存中,后者的內(nèi)存延時要慢于前者。舉例來說,DDR 400和DDR2-400具有相同的延遲,而后者具有高一倍的帶寬。實際上,DDR2-400和DDR 400具有相同的帶寬,它們都是3.2GB/s,但是DDR400的核心工作頻率是200MHz,而DDR2-400的核心工作頻率是100MHz,也就是說DDR2-400的延遲要高于DDR400。

封裝

DDR2內(nèi)存技術(shù)最大的突破點其實不在于用戶們所認為的兩倍于DDR的傳輸能力,而是在采用更低發(fā)熱量、更低功耗的情況下,DDR2可以獲得更快的頻率提升,突破標準DDR的400MHZ限制。DDR內(nèi)存通常采用TSOP芯片封裝形式,這種封裝形式可以很好的工作在200MHz上,當頻率更高時,它過長的管腳就會產(chǎn)生很高的阻抗和寄生電容,這會影響它的穩(wěn)定性和頻率提升的難度。這也就是DDR的核心頻率很難突破275MHZ的原因。而DDR2內(nèi)存均采用FBGA封裝形式。不同于廣泛應(yīng)用的TSOP封裝形式,F(xiàn)BGA封裝提供了更好的電氣性能與散熱性,為DDR2內(nèi)存的穩(wěn)定工作與未來頻率的發(fā)展提供了良好的保障。DDR2內(nèi)存采用1.8V電壓,相對于DDR標準的2.5V,降低了不少,從而提供了明顯的更小的功耗與更小的發(fā)熱量,這一點的變化是意義重大的。

雙通道內(nèi)存

需要INTEL芯片組的支持,內(nèi)存的CAS延遲、容量需要相同。不過,INTEL的彈性雙通道的出現(xiàn)使雙通道的形成條件更加寬松,不同容量的內(nèi)存甚至都能組建雙通道除了以上所說的區(qū)別外,DDR2還引入了三項新的技術(shù),它們是OCD、ODT和Post CAS。

離線驅(qū)動

OCD(Off-Chip Driver):也就是所謂的離線驅(qū)動調(diào)整,DDR Ⅱ通過OCD可以提高信號的完整性。DDR Ⅱ通過調(diào)整上拉(pull-up)/下拉(pull-down)的電阻值使兩者電壓相等。使用OCD通過減少DQ-DQS的傾斜來提高信號的完整性;通過控制電壓來提高信號品質(zhì)。

終結(jié)電阻器

ODT:ODT是內(nèi)建核心的終結(jié)電阻器。我們知道使用DDR SDRAM的主板上面為了防止數(shù)據(jù)線終端反射信號需要大量的終結(jié)電阻。它大大增加了主板的制造成本。實際上,不同的內(nèi)存模組對終結(jié)電路的要求是不一樣的,終結(jié)電阻的大小決定了數(shù)據(jù)線的信號比和反射率,終結(jié)電阻小則數(shù)據(jù)線信號反射低但是信噪比也較低;終結(jié)電阻高,則數(shù)據(jù)線的信噪比高,但是信號反射也會增加。因此主板上的終結(jié)電阻并不能非常好的匹配內(nèi)存模組,還會在一定程度上影響信號品質(zhì)。DDR2可以根據(jù)自己的特點內(nèi)建合適的終結(jié)電阻,這樣可以保證最佳的信號波形。使用DDR2不但可以降低主板成本,還得到了最佳的信號品質(zhì),這是DDR不能比擬的。

利用效率

Post CAS:它是為了提高DDR Ⅱ內(nèi)存的利用效率而設(shè)定的。在Post CAS操作中,CAS信號(讀寫/命令)能夠被插到RAS信號后面的一個時鐘周期,CAS命令可以在附加延遲(Additive Latency)后面保持有效。原來的tRCD(RAS到CAS和延遲)被AL(Additive Latency)所取代,AL可以在0,1,2,3,4中進行設(shè)置。由于CAS信號放在了RAS信號后面一個時鐘周期,因此ACT和CAS信號永遠也不會產(chǎn)生碰撞沖突。 采用雙通道運行,速度是DDR的2倍。 總的來說,DDR2采用了諸多的新技術(shù),改善了DDR的諸多不足,雖然它目前有成本高、延遲慢能諸多不足,但相信隨著技術(shù)的不斷提高和完善,這些問題終將得到解決。

技術(shù)特點

DDR2引入了三項新的技術(shù),它們是OCD、ODT和PostCAS。

OCD(Off-ChipDriver):也就是所謂的離線驅(qū)動調(diào)整。

ODT:ODT是內(nèi)建核心的終結(jié)電阻器。

PostCAS:它是為了提高DDR2內(nèi)存的利用效率而設(shè)定的。

DDR2和DDR3有什么區(qū)別

DDR2和DDR3的區(qū)別

DDR2和DDR3的插槽是不一樣,DDR3比DDR2頻率高,速度快,容量大,性能高。

DDR3內(nèi)存相對于DDR2內(nèi)存,其實只是規(guī)格上的提高,并沒有真正的全面換代的新架構(gòu)。DDR3接觸針腳數(shù)目同DDR2皆為240pin。但是防呆的缺口位置不同。DDR3在大容量內(nèi)存的支持較好,而大容量內(nèi)存的分水嶺是4GB這個容量,4GB是32位操作系統(tǒng)的執(zhí)行上限(不考慮PAE等等的內(nèi)存映像模式,因這些32位元元延伸模式只是過渡方式,會降低效能,不會在零售市場成為技術(shù)主流)當市場需求超過4GB的時候,64位CPU與操作系統(tǒng)就是唯一的解決方案,此時也就是DDR3內(nèi)存的普及時期。

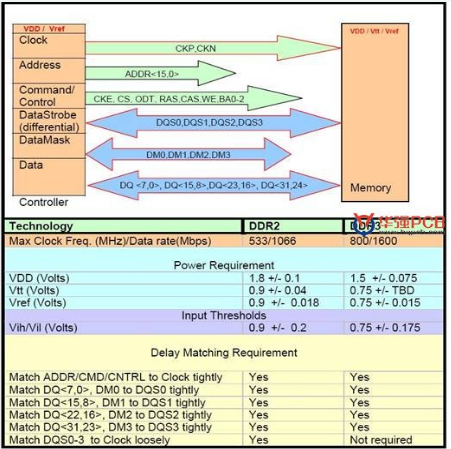

DDR2與DDR3內(nèi)存的特性區(qū)別:

1、邏輯Bank數(shù)量

DDR2 SDRAM中有4Bank和8Bank的設(shè)計,目的就是為了應(yīng)對未來大容量芯片的需求。而DDR3很可能將從2Gb容量起步,因此起始的邏輯Bank就是8個,另外還為未來的16個邏輯Bank做好了準備。

2、封裝(Packages)

由于DDR3新增了一些功能,在引腳方面會有所增加,8bit芯片采用78球FBGA封裝,16bit芯片采用96球FBGA封裝,而DDR2則有60/68/84球FBGA封裝三種規(guī)格。并且DDR3必須是綠色封裝,不能含有任何有害物質(zhì)。

3、突發(fā)長度(BL,Burst Length)

由于DDR3的預(yù)取為8bit,所以突發(fā)傳輸周期(BL,Burst Length)也固定為8,而對于DDR2和早期的DDR架構(gòu)的系統(tǒng),BL=4也是常用的,DDR3為此增加了一個4-bit Burst Chop(突發(fā)突變)模式,即由一個BL=4的讀取操作加上一個BL=4的寫入操作來合成一個BL=8的數(shù)據(jù)突發(fā)傳輸,屆時可通過A12地址線來控制這一突發(fā)模式。

4、尋址時序(Timing)

就像DDR2從DDR轉(zhuǎn)變而來后延遲周期數(shù)增加一樣,DDR3的CL周期也將比DDR2有所提高。DDR2的CL范圍一般在2至5之間,而DDR3則在5至11之間,且附加延遲(AL)的設(shè)計也有所變化。DDR2時AL的范圍是0至4,而DDR3時AL有三種選項,分別是0、CL-1和CL-2。另外,DDR3還新增加了一個時序參數(shù)——寫入延遲(CWD),這一參數(shù)將根據(jù)具體的工作頻率而定。

二、與DDR2相比DDR3具有的優(yōu)點(桌上型unbuffered DIMM):

1.速度更快:prefetch buffer寬度從4bit提升到8bit,核心同頻率下數(shù)據(jù)傳輸量將會是DDR2的兩倍。

2.更省電:DDR3 Module電壓從DDR2的1.8V降低到1.5V,同頻率下比DDR2更省電,搭配SRT(Self-Refresh Temperature)功能,內(nèi)部增加溫度senser,可依溫度動態(tài)控制更新率(RASR,Partial Array Self-Refresh功能),達到省電目的。

3.容量更大:更多的Bank數(shù)量,依照JEDEC標準,DDR2應(yīng)可出到單位元元4Gb的容量(亦即單條模塊可到8GB),但目前許多DRAM廠商的規(guī)劃,DDR2生產(chǎn)可能會跳過這個4Gb單位元元容量,也就是說屆時單條DDR2的DRAM模塊,容量最大可能只會到4GB。而DDR3模塊容量將從1GB起跳,目前規(guī)劃單條模塊到16GB也沒問題(注意:這里指的是零售組裝市場專用的unbuffered DIMM而言,server用的FB與Registered不在此限)。

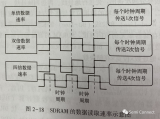

在同步動態(tài)隨機存取存儲器(SDRAM)的工作模式中,以數(shù)據(jù)讀取速率來分類,有單倍數(shù)據(jù)速率 (Single Data Rate, SDR) SDRAM、雙....

在嵌入式系統(tǒng)中,內(nèi)存是比較緊缺的資源,特別是在消費類產(chǎn)品中, 為了節(jié)省成本,一般都會將硬件資源應(yīng)用到極致。在開發(fā)過程中,就經(jīng)...

改善帶有ECC奇數(shù)負載的DDR2信號質(zhì)量的方法

這里介紹兩種方式改善帶有ECC的奇數(shù)負載的DDR2信號質(zhì)量。一種不需要改變拓撲結(jié)構(gòu),另一種需要對拓撲結(jié)構(gòu)進行調(diào)整。

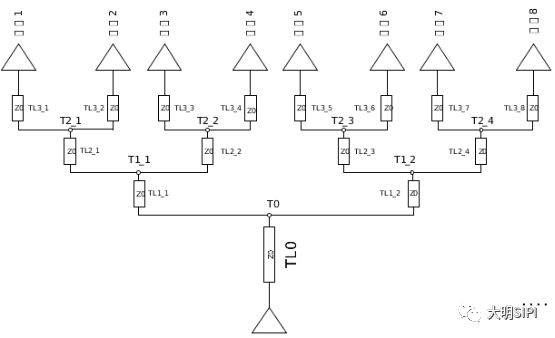

樹形拓撲結(jié)構(gòu)的設(shè)計關(guān)鍵點

樹形拓撲也是一種非常常見的拓撲,DDR2的內(nèi)存條中地址控制信號經(jīng)常使用這種拓撲。雖然現(xiàn)在信號的速率越來越高,DDR5的速率已經(jīng)達到了6400Mbps,早....

DDR、DDR2、DDR3、DDR4、LPDDR區(qū)別

DDR是Double Data Rate的縮寫,即“雙比特翻轉(zhuǎn)”。DDR是一種技術(shù),中國大陸工程師習(xí)慣用DDR稱呼用了DDR技術(shù)的SDRAM,而在中國臺...

本文首先列出了DDR2布線中面臨的困難,接著系統(tǒng)的講述了DDR2電路板設(shè)計的具體方法,最后給出個人對本次電路設(shè)計的一些思考。

基于DDR2和DDR3的PCB信號完整性設(shè)計和注意事項解析

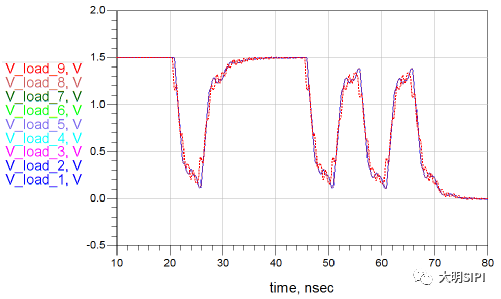

目前,比較普遍使用中的DDR2的速度已經(jīng)高達800 Mbps,甚至更高的速度,如1066 Mbps,而DDR3的速度已經(jīng)高達1600 Mbps。對于如此...

2019-07-25 標簽:DDR3DDR2PCB設(shè)計 2054 0

TMS320DM644x DMSoC DDR2內(nèi)存控制器用戶指南立即下載

類別:電子資料 2024-12-16 標簽:DDR2內(nèi)存控制器DMSoC

在TMS320C6455/C6454上實現(xiàn)DDR2 PCB布局立即下載

類別:電子資料 2024-10-16 標簽:pcbDDR2TMS320C6455

在TMS320DM335 DMSoC上實現(xiàn)DDR2/mDDR PCB布局立即下載

類別:電子資料 2024-10-15 標簽:pcbDDR2tms320dm335

華邦自DDR2時期就深入物聯(lián)網(wǎng)、汽車、工業(yè)、電信等高附加值領(lǐng)域,而隨著制程升級至DDR3階段,該公司開始加大對DDR3產(chǎn)能建設(shè)的投資力...

2024-05-13 標簽:DRAM物聯(lián)網(wǎng)DDR2 648 0

致遠微電子首款多媒體控制和圖像顯示應(yīng)用高集成度芯片——ZMP110XP144C

ZMP110XP144C是廣州致遠微電子推出的首款多媒體控制和圖像顯示應(yīng)用的高集成度芯片,采用ARM9內(nèi)核架構(gòu),內(nèi)部集成了DDR2 SDRAM存儲器、圖...

K4T51163Q(三星DDR2)停產(chǎn)了怎么辦?

不少工程師發(fā)現(xiàn),公司產(chǎn)品量產(chǎn)時突然采購告知所用SDRAM缺貨或停產(chǎn)了,讓工程師重新找一個替代的型號,輕則找一個PIN TO PIN兼容的就完事了...

DDR2連接器實現(xiàn)內(nèi)存擴展 兩種端接類型均可使用無鉛選項

FCI開發(fā)了一系列垂直內(nèi)存插槽,可接受標準DDR2(雙倍數(shù)據(jù)速率)內(nèi)存模塊組件,以便在臺式機和服務(wù)器中實現(xiàn)內(nèi)存擴展。 240...

基于FPGA與DDR2 SDRAM器件HY5PS121621實現(xiàn)DDR2控制器的設(shè)計

DDR2(Double Data Rate2)SDRAM是由JEDEC(電子設(shè)備工程聯(lián)合委員會)制定的新生代內(nèi)存技術(shù)標準,它與上一代DDR內(nèi)存技術(...

泰克推出完整的DDR2協(xié)議調(diào)試和驗證解決方案

全球領(lǐng)先的測試、測量和監(jiān)測儀器提供商--泰克公司日前宣布,推出完整的 DDR2 協(xié)議調(diào)試和驗證解決方案,基于屢獲獎項的 TLA6000 系列邏輯分析儀

據(jù)報道,存儲芯片調(diào)研公司inSpectrum近日表示,7月份下半個月的主流DDR3內(nèi)存期貨價格已經(jīng)出現(xiàn)了小幅度下滑,這也反映出了市場的低需求。逐步...

DDR2,DDR2是什么意思 DDR2(Double Data Rate 2) SDRAM是由JEDEC(電子設(shè)備工程聯(lián)合委員會)進行開發(fā)的新生代內(nèi)存...

2010-03-24 標簽:DDR2 1496 0

IDT推出DDR3內(nèi)存模塊高精度溫度傳感器 新器件可提高企業(yè)、移動及嵌入式計算系統(tǒng)的可靠性、性能和電源效率 IDT公司(Integrated ...

廠商采取搭售策略 挽回DDR2銷售頹勢 全球DRAM市場正加速進行世代交替,DDR3芯片因缺貨使得價格持續(xù)上漲,DDR2價格卻嚴重下跌,且累積庫存越...

2010-01-20 標簽:DDR2 799 0

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題 教程专题

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |